Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 60 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                  |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 256KB (85.5K x 24)                                                             |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 6x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                             |

| Mounting Type              | Through Hole                                                                   |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                        |

| Supplier Device Package    | 28-SPDIP                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep256mc202-e-sp |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 4.2 Data Address Space

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X CPU has a separate 16-bit-wide data memory space. The Data Space is accessed using separate Address Generation Units (AGUs) for read and write operations. The data memory maps, which are presented by device family and memory size, are shown in Figure 4-7 through Figure 4-16.

All Effective Addresses (EAs) in the data memory space are 16 bits wide and point to bytes within the Data Space. This arrangement gives a base Data Space address range of 64 Kbytes (32K words).

The base Data Space address is used in conjunction with a Read or Write Page register (DSRPAG or DSWPAG) to form an Extended Data Space, which has a total address range of 16 Mbytes.

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices implement up to 52 Kbytes of data memory (4 Kbytes of data memory for Special Function Registers and up to 48 Kbytes of data memory for RAM). If an EA points to a location outside of this area, an all-zero word or byte is returned.

# 4.2.1 DATA SPACE WIDTH

The data memory space is organized in byteaddressable, 16-bit-wide blocks. Data is aligned in data memory and registers as 16-bit words, but all Data Space EAs resolve to bytes. The Least Significant Bytes (LSBs) of each word have even addresses, while the Most Significant Bytes (MSBs) have odd addresses.

#### 4.2.2 DATA MEMORY ORGANIZATION AND ALIGNMENT

To maintain backward compatibility with PIC<sup>®</sup> MCU devices and improve Data Space memory usage efficiency, the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X instruction set supports both word and byte operations. As a consequence of byte accessibility, all Effective Address calculations are internally scaled to step through word-aligned memory. For example, the core recognizes that Post-Modified Register Indirect Addressing mode [Ws++] results in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

A data byte read, reads the complete word that contains the byte, using the LSb of any EA to determine which byte to select. The selected byte is placed onto the LSB of the data path. That is, data memory and registers are organized as two parallel, byte-wide entities with shared (word) address decode but separate write lines. Data byte writes only write to the corresponding side of the array or register that matches the byte address. All word accesses must be aligned to an even address. Misaligned word data fetches are not supported, so care must be taken when mixing byte and word operations, or translating from 8-bit MCU code. If a misaligned read or write is attempted, an address error trap is generated. If the error occurred on a read, the instruction underway is completed. If the error occurred on a write, the instruction is executed but the write does not occur. In either case, a trap is then executed, allowing the system and/or user application to examine the machine state prior to execution of the address Fault.

All byte loads into any W register are loaded into the LSB. The MSB is not modified.

A Sign-Extend (SE) instruction is provided to allow user applications to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, user applications can clear the MSB of any W register by executing a Zero-Extend (ZE) instruction on the appropriate address.

# 4.2.3 SFR SPACE

The first 4 Kbytes of the Near Data Space, from 0x0000 to 0x0FFF, is primarily occupied by Special Function Registers (SFRs). These are used by the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X core and peripheral modules for controlling the operation of the device.

SFRs are distributed among the modules that they control and are generally grouped together by module. Much of the SFR space contains unused addresses; these are read as '0'.

**Note:** The actual set of peripheral features and interrupts varies by the device. Refer to the corresponding device tables and pinout diagrams for device-specific information.

# 4.2.4 NEAR DATA SPACE

The 8-Kbyte area, between 0x0000 and 0x1FFF, is referred to as the Near Data Space. Locations in this space are directly addressable through a 13-bit absolute address field within all memory direct instructions. Additionally, the whole Data Space is addressable using MOV instructions, which support Memory Direct Addressing mode with a 16-bit address field, or by using Indirect Addressing mode using a working register as an Address Pointer.

#### TABLE 4-24: CRC REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14                 | Bit 13 | Bit 12 | Bit 11 | Bit 10    | Bit 9 | Bit 8    | Bit 7        | Bit 6  | Bit 5   | Bit 4 | Bit 3   | Bit 2     | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------|--------|------------------------|--------|--------|--------|-----------|-------|----------|--------------|--------|---------|-------|---------|-----------|-------|-------|---------------|

| CRCCON1   | 0640  | CRCEN  | —                      | CSIDL  |        | V      | WORD<4:0  | )>    |          | CRCFUL       | CRCMPT | CRCISEL | CRCGO | LENDIAN | _         | _     | —     | 0000          |

| CRCCON2   | 0642  |        | _                      | _      |        | D      | WIDTH<4:0 | )>    |          | _            | -      | _       |       | F       | PLEN<4:0> |       |       | 0000          |

| CRCXORL   | 0644  |        | X<15:1> —              |        |        |        |           |       |          |              | 0000   |         |       |         |           |       |       |               |

| CRCXORH   | 0646  |        |                        |        |        |        |           |       | X·       | <31:16>      |        |         |       |         |           |       |       | 0000          |

| CRCDATL   | 0648  |        |                        |        |        |        |           |       | CRC Data | Input Low V  | Vord   |         |       |         |           |       |       | 0000          |

| CRCDATH   | 064A  |        |                        |        |        |        |           |       | CRC Data | Input High \ | Vord   |         |       |         |           |       |       | 0000          |

| CRCWDATL  | 064C  |        | CRC Result Low Word    |        |        |        |           |       |          |              | 0000   |         |       |         |           |       |       |               |

| CRCWDATH  | 064E  |        | CRC Result High Word 0 |        |        |        |           |       |          |              | 0000   |         |       |         |           |       |       |               |

Legend: — = unimplemented, read as '0'. Shaded bits are not used in the operation of the programmable CRC module.

# TABLE 4-25: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EPXXXGP/MC202/502 AND PIC24EPXXXGP/MC202 DEVICES ONLY DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12     | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6      | Bit 5      | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|------------|--------|--------|-------|-------|-------|------------|------------|-------|-------|--------|-------|-------|---------------|

| RPOR0        | 0680  | —      | —      |        | RP35R<5:0> |        |        |       | _     | _     | RP20R<5:0> |            |       |       |        |       | 0000  |               |

| RPOR1        | 0682  | _      | _      |        | RP37R<5:0> |        |        |       | _     | Ι     | RP36R<5:0> |            |       |       |        |       | 0000  |               |

| RPOR2        | 0684  | _      | _      |        |            | RP39F  | <5:0>  |       |       | _     | Ι          | RP38R<5:0> |       |       |        |       | 0000  |               |

| RPOR3        | 0686  | _      | _      |        | RP41R<5:0> |        |        |       | _     | Ι     | RP40R<5:0> |            |       |       | 0000   |       |       |               |

| RPOR4        | 0688  | _      | _      |        | RP43R<5:0> |        |        |       |       | —     | _          |            |       | RP42F | R<5:0> |       |       | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-26: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EPXXXGP/MC203/503 AND PIC24EPXXXGP/MC203 DEVICES ONLY DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5      | Bit 4      | Bit 3 | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|------------|------------|-------|--------|-------|-------|---------------|

| RPOR0        | 0680  |        | —      |        |        | RP35F  | R<5:0> |       |       | _     | _     |            |            | RP20F | २<5:0> |       |       | 0000          |

| RPOR1        | 0682  | _      | _      |        |        | RP37F  | ۲<5:0> |       |       | _     | _     |            |            | RP36F | २<5:0> |       |       | 0000          |

| RPOR2        | 0684  | _      | _      |        |        | RP39F  | २<5:0> |       |       | _     | —     |            | RP38R<5:0> |       |        |       | 0000  |               |

| RPOR3        | 0686  | _      | _      |        |        | RP41F  | २<5:0> |       |       | _     | —     |            |            | RP40F | R<5:0> |       |       | 0000          |

| RPOR4        | 0688  | _      | _      |        |        | RP43F  | ۲<5:0> |       |       | _     | _     |            |            | RP42F | २<5:0> |       |       | 0000          |

| RPOR5        | 068A  | _      | _      | _      | _      | _      | _      |       | _     | _     | _     | _          | _          | _     | _      |       |       | 0000          |

| RPOR6        | 068C  | _      | —      | —      | _      | _      | _      | _     | —     | _     | _     | RP56R<5:0> |            |       | 0000   |       |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

|                                                     | Vector                        | IRQ     |                   | Inte     | errupt Bit L | ocation      |  |  |  |

|-----------------------------------------------------|-------------------------------|---------|-------------------|----------|--------------|--------------|--|--|--|

| Interrupt Source                                    | #                             | #       | IVT Address       | Flag     | Enable       | Priority     |  |  |  |

| QEI1 – QEI1 Position Counter Compare <sup>(2)</sup> | 66                            | 58      | 0x000088          | IFS3<10> | IEC3<10>     | IPC14<10:8>  |  |  |  |

| Reserved                                            | 67-72                         | 59-64   | 0x00008A-0x000094 | _        | _            | _            |  |  |  |

| U1E – UART1 Error Interrupt                         | 73                            | 65      | 0x000096          | IFS4<1>  | IEC4<1>      | IPC16<6:4>   |  |  |  |

| U2E – UART2 Error Interrupt                         | 74                            | 66      | 0x000098          | IFS4<2>  | IEC4<2>      | IPC16<10:8>  |  |  |  |

| CRC – CRC Generator Interrupt                       | 75                            | 67      | 0x00009A          | IFS4<3>  | IEC4<3>      | IPC16<14:12> |  |  |  |

| Reserved                                            | 76-77                         | 68-69   | 0x00009C-0x00009E | —        | _            | —            |  |  |  |

| C1TX – CAN1 TX Data Request <sup>(1)</sup>          | 78                            | 70      | 0x000A0           | IFS4<6>  | IEC4<6>      | IPC17<10:8>  |  |  |  |

| Reserved                                            | 79-84                         | 71-76   | 0x0000A2-0x0000AC | —        | _            | —            |  |  |  |

| CTMU – CTMU Interrupt                               | 85                            | 77      | 0x0000AE          | IFS4<13> | IEC4<13>     | IPC19<6:4>   |  |  |  |

| Reserved                                            | 86-101                        | 78-93   | 0x0000B0-0x0000CE | —        | _            | —            |  |  |  |

| PWM1 – PWM Generator 1 <sup>(2)</sup>               | 102                           | 94      | 0x0000D0          | IFS5<14> | IEC5<14>     | IPC23<10:8>  |  |  |  |

| PWM2 – PWM Generator 2 <sup>(2)</sup>               | 103                           | 95      | 0x0000D2          | IFS5<15> | IEC5<15>     | IPC23<14:12> |  |  |  |

| PWM3 – PWM Generator 3 <sup>(2)</sup>               | 104                           | 96      | 0x0000D4          | IFS6<0>  | IEC6<0>      | IPC24<2:0>   |  |  |  |

| Reserved                                            | 105-149                       | 97-141  | 0x0001D6-0x00012E | —        | _            | —            |  |  |  |

| ICD – ICD Application                               | 150                           | 142     | 0x000142          | IFS8<14> | IEC8<14>     | IPC35<10:8>  |  |  |  |

| JTAG – JTAG Programming                             | 151                           | 143     | 0x000130          | IFS8<15> | IEC8<15>     | IPC35<14:12> |  |  |  |

| Reserved                                            | 152                           | 144     | 0x000134          | —        | _            | _            |  |  |  |

| PTGSTEP – PTG Step                                  | 153                           | 145     | 0x000136          | IFS9<1>  | IEC9<1>      | IPC36<6:4>   |  |  |  |

| PTGWDT – PTG Watchdog Time-out                      | 154                           | 146     | 0x000138          | IFS9<2>  | IEC9<2>      | IPC36<10:8>  |  |  |  |

| PTG0 – PTG Interrupt 0                              | 155                           | 147     | 0x00013A          | IFS9<3>  | IEC9<3>      | IPC36<14:12> |  |  |  |

| PTG1 – PTG Interrupt 1                              | 156                           | 148     | 0x00013C          | IFS9<4>  | IEC9<4>      | IPC37<2:0>   |  |  |  |

| PTG2 – PTG Interrupt 2                              | 157                           | 149     | 0x00013E          | IFS9<5>  | IEC9<5>      | IPC37<6:4>   |  |  |  |

| PTG3 – PTG Interrupt 3                              | 158                           | 150     | 0x000140          | IFS9<6>  | IEC9<6>      | IPC37<10:8>  |  |  |  |

| Reserved                                            | 159-245                       | 151-245 | 0x000142-0x0001FE | —        | —            | _            |  |  |  |

|                                                     | Lowest Natural Order Priority |         |                   |          |              |              |  |  |  |

# TABLE 7-1: INTERRUPT VECTOR DETAILS (CONTINUED)

Note 1: This interrupt source is available on dsPIC33EPXXXGP50X and dsPIC33EPXXXMC50X devices only.

2: This interrupt source is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

| U-0     | U-0   | U-0   | U-0   | U-0        | U-0   | U-0   | U-0   |

|---------|-------|-------|-------|------------|-------|-------|-------|

| —       | —     | —     | —     | —          | —     | —     | —     |

| bit 15  | •     |       |       |            | •     |       | bit 8 |

|         |       |       |       |            |       |       |       |

| U-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

| _       |       |       |       | OCFAR<6:0> | >     |       |       |

| bit 7   | •     |       |       |            |       |       | bit 0 |

|         |       |       |       |            |       |       |       |

| Leaend: |       |       |       |            |       |       |       |

#### REGISTER 11-6: RPINR11: PERIPHERAL PIN SELECT INPUT REGISTER 11

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-7 Unimplemented: Read as '0'

bit 6-0 OCFAR<6:0>: Assign Output Compare Fault A (OCFA) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) 1111001 = Input tied to RPI121

> . 0000001 = Input tied to CMP1 0000000 = Input tied to Vss

# 13.0 TIMER2/3 AND TIMER4/5

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70362) of the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The Timer2/3 and Timer4/5 modules are 32-bit timers, which can also be configured as four independent 16-bit timers with selectable operating modes.

As 32-bit timers, Timer2/3 and Timer4/5 operate in three modes:

- Two Independent 16-Bit Timers (e.g., Timer2 and Timer3) with all 16-Bit Operating modes (except Asynchronous Counter mode)

- Single 32-Bit Timer

- Single 32-Bit Synchronous Counter

- They also support these features:

- Timer Gate Operation

- Selectable Prescaler Settings

- Timer Operation during Idle and Sleep modes

- Interrupt on a 32-Bit Period Register Match

- Time Base for Input Capture and Output Compare Modules (Timer2 and Timer3 only)

- ADC1 Event Trigger (32-bit timer pairs, and Timer3 and Timer5 only)

Individually, all four of the 16-bit timers can function as synchronous timers or counters. They also offer the features listed previously, except for the event trigger; this is implemented only with Timer2/3. The operating modes and enabled features are determined by setting the appropriate bit(s) in the T2CON, T3CON, and T4CON, T5CON registers. T2CON and T4CON are shown in generic form in Register 13-1. T3CON and T5CON are shown in Register 13-2.

For 32-bit timer/counter operation, Timer2 and Timer4 are the least significant word (lsw); Timer3 and Timer5 are the most significant word (msw) of the 32-bit timers.

Note: For 32-bit operation, T3CON and T5CON control bits are ignored. Only T2CON and T4CON control bits are used for setup and control. Timer2 and Timer4 clock and gate inputs are utilized for the 32-bit timer modules, but an interrupt is generated with the Timer3 and Timer5 interrupt flags.

A block diagram for an example 32-bit timer pair (Timer2/3 and Timer4/5) is shown in Figure 13-3.

**Note:** Only Timer2, 3, 4 and 5 can trigger a DMA data transfer.

# 14.2 Input Capture Registers

#### REGISTER 14-1: ICxCON1: INPUT CAPTURE x CONTROL REGISTER 1

| U-0    | U-0 | R/W-0  | R/W-0   | R/W-0   | R/W-0   | U-0 | U-0   |

|--------|-----|--------|---------|---------|---------|-----|-------|

| _      | —   | ICSIDL | ICTSEL2 | ICTSEL1 | ICTSEL0 |     | —     |

| bit 15 |     |        |         |         |         |     | bit 8 |

| U-0   | R/W-0 | R/W-0 | R/HC/HS-0 | R/HC/HS-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-----------|-----------|-------|-------|-------|

| —     | ICI1  | ICI0  | ICOV      | ICBNE     | ICM2  | ICM1  | ICM0  |

| bit 7 |       |       |           |           |       |       | bit 0 |

| Legend:           | HC = Hardware Clearable bit | HS = Hardware Settable bit |                    |  |  |  |

|-------------------|-----------------------------|----------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, re  | ead as '0'         |  |  |  |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared       | x = Bit is unknown |  |  |  |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                                  |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13    | ICSIDL: Input Capture Stop in Idle Control bit                                                                                                              |

|           | 1 = Input capture will Halt in CPU Idle mode                                                                                                                |

|           | 0 = Input capture will continue to operate in CPU Idle mode                                                                                                 |

| bit 12-10 | ICTSEL<2:0>: Input Capture Timer Select bits                                                                                                                |

|           | 111 = Peripheral clock (FP) is the clock source of the ICx                                                                                                  |

|           | 110 = Reserved                                                                                                                                              |

|           | 101 = Reserved                                                                                                                                              |

|           | 100 = T1CLK is the clock source of the ICx (only the synchronous clock is supported)<br>011 = T5CLK is the clock source of the ICx                          |

|           | 010 = T4CLK is the clock source of the ICx                                                                                                                  |

|           | 001 = T2CLK is the clock source of the ICx                                                                                                                  |

|           | 000 = T3CLK is the clock source of the ICx                                                                                                                  |

| bit 9-7   | Unimplemented: Read as '0'                                                                                                                                  |

| bit 6-5   | ICI<1:0>: Number of Captures per Interrupt Select bits (this field is not used if ICM<2:0> = 001 or 111)                                                    |

|           | 11 = Interrupt on every fourth capture event                                                                                                                |

|           | 10 = Interrupt on every third capture event                                                                                                                 |

|           | 01 = Interrupt on every second capture event<br>00 = Interrupt on every capture event                                                                       |

| bit 4     | ICOV: Input Capture Overflow Status Flag bit (read-only)                                                                                                    |

| bit 4     | 1 = Input capture buffer overflow occurred                                                                                                                  |

|           | 0 = No input capture buffer overflow occurred                                                                                                               |

| bit 3     | ICBNE: Input Capture Buffer Not Empty Status bit (read-only)                                                                                                |

|           | 1 = Input capture buffer is not empty, at least one more capture value can be read                                                                          |

|           | 0 = Input capture buffer is empty                                                                                                                           |

| bit 2-0   | ICM<2:0>: Input Capture Mode Select bits                                                                                                                    |

|           | 111 = Input capture functions as interrupt pin only in CPU Sleep and Idle modes (rising edge detect only, all other control bits are not applicable)        |

|           | 110 = Unused (module is disabled)                                                                                                                           |

|           | 101 = Capture mode, every 16th rising edge (Prescaler Capture mode)                                                                                         |

|           | <ul> <li>100 = Capture mode, every 4th rising edge (Prescaler Capture mode)</li> <li>011 = Capture mode, every rising edge (Simple Capture mode)</li> </ul> |

|           | 010 = Capture mode, every falling edge (Simple Capture mode)                                                                                                |

|           | 001 = Capture mode, every edge rising and falling (Edge Detect mode (ICI<1:0>) is not used in this mode)                                                    |

|           | 000 = Input capture module is turned off                                                                                                                    |

| U-0    | U-0      | U-0 | U-0   | U-0   | U-0   | U-0   | R/W-0 |

|--------|----------|-----|-------|-------|-------|-------|-------|

| —      | _        | -   | —     | —     | —     | —     | IC32  |

| bit 15 |          |     |       |       |       |       | bit 8 |

|        |          |     |       |       |       |       |       |

| R/W-0  | R/W/HS-0 | U-0 | R/W-0 | R/W-1 | R/W-1 | R/W-0 | R/W-1 |

#### REGISTER 14-2: ICxCON2: INPUT CAPTURE x CONTROL REGISTER 2

| bit 7            |                      |                                    | bit 0 |

|------------------|----------------------|------------------------------------|-------|

|                  |                      |                                    |       |

| Legend:          | HS = Hardware Settal | ble bit                            |       |

| R = Readable bit | W = Writable bit     | U = Unimplemented bit, read as '0' |       |

SYNCSEL4<sup>(4)</sup> SYNCSEL3<sup>(4)</sup> SYNCSEL2<sup>(4)</sup> SYNCSEL1<sup>(4)</sup>

SYNCSEL0(4)

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

|-------------------|------------------|----------------------|--------------------|

bit 15-9 Unimplemented: Read as '0'

TRIGSTAT<sup>(3)</sup>

ICTRIG<sup>(2)</sup>

bit 8

- IC32: Input Capture 32-Bit Timer Mode Select bit (Cascade mode)

- 1 = Odd IC and Even IC form a single 32-bit input capture module<sup>(1)</sup>

- 0 = Cascade module operation is disabled

#### bit 7 ICTRIG: Input Capture Trigger Operation Select bit<sup>(2)</sup>

- 1 = Input source used to trigger the input capture timer (Trigger mode)

- 0 = Input source used to synchronize the input capture timer to a timer of another module (Synchronization mode)

#### bit 6 **TRIGSTAT:** Timer Trigger Status bit<sup>(3)</sup>

- 1 = ICxTMR has been triggered and is running

- 0 = ICxTMR has not been triggered and is being held clear

#### bit 5 Unimplemented: Read as '0'

- **Note 1:** The IC32 bit in both the Odd and Even IC must be set to enable Cascade mode.

- 2: The input source is selected by the SYNCSEL<4:0> bits of the ICxCON2 register.

- **3:** This bit is set by the selected input source (selected by SYNCSEL<4:0> bits). It can be read, set and cleared in software.

- 4: Do not use the ICx module as its own Sync or Trigger source.

- 5: This option should only be selected as a trigger source and not as a synchronization source.

- 6: Each Input Capture x (ICx) module has one PTG input source. See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for more information.

PTGO8 = IC1 PTGO9 = IC2 PTGO10 = IC3 PTGO11 = IC4

DS70000657H-page 216

| U-0             | U-0   | R/W-0            | R/W-0      | R/W-0            | R/W-0           | R/W-0           | R/W-0 |  |  |  |

|-----------------|-------|------------------|------------|------------------|-----------------|-----------------|-------|--|--|--|

| —               | -     |                  | DTRx<13:8> |                  |                 |                 |       |  |  |  |

| bit 15          |       |                  |            |                  |                 |                 | bit 8 |  |  |  |

|                 |       |                  |            |                  |                 |                 |       |  |  |  |

| R/W-0           | R/W-0 | R/W-0            | R/W-0      | R/W-0            | R/W-0           | R/W-0           | R/W-0 |  |  |  |

|                 |       |                  | DTR        | x<7:0>           |                 |                 |       |  |  |  |

| bit 7           |       |                  |            |                  |                 |                 | bit 0 |  |  |  |

|                 |       |                  |            |                  |                 |                 |       |  |  |  |

| Legend:         |       |                  |            |                  |                 |                 |       |  |  |  |

| R = Readable    | bit   | W = Writable b   | bit        | U = Unimpler     | nented bit, rea | id as '0'       |       |  |  |  |

| -n = Value at F | POR   | '1' = Bit is set |            | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |  |  |  |

# REGISTER 16-10: DTRx: PWMx DEAD-TIME REGISTER

bit 15-14 Unimplemented: Read as '0'

bit 13-0 DTRx<13:0>: Unsigned 14-Bit Dead-Time Value for PWMx Dead-Time Unit bits

#### REGISTER 16-11: ALTDTRx: PWMx ALTERNATE DEAD-TIME REGISTER

| U-0                                                                  | U-0   | R/W-0            | R/W-0         | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |  |

|----------------------------------------------------------------------|-------|------------------|---------------|-----------------------------------------|-------|-------|-------|--|--|

| —                                                                    | _     |                  | ALTDTRx<13:8> |                                         |       |       |       |  |  |

| bit 15                                                               |       |                  |               |                                         |       |       | bit 8 |  |  |

|                                                                      |       |                  |               |                                         |       |       |       |  |  |

| R/W-0                                                                | R/W-0 | R/W-0            | R/W-0         | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |  |

|                                                                      |       |                  | ALTDT         | Rx<7:0>                                 |       |       |       |  |  |

| bit 7                                                                |       |                  |               |                                         |       |       | bit 0 |  |  |

| Legend:                                                              |       |                  |               |                                         |       |       |       |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |       |                  |               |                                         |       |       |       |  |  |

| -n = Value at P                                                      | OR    | '1' = Bit is set |               | '0' = Bit is cleared x = Bit is unknown |       |       |       |  |  |

bit 15-14 Unimplemented: Read as '0'

bit 13-0 ALTDTRx<13:0>: Unsigned 14-Bit Dead-Time Value for PWMx Dead-Time Unit bits

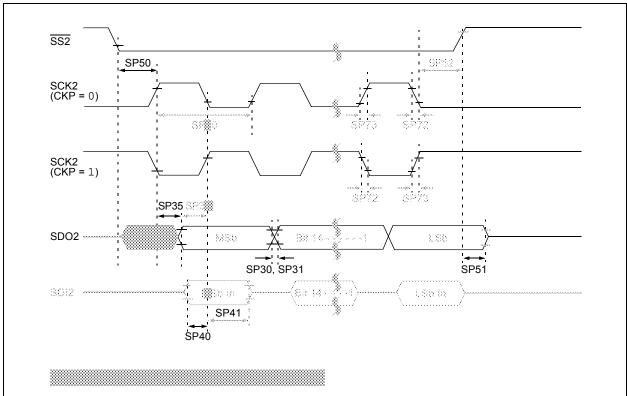

# 18.0 SERIAL PERIPHERAL INTERFACE (SPI)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Serial Peripheral Interface (SPI)" (DS70569) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The SPI module is a synchronous serial interface, useful for communicating with other peripheral or microcontroller devices. These peripheral devices can be serial EEPROMs, shift registers, display drivers, ADC Converters, etc. The SPI module is compatible with Motorola<sup>®</sup> SPI and SIOP interfaces.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X device family offers two SPI modules on a single device. These modules, which are designated as SPI1 and SPI2, are functionally identical. Each SPI module includes an eight-word FIFO buffer and allows DMA bus connections. When using the SPI module with DMA, FIFO operation can be disabled.

Note: In this section, the SPI modules are referred to together as SPIx, or separately as SPI1 and SPI2. Special Function Registers follow a similar notation. For example, SPIxCON refers to the control register for the SPI1 and SPI2 modules.

The SPI1 module uses dedicated pins which allow for a higher speed when using SPI1. The SPI2 module takes advantage of the Peripheral Pin Select (PPS) feature to allow for greater flexibility in pin configuration of the SPI2 module, but results in a lower maximum speed for SPI2. See **Section 30.0** "**Electrical Characteristics**" for more information.

The SPIx serial interface consists of four pins, as follows:

- SDIx: Serial Data Input

- SDOx: Serial Data Output

- SCKx: Shift Clock Input or Output

- SSx/FSYNCx: Active-Low Slave Select or Frame Synchronization I/O Pulse

The SPIx module can be configured to operate with two, three or four pins. In 3-pin mode, SSx is not used. In 2-pin mode, neither SDOx nor SSx is used.

Figure 18-1 illustrates the block diagram of the SPIx module in Standard and Enhanced modes.

# REGISTER 19-2: I2CxSTAT: I2Cx STATUS REGISTER (CONTINUED)

| bit 3 | S: Start bit                                                                                             |

|-------|----------------------------------------------------------------------------------------------------------|

|       | 1 = Indicates that a Start (or Repeated Start) bit has been detected last                                |

|       | 0 = Start bit was not detected last                                                                      |

|       | Hardware is set or clear when a Start, Repeated Start or Stop is detected.                               |

| bit 2 | <b>R_W:</b> Read/Write Information bit (when operating as I <sup>2</sup> C slave)                        |

|       | 1 = Read – Indicates data transfer is output from the slave                                              |

|       | 0 = Write – Indicates data transfer is input to the slave                                                |

|       | Hardware is set or clear after reception of an I <sup>2</sup> C device address byte.                     |

| bit 1 | RBF: Receive Buffer Full Status bit                                                                      |

|       | 1 = Receive is complete, I2CxRCV is full                                                                 |

|       | 0 = Receive is not complete, I2CxRCV is empty                                                            |

|       | Hardware is set when I2CxRCV is written with a received byte. Hardware is clear when software reads      |

|       | I2CxRCV.                                                                                                 |

| bit 0 | TBF: Transmit Buffer Full Status bit                                                                     |

|       | 1 = Transmit in progress, I2CxTRN is full                                                                |

|       | 0 = Transmit is complete, I2CxTRN is empty                                                               |

|       | Hardware is set when software writes to I2CxTRN. Hardware is clear at completion of a data transmission. |

| R/W-0           | R/W-0                           | R/W-0                            | U-0           | U-0              | U-0             | U-0             | U-0   |  |  |  |

|-----------------|---------------------------------|----------------------------------|---------------|------------------|-----------------|-----------------|-------|--|--|--|

| DMABS2          | DMABS1                          | DMABS0                           | —             | —                | —               | —               | —     |  |  |  |

| bit 15          |                                 |                                  |               |                  |                 |                 | bit 8 |  |  |  |

|                 |                                 |                                  |               |                  |                 |                 |       |  |  |  |

| U-0             | U-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0 |                                  |               |                  |                 |                 | R/W-0 |  |  |  |

| —               | _                               | —                                | FSA4          | FSA3             | FSA2            | FSA1            | FSA0  |  |  |  |

| bit 7           |                                 |                                  |               |                  |                 |                 | bit 0 |  |  |  |

|                 |                                 |                                  |               |                  |                 |                 |       |  |  |  |

| Legend:         |                                 |                                  |               |                  |                 |                 |       |  |  |  |

| R = Readable    | bit                             | W = Writable I                   | bit           | U = Unimpler     | mented bit, rea | d as '0'        |       |  |  |  |

| -n = Value at I | POR                             | '1' = Bit is set                 |               | '0' = Bit is cle | eared           | x = Bit is unkr | nown  |  |  |  |

|                 |                                 |                                  |               |                  |                 |                 |       |  |  |  |

| bit 15-13       | DMABS<2:0                       | >: DMA Buffer S                  | Size bits     |                  |                 |                 |       |  |  |  |

|                 | 111 = Reserved                  |                                  |               |                  |                 |                 |       |  |  |  |

|                 | 110 = 32 buffers in RAM         |                                  |               |                  |                 |                 |       |  |  |  |

|                 | 101 = 24 buffers in RAM         |                                  |               |                  |                 |                 |       |  |  |  |

|                 | 100 <b>= 16 buf</b>             | fers in RAM                      |               |                  |                 |                 |       |  |  |  |

|                 | 011 <b>= 12 buf</b>             |                                  |               |                  |                 |                 |       |  |  |  |

|                 | 010 = 8 buffe                   | -                                |               |                  |                 |                 |       |  |  |  |

|                 | 001 = 6 buffe                   | -                                |               |                  |                 |                 |       |  |  |  |

| bit 12-5        |                                 | nted: Read as '                  | <b>,</b>      |                  |                 |                 |       |  |  |  |

| bit 4-0         | -                               | IFO Area Starts                  |               | :4-              |                 |                 |       |  |  |  |

| DIT 4-0         |                                 |                                  | with Buller b | llS              |                 |                 |       |  |  |  |

|                 |                                 | ad Buffer RB31<br>ad Buffer RB30 |               |                  |                 |                 |       |  |  |  |

|                 | 11110 <b>- Rea</b>              |                                  |               |                  |                 |                 |       |  |  |  |

|                 | -                               |                                  |               |                  |                 |                 |       |  |  |  |

|                 | -                               |                                  |               |                  |                 |                 |       |  |  |  |

|                 |                                 |                                  |               |                  |                 |                 |       |  |  |  |

|                 |                                 | RX Buffer TRB1<br>RX Buffer TRB0 |               |                  |                 |                 |       |  |  |  |

|                 |                                 |                                  | ,             |                  |                 |                 |       |  |  |  |

|                 |                                 |                                  |               |                  |                 |                 |       |  |  |  |

# REGISTER 21-4: CxFCTRL: ECANx FIFO CONTROL REGISTER

| R/W-0                                                           | R/W-0                        | R/W-0                                                                                                                      | R/W-0                                          | R/W-0                              | R/W-0          | R/W-0           | R/W-0              |  |

|-----------------------------------------------------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|------------------------------------|----------------|-----------------|--------------------|--|

|                                                                 | F15B                         | P<3:0>                                                                                                                     |                                                | F14BP<3:0>                         |                |                 |                    |  |

| bit 15                                                          |                              |                                                                                                                            |                                                |                                    |                |                 | bit 8              |  |

| R/W-0                                                           | R/W-0                        | R/W-0                                                                                                                      | R/W-0                                          | R/W-0                              | R/W-0          | R/W-0           | R/W-0              |  |

| F13BP<3:0>                                                      |                              |                                                                                                                            |                                                |                                    |                | P<3:0>          | 1010 0             |  |

| bit 7                                                           |                              |                                                                                                                            |                                                |                                    |                |                 | bit 0              |  |

| Legend:                                                         |                              |                                                                                                                            |                                                |                                    |                |                 |                    |  |

| R = Readabl                                                     | e bit                        | W = Writable                                                                                                               | bit                                            | U = Unimplemented bit, read as '0' |                |                 |                    |  |

| -n = Value at                                                   | t POR                        | '1' = Bit is set                                                                                                           |                                                | '0' = Bit is cleared x =           |                | x = Bit is unkr | x = Bit is unknown |  |

| bit 15-12                                                       | 1111 = Filte<br>1110 = Filte | RX Buffer Ma<br>r hits received in<br>r hits received in<br>r hits received in<br>r hits received in<br>r hits received in | n RX FIFO bu<br>n RX Buffer 1<br>n RX Buffer 1 | ıffer<br>4                         |                |                 |                    |  |

| bit 11-8                                                        | F14BP<3:0:                   | RX Buffer Ma                                                                                                               | sk for Filter 1                                | 4 bits (same val                   | ues as bits<15 | :12>)           |                    |  |

| bit 7-4                                                         | F13BP<3:0;                   | RX Buffer Ma                                                                                                               | sk for Filter 1                                | 3 bits (same val                   | ues as bits<15 | :12>)           |                    |  |

| bit 3-0 F12BP<3:0>: RX Buffer Mask for Filter 12 bits (same val |                              |                                                                                                                            |                                                |                                    |                | :12>)           |                    |  |

# REGISTER 21-15: CxBUFPNT4: ECANx FILTER 12-15 BUFFER POINTER REGISTER 4

#### REGISTER 21-19: CxFMSKSEL2: ECANx FILTER 15-8 MASK SELECTION REGISTER 2

| R/W-0                                        | R/W-0                                                                                                                        | R/W-0                                                                                                                                            | R/W-0                                                                                                                                                | R/W-0                                                                                                                     | R/W-0                                                                   | R/W-0                        | R/W-0  |

|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|------------------------------|--------|

| F15MSK<1:0>                                  |                                                                                                                              | F14MS                                                                                                                                            | F14MSK<1:0>                                                                                                                                          |                                                                                                                           | F13MSK<1:0>                                                             |                              | K<1:0> |

| bit 15                                       |                                                                                                                              |                                                                                                                                                  |                                                                                                                                                      |                                                                                                                           |                                                                         |                              | bit 8  |

| R/W-0                                        | R/W-0                                                                                                                        | R/W-0                                                                                                                                            | R/W-0                                                                                                                                                | R/W-0                                                                                                                     | R/W-0                                                                   | R/W-0                        | R/W-0  |

|                                              | 1SK<1:0>                                                                                                                     | F10MS                                                                                                                                            |                                                                                                                                                      |                                                                                                                           | K<1:0>                                                                  |                              | <1:0>  |

| bit 7                                        |                                                                                                                              |                                                                                                                                                  |                                                                                                                                                      |                                                                                                                           |                                                                         |                              | bit C  |

|                                              |                                                                                                                              |                                                                                                                                                  |                                                                                                                                                      |                                                                                                                           |                                                                         |                              |        |

| Legend:                                      |                                                                                                                              |                                                                                                                                                  |                                                                                                                                                      |                                                                                                                           |                                                                         |                              |        |

| R = Readabl                                  | le bit                                                                                                                       | W = Writable                                                                                                                                     | bit                                                                                                                                                  | U = Unimplem                                                                                                              | nented bit, read                                                        | l as '0'                     |        |

| -n = Value at                                | t POR                                                                                                                        | '1' = Bit is set                                                                                                                                 |                                                                                                                                                      | '0' = Bit is cleared                                                                                                      |                                                                         | x = Bit is unknown           |        |

|                                              |                                                                                                                              |                                                                                                                                                  |                                                                                                                                                      |                                                                                                                           |                                                                         |                              |        |

|                                              |                                                                                                                              |                                                                                                                                                  |                                                                                                                                                      |                                                                                                                           |                                                                         |                              |        |

| bit 15-14                                    | F15MSK<1:                                                                                                                    | 0>: Mask Sourc                                                                                                                                   | e for Filter 15                                                                                                                                      | bits                                                                                                                      |                                                                         |                              |        |

| bit 15-14                                    | 11 = Reserv                                                                                                                  | ed                                                                                                                                               |                                                                                                                                                      |                                                                                                                           |                                                                         |                              |        |

| bit 15-14                                    | 11 = Reserv<br>10 = Accepta                                                                                                  | ed<br>ance Mask 2 reg                                                                                                                            | gisters contair                                                                                                                                      | n mask                                                                                                                    |                                                                         |                              |        |

| bit 15-14                                    | 11 = Reserv<br>10 = Accept<br>01 = Accept                                                                                    | ed                                                                                                                                               | gisters contair<br>gisters contair                                                                                                                   | n mask<br>n mask                                                                                                          |                                                                         |                              |        |

| bit 15-14<br>bit 13-12                       | 11 = Reserv<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta                                                                  | red<br>ance Mask 2 reg<br>ance Mask 1 reg                                                                                                        | gisters contair<br>gisters contair<br>gisters contair                                                                                                | n mask<br>n mask<br>n mask                                                                                                | les as bits<15∷                                                         | 14>)                         |        |

|                                              | 11 = Reserv<br>10 = Accept<br>01 = Accept<br>00 = Accept<br>F14MSK<1:                                                        | red<br>ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg                                                                                     | gisters contair<br>gisters contair<br>gisters contair<br>e for Filter 14                                                                             | n mask<br>n mask<br>n mask<br>n mask<br>bits (same valu                                                                   |                                                                         |                              |        |

| bit 13-12                                    | 11 = Reserv<br>10 = Accept<br>01 = Accept<br>00 = Accept<br>F14MSK<1:<br>F13MSK<1:                                           | red<br>ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg<br><b>0&gt;:</b> Mask Sourc                                                         | gisters contair<br>gisters contair<br>gisters contair<br>gisters contair<br>e for Filter 14<br>e for Filter 13                                       | n mask<br>n mask<br>n mask<br>n mask<br>bits (same valu<br>bits (same valu                                                | ies as bits<15:                                                         | 14>)                         |        |

| bit 13-12<br>bit 11-10                       | 11 = Reserv<br>10 = Accept<br>01 = Accept<br>00 = Accept<br>F14MSK<1:<br>F13MSK<1:<br>F12MSK<1:                              | red<br>ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg<br><b>0&gt;:</b> Mask Sourc<br><b>0&gt;:</b> Mask Sourc                             | gisters contair<br>gisters contair<br>gisters contair<br>e for Filter 14<br>e for Filter 13<br>e for Filter 12                                       | n mask<br>n mask<br>n mask<br>bits (same valu<br>bits (same valu<br>bits (same valu                                       | ies as bits<15:<br>ies as bits<15:                                      | 14>)<br>14>)                 |        |

| bit 13-12<br>bit 11-10<br>bit 9-8            | 11 = Reserv<br>10 = Accept<br>01 = Accept<br>00 = Accept<br>F14MSK<1:<br>F13MSK<1:<br>F12MSK<1:                              | red<br>ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg<br><b>0&gt;:</b> Mask Sourc<br><b>0&gt;:</b> Mask Sourc<br><b>0&gt;:</b> Mask Sourc | gisters contair<br>gisters contair<br>gisters contair<br>e for Filter 14<br>e for Filter 13<br>e for Filter 12<br>e for Filter 11                    | n mask<br>n mask<br>n mask<br>bits (same valu<br>bits (same valu<br>bits (same valu<br>bits (same valu                    | ies as bits<15:<br>ies as bits<15:<br>es as bits<15:′                   | 14>)<br>14>)<br>14>)         |        |

| bit 13-12<br>bit 11-10<br>bit 9-8<br>bit 7-6 | 11 = Reserv<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta<br>F14MSK<1:<br>F13MSK<1:<br>F12MSK<1:<br>F11MSK<1:<br>F10MSK<1: | red<br>ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg<br><b>0&gt;:</b> Mask Sourc<br><b>0&gt;:</b> Mask Sourc<br><b>0&gt;:</b> Mask Sourc | gisters contair<br>gisters contair<br>gisters contair<br>e for Filter 14<br>e for Filter 13<br>e for Filter 13<br>e for Filter 11<br>e for Filter 10 | n mask<br>n mask<br>n mask<br>bits (same valu<br>bits (same valu<br>bits (same valu<br>bits (same valu<br>bits (same valu | ies as bits<15:<br>ies as bits<15:<br>es as bits<15:<br>ies as bits<15: | 14>)<br>14>)<br>14>)<br>14>) |        |

|               | 23-2: Al                                                                               |                                                | CONTROL REG                              |                     |                   |                  |                |  |  |  |

|---------------|----------------------------------------------------------------------------------------|------------------------------------------------|------------------------------------------|---------------------|-------------------|------------------|----------------|--|--|--|

| R/W-0         | R/W-                                                                                   | 0 R/W-0                                        | U-0                                      | U-0                 | R/W-0             | R/W-0            | R/W-0          |  |  |  |

| VCFG2         | VCFO                                                                                   | G1 VCFG0                                       | —                                        | _                   | CSCNA             | CHPS1            | CHPS0          |  |  |  |

| bit 15        |                                                                                        |                                                |                                          |                     |                   |                  | bit            |  |  |  |

| R-0           | R/W-                                                                                   | 0 R/W-0                                        | R/W-0                                    | R/W-0               | R/W-0             | R/W-0            | R/W-0          |  |  |  |

| BUFS          | SMPI                                                                                   |                                                | SMPI2                                    | SMPI1               | SMPI0             | BUFM             | ALTS           |  |  |  |

| bit 7         | Sivil                                                                                  |                                                |                                          |                     |                   | BOTW             | bit            |  |  |  |

| Logondi       |                                                                                        |                                                |                                          |                     |                   |                  |                |  |  |  |

| Legend:       | hit                                                                                    | M/ - Mritabla                                  | hit U                                    | - Unimplo           | monted hit read   |                  |                |  |  |  |

| R = Readable  |                                                                                        | W = Writable                                   |                                          | •                   | mented bit, read  |                  |                |  |  |  |

| -n = Value at | POR                                                                                    | '1' = Bit is set                               | t 'U                                     | )' = Bit is cle     | eared             | x = Bit is unkr  | nown           |  |  |  |

| bit 15-13     | VCFG<2                                                                                 | 2:0>: Converter Volt                           | age Reference Co                         | onfiguration        | bits              |                  |                |  |  |  |

|               | Value                                                                                  | VREFH                                          | VREFL                                    |                     |                   |                  |                |  |  |  |

|               | 000                                                                                    | Avdd                                           | Avss                                     |                     |                   |                  |                |  |  |  |

|               | 001                                                                                    | External VREF+                                 | Avss                                     |                     |                   |                  |                |  |  |  |

|               | 010                                                                                    | Avdd                                           | External VREF-                           |                     |                   |                  |                |  |  |  |

|               | 011                                                                                    | External VREF+                                 | External VREF-                           |                     |                   |                  |                |  |  |  |

|               | 1xx                                                                                    | Avdd                                           | Avss                                     |                     |                   |                  |                |  |  |  |

| bit 12-11     | Unimple                                                                                | emented: Read as '                             | ʻ0'                                      |                     |                   |                  |                |  |  |  |

| bit 10        |                                                                                        | : Input Scan Select                            |                                          |                     |                   |                  |                |  |  |  |

|               |                                                                                        | ns inputs for CH0+ of                          |                                          | IXA                 |                   |                  |                |  |  |  |

|               |                                                                                        | s not scan inputs                              | gp                                       |                     |                   |                  |                |  |  |  |

| bit 9-8       | CHPS<1:0>: Channel Select bits                                                         |                                                |                                          |                     |                   |                  |                |  |  |  |

|               | <u>In 12-bit</u>                                                                       | mode (AD21B = 1)                               | , the CHPS<1:0>                          | <u>bits are Uni</u> | mplemented an     | d are Read as    | <u>'0':</u>    |  |  |  |

|               |                                                                                        | nverts CH0, CH1, C                             |                                          |                     |                   |                  |                |  |  |  |

|               |                                                                                        | nverts CH0 and CH                              | 1                                        |                     |                   |                  |                |  |  |  |

| L:1 7         |                                                                                        | nverts CH0                                     | (                                        |                     |                   |                  |                |  |  |  |

| bit 7         |                                                                                        | Buffer Fill Status bit                         |                                          | -                   | a waar annligeti  |                  | aa data in ti  |  |  |  |

|               |                                                                                        | C is currently filling t<br>half of the buffer | ne second half of i                      | ne buller; tr       | ie user applicati | ion should acce  | ess data in ti |  |  |  |

|               |                                                                                        | C is currently filling                         | the first half of the                    | e buffer; the       | e user applicatio | on should acce   | ss data in t   |  |  |  |

|               |                                                                                        | ond half of the buffe                          |                                          | ,                   |                   |                  |                |  |  |  |

| bit 6-2       | SMPI<4                                                                                 | :0>: Increment Rate                            | e bits                                   |                     |                   |                  |                |  |  |  |

|               | When Al                                                                                | DDMAEN = 0:                                    |                                          |                     |                   |                  |                |  |  |  |

|               | x1111 = Generates interrupt after completion of every 16th sample/conversion operation |                                                |                                          |                     |                   |                  |                |  |  |  |