Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 70 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                  |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 256KB (85.5K x 24)                                                             |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 6x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                 |

| Supplier Device Package    | 28-SOIC                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep256mc202-i-so |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 1.0   | Device Overview                                                                                    |     |

|-------|----------------------------------------------------------------------------------------------------|-----|

| 2.0   | Guidelines for Getting Started with 16-bit Digital Signal Controllers and Microcontrollers         | 29  |

| 3.0   | CPU                                                                                                | 35  |

| 4.0   | Memory Organization                                                                                | 45  |

| 5.0   | Flash Program Memory                                                                               | 119 |

| 6.0   | Resets                                                                                             |     |

| 7.0   | Interrupt Controller                                                                               | 127 |

| 8.0   | Direct Memory Access (DMA)                                                                         | 139 |

| 9.0   | Oscillator Configuration                                                                           |     |

| 10.0  | Power-Saving Features                                                                              | 163 |

| 11.0  | I/O Ports                                                                                          | 173 |

| 12.0  | Timer1                                                                                             | 203 |

| 13.0  | Timer2/3 and Timer4/5                                                                              | 207 |

| 14.0  | Input Capture                                                                                      | 213 |

|       | Output Compare                                                                                     |     |

|       | High-Speed PWM Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)                     |     |

|       | Quadrature Encoder Interface (QEI) Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only) |     |

|       | Serial Peripheral Interface (SPI)                                                                  |     |

|       | Inter-Integrated Circuit™ (I <sup>2</sup> C™)                                                      |     |

|       | Universal Asynchronous Receiver Transmitter (UART)                                                 |     |

|       | Enhanced CAN (ECAN™) Module (dsPIC33EPXXXGP/MC50X Devices Only)                                    |     |

|       | Charge Time Measurement Unit (CTMU)                                                                |     |

|       | 10-Bit/12-Bit Analog-to-Digital Converter (ADC)                                                    |     |

|       | Peripheral Trigger Generator (PTG) Module                                                          |     |

| 25.0  | Op Amp/Comparator Module                                                                           |     |

|       | Programmable Cyclic Redundancy Check (CRC) Generator                                               |     |

| 27.0  |                                                                                                    |     |

|       |                                                                                                    |     |

| 29.0  | Development Support                                                                                |     |

|       | Electrical Characteristics                                                                         |     |

|       | High-Temperature Electrical Characteristics                                                        |     |

|       | DC and AC Device Characteristics Graphs                                                            |     |

|       | Packaging Information                                                                              |     |

|       | ndix A: Revision History                                                                           |     |

|       | (                                                                                                  |     |

|       | Vicrochip Web Site                                                                                 |     |

|       | omer Change Notification Service                                                                   |     |

|       | omer Support                                                                                       |     |

| Produ | uct Identification System                                                                          | 527 |

| Pin Name <sup>(4)</sup>       | Pin<br>Type | Buffer<br>Type | PPS     | Description                                                                                     |  |  |  |

|-------------------------------|-------------|----------------|---------|-------------------------------------------------------------------------------------------------|--|--|--|

| C1IN1-                        | I           | Analog         | No      | Op Amp/Comparator 1 Negative Input 1.                                                           |  |  |  |

| C1IN2-                        | I           | Analog         | No      | Comparator 1 Negative Input 2.                                                                  |  |  |  |

| C1IN1+                        | I           | Analog         | No      | Op Amp/Comparator 1 Positive Input 1.                                                           |  |  |  |

| OA1OUT                        | 0           | Analog         | No      | Op Amp 1 output.                                                                                |  |  |  |

| C1OUT                         | 0           | —              | Yes     | Comparator 1 output.                                                                            |  |  |  |

| C2IN1-                        | I           | Analog         | No      | Op Amp/Comparator 2 Negative Input 1.                                                           |  |  |  |

| C2IN2-                        | I           | Analog         | No      | Comparator 2 Negative Input 2.                                                                  |  |  |  |

| C2IN1+                        | I           | Analog         | No      | Op Amp/Comparator 2 Positive Input 1.                                                           |  |  |  |

| OA2OUT                        | 0           | Analog         | No      | Op Amp 2 output.                                                                                |  |  |  |

| C2OUT                         | 0           |                | Yes     | Comparator 2 output.                                                                            |  |  |  |

| C3IN1-                        | I           | Analog         | No      | Op Amp/Comparator 3 Negative Input 1.                                                           |  |  |  |

| C3IN2-                        | I           | Analog         | No      | Comparator 3 Negative Input 2.                                                                  |  |  |  |

| C3IN1+                        | I           | Analog         | No      | Op Amp/Comparator 3 Positive Input 1.                                                           |  |  |  |

| OA3OUT                        | 0           | Analog         | No      | Op Amp 3 output.                                                                                |  |  |  |

| C3OUT                         | 0           |                | Yes     | Comparator 3 output.                                                                            |  |  |  |

| C4IN1-                        | I.          | Analog         | No      | Comparator 4 Negative Input 1.                                                                  |  |  |  |

| C4IN1+                        | I.          | Analog         | No      | Comparator 4 Positive Input 1.                                                                  |  |  |  |

| C4OUT                         | 0           |                | Yes     | Comparator 4 output.                                                                            |  |  |  |

| CVREF10                       | 0           | Analog         | No      | Op amp/comparator voltage reference output.                                                     |  |  |  |

| CVREF20                       | 0           | Analog         | No      | Op amp/comparator voltage reference divided by 2 output.                                        |  |  |  |

| PGED1                         | I/O         | ST             | No      | Data I/O pin for Programming/Debugging Communication Channel 1.                                 |  |  |  |

| PGEC1                         | I           | ST             | No      | Clock input pin for Programming/Debugging Communication Channel 1.                              |  |  |  |

| PGED2                         | I/O         | ST             | No      | Data I/O pin for Programming/Debugging Communication Channel 2.                                 |  |  |  |

| PGEC2                         | I           | ST             | No      | Clock input pin for Programming/Debugging Communication Channel 2.                              |  |  |  |

| PGED3                         | I/O         | ST             | No      | Data I/O pin for Programming/Debugging Communication Channel 3.                                 |  |  |  |

| PGEC3                         | I           | ST             | No      | Clock input pin for Programming/Debugging Communication Channel 3.                              |  |  |  |

| MCLR                          | I/P         | ST             | No      | Master Clear (Reset) input. This pin is an active-low Reset to the device.                      |  |  |  |

| AVDD                          | Р           | Р              | No      | Positive supply for analog modules. This pin must be connected at all times.                    |  |  |  |

| AVss                          | Р           | Р              | No      | Ground reference for analog modules. This pin must be connected at all times.                   |  |  |  |

| Vdd                           | Р           |                | No      | Positive supply for peripheral logic and I/O pins.                                              |  |  |  |

| VCAP                          | Р           |                | No      | CPU logic filter capacitor connection.                                                          |  |  |  |

| Vss                           | Р           |                | No      | Ground reference for logic and I/O pins.                                                        |  |  |  |

| VREF+                         | 1           | Analog         | No      | Analog voltage reference (high) input.                                                          |  |  |  |

| VREF-                         | Ι           | Analog         | No      | Analog voltage reference (low) input.                                                           |  |  |  |

| Legend: CMOS = C<br>ST = Schn | nitt Trigg  | jer input v    | with CI | or output     Analog = Analog input     P = Power       MOS levels     O = Output     I = Input |  |  |  |

Note 1: This pin is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This pin is available on dsPIC33EPXXXGP/MC50X devices only.

PPS = Peripheral Pin Select

3: This is the default Fault on Reset for dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices. See Section 16.0 "High-Speed PWM Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)" for more information.

TTL = TTL input buffer

4: Not all pins are available in all packages variants. See the "Pin Diagrams" section for pin availability.

**5:** There is an internal pull-up resistor connected to the TMS pin when the JTAG interface is active. See the JTAGEN bit field in Table 27-2.

### 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to 3 MHz <  $F_{IN}$  < 5.5 MHz to comply with device PLL start-up conditions. This means that if the external oscillator frequency is outside this range, the application must start-up in the FRC mode first. The default PLL settings after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV and PLLFBD, to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source. Note that clock switching must be enabled in the device Configuration Word.

## 2.8 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state.

Alternatively, connect a 1k to 10k resistor between Vss and unused pins, and drive the output to logic low.

## 2.9 Application Examples

- · Induction heating

- Uninterruptable Power Supplies (UPS)

- DC/AC inverters

- · Compressor motor control

- · Washing machine 3-phase motor control

- BLDC motor control

- · Automotive HVAC, cooling fans, fuel pumps

- Stepper motor control

- · Audio and fluid sensor monitoring

- · Camera lens focus and stability control

- Speech (playback, hands-free kits, answering machines, VoIP)

- Consumer audio

- Industrial and building control (security systems and access control)

- · Barcode reading

- Networking: LAN switches, gateways

- Data storage device management

- · Smart cards and smart card readers

Examples of typical application connections are shown in Figure 2-4 through Figure 2-8.

#### FIGURE 2-4: BOOST CONVERTER IMPLEMENTATION

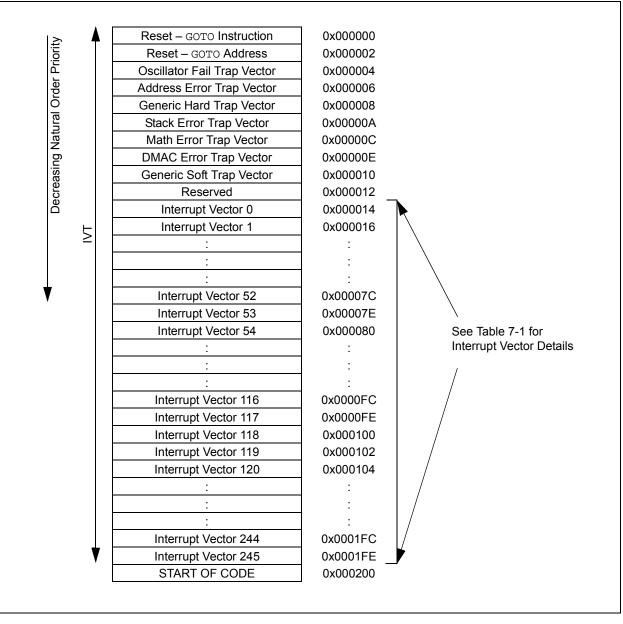

#### FIGURE 7-1: dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X INTERRUPT VECTOR TABLE

| R/W-0                                                 | R/W-0                                                                                                                                                          | R/W-0                 | R/W-0                             | R/W-0                   | R/W-0                 | R/W-0                | R/W-0                |

|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------------------|-------------------------|-----------------------|----------------------|----------------------|

| NSTDIS                                                | OVAERR <sup>(1)</sup>                                                                                                                                          | OVBERR <sup>(1)</sup> | COVAERR <sup>(1)</sup>            | COVBERR <sup>(1)</sup>  | OVATE <sup>(1)</sup>  | OVBTE <sup>(1)</sup> | COVTE <sup>(1)</sup> |

| pit 15                                                |                                                                                                                                                                |                       |                                   |                         |                       |                      | bit 8                |

|                                                       |                                                                                                                                                                |                       |                                   |                         |                       |                      |                      |

| R/W-0                                                 | R/W-0                                                                                                                                                          | R/W-0                 | R/W-0                             | R/W-0                   | R/W-0                 | R/W-0                | U-0                  |

| SFTACERR <sup>(1</sup>                                | ) DIV0ERR                                                                                                                                                      | DMACERR               | MATHERR                           | ADDRERR                 | STKERR                | OSCFAIL              | —                    |

| pit 7                                                 |                                                                                                                                                                |                       |                                   |                         |                       |                      | bit 0                |

|                                                       |                                                                                                                                                                |                       |                                   |                         |                       |                      |                      |

| _egend:                                               |                                                                                                                                                                |                       |                                   |                         |                       |                      |                      |

| R = Readable                                          |                                                                                                                                                                | W = Writable          |                                   | U = Unimpleme           |                       |                      |                      |

| n = Value at                                          | POR                                                                                                                                                            | '1' = Bit is set      |                                   | '0' = Bit is clear      | ed                    | x = Bit is unk       | nown                 |

| bit 15                                                | NSTDIS: Inte                                                                                                                                                   | errupt Nesting        | Disable hit                       |                         |                       |                      |                      |

|                                                       |                                                                                                                                                                | nesting is disa       |                                   |                         |                       |                      |                      |

|                                                       | •                                                                                                                                                              | nesting is ena        |                                   |                         |                       |                      |                      |

| pit 14                                                | -                                                                                                                                                              | -                     | Overflow Trap F                   | lag bit <sup>(1)</sup>  |                       |                      |                      |

|                                                       |                                                                                                                                                                |                       | erflow of Accur                   |                         |                       |                      |                      |

|                                                       | =                                                                                                                                                              |                       | overflow of A                     |                         |                       |                      |                      |

| pit 13                                                |                                                                                                                                                                |                       | Overflow Trap F                   | •                       |                       |                      |                      |

|                                                       | <ul> <li>1 = Trap was caused by overflow of Accumulator B</li> <li>0 = Trap was not caused by overflow of Accumulator B</li> </ul>                             |                       |                                   |                         |                       |                      |                      |

| pit 12                                                | -                                                                                                                                                              |                       |                                   | Overflow Trap Fla       | ag bit <sup>(1)</sup> |                      |                      |

|                                                       | 1 = Trap was                                                                                                                                                   | caused by ca          | tastrophic over                   | flow of Accumula        | ator A                |                      |                      |

| pit 11                                                |                                                                                                                                                                |                       |                                   | Overflow Trap Fla       |                       |                      |                      |

|                                                       |                                                                                                                                                                |                       | •                                 | flow of Accumula        | •                     |                      |                      |

|                                                       | =                                                                                                                                                              |                       | -                                 | overflow of Accur       | nulator B             |                      |                      |

| pit 10                                                |                                                                                                                                                                |                       | erflow Trap Ena                   | able bit <sup>(1)</sup> |                       |                      |                      |

|                                                       | 1 = Trap ove<br>0 = Trap is d                                                                                                                                  | rflow of Accum        | ulator A                          |                         |                       |                      |                      |

| pit 9                                                 | OVBTE: Acc                                                                                                                                                     | umulator B Ov         | erflow Trap En                    | able bit <sup>(1)</sup> |                       |                      |                      |

|                                                       | 1 = Trap ove<br>0 = Trap is d                                                                                                                                  | rflow of Accum        | ulator B                          |                         |                       |                      |                      |

| oit 8                                                 | COVTE: Cat                                                                                                                                                     | astrophic Over        | flow Trap Enat                    | ole bit <sup>(1)</sup>  |                       |                      |                      |

|                                                       | <ul> <li>1 = Trap on catastrophic overflow of Accumulator A or B is enabled</li> <li>0 = Trap is disabled</li> </ul>                                           |                       |                                   |                         |                       |                      |                      |

| oit 7                                                 | SFTACERR:                                                                                                                                                      | Shift Accumul         | ator Error Statu                  | us bit <sup>(1)</sup>   |                       |                      |                      |

|                                                       | <ul> <li>1 = Math error trap was caused by an invalid accumulator shift</li> <li>0 = Math error trap was not caused by an invalid accumulator shift</li> </ul> |                       |                                   |                         |                       |                      |                      |

| bit 6 <b>DIV0ERR:</b> Divide-by-Zero Error Status bit |                                                                                                                                                                |                       |                                   |                         |                       |                      |                      |

|                                                       |                                                                                                                                                                |                       | used by a divide<br>caused by a d |                         |                       |                      |                      |

|                                                       | DMACERR:                                                                                                                                                       |                       |                                   | -                       |                       |                      |                      |

| oit 5                                                 |                                                                                                                                                                |                       |                                   |                         |                       |                      |                      |

#### REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1

#### 10.3 Doze Mode

The preferred strategies for reducing power consumption are changing clock speed and invoking one of the powersaving modes. In some circumstances, this cannot be practical. For example, it may be necessary for an application to maintain uninterrupted synchronous communication, even while it is doing nothing else. Reducing system clock speed can introduce communication errors, while using a power-saving mode can stop communications completely.

Doze mode is a simple and effective alternative method to reduce power consumption while the device is still executing code. In this mode, the system clock continues to operate from the same source and at the same speed. Peripheral modules continue to be clocked at the same speed, while the CPU clock speed is reduced. Synchronization between the two clock domains is maintained, allowing the peripherals to access the SFRs while the CPU executes code at a slower rate.

Doze mode is enabled by setting the DOZEN bit (CLKDIV<11>). The ratio between peripheral and core clock speed is determined by the DOZE<2:0> bits (CLKDIV<14:12>). There are eight possible configurations, from 1:1 to 1:128, with 1:1 being the default setting.

Programs can use Doze mode to selectively reduce power consumption in event-driven applications. This allows clock-sensitive functions, such as synchronous communications, to continue without interruption while the CPU Idles, waiting for something to invoke an interrupt routine. An automatic return to full-speed CPU operation on interrupts can be enabled by setting the ROI bit (CLKDIV<15>). By default, interrupt events have no effect on Doze mode operation.

For example, suppose the device is operating at 20 MIPS and the ECAN<sup>™</sup> module has been configured for 500 kbps, based on this device operating speed. If the device is placed in Doze mode with a clock frequency ratio of 1:4, the ECAN module continues to communicate at the required bit rate of 500 kbps, but the CPU now starts executing instructions at a frequency of 5 MIPS.

#### 10.4 Peripheral Module Disable

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled using the appropriate PMD control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers do not have effect and read values are invalid.

A peripheral module is enabled only if both the associated bit in the PMD register is cleared and the peripheral is supported by the specific dsPIC<sup>®</sup> DSC variant. If the peripheral is present in the device, it is enabled in the PMD register by default.

| Note: | If a PMD bit is set, the corresponding        |

|-------|-----------------------------------------------|

|       | module is disabled after a delay of one       |

|       | instruction cycle. Similarly, if a PMD bit is |

|       | cleared, the corresponding module is          |

|       | enabled after a delay of one instruction      |

|       | cycle (assuming the module control regis-     |

|       | ters are already configured to enable         |

|       | module operation).                            |

### 10.5 Power-Saving Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

#### 10.5.1 KEY RESOURCES

- "Watchdog Timer and Power-Saving Modes" (DS70615) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

| Peripheral Pin<br>Select Input<br>Register Value | Input/<br>Output | Pin Assignment | Peripheral Pin<br>Select Input<br>Register Value | Input/<br>Output | Pin Assignment |

|--------------------------------------------------|------------------|----------------|--------------------------------------------------|------------------|----------------|

| 010 1000                                         | I/O              | RP40           | 101 0101                                         | —                | _              |

| 010 1001                                         | I/O              | RP41           | 101 0110                                         | —                | —              |

| 010 1010                                         | I/O              | RP42           | 101 0111                                         | —                | —              |

| 010 1011                                         | I/O              | RP43           | 101 1000                                         |                  | —              |

| 010 1100                                         | I                | RPI44          | 101 1001                                         |                  | —              |

| 101 1010                                         | —                | _              | 110 1101                                         | —                | _              |

| 101 1011                                         | —                | —              | 110 1110                                         |                  | —              |

| 101 1100                                         | —                | —              | 110 1111                                         |                  | —              |

| 101 1101                                         | —                | _              | 111 0000                                         | —                | _              |

| 101 1110                                         | 1                | RPI94          | 111 0001                                         | —                | _              |

| 101 1111                                         | I                | RP195          | 111 0010                                         |                  | —              |

| 110 0000                                         | I                | RPI96          | 111 0011                                         | —                | —              |

| 110 0001                                         | I/O              | RP97           | 111 0100                                         |                  | —              |

| 110 0010                                         | —                | —              | 111 0101                                         |                  | —              |

| 110 0011                                         | —                | —              | 111 0110                                         | I/O              | RP118          |

| 110 0100                                         | —                | —              | 111 0111                                         | Ι                | RPI119         |

| 110 0101                                         | —                | —              | 111 1000                                         | I/O              | RP120          |

| 110 0110                                         | _                |                | 111 1001                                         | Ι                | RPI121         |

| 110 0111                                         |                  |                | 111 1010                                         | —                |                |

| 110 1000                                         | —                | _              | 111 1011                                         | —                | _              |

| 110 1001                                         | —                |                | 111 1100                                         | —                |                |

| 110 1010                                         |                  |                | 111 1101                                         | —                |                |

| 110 1011                                         | —                | _              | 111 1110                                         | —                |                |

| 110 1100                                         | —                | _              | 111 1111                                         | _                |                |

#### TABLE 11-2: INPUT PIN SELECTION FOR SELECTABLE INPUT SOURCES (CONTINUED)

Legend: Shaded rows indicate PPS Input register values that are unimplemented.

Note 1: See Section 11.4.4.1 "Virtual Connections" for more information on selecting this pin assignment.

2: These inputs are available on dsPIC33EPXXXGP/MC50X devices only.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0                                                                  | U-0                                                                        | R/W-0           | R/W-0                                   | R/W-0 | R/W-0  | R/W-0    | R/W-0 |

|----------------------------------------------------------------------|----------------------------------------------------------------------------|-----------------|-----------------------------------------|-------|--------|----------|-------|

| _                                                                    | —                                                                          |                 |                                         | RP39  | R<5:0> |          |       |

| bit 15                                                               |                                                                            |                 |                                         |       |        |          | bit 8 |

|                                                                      |                                                                            |                 |                                         |       |        |          |       |

| U-0                                                                  | U-0                                                                        | R/W-0           | R/W-0                                   | R/W-0 | R/W-0  | R/W-0    | R/W-0 |

| —                                                                    | —                                                                          |                 |                                         | RP38  | R<5:0> |          |       |

| bit 7                                                                |                                                                            |                 |                                         |       |        |          | bit 0 |

|                                                                      |                                                                            |                 |                                         |       |        |          |       |

| Legend:                                                              |                                                                            |                 |                                         |       |        |          |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                                                                            |                 |                                         |       |        | d as '0' |       |

| -n = Value at POR '1' = Bit is set                                   |                                                                            |                 | '0' = Bit is cleared x = Bit is unknown |       |        |          |       |

|                                                                      |                                                                            |                 |                                         |       |        |          |       |

| bit 15-14                                                            | Unimplemer                                                                 | nted: Read as ' | 0'                                      |       |        |          |       |

| bit 13-8                                                             | RP39R<5:0>: Peripheral Output Function is Assigned to RP39 Output Pin bits |                 |                                         |       |        |          |       |

#### REGISTER 11-20: RPOR2: PERIPHERAL PIN SELECT OUTPUT REGISTER 2

|         | (see Table 11-3 for peripheral function numbers)                           |

|---------|----------------------------------------------------------------------------|

| bit 7-6 | Unimplemented: Read as '0'                                                 |

| bit 5-0 | RP38R<5:0>: Peripheral Output Function is Assigned to RP38 Output Pin bits |

|         | (see Table 11-3 for peripheral function numbers)                           |

#### REGISTER 11-21: RPOR3: PERIPHERAL PIN SELECT OUTPUT REGISTER 3

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| —      | —   |       |       | RP41  | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|--------|-------|-------|

| —     | —   |       |       | RP40  | R<5:0> |       |       |

| bit 7 |     |       |       |       |        |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

- bit 13-8 **RP41R<5:0>:** Peripheral Output Function is Assigned to RP41 Output Pin bits (see Table 11-3 for peripheral function numbers)

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 **RP40R<5:0>:** Peripheral Output Function is Assigned to RP40 Output Pin bits (see Table 11-3 for peripheral function numbers)

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0             | U-0                                                                                                                                      | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------|-------------------|------------------|-----------------|-------|

| —               | —                                                                                                                                        |                  |       | RP57              | R<5:0>           |                 |       |

| bit 15          |                                                                                                                                          |                  |       |                   |                  |                 | bit 8 |

|                 |                                                                                                                                          |                  |       |                   |                  |                 |       |

| U-0             | U-0                                                                                                                                      | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

| _               | —                                                                                                                                        |                  |       | RP56              | R<5:0>           |                 |       |

| bit 7           |                                                                                                                                          |                  |       |                   |                  |                 | bit 0 |

|                 |                                                                                                                                          |                  |       |                   |                  |                 |       |

| Legend:         |                                                                                                                                          |                  |       |                   |                  |                 |       |

| R = Readable I  | bit                                                                                                                                      | W = Writable     | bit   | U = Unimplen      | nented bit, read | d as '0'        |       |

| -n = Value at P | OR                                                                                                                                       | '1' = Bit is set | :     | '0' = Bit is clea | ared             | x = Bit is unkr | iown  |

|                 |                                                                                                                                          |                  |       |                   |                  |                 |       |

| bit 15-14       | Unimplemen                                                                                                                               | ted: Read as '   | 0'    |                   |                  |                 |       |

| bit 13-8        | <b>RP57R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP57 Output Pin bits (see Table 11-3 for peripheral function numbers) |                  |       |                   |                  |                 |       |

| bit 7-6         | Unimplemented: Read as '0'                                                                                                               |                  |       |                   |                  |                 |       |

#### REGISTER 11-24: RPOR6: PERIPHERAL PIN SELECT OUTPUT REGISTER 6

| (see Table 11-3 for peripheral function numbers) |

|--------------------------------------------------|

|                                                  |

#### REGISTER 11-25: RPOR7: PERIPHERAL PIN SELECT OUTPUT REGISTER 7

| U-0    | U-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|--------|-----|-------|------------|-------|-------|-------|-------|--|--|

| —      | —   |       | RP97R<5:0> |       |       |       |       |  |  |

| bit 15 |     |       |            |       |       |       | bit 8 |  |  |

RP56R<5:0>: Peripheral Output Function is Assigned to RP56 Output Pin bits

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| —     | —   | —   |     | —   | —   |     | —     |

| bit 7 |     |     |     |     |     |     | bit 0 |

| Legend:           |                  |                             |                                    |  |  |  |

|-------------------|------------------|-----------------------------|------------------------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | J = Unimplemented bit, read as '0' |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown                 |  |  |  |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP97R<5:0>:** Peripheral Output Function is Assigned to RP97 Output Pin bits (see Table 11-3 for peripheral function numbers)

bit 7-0 Unimplemented: Read as '0'

bit 5-0

# 15.2 Output Compare Control Registers

# REGISTER 15-1: OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1

| U-0           | U-0                          | R/W-0                                  | R/W-0             | R/W-0             | R/W-0                  | U-0              | R/W-0         |

|---------------|------------------------------|----------------------------------------|-------------------|-------------------|------------------------|------------------|---------------|

|               | 0-0                          | OCSIDL                                 | OCTSEL2           | OCTSEL1           | OCTSEL0                |                  | ENFLTB        |

| <br>bit 15    |                              | COOIDE                                 |                   | OUTOLLI           | OUTOLLU                |                  | bit 8         |

| Sit 10        |                              |                                        |                   |                   |                        |                  | bit 0         |

| R/W-0         | U-0                          | R/W-0, HSC                             | R/W-0, HSC        | R/W-0             | R/W-0                  | R/W-0            | R/W-0         |

| ENFLT         |                              | OCFLTB                                 | OCFLTA            | TRIGMODE          | OCM2                   | OCM1             | OCM0          |

| bit 7         |                              |                                        |                   |                   |                        |                  | bit 0         |

|               |                              |                                        |                   |                   |                        |                  |               |

| Legend:       |                              | HSC = Hardw                            | are Settable/Cl   | earable bit       |                        |                  |               |

| R = Read      | able bit                     | W = Writable I                         | oit               | U = Unimplem      | nented bit, read       | as '0'           |               |

| -n = Value    | e at POR                     | '1' = Bit is set                       |                   | '0' = Bit is clea | ared                   | x = Bit is unkn  | own           |

|               |                              |                                        |                   |                   |                        |                  |               |

| bit 15-14     | Unimplemen                   | ted: Read as '0                        | )'                |                   |                        |                  |               |

| bit 13        | OCSIDL: Out                  | tput Compare x                         | Stop in Idle Mo   | de Control bit    |                        |                  |               |

|               |                              | ompare x Halts                         |                   |                   |                        |                  |               |

|               | •                            | compare x conti                        | •                 |                   | ode                    |                  |               |

| bit 12-10     |                              | )>: Output Com                         | pare x Clock S    | elect bits        |                        |                  |               |

|               | 111 = Periph<br>110 = Reserv | eral clock (FP)                        |                   |                   |                        |                  |               |

|               | 101 = PTGO                   |                                        |                   |                   |                        |                  |               |

|               |                              | is the clock so                        |                   |                   | hronous clock          | is supported)    |               |

|               |                              | is the clock so                        |                   |                   |                        |                  |               |

|               |                              | ( is the clock so<br>( is the clock so |                   |                   |                        |                  |               |

|               |                              | is the clock so                        |                   |                   |                        |                  |               |

| bit 9         | Unimplemen                   | ted: Read as '0                        | )'                |                   |                        |                  |               |

| bit 8         | ENFLTB: Fau                  | ult B Input Enab                       | le bit            |                   |                        |                  |               |

|               |                              | compare Fault B<br>compare Fault B     |                   |                   |                        |                  |               |

| bit 7         | -                            | ult A Input Enab                       |                   |                   |                        |                  |               |

|               | 1 = Output C                 | ompare Fault A<br>compare Fault A      | input (OCFA)      |                   |                        |                  |               |

| bit 6         | •                            | ted: Read as '0                        | • • •             |                   |                        |                  |               |

| bit 5         | OCFLTB: PW                   | M Fault B Con                          | dition Status bit |                   |                        |                  |               |

|               |                              | ult B condition of Fault B condition   |                   |                   |                        |                  |               |

| bit 4         |                              | /M Fault A Cond                        | •                 |                   |                        |                  |               |

|               |                              | ult A condition o                      |                   |                   |                        |                  |               |

| Note 1:       | OCxR and OCxF                | 29 are double h                        | uffered in D\\//  | / mode only       |                        |                  |               |

| Note 1.<br>2: | Each Output Cor              |                                        |                   | -                 | irce. See <b>Secti</b> | on 24.0 "Perin   | heral Trigger |

| 2.            | Generator (PTG               |                                        |                   |                   |                        | 5.1 2 7.0 1 611p |               |

|               | PTGO4 = OC1                  | -                                      |                   |                   |                        |                  |               |

|               | PTGO5 = OC2                  |                                        |                   |                   |                        |                  |               |

|               | PTGO6 = OC3<br>PTGO7 = OC4   |                                        |                   |                   |                        |                  |               |

|               |                              |                                        |                   |                   |                        |                  |               |

#### REGISTER 16-15: FCLCONx: PWMx FAULT CURRENT-LIMIT CONTROL REGISTER<sup>(1)</sup>

- bit 7-3 FLTSRC<4:0>: Fault Control Signal Source Select for PWM Generator # bits 11111 = Fault 32 (default) 11110 = Reserved . . 01100 = Reserved 01011 = Comparator 4 01010 = Op Amp/Comparator 3

- 01001 = Op Amp/Comparator 2

- 01000 = Op Amp/Comparator 1

- 00111 = Reserved

- 00110 = Reserved

- 00101 = Reserved

- 00100 = Reserved

- 00011 = Fault 4

- 00010 = Fault 3

- 00001 = Fault 2 00000 = Fault 1

- bit 2 ELTROL Fault Delarity for DWM Concrete

# bit 2 **FLTPOL:** Fault Polarity for PWM Generator # bit<sup>(2)</sup>

- 1 = The selected Fault source is active-low

- 0 = The selected Fault source is active-high

- bit 1-0 FLTMOD<1:0>: Fault Mode for PWM Generator # bits

- 11 = Fault input is disabled

- 10 = Reserved

- 01 = The selected Fault source forces PWMxH, PWMxL pins to FLTDAT values (cycle)

- 00 = The selected Fault source forces PWMxH, PWMxL pins to FLTDAT values (latched condition)

- **Note 1:** If the PWMLOCK Configuration bit (FOSCSEL<6>) is a '1', the IOCONx register can only be written after the unlock sequence has been executed.

- **2:** These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

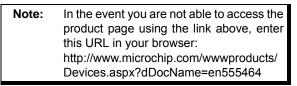

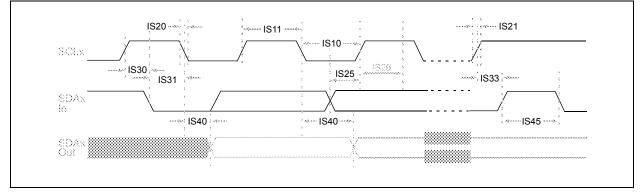

FIGURE 19-1: I2Cx BLOCK DIAGRAM (X = 1 OR 2)

# 20.3 UARTx Control Registers

#### REGISTER 20-1: UXMODE: UARTX MODE REGISTER

| R/W-0                | U-0                                           | R/W-0                                                                                          | R/W-0                                                    | R/W-0                              | U-0                        | R/W-0                   | R/W-0                     |

|----------------------|-----------------------------------------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------|------------------------------------|----------------------------|-------------------------|---------------------------|

| UARTEN <sup>(1</sup> | ) _                                           | USIDL                                                                                          | IREN <sup>(2)</sup>                                      | RTSMD                              |                            | UEN1                    | UEN0                      |

| bit 15               |                                               |                                                                                                |                                                          |                                    |                            |                         | bit                       |

|                      |                                               |                                                                                                |                                                          |                                    | <b>D</b> 444 A             |                         |                           |

| R/W-0, HC            |                                               | R/W-0, HC                                                                                      | R/W-0                                                    | R/W-0                              | R/W-0                      | R/W-0                   | R/W-0                     |

| WAKE                 | LPBACK                                        | ABAUD                                                                                          | URXINV                                                   | BRGH                               | PDSEL1                     | PDSEL0                  | STSEL                     |

| bit 7                |                                               |                                                                                                |                                                          |                                    |                            |                         | bit                       |

| Legend:              |                                               | HC = Hardwar                                                                                   | e Clearable b                                            | it                                 |                            |                         |                           |

| R = Readal           | ole bit                                       | W = Writable b                                                                                 | it                                                       | U = Unimplem                       | nented bit, read           | as '0'                  |                           |

| -n = Value a         | at POR                                        | '1' = Bit is set                                                                               |                                                          | '0' = Bit is clea                  |                            | x = Bit is unkn         | iown                      |

| bit 15               | 1 = UARTx is                                  | ARTx Enable bit<br>s enabled; all UA<br>s disabled; all UA                                     | ARTx pins are                                            |                                    |                            |                         |                           |

| bit 14               | Unimplemen                                    | ted: Read as '0                                                                                | ,                                                        |                                    |                            |                         |                           |

| bit 13               | USIDL: UAR                                    | Tx Stop in Idle M                                                                              | lode bit                                                 |                                    |                            |                         |                           |

|                      |                                               | nues module opera                                                                              |                                                          |                                    | le mode                    |                         |                           |

| bit 12               | 1 = IrDA end                                  | Encoder and De<br>oder and decod<br>oder and decod                                             | er are enable                                            | d                                  |                            |                         |                           |

| bit 11               | $1 = \overline{\text{UxRTS}} p$               | le Selection for<br>bin is in Simplex<br>bin is in Flow Co                                     | mode                                                     | t                                  |                            |                         |                           |

| bit 10               | Unimplemen                                    | ted: Read as '0                                                                                | ,                                                        |                                    |                            |                         |                           |

| bit 9-8              | 11 = UxTX, U<br>10 = UxTX, U<br>01 = UxTX, U  | JARTx Pin Enab<br>JxRX and BCLK<br>JxRX, UxCTS ar<br>JxRX and UxRT<br>nd UxRX pins a<br>atches | x p <u>ins are</u> ena<br>nd UxRTS pin<br>S pins are ena | s are enabled a<br>abled and used; | nd used <sup>(4)</sup><br> | controlled by PC        | ORT latches <sup>(4</sup> |

| bit 7                | WAKE: Wake                                    | e-up on Start bit                                                                              | Detect During                                            | Sleep Mode E                       | nable bit                  |                         |                           |

|                      | in hardw                                      | continues to sam<br>are on the follow<br>-up is enabled                                        |                                                          |                                    | generated on t             | the falling edge        | ; bit is cleare           |

| bit 6                | LPBACK: UA                                    | ARTx Loopback                                                                                  | Mode Select I                                            | bit                                |                            |                         |                           |

|                      |                                               | Loopback mode<br>k mode is disabl                                                              |                                                          |                                    |                            |                         |                           |

| e                    | Refer to the " <b>UAI</b><br>enabling the UAF | RTx module for re                                                                              | ceive or trans                                           | mit operation.                     | -                          | <i>ce Manual"</i> for i | nformation or             |

| 2:                   | This feature is or                            | nly available for                                                                              | the 16x BRG                                              | mode (BRGH =                       | 0).                        |                         |                           |

|                      | This feature is or                            | -                                                                                              | =                                                        | -                                  |                            |                         |                           |

| 4                    | This fasture is ar                            | ly available on (                                                                              | 24 nin dovice                                            | -                                  |                            |                         |                           |

4: This feature is only available on 64-pin devices.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| Legend:<br>R = Readable | bit   | C = Writable b<br>W = Writable |      |        | n to clear the bit<br>mented bit, read |       |       |

|-------------------------|-------|--------------------------------|------|--------|----------------------------------------|-------|-------|

| <b></b>                 |       |                                |      |        |                                        |       |       |

| bit 7                   |       |                                |      |        |                                        |       | bit 0 |

| IVRIF                   | WAKIF | ERRIF                          | _    | FIFOIF | RBOVIF                                 | RBIF  | TBIF  |

| R/C-0                   | R/C-0 | R/C-0                          | U-0  | R/C-0  | R/C-0                                  | R/C-0 | R/C-0 |

|                         |       |                                |      |        |                                        |       |       |

| bit 15                  | •     |                                |      |        |                                        |       | bit 8 |

| _                       | —     | ТХВО                           | TXBP | RXBP   | TXWAR                                  | RXWAR | EWARN |

| U-0                     | U-0   | R-0                            | R-0  | R-0    | R-0                                    | R-0   | R-0   |

'0' = Bit is cleared

x = Bit is unknown

#### REGISTER 21-6: CxINTF: ECANx INTERRUPT FLAG REGISTER

'1' = Bit is set

| bit 15-14 | Unimplemented: Read as '0'                                                                             |

|-----------|--------------------------------------------------------------------------------------------------------|

| bit 13    | <b>TXBO:</b> Transmitter in Error State Bus Off bit                                                    |

|           | 1 = Transmitter is in Bus Off state                                                                    |

|           | 0 = Transmitter is not in Bus Off state                                                                |

| bit 12    | <b>TXBP:</b> Transmitter in Error State Bus Passive bit                                                |

|           | 1 = Transmitter is in Bus Passive state                                                                |

|           | 0 = Transmitter is not in Bus Passive state                                                            |

| bit 11    | <b>RXBP:</b> Receiver in Error State Bus Passive bit                                                   |

|           | 1 = Receiver is in Bus Passive state                                                                   |

|           | 0 = Receiver is not in Bus Passive state                                                               |

| bit 10    | TXWAR: Transmitter in Error State Warning bit                                                          |

|           | 1 = Transmitter is in Error Warning state                                                              |

| h:+ 0     | 0 = Transmitter is not in Error Warning state                                                          |

| bit 9     | RXWAR: Receiver in Error State Warning bit                                                             |

|           | 1 = Receiver is in Error Warning state<br>0 = Receiver is not in Error Warning state                   |

| bit 8     | EWARN: Transmitter or Receiver in Error State Warning bit                                              |

| bit o     | 1 = Transmitter or receiver is in Error Warning state                                                  |

|           | 0 = Transmitter or receiver is not in Error Warning state                                              |

| bit 7     | IVRIF: Invalid Message Interrupt Flag bit                                                              |

|           | 1 = Interrupt request has occurred                                                                     |

|           | 0 = Interrupt request has not occurred                                                                 |

| bit 6     | WAKIF: Bus Wake-up Activity Interrupt Flag bit                                                         |

|           | 1 = Interrupt request has occurred                                                                     |

|           | 0 = Interrupt request has not occurred                                                                 |

| bit 5     | ERRIF: Error Interrupt Flag bit (multiple sources in CxINTF<13:8>)                                     |

|           | 1 = Interrupt request has occurred                                                                     |

|           | 0 = Interrupt request has not occurred                                                                 |

| bit 4     | Unimplemented: Read as '0'                                                                             |

| bit 3     | FIFOIF: FIFO Almost Full Interrupt Flag bit                                                            |

|           | 1 = Interrupt request has occurred                                                                     |

| hit O     | 0 = Interrupt request has not occurred                                                                 |

| bit 2     | RBOVIF: RX Buffer Overflow Interrupt Flag bit                                                          |

|           | <ul> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> </ul> |

|           |                                                                                                        |

-n = Value at POR

| Field                                                                                                                                          | Description                                                                                                                                                                                                                                                          |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Wm,Wn                                                                                                                                          | Dividend, Divisor working register pair (direct addressing)                                                                                                                                                                                                          |  |  |