Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 256KB (85.5K x 24)                                                              |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 16K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 6x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep256mc202t-i-mm |

TABLE 2: dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X MOTOR CONTROL FAMILIES

|                   |                                | (s                            |              |                      |               | Rei            | nappa                                          | ble Pe                       | eriphe | erals               |                  |                                    |         |               |                              |                     |      |     |          |           |                                |

|-------------------|--------------------------------|-------------------------------|--------------|----------------------|---------------|----------------|------------------------------------------------|------------------------------|--------|---------------------|------------------|------------------------------------|---------|---------------|------------------------------|---------------------|------|-----|----------|-----------|--------------------------------|

| Device            | Page Erase Size (Instructions) | Program Flash Memory (Kbytes) | RAM (Kbytes) | 16-Bit/32-Bit Timers | Input Capture | Output Compare | Motor Control PWM <sup>(4)</sup><br>(Channels) | Quadrature Encoder Interface | UART   | ( <sub>2</sub> )IdS | ECAN™ Technology | External Interrupts <sup>(3)</sup> | м_12Стм | CRC Generator | 10-Bit/12-Bit ADC (Channels) | Op Amps/Comparators | ОШТЭ | PTG | I/O Pins | Pins      | Packages                       |

| PIC24EP32MC202    | 512                            | 32                            | 4            |                      |               |                |                                                |                              |        |                     |                  |                                    |         |               |                              |                     |      |     |          |           |                                |

| PIC24EP64MC202    | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                     |                  |                                    |         |               |                              |                     |      |     |          |           | SPDIP,                         |

| PIC24EP128MC202   | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                   | _                | 3                                  | 2       | 1             | 6                            | 2/3(1)              | Yes  | Yes | 21       | 28        | SOIC,<br>SSOP <sup>(5)</sup> , |

| PIC24EP256MC202   | 1024                           | 256                           | 32           |                      |               |                |                                                |                              |        |                     |                  |                                    |         |               |                              |                     |      |     |          |           | QFN-S                          |

| PIC24EP512MC202   | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                     |                  |                                    |         |               |                              |                     |      |     |          |           |                                |

| PIC24EP32MC203    | 512                            | 32                            | 4            | ٠                    | 4             | _              | _                                              | 1                            | ٠      | ٥                   |                  | ٠                                  | ٥       | 4             | •                            | 2/4                 | V    | V   | ٥.       | 00        | \                              |

| PIC24EP64MC203    | 1024                           | 64                            | 8            | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                   | _                | 3                                  | 2       | 1             | 8                            | 3/4                 | Yes  | Yes | 25       | 36        | VTLA                           |

| PIC24EP32MC204    | 512                            | 32                            | 4            |                      |               |                |                                                |                              |        |                     |                  |                                    |         |               |                              |                     |      |     |          |           |                                |

| PIC24EP64MC204    | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                     |                  |                                    |         |               |                              |                     |      |     |          |           | VTLA <sup>(5)</sup> ,          |

| PIC24EP128MC204   | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                   | _                | 3                                  | 2       | 1             | 9                            | 3/4                 | Yes  | Yes | 35       | 44/<br>48 | TQFP,<br>QFN,                  |

| PIC24EP256MC204   | 1024                           | 256                           | 32           |                      |               |                |                                                |                              |        |                     |                  |                                    |         |               |                              |                     |      |     |          | 70        | UQFN                           |

| PIC24EP512MC204   | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                     |                  |                                    |         |               |                              |                     |      |     |          |           |                                |

| PIC24EP64MC206    | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                     |                  |                                    |         |               |                              |                     |      |     |          |           |                                |

| PIC24EP128MC206   | 1024                           | 128                           | 16           | _                    |               |                |                                                |                              | •      |                     |                  | •                                  |         |               | 40                           | 0/4                 |      |     |          | 0.4       | TQFP,                          |

| PIC24EP256MC206   | 1024                           | 256                           | 32           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                   | _                | 3                                  | 2       | 1             | 16                           | 3/4                 | Yes  | Yes | 53       | 64        | QFN                            |

| PIC24EP512MC206   | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                     |                  |                                    |         |               |                              |                     |      |     |          |           |                                |

| dsPIC33EP32MC202  | 512                            | 32                            | 4            |                      |               |                |                                                |                              |        |                     |                  |                                    |         |               |                              |                     |      |     |          |           |                                |

| dsPIC33EP64MC202  | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                     |                  |                                    |         |               |                              |                     |      |     |          |           | SPDIP,                         |

| dsPIC33EP128MC202 | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                   | _                | 3                                  | 2       | 1             | 6                            | 2/3(1)              | Yes  | Yes | 21       | 28        | SOIC,<br>SSOP <sup>(5)</sup> , |

| dsPIC33EP256MC202 | 1024                           | 256                           | 32           |                      |               |                |                                                |                              |        |                     |                  |                                    |         |               |                              |                     |      |     |          |           | QFN-S                          |

| dsPIC33EP512MC202 | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                     |                  |                                    |         |               |                              |                     |      |     |          |           |                                |

| dsPIC33EP32MC203  | 512                            | 32                            | 4            | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                   |                  | 3                                  | 2       | 1             | 8                            | 3/4                 | Von  | Voo | 25       | 36        | VTLA                           |

| dsPIC33EP64MC203  | 1024                           | 64                            | 8            | ດ                    | 4             | 4              | 0                                              | ı                            | 2      | 2                   |                  | 9                                  | 2       | ı             | 0                            | 3/4                 | Yes  | Yes | 25       | 30        | VILA                           |

| dsPIC33EP32MC204  | 512                            | 32                            | 4            |                      |               |                |                                                |                              |        |                     |                  |                                    |         |               |                              |                     |      |     |          |           |                                |

| dsPIC33EP64MC204  | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                     |                  |                                    |         |               |                              |                     |      |     |          | 441       | VTLA <sup>(5)</sup> ,          |

| dsPIC33EP128MC204 | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                   | _                | 3                                  | 2       | 1             | 9                            | 3/4                 | Yes  | Yes | 35       | 44/<br>48 | TQFP,<br>QFN,                  |

| dsPIC33EP256MC204 | 1024                           | 256                           | 32           |                      |               |                |                                                |                              |        |                     |                  |                                    |         |               |                              |                     |      |     |          | 10        | UQFN                           |

| dsPIC33EP512MC204 | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                     |                  |                                    |         |               |                              |                     |      |     |          |           |                                |

| dsPIC33EP64MC206  | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                     |                  |                                    |         |               |                              |                     |      |     |          |           |                                |

| dsPIC33EP128MC206 | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                   |                  | 3                                  | 2       | 1             | 16                           | 3/4                 | Yes  | Yes | 53       | 64        | TQFP,                          |

| dsPIC33EP256MC206 | 1024                           | 256                           | 32           | 3                    | 4             | 4              | ٥                                              | '                            | 2      | 2                   | _                | 3                                  | 2       | '             | 10                           | 3/4                 | 163  | 163 | 55       | 04        | QFN                            |

| dsPIC33EP512MC206 | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                     |                  |                                    |         |               |                              |                     |      |     |          |           |                                |

| dsPIC33EP32MC502  | 512                            | 32                            | 4            |                      |               |                |                                                |                              |        |                     |                  |                                    |         |               |                              |                     |      |     |          |           |                                |

| dsPIC33EP64MC502  | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                     |                  |                                    |         |               |                              |                     |      |     |          |           | SPDIP,                         |

| dsPIC33EP128MC502 | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                   | 1                | 3                                  | 2       | 1             | 6                            | 2/3 <sup>(1)</sup>  | Yes  | Yes | 21       | 28        | SOIC,<br>SSOP <sup>(5)</sup> , |

| dsPIC33EP256MC502 | 1024                           | 256                           | 32           |                      |               |                |                                                |                              |        |                     |                  |                                    |         |               |                              |                     |      |     |          |           | QFN-S                          |

| dsPIC33EP512MC502 | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                     |                  |                                    |         |               |                              |                     |      |     |          |           |                                |

| dsPIC33EP32MC503  | 512                            | 32                            | 4            | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                   | 1                | 3                                  | 2       | 1             | 8                            | 3/4                 | Yes  | Yes | 25       | 36        | VTLA                           |

| dsPIC33EP64MC503  | 1024                           | 64                            | 8            | 5                    | -             | -              | J                                              | •                            |        | _                   | 1                | J                                  | _       | '             | J                            | 0/7                 | 100  | 103 | 20       | - 50      | V I LA                         |

Note 1: On 28-pin devices, Comparator 4 does not have external connections. Refer to Section 25.0 "Op Amp/Comparator Module" for details.

<sup>2:</sup> Only SPI2 is remappable.

<sup>3:</sup> INT0 is not remappable.

<sup>4:</sup> Only the PWM Faults are remappable.

<sup>5:</sup> The SSOP and VTLA packages are not available for devices with 512 Kbytes of memory.

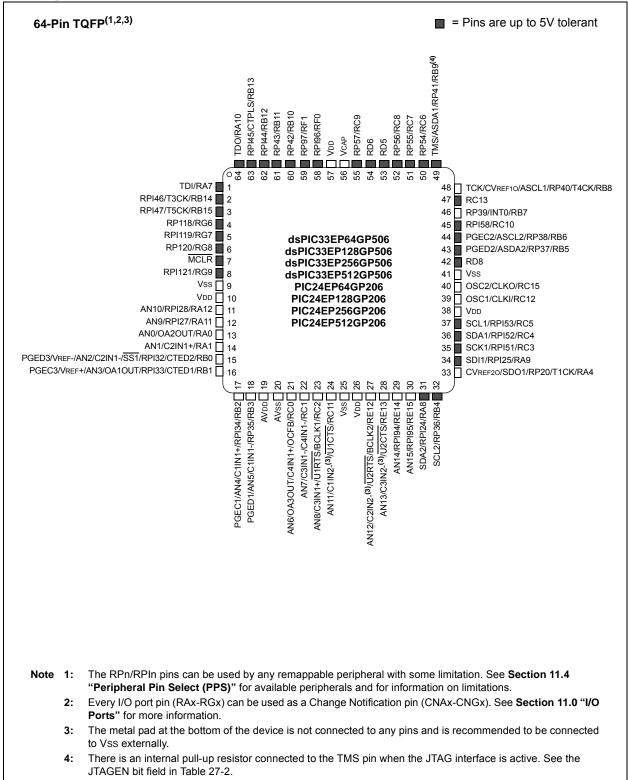

## Pin Diagrams (Continued)

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

| Pin Name <sup>(4)</sup> | Pin<br>Type | Buffer<br>Type | PPS | Description                                                                   |

|-------------------------|-------------|----------------|-----|-------------------------------------------------------------------------------|

| C1IN1-                  | I           | Analog         | No  | Op Amp/Comparator 1 Negative Input 1.                                         |

| C1IN2-                  | ı           | Analog         | No  | Comparator 1 Negative Input 2.                                                |

| C1IN1+                  | ı           | Analog         | No  | Op Amp/Comparator 1 Positive Input 1.                                         |

| OA1OUT                  | 0           | Analog         | No  | Op Amp 1 output.                                                              |

| C1OUT                   | 0           |                | Yes | Comparator 1 output.                                                          |

| C2IN1-                  | ı           | Analog         | No  | Op Amp/Comparator 2 Negative Input 1.                                         |

| C2IN2-                  | I           | Analog         | No  | Comparator 2 Negative Input 2.                                                |

| C2IN1+                  | I           | Analog         | No  | Op Amp/Comparator 2 Positive Input 1.                                         |

| OA2OUT                  | О           | Analog         | No  | Op Amp 2 output.                                                              |

| C2OUT                   | 0           | _              | Yes | Comparator 2 output.                                                          |

| C3IN1-                  | I           | Analog         | No  | Op Amp/Comparator 3 Negative Input 1.                                         |

| C3IN2-                  | I           | Analog         | No  | Comparator 3 Negative Input 2.                                                |

| C3IN1+                  | I           | Analog         | No  | Op Amp/Comparator 3 Positive Input 1.                                         |

| OA3OUT                  | О           | Analog         | No  | Op Amp 3 output.                                                              |

| C3OUT                   | 0           | _              | Yes | Comparator 3 output.                                                          |

| C4IN1-                  | I           | Analog         | No  | Comparator 4 Negative Input 1.                                                |

| C4IN1+                  | 1           | Analog         | No  | Comparator 4 Positive Input 1.                                                |

| C4OUT                   | 0           | _              | Yes | Comparator 4 output.                                                          |

| CVREF10                 | 0           | Analog         | No  | Op amp/comparator voltage reference output.                                   |

| CVREF20                 | 0           | Analog         | No  | Op amp/comparator voltage reference divided by 2 output.                      |

| PGED1                   | I/O         | ST             | No  | Data I/O pin for Programming/Debugging Communication Channel 1.               |

| PGEC1                   | ı           | ST             | No  | Clock input pin for Programming/Debugging Communication Channel 1.            |

| PGED2                   | I/O         | ST             | No  | Data I/O pin for Programming/Debugging Communication Channel 2.               |

| PGEC2                   | ı           | ST             | No  | Clock input pin for Programming/Debugging Communication Channel 2.            |

| PGED3                   | I/O         | ST             | No  | Data I/O pin for Programming/Debugging Communication Channel 3.               |

| PGEC3                   | l           | ST             | No  | Clock input pin for Programming/Debugging Communication Channel 3.            |

| MCLR                    | I/P         | ST             | No  | Master Clear (Reset) input. This pin is an active-low Reset to the device.    |

| AVDD                    | Р           | Р              | No  | Positive supply for analog modules. This pin must be connected at all times.  |

| AVss                    | Р           | Р              | No  | Ground reference for analog modules. This pin must be connected at all times. |

| VDD                     | Р           | _              | No  | Positive supply for peripheral logic and I/O pins.                            |

| VCAP                    | Р           | _              | No  | CPU logic filter capacitor connection.                                        |

| Vss                     | Р           | _              | No  | Ground reference for logic and I/O pins.                                      |

| VREF+                   | I           | Analog         | No  | Analog voltage reference (high) input.                                        |

| VREF-                   | I           | Analog         | No  | Analog voltage reference (low) input.                                         |

Legend:CMOS = CMOS compatible input or outputAnalog = Analog inputP = PowerST = Schmitt Trigger input with CMOS levelsO = OutputI = InputPPS = Peripheral Pin SelectTTL = TTL input buffer

Note 1: This pin is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

- 2: This pin is available on dsPIC33EPXXXGP/MC50X devices only.

- 3: This is the default Fault on Reset for dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices. See Section 16.0 "High-Speed PWM Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)" for more information.

- 4: Not all pins are available in all packages variants. See the "Pin Diagrams" section for pin availability.

- 5: There is an internal pull-up resistor connected to the TMS pin when the JTAG interface is active. See the JTAGEN bit field in Table 27-2.

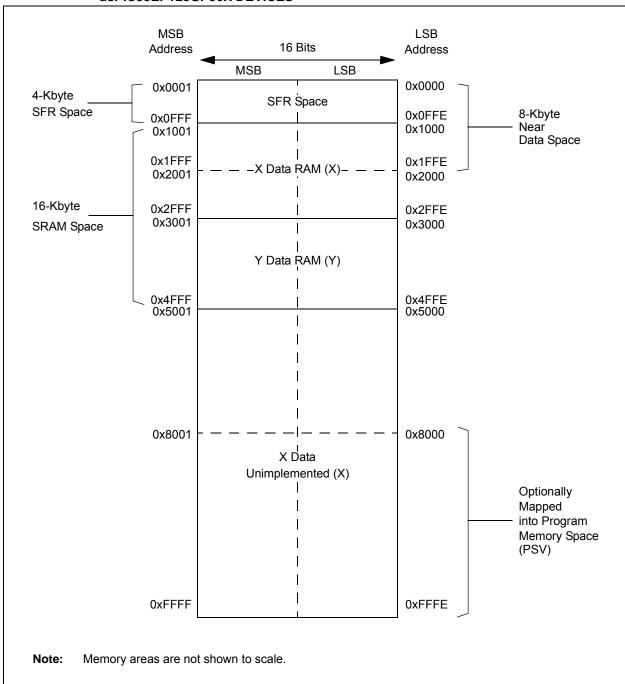

## 4.2 Data Address Space

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X CPU has a separate 16-bit-wide data memory space. The Data Space is accessed using separate Address Generation Units (AGUs) for read and write operations. The data memory maps, which are presented by device family and memory size, are shown in Figure 4-7 through Figure 4-16.

All Effective Addresses (EAs) in the data memory space are 16 bits wide and point to bytes within the Data Space. This arrangement gives a base Data Space address range of 64 Kbytes (32K words).

The base Data Space address is used in conjunction with a Read or Write Page register (DSRPAG or DSWPAG) to form an Extended Data Space, which has a total address range of 16 Mbytes.

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices implement up to 52 Kbytes of data memory (4 Kbytes of data memory for Special Function Registers and up to 48 Kbytes of data memory for RAM). If an EA points to a location outside of this area, an all-zero word or byte is returned.

#### 4.2.1 DATA SPACE WIDTH

The data memory space is organized in byte-addressable, 16-bit-wide blocks. Data is aligned in data memory and registers as 16-bit words, but all Data Space EAs resolve to bytes. The Least Significant Bytes (LSBs) of each word have even addresses, while the Most Significant Bytes (MSBs) have odd addresses.

## 4.2.2 DATA MEMORY ORGANIZATION AND ALIGNMENT

To maintain backward compatibility with PIC® MCU devices and improve Data Space memory usage efficiency, the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X instruction set supports both word and byte operations. As a consequence of byte accessibility, all Effective Address calculations are internally scaled to step through word-aligned memory. For example, the core recognizes that Post-Modified Register Indirect Addressing mode [Ws++] results in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

A data byte read, reads the complete word that contains the byte, using the LSb of any EA to determine which byte to select. The selected byte is placed onto the LSB of the data path. That is, data memory and registers are organized as two parallel, byte-wide entities with shared (word) address decode but separate write lines. Data byte writes only write to the corresponding side of the array or register that matches the byte address.

All word accesses must be aligned to an even address. Misaligned word data fetches are not supported, so care must be taken when mixing byte and word operations, or translating from 8-bit MCU code. If a misaligned read or write is attempted, an address error trap is generated. If the error occurred on a read, the instruction underway is completed. If the error occurred on a write, the instruction is executed but the write does not occur. In either case, a trap is then executed, allowing the system and/or user application to examine the machine state prior to execution of the address Fault.

All byte loads into any W register are loaded into the LSB. The MSB is not modified.

A Sign-Extend (SE) instruction is provided to allow user applications to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, user applications can clear the MSB of any W register by executing a Zero-Extend (ZE) instruction on the appropriate address.

#### 4.2.3 SFR SPACE

The first 4 Kbytes of the Near Data Space, from 0x0000 to 0x0FFF, is primarily occupied by Special Function Registers (SFRs). These are used by the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X core and peripheral modules for controlling the operation of the device.

SFRs are distributed among the modules that they control and are generally grouped together by module. Much of the SFR space contains unused addresses; these are read as '0'.

Note: The actual set of peripheral features and interrupts varies by the device. Refer to the corresponding device tables and pinout diagrams for device-specific information.

### 4.2.4 NEAR DATA SPACE

The 8-Kbyte area, between 0x0000 and 0x1FFF, is referred to as the Near Data Space. Locations in this space are directly addressable through a 13-bit absolute address field within all memory direct instructions. Additionally, the whole Data Space is addressable using MOV instructions, which support Memory Direct Addressing mode with a 16-bit address field, or by using Indirect Addressing mode using a working register as an Address Pointer.

FIGURE 4-9: DATA MEMORY MAP FOR dsPIC33EP128MC20X/50X AND dsPIC33EP128GP50X DEVICES

TABLE 4-23: ECAN1 REGISTER MAP WHEN WIN (C1CTRL1<0>) = 1 FOR dsPIC33EPXXXMC/GP50X DEVICES ONLY (CONTINUED)

| File Name  | Addr | Bit 15 | Bit 14    | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9                  | Bit 8    | Bit 7                         | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|------------|------|--------|-----------|--------|--------|--------|--------|------------------------|----------|-------------------------------|-------|-------|-------|-------|-------|-------|-------|---------------|

| C1RXF11EID | 046E |        | EID<15:8> |        |        |        |        |                        | EID<7:0> |                               |       |       |       |       |       |       | xxxx  |               |

| C1RXF12SID | 0470 |        | SID<10:3> |        |        |        |        | SID<2:0>               |          | _                             | EXIDE | _     | EID<1 | 7:16> | xxxx  |       |       |               |

| C1RXF12EID | 0472 |        | EID<15:8> |        |        |        |        | EID<7:0>               |          |                               |       |       |       |       |       | xxxx  |       |               |

| C1RXF13SID | 0474 |        | SID<10:3> |        |        |        |        |                        |          | SID<2:0>                      |       | _     | EXIDE | _     | EID<1 | 7:16> | xxxx  |               |

| C1RXF13EID | 0476 |        |           |        | EID<   | 15:8>  |        |                        |          | EID<7:0>                      |       |       |       |       |       |       |       | xxxx          |

| C1RXF14SID | 0478 |        |           |        | SID<   | 10:3>  |        |                        |          | SID<2:0> — EXIDE — EID<17:16> |       |       |       |       |       |       | 7:16> | xxxx          |

| C1RXF14EID | 047A |        | EID<15:8> |        |        |        |        |                        | EID<7:0> |                               |       |       |       |       |       | xxxx  |       |               |

| C1RXF15SID | 047C |        | SID<10:3> |        |        |        |        | SID<2:0> — EXIDE — EID |          |                               |       |       | EID<1 | 7:16> | xxxx  |       |       |               |

| C1RXF15EID | 047E |        | EID<15:8> |        |        |        |        |                        | EID<7:0> |                               |       |       |       |       |       | xxxx  |       |               |

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## 9.3 Oscillator Control Registers

## REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1)</sup>

| U-0    | R-0   | R-0   | R-0   | U-0 | R/W-y                | R/W-y                | R/W-y                |

|--------|-------|-------|-------|-----|----------------------|----------------------|----------------------|

| _      | COSC2 | COSC1 | COSC0 | _   | NOSC2 <sup>(2)</sup> | NOSC1 <sup>(2)</sup> | NOSC0 <sup>(2)</sup> |

| bit 15 |       |       |       |     |                      |                      | bit 8                |

| R/W-0   | R/W-0  | R-0  | U-0 | R/W-0             | U-0 | U-0 | R/W-0 |

|---------|--------|------|-----|-------------------|-----|-----|-------|

| CLKLOCK | IOLOCK | LOCK | _   | CF <sup>(3)</sup> | _   | _   | OSWEN |

| bit 7   |        |      |     |                   |     |     | bit 0 |

| Legend:           | y = Value set from Configu | y = Value set from Configuration bits on POR |                    |  |  |  |  |  |  |

|-------------------|----------------------------|----------------------------------------------|--------------------|--|--|--|--|--|--|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, rea                   | d as '0'           |  |  |  |  |  |  |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared                         | x = Bit is unknown |  |  |  |  |  |  |

bit 15 **Unimplemented:** Read as '0'

bit 14-12 **COSC<2:0>:** Current Oscillator Selection bits (read-only)

111 = Fast RC Oscillator (FRC) with Divide-by-n

110 = Fast RC Oscillator (FRC) with Divide-by-16

101 = Low-Power RC Oscillator (LPRC)

100 = Reserved

011 = Primary Oscillator (XT, HS, EC) with PLL

010 = Primary Oscillator (XT, HS, EC)

001 = Fast RC Oscillator (FRC) with Divide-by-N and PLL (FRCPLL)

000 = Fast RC Oscillator (FRC)

bit 11 **Unimplemented:** Read as '0'

bit 10-8 NOSC<2:0>: New Oscillator Selection bits<sup>(2)</sup>

111 = Fast RC Oscillator (FRC) with Divide-by-n

110 = Fast RC Oscillator (FRC) with Divide-by-16

101 = Low-Power RC Oscillator (LPRC)

100 = Reserved

011 = Primary Oscillator (XT, HS, EC) with PLL

010 = Primary Oscillator (XT, HS, EC)

001 = Fast RC Oscillator (FRC) with Divide-by-N and PLL (FRCPLL)

000 = Fast RC Oscillator (FRC)

bit 7 CLKLOCK: Clock Lock Enable bit

1 = If (FCKSM0 = 1), then clock and PLL configurations are locked; if (FCKSM0 = 0), then clock and PLL configurations may be modified

0 = Clock and PLL selections are not locked, configurations may be modified

bit 6 IOLOCK: I/O Lock Enable bit

1 = I/O lock is active

0 = I/O lock is not active

bit 5 LOCK: PLL Lock Status bit (read-only)

1 = Indicates that PLL is in lock or PLL start-up timer is satisfied

0 = Indicates that PLL is out of lock, start-up timer is in progress or PLL is disabled

- **Note 1:** Writes to this register require an unlock sequence. Refer to "Oscillator" (DS70580) in the "dsPIC33/PIC24 Family Reference Manual" (available from the Microchip web site) for details.

- 2: Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transitional clock source between the two PLL modes.

- **3:** This bit should only be cleared in software. Setting the bit in software (= 1) will have the same effect as an actual oscillator failure and trigger an oscillator failure trap.

#### 11.1.1 OPEN-DRAIN CONFIGURATION

In addition to the PORTx, LATx and TRISx registers for data control, port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs other than VDD by using external pull-up resistors. The maximum open-drain voltage allowed on any pin is the same as the maximum VIH specification for that particular pin.

See the "**Pin Diagrams**" section for the available 5V tolerant pins and Table 30-11 for the maximum VIH specification for each pin.

## 11.2 Configuring Analog and Digital Port Pins

The ANSELx register controls the operation of the analog port pins. The port pins that are to function as analog inputs or outputs must have their corresponding ANSELx and TRISx bits set. In order to use port pins for I/O functionality with digital modules, such as Timers, UARTs, etc., the corresponding ANSELx bit must be cleared.

The ANSELx register has a default value of 0xFFFF; therefore, all pins that share analog functions are analog (not digital) by default.

Pins with analog functions affected by the ANSELx registers are listed with a buffer type of analog in the Pinout I/O Descriptions (see Table 1-1).

If the TRISx bit is cleared (output) while the ANSELx bit is set, the digital output level (VOH or VOL) is converted by an analog peripheral, such as the ADC module or comparator module.

When the PORTx register is read, all pins configured as analog input channels are read as cleared (a low level).

Pins configured as digital inputs do not convert an analog input. Analog levels on any pin defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications.

#### 11.2.1 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically this instruction would be a  ${\tt NOP},$  as shown in Example 11-1.

## 11.3 Input Change Notification (ICN)

The Input Change Notification function of the I/O ports allows devices to generate interrupt requests to the processor in response to a Change-of-State (COS) on selected input pins. This feature can detect input Change-of-States even in Sleep mode, when the clocks are disabled. Every I/O port pin can be selected (enabled) for generating an interrupt request on a Change-of-State.

Three control registers are associated with the Change Notification (CN) functionality of each I/O port. The CNENx registers contain the CN interrupt enable control bits for each of the input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

Each I/O pin also has a weak pull-up and a weak pull-down connected to it. The pull-ups and pull-downs act as a current source or sink source connected to the pin and eliminate the need for external resistors when push button, or keypad devices are connected. The pull-ups and pull-downs are enabled separately, using the CNPUx and the CNPDx registers, which contain the control bits for each of the pins. Setting any of the control bits enables the weak pull-ups and/or pull-downs for the corresponding pins.

Note: Pull-ups and pull-downs on Change Notification pins should always be disabled when the port pin is configured as a digital output.

# EXAMPLE 11-1: PORT WRITE/READ EXAMPLE

```

MOV 0xFF00, W0 ; Configure PORTB<15:8>

; as inputs

MOV W0, TRISB ; and PORTB<7:0>

; as outputs

NOP ; Delay 1 cycle

BTSS PORTB, #13 ; Next Instruction

```

TABLE 11-1: SELECTABLE INPUT SOURCES (MAPS INPUT TO FUNCTION)

| Input Name <sup>(1)</sup>                   | <b>Function Name</b> | Register | Configuration Bits |

|---------------------------------------------|----------------------|----------|--------------------|

| External Interrupt 1                        | INT1                 | RPINR0   | INT1R<6:0>         |

| External Interrupt 2                        | INT2                 | RPINR1   | INT2R<6:0>         |

| Timer2 External Clock                       | T2CK                 | RPINR3   | T2CKR<6:0>         |

| Input Capture 1                             | IC1                  | RPINR7   | IC1R<6:0>          |

| Input Capture 2                             | IC2                  | RPINR7   | IC2R<6:0>          |

| Input Capture 3                             | IC3                  | RPINR8   | IC3R<6:0>          |

| Input Capture 4                             | IC4                  | RPINR8   | IC4R<6:0>          |

| Output Compare Fault A                      | OCFA                 | RPINR11  | OCFAR<6:0>         |

| PWM Fault 1 <sup>(3)</sup>                  | FLT1                 | RPINR12  | FLT1R<6:0>         |

| PWM Fault 2 <sup>(3)</sup>                  | FLT2                 | RPINR12  | FLT2R<6:0>         |

| QEI1 Phase A <sup>(3)</sup>                 | QEA1                 | RPINR14  | QEA1R<6:0>         |

| QEI1 Phase B <sup>(3)</sup>                 | QEB1                 | RPINR14  | QEB1R<6:0>         |

| QEI1 Index <sup>(3)</sup>                   | INDX1                | RPINR15  | INDX1R<6:0>        |

| QEI1 Home <sup>(3)</sup>                    | HOME1                | RPINR15  | HOM1R<6:0>         |

| UART1 Receive                               | U1RX                 | RPINR18  | U1RXR<6:0>         |

| UART2 Receive                               | U2RX                 | RPINR19  | U2RXR<6:0>         |

| SPI2 Data Input                             | SDI2                 | RPINR22  | SDI2R<6:0>         |

| SPI2 Clock Input                            | SCK2                 | RPINR22  | SCK2R<6:0>         |

| SPI2 Slave Select                           | SS2                  | RPINR23  | SS2R<6:0>          |

| CAN1 Receive <sup>(2)</sup>                 | C1RX                 | RPINR26  | C1RXR<6:0>         |

| PWM Sync Input 1 <sup>(3)</sup>             | SYNCI1               | RPINR37  | SYNCI1R<6:0>       |

| PWM Dead-Time Compensation 1 <sup>(3)</sup> | DTCMP1               | RPINR38  | DTCMP1R<6:0>       |

| PWM Dead-Time Compensation 2 <sup>(3)</sup> | DTCMP2               | RPINR39  | DTCMP2R<6:0>       |

| PWM Dead-Time Compensation 3 <sup>(3)</sup> | DTCMP3               | RPINR39  | DTCMP3R<6:0>       |

Note 1: Unless otherwise noted, all inputs use the Schmitt Trigger input buffers.

<sup>2:</sup> This input source is available on dsPIC33EPXXXGP/MC50X devices only.

<sup>3:</sup> This input source is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

## REGISTER 11-18: RPOR0: PERIPHERAL PIN SELECT OUTPUT REGISTER 0

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| _      | _   |       |       | RP35  | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|--------|-------|-------|

| _     | _   |       |       | RP20  | R<5:0> |       |       |

| bit 7 |     |       |       |       |        |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 **Unimplemented:** Read as '0'

bit 13-8 RP35R<5:0>: Peripheral Output Function is Assigned to RP35 Output Pin bits

(see Table 11-3 for peripheral function numbers)

bit 7-6 **Unimplemented:** Read as '0'

bit 5-0 RP20R<5:0>: Peripheral Output Function is Assigned to RP20 Output Pin bits

(see Table 11-3 for peripheral function numbers)

#### REGISTER 11-19: RPOR1: PERIPHERAL PIN SELECT OUTPUT REGISTER 1

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| _      | _   |       |       | RP37  | R<5:0> |       |       |

| bit 15 | _   |       | _     | _     | _      |       | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|--------|-------|-------|

| _     | _   |       |       | RP36  | R<5:0> |       |       |

| bit 7 |     |       |       |       |        |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 Unimplemented: Read as '0'

bit 13-8 RP37R<5:0>: Peripheral Output Function is Assigned to RP37 Output Pin bits

(see Table 11-3 for peripheral function numbers)

bit 7-6 **Unimplemented:** Read as '0'

bit 5-0 RP36R<5:0>: Peripheral Output Function is Assigned to RP36 Output Pin bits

(see Table 11-3 for peripheral function numbers)

## 14.2 Input Capture Registers

#### REGISTER 14-1: ICxCON1: INPUT CAPTURE x CONTROL REGISTER 1

| U-0    | U-0 | R/W-0  | R/W-0   | R/W-0   | R/W-0   | U-0 | U-0 |

|--------|-----|--------|---------|---------|---------|-----|-----|

| _      | _   | ICSIDL | ICTSEL2 | ICTSEL1 | ICTSEL0 | _   | _   |

| bit 15 |     |        |         |         |         |     |     |

| U-0   | R/W-0 | R/W-0 | R/HC/HS-0 | R/HC/HS-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-----------|-----------|-------|-------|-------|

| _     | ICI1  | ICI0  | ICOV      | ICBNE     | ICM2  | ICM1  | ICM0  |

| bit 7 |       |       |           |           |       |       | bit 0 |

| Legend:           | HC = Hardware Clearable bit | HS = Hardware Settable bit | į –                |

|-------------------|-----------------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, rea | nd as '0'          |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13 ICSIDL: Input Capture Stop in Idle Control bit

1 = Input capture will Halt in CPU Idle mode

0 = Input capture will continue to operate in CPU Idle mode

bit 12-10 ICTSEL<2:0>: Input Capture Timer Select bits

111 = Peripheral clock (FP) is the clock source of the ICx

110 = Reserved 101 = Reserved

100 = T1CLK is the clock source of the ICx (only the synchronous clock is supported)

011 = T5CLK is the clock source of the ICx 010 = T4CLK is the clock source of the ICx

001 = T2CLK is the clock source of the ICx

000 = T3CLK is the clock source of the ICx

bit 9-7 Unimplemented: Read as '0'

bit 6-5 ICI<1:0>: Number of Captures per Interrupt Select bits (this field is not used if ICM<2:0> = 001 or 111)

11 = Interrupt on every fourth capture event

10 = Interrupt on every third capture event

01 = Interrupt on every second capture event

00 = Interrupt on every capture event

bit 4 ICOV: Input Capture Overflow Status Flag bit (read-only)

1 = Input capture buffer overflow occurred0 = No input capture buffer overflow occurred

bit 3 **ICBNE:** Input Capture Buffer Not Empty Status bit (read-only)

1 = Input capture buffer is not empty, at least one more capture value can be read

0 = Input capture buffer is empty

bit 2-0 ICM<2:0>: Input Capture Mode Select bits

111 = Input capture functions as interrupt pin only in CPU Sleep and Idle modes (rising edge detect only, all other control bits are not applicable)

110 = Unused (module is disabled)

101 = Capture mode, every 16th rising edge (Prescaler Capture mode)

100 = Capture mode, every 4th rising edge (Prescaler Capture mode)

011 = Capture mode, every rising edge (Simple Capture mode)

010 = Capture mode, every falling edge (Simple Capture mode)

001 = Capture mode, every edge rising and falling (Edge Detect mode (ICI<1:0>) is not used in this mode)

000 = Input capture module is turned off

## REGISTER 17-15: QEI1GECH: QEI1 GREATER THAN OR EQUAL COMPARE HIGH WORD REGISTER

| R/W-0  | R/W-0         | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|--------|---------------|-------|-------|-------|-------|-------|-------|--|--|

|        | QEIGEC<31:24> |       |       |       |       |       |       |  |  |

| bit 15 |               |       |       |       |       |       | bit 8 |  |  |

| R/W-0         | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|---------------|-------|-------|-------|-------|-------|-------|-------|--|

| QEIGEC<23:16> |       |       |       |       |       |       |       |  |

| bit 7         |       |       |       |       |       |       | bit 0 |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 QEIGEC<31:16>: High Word Used to Form 32-Bit Greater Than or Equal Compare Register (QEI1GEC) bits

#### REGISTER 17-16: QEI1GECL: QEI1 GREATER THAN OR EQUAL COMPARE LOW WORD REGISTER

| R/W-0        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|--------------|-------|-------|-------|-------|-------|-------|-------|--|

| QEIGEC<15:8> |       |       |       |       |       |       |       |  |

| bit 15       |       |       |       |       |       |       | bit 8 |  |

| R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|-------------|-------|-------|-------|-------|-------|-------|-------|--|

| QEIGEC<7:0> |       |       |       |       |       |       |       |  |

| bit 7       |       |       |       |       |       |       | bit 0 |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 QEIGEC<15:0>: Low Word Used to Form 32-Bit Greater Than or Equal Compare Register (QEI1GEC) bits

## REGISTER 20-1: UxMODE: UARTx MODE REGISTER (CONTINUED)

bit 5 ABAUD: Auto-Baud Enable bit

1 = Enables baud rate measurement on the next character – requires reception of a Sync field (55h) before other data; cleared in hardware upon completion

0 = Baud rate measurement is disabled or completed

bit 4 URXINV: UARTx Receive Polarity Inversion bit

1 = UxRX Idle state is '0'

0 = UxRX Idle state is '1'

bit 3 BRGH: High Baud Rate Enable bit

1 = BRG generates 4 clocks per bit period (4x baud clock, High-Speed mode)

0 = BRG generates 16 clocks per bit period (16x baud clock, Standard mode)

bit 2-1 PDSEL<1:0>: Parity and Data Selection bits

11 = 9-bit data, no parity 10 = 8-bit data, odd parity 01 = 8-bit data, even parity 00 = 8-bit data, no parity

bit 0 STSEL: Stop Bit Selection bit

1 = Two Stop bits 0 = One Stop bit

**Note 1:** Refer to the "**UART**" (DS70582) section in the "dsPIC33/PIC24 Family Reference Manual" for information on enabling the UARTx module for receive or transmit operation.

2: This feature is only available for the 16x BRG mode (BRGH = 0).

3: This feature is only available on 44-pin and 64-pin devices.

4: This feature is only available on 64-pin devices.

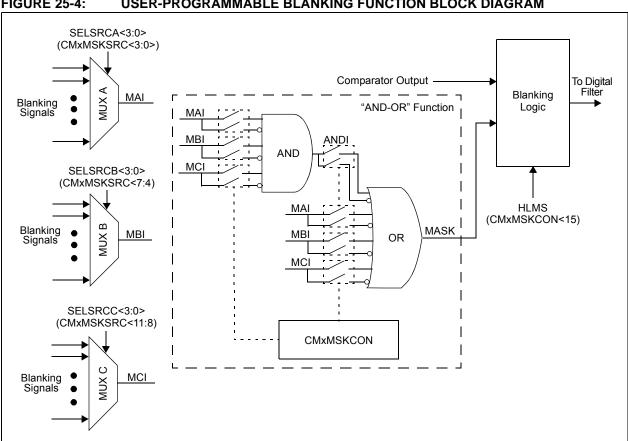

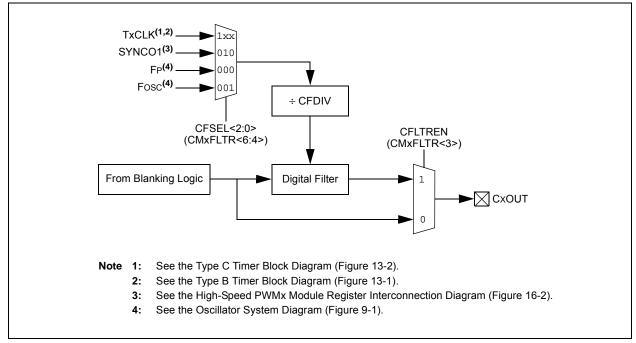

**FIGURE 25-4: USER-PROGRAMMABLE BLANKING FUNCTION BLOCK DIAGRAM**

#### **FIGURE 25-5:** DIGITAL FILTER INTERCONNECT BLOCK DIAGRAM

## REGISTER 25-3: CM4CON: COMPARATOR 4 CONTROL REGISTER (CONTINUED)

bit 5 **Unimplemented:** Read as '0'

bit 4 CREF: Comparator Reference Select bit (VIN+ input)<sup>(1)</sup>

1 = VIN+ input connects to internal CVREFIN voltage

0 = VIN+ input connects to C4IN1+ pin

bit 3-2 **Unimplemented:** Read as '0'

bit 1-0 **CCH<1:0>:** Comparator Channel Select bits<sup>(1)</sup>

11 = VIN- input of comparator connects to OA3/AN6 10 = VIN- input of comparator connects to OA2/AN0 01 = VIN- input of comparator connects to OA1/AN3 00 = VIN- input of comparator connects to C4IN1-

**Note 1:** Inputs that are selected and not available will be tied to Vss. See the "**Pin Diagrams**" section for available inputs for each package.

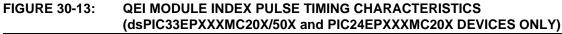

TABLE 30-32: QEI INDEX PULSE TIMING REQUIREMENTS

(dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

| AC CHARACTERISTICS |        |                                                                     | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |      |       |                                                           |

|--------------------|--------|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-----------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>                                       | Min.                                                                                                                                                                                                                                             | Max. | Units | Conditions                                                |

| TQ50               | TqiL   | Filter Time to Recognize Low, with Digital Filter                   | 3 * N * Tcy                                                                                                                                                                                                                                      | _    | ns    | N = 1, 2, 4, 16, 32, 64,<br>128 and 256 ( <b>Note 2</b> ) |

| TQ51               | TqiH   | Filter Time to Recognize High, with Digital Filter                  | 3 * N * Tcy                                                                                                                                                                                                                                      | _    | ns    | N = 1, 2, 4, 16, 32, 64,<br>128 and 256 ( <b>Note 2</b> ) |

| TQ55               | Tqidxr | Index Pulse Recognized to Position<br>Counter Reset (ungated index) | 3 Tcy                                                                                                                                                                                                                                            | _    | ns    |                                                           |

**Note 1:** These parameters are characterized but not tested in manufacturing.

<sup>2:</sup> Alignment of index pulses to QEA and QEB is shown for position counter Reset timing only. Shown for forward direction only (QEA leads QEB). Same timing applies for reverse direction (QEA lags QEB) but index pulse recognition occurs on the falling edge.

| dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X |

|-----------------------------------------------------------------|

| NOTES:                                                          |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

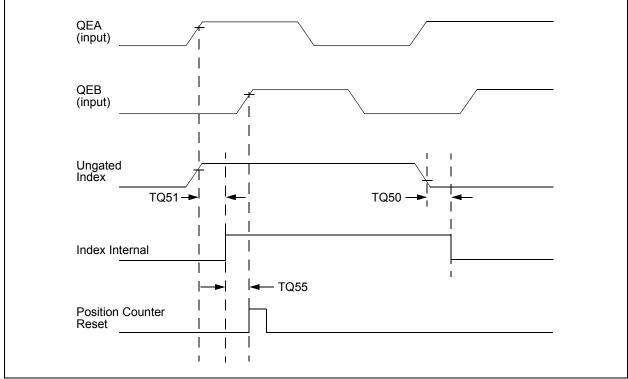

## 33.2 Package Details

## 28-Lead Skinny Plastic Dual In-Line (SP) - 300 mil Body [SPDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units            |       | INCHES   |       |

|----------------------------|------------------|-------|----------|-------|

| Dimensio                   | Dimension Limits |       |          | MAX   |

| Number of Pins             | N                |       | 28       |       |

| Pitch                      | е                |       | .100 BSC |       |

| Top to Seating Plane       | Α                | _     | _        | .200  |

| Molded Package Thickness   | A2               | .120  | .135     | .150  |

| Base to Seating Plane      | A1               | .015  | _        | _     |

| Shoulder to Shoulder Width | Е                | .290  | .310     | .335  |

| Molded Package Width       | E1               | .240  | .285     | .295  |

| Overall Length             | D                | 1.345 | 1.365    | 1.400 |

| Tip to Seating Plane       | L                | .110  | .130     | .150  |

| Lead Thickness             | С                | .008  | .010     | .015  |

| Upper Lead Width           | b1               | .040  | .050     | .070  |

| Lower Lead Width           | b                | .014  | .018     | .022  |

| Overall Row Spacing §      | eВ               | _     | _        | .430  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-070B

## 28-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**ote:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

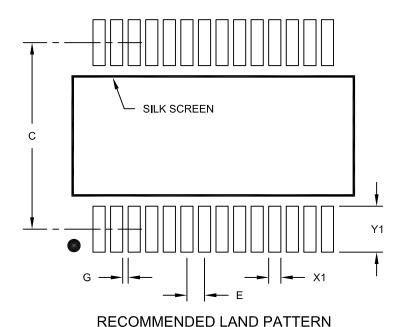

Units **MILLIMETERS Dimension Limits** MIN MOM MAX Contact Pitch Ε 0.65 BSC Contact Pad Spacing С 7.20 Contact Pad Width (X28) X1 0.45 Contact Pad Length (X28) 1.75 Υ1

G

0.20

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

Distance Between Pads

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2073A

| TyCON (Timer3 and Timer5 Control)      | 211     | Input Capture x (ICx)                         | 420 |

|----------------------------------------|---------|-----------------------------------------------|-----|

| UxMODE (UARTx Mode)                    |         | OCx/PWMx                                      |     |

| UxSTA (UARTx Status and Control)       |         | Output Compare x (OCx)                        |     |

| VEL1CNT (Velocity Counter 1)           |         | QEA/QEB Input                                 |     |

| Resets                                 |         | QEI Module Index Pulse                        |     |

| Brown-out Reset (BOR)                  | 123     | SPI1 Master Mode (Full-Duplex, CKE = 0,       |     |

| Configuration Mismatch Reset (CM)      | 123     | CKP = x, SMP = 1)                             | 441 |

| Illegal Condition Reset (IOPUWR)       |         | SPI1 Master Mode (Full-Duplex, CKE = 1,       |     |

| Illegal Opcode                         |         | CKP = x, SMP = 1)                             | 440 |

| Security                               |         | SPI1 Master Mode (Half-Duplex, Transmit Only, |     |

| Uninitialized W Register               |         | CKE = 0)                                      | 438 |

| Master Clear (MCLR) Pin Reset          |         | SPI1 Master Mode (Half-Duplex, Transmit Only, |     |

| Power-on Reset (POR)                   |         | CKE = 1)                                      | 439 |

| RESET Instruction (SWR)                |         | SPI1 Slave Mode (Full-Duplex, CKE = 0,        |     |

| Resources                              |         | CKP = 0, SMP = 0)                             | 448 |

| Trap Conflict Reset (TRAPR)            |         | SPI1 Slave Mode (Full-Duplex, CKE = 0,        |     |

| Watchdog Timer Time-out Reset (WDTO)   |         | CKP = 1, SMP = 0)                             | 446 |

| Resources Required for Digital PFC     |         | SPI1 Slave Mode (Full-Duplex, CKE = 1,        | 0   |

| Revision History                       |         | CKP = 0, SMP = 0)                             | 112 |

| TCVISION FIRSTORY                      |         | SPI1 Slave Mode (Full-Duplex, CKE = 1,        | 2   |

| S                                      |         | CKP = 1, SMP = 0)                             | 111 |

| Serial Peripheral Interface (SPI)      | 265     | SPI2 Master Mode (Full-Duplex, CKE = 0,       | 444 |

| Software Stack Pointer (SSP)           |         | •                                             | 420 |

| Special Features of the CPU            |         | CKP = x, SMP = 1)                             | 429 |

| SPI                                    | 319     | SPI2 Master Mode (Full-Duplex, CKE = 1,       | 420 |

| Control Registers                      | 269     | CKP = x, SMP = 1)                             | 420 |

| Helpful Tips                           |         | SPI2 Master Mode (Half-Duplex, Transmit Only, | 400 |

| Resources                              |         | CKE = 0)                                      | 426 |

| Resources                              | 207     | SPI2 Master Mode (Half-Duplex, Transmit Only, | 407 |

| Т                                      |         | CKE = 1)                                      | 427 |

| Temperature and Voltage Specifications |         | SPI2 Slave Mode (Full-Duplex, CKE = 0,        | 400 |

| AC                                     | 112 171 | CKP = 0, SMP = 0)                             | 436 |

|                                        |         | SPI2 Slave Mode (Full-Duplex, CKE = 0,        |     |

| Thermal Declaring Conditions           |         | CKP = 1, SMP = 0)                             | 434 |

| Thermal Packaging Characteristics      |         | SPI2 Slave Mode (Full-Duplex, CKE = 1,        |     |

| Timer1                                 |         | CKP = 0, SMP = 0)                             | 430 |

| Control Register                       |         | SPI2 Slave Mode (Full-Duplex, CKE = 1,        |     |

| Resources                              |         | CKP = 1, SMP = 0)                             |     |

| Timer2/3 and Timer4/5                  |         | Timer1-Timer5 External Clock                  |     |

| Control Registers                      |         | TimerQ (QEI Module) External Clock            |     |

| Resources                              | 209     | UARTx I/O                                     | 454 |

| Timing Diagrams                        |         | U                                             |     |

| 10-Bit ADC Conversion (CHPS<1:0> = 01, |         | •                                             |     |

| SIMSAM = 0, ASAM = 0, SSRC<2:0> =      |         | Universal Asynchronous Receiver               |     |

| SSRCG = 0)                             | 464     | Transmitter (UART)                            |     |

| 10-Bit ADC Conversion (CHPS<1:0> = 01, |         | Control Registers                             | 283 |

| SIMSAM = 0, $ASAM = 1$ , $SSRC<2:0> =$ | ,       | Helpful Tips                                  | 282 |

| SSRCG = 0, SAMC<4:0> = 00010)          | 464     | Resources                                     | 282 |

| 12-Bit ADC Conversion (ASAM = 0,       |         | User ID Words                                 | 384 |

| SSRC<2:0> = 000, SSRCG = 0)            | 462     | V                                             |     |

| BOR and Master Clear Reset             | 416     | V                                             |     |

| ECANx I/O                              | 454     | Voltage Regulator (On-Chip)                   | 384 |

| External Clock                         | 414     | W                                             |     |

| High-Speed PWMx Fault                  | 422     | W                                             |     |

| High-Speed PWMx Module                 |         | Watchdog Timer (WDT)379                       |     |

| I/O Characteristics                    |         | Programming Considerations                    |     |

| I2Cx Bus Data (Master Mode)            |         | WWW Address                                   |     |

| I2Cx Bus Data (Slave Mode)             |         | WWW, On-Line Support                          |     |

| I2Cx Bus Start/Stop Bits (Master Mode) |         | , , , , , , , , , , , , , , , , , , , ,       |     |

| I2Cx Bus Start/Stop Bits (Slave Mode)  |         |                                               |     |