Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Betans                     |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 60 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                  |

| Number of I/O              | 35                                                                             |

| Program Memory Size        | 256KB (85.5K x 24)                                                             |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 9x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-TQFP                                                                        |

| Supplier Device Package    | 44-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep256mc204-h-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

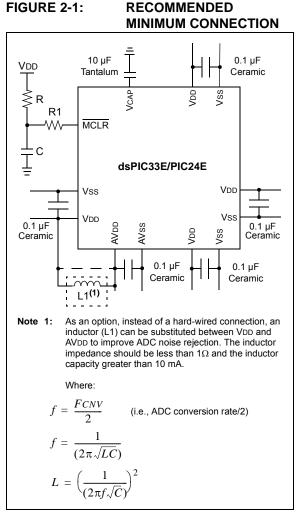

### 2.2.1 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits including DSCs to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

### 2.3 CPU Logic Filter Capacitor Connection (VCAP)

A low-ESR (< 1 Ohm) capacitor is required on the VCAP pin, which is used to stabilize the voltage regulator output voltage. The VCAP pin must not be connected to VDD and must have a capacitor greater than 4.7  $\mu$ F (10  $\mu$ F is recommended), 16V connected to ground. The type can be ceramic or tantalum. See **Section 30.0** "**Electrical Characteristics**" for additional information.

The placement of this capacitor should be close to the VCAP pin. It is recommended that the trace length not exceeds one-quarter inch (6 mm). See **Section 27.3 "On-Chip Voltage Regulator"** for details.

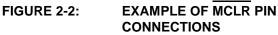

### 2.4 Master Clear (MCLR) Pin

The MCLR pin provides two specific device functions:

- Device Reset

- Device Programming and Debugging.

During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as shown in Figure 2-2, it is recommended that the capacitor, C, be isolated from the  $\overline{\text{MCLR}}$  pin during programming and debugging operations.

Place the components as shown in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

### 4.6 Modulo Addressing (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X Devices Only)

Modulo Addressing mode is a method of providing an automated means to support circular data buffers using hardware. The objective is to remove the need for software to perform data address boundary checks when executing tightly looped code, as is typical in many DSP algorithms.

Modulo Addressing can operate in either Data or Program Space (since the Data Pointer mechanism is essentially the same for both). One circular buffer can be supported in each of the X (which also provides the pointers into Program Space) and Y Data Spaces. Modulo Addressing can operate on any W Register Pointer. However, it is not advisable to use W14 or W15 for Modulo Addressing since these two registers are used as the Stack Frame Pointer and Stack Pointer, respectively.

In general, any particular circular buffer can be configured to operate in only one direction, as there are certain restrictions on the buffer start address (for incrementing buffers) or end address (for decrementing buffers), based upon the direction of the buffer.

The only exception to the usage restrictions is for buffers that have a power-of-two length. As these buffers satisfy the start and end address criteria, they can operate in a bidirectional mode (that is, address boundary checks are performed on both the lower and upper address boundaries).

### 4.6.1 START AND END ADDRESS

The Modulo Addressing scheme requires that a starting and ending address be specified, and loaded into the 16-bit Modulo Buffer Address registers: XMODSRT, XMODEND, YMODSRT and YMODEND (see Table 4-1).

| Note: | Y space Modulo Addressing EA calcula- |  |  |  |  |  |  |  |  |

|-------|---------------------------------------|--|--|--|--|--|--|--|--|

|       | tions assume word-sized data (LSb of  |  |  |  |  |  |  |  |  |

|       | every EA is always clear).            |  |  |  |  |  |  |  |  |

The length of a circular buffer is not directly specified. It is determined by the difference between the corresponding start and end addresses. The maximum possible length of the circular buffer is 32K words (64 Kbytes).

### 4.6.2 W ADDRESS REGISTER SELECTION

The Modulo and Bit-Reversed Addressing Control register, MODCON<15:0>, contains enable flags as well as a W register field to specify the W Address registers. The XWM and YWM fields select the registers that operate with Modulo Addressing:

- If XWM = 1111, X RAGU and X WAGU Modulo Addressing is disabled

- If YWM = 1111, Y AGU Modulo Addressing is disabled

The X Address Space Pointer W register (XWM), to which Modulo Addressing is to be applied, is stored in MODCON<3:0> (see Table 4-1). Modulo Addressing is enabled for X Data Space when XWM is set to any value other than '1111' and the XMODEN bit is set (MODCON<15>).

The Y Address Space Pointer W register (YWM), to which Modulo Addressing is to be applied, is stored in MODCON<7:4>. Modulo Addressing is enabled for Y Data Space when YWM is set to any value other than '1111' and the YMODEN bit is set at MODCON<14>.

#### Byte MOV #0x1100. W0 Address MOV W0, XMODSRT :set modulo start address MOV #0x1163, W0 0x1100 MOV W0, MODEND set modulo end address MOV #0x8001, W0 MOV W0, MODCON ;enable W1, X AGU for modulo MOV #0x0000, W0 ;W0 holds buffer fill value MOV ;point W1 to buffer #0x1110. W1 0x1163 DO AGAIN, #0x31 ;fill the 50 buffer locations MOV W0, [W1++] ;fill the next location AGAIN: INC W0, W0 increment the fill value Start Addr = 0x1100 End Addr = 0x1163 Length = 50 words

### FIGURE 4-20: MODULO ADDRESSING OPERATION EXAMPLE

|                                                     | Vector  | IRQ        |                   | Interrupt Bit Location |          |              |  |

|-----------------------------------------------------|---------|------------|-------------------|------------------------|----------|--------------|--|

| Interrupt Source                                    | # #     |            | IVT Address       | Flag                   | Enable   | Priority     |  |

| QEI1 – QEI1 Position Counter Compare <sup>(2)</sup> | 66      | 58         | 0x000088          | IFS3<10>               | IEC3<10> | IPC14<10:8>  |  |

| Reserved                                            | 67-72   | 59-64      | 0x00008A-0x000094 | _                      | _        | _            |  |

| U1E – UART1 Error Interrupt                         | 73      | 65         | 0x000096          | IFS4<1>                | IEC4<1>  | IPC16<6:4>   |  |

| U2E – UART2 Error Interrupt                         | 74      | 66         | 0x000098          | IFS4<2>                | IEC4<2>  | IPC16<10:8>  |  |

| CRC – CRC Generator Interrupt                       | 75      | 67         | 0x00009A          | IFS4<3>                | IEC4<3>  | IPC16<14:12> |  |

| Reserved                                            | 76-77   | 68-69      | 0x00009C-0x00009E | —                      | _        | —            |  |

| C1TX – CAN1 TX Data Request <sup>(1)</sup>          | 78      | 70         | 0x000A0           | IFS4<6>                | IEC4<6>  | IPC17<10:8>  |  |

| Reserved                                            | 79-84   | 71-76      | 0x0000A2-0x0000AC | —                      | _        | —            |  |

| CTMU – CTMU Interrupt                               | 85      | 77         | 0x0000AE          | IFS4<13>               | IEC4<13> | IPC19<6:4>   |  |

| Reserved                                            | 86-101  | 78-93      | 0x0000B0-0x0000CE | —                      | _        | —            |  |

| PWM1 – PWM Generator 1 <sup>(2)</sup>               | 102     | 94         | 0x0000D0          | IFS5<14>               | IEC5<14> | IPC23<10:8>  |  |

| PWM2 – PWM Generator 2 <sup>(2)</sup>               | 103     | 95         | 0x0000D2          | IFS5<15>               | IEC5<15> | IPC23<14:12> |  |

| PWM3 – PWM Generator 3 <sup>(2)</sup>               | 104     | 96         | 0x0000D4          | IFS6<0>                | IEC6<0>  | IPC24<2:0>   |  |

| Reserved                                            | 105-149 | 97-141     | 0x0001D6-0x00012E | —                      | _        | —            |  |

| ICD – ICD Application                               | 150     | 142        | 0x000142          | IFS8<14>               | IEC8<14> | IPC35<10:8>  |  |

| JTAG – JTAG Programming                             | 151     | 143        | 0x000130          | IFS8<15>               | IEC8<15> | IPC35<14:12> |  |

| Reserved                                            | 152     | 144        | 0x000134          | —                      | —        | _            |  |

| PTGSTEP – PTG Step                                  | 153     | 145        | 0x000136          | IFS9<1>                | IEC9<1>  | IPC36<6:4>   |  |

| PTGWDT – PTG Watchdog Time-out                      | 154     | 146        | 0x000138          | IFS9<2>                | IEC9<2>  | IPC36<10:8>  |  |

| PTG0 – PTG Interrupt 0                              | 155     | 147        | 0x00013A          | IFS9<3>                | IEC9<3>  | IPC36<14:12> |  |

| PTG1 – PTG Interrupt 1                              | 156     | 148        | 0x00013C          | IFS9<4>                | IEC9<4>  | IPC37<2:0>   |  |

| PTG2 – PTG Interrupt 2                              | 157     | 149        | 0x00013E          | IFS9<5>                | IEC9<5>  | IPC37<6:4>   |  |

| PTG3 – PTG Interrupt 3                              | 158     | 150        | 0x000140          | IFS9<6>                | IEC9<6>  | IPC37<10:8>  |  |

| Reserved                                            | 159-245 | 151-245    | 0x000142-0x0001FE | —                      | —        | _            |  |

|                                                     | Lowe    | est Natura | I Order Priority  |                        |          |              |  |

### TABLE 7-1: INTERRUPT VECTOR DETAILS (CONTINUED)

Note 1: This interrupt source is available on dsPIC33EPXXXGP50X and dsPIC33EPXXXMC50X devices only.

2: This interrupt source is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

| R/W-0        | R/W-0                                                                                                 | R/W-0            | R/W-0           | R/W-0                           | U-0             | U-0             | U-0     |  |  |  |  |

|--------------|-------------------------------------------------------------------------------------------------------|------------------|-----------------|---------------------------------|-----------------|-----------------|---------|--|--|--|--|

| CHEN         | SIZE                                                                                                  | DIR              | HALF            | NULLW                           | —               |                 |         |  |  |  |  |

| bit 15       |                                                                                                       |                  | •               |                                 |                 |                 | bit     |  |  |  |  |

|              |                                                                                                       |                  |                 |                                 |                 |                 |         |  |  |  |  |

| U-0          | U-0                                                                                                   | R/W-0            | R/W-0           | U-0                             | U-0             | R/W-0           | R/W-0   |  |  |  |  |

|              | —                                                                                                     | AMODE1           | AMODE0          | —                               | —               | MODE1           | MODE0   |  |  |  |  |

| bit 7        |                                                                                                       |                  |                 |                                 |                 |                 | bit     |  |  |  |  |

| Legend:      |                                                                                                       |                  |                 |                                 |                 |                 |         |  |  |  |  |

| R = Readat   | ole bit                                                                                               | W = Writable     | bit             | U = Unimplem                    | nented bit, rea | ıd as '0'       |         |  |  |  |  |

| -n = Value a | at POR                                                                                                | '1' = Bit is set |                 | '0' = Bit is clea               | ared            | x = Bit is unkr | nown    |  |  |  |  |

|              |                                                                                                       |                  |                 |                                 |                 |                 |         |  |  |  |  |

| bit 15       | -                                                                                                     | Channel Enabl    | e bit           |                                 |                 |                 |         |  |  |  |  |

|              | 1 = Channel<br>0 = Channel                                                                            |                  |                 |                                 |                 |                 |         |  |  |  |  |

| hit 11       |                                                                                                       |                  | izo hit         |                                 |                 |                 |         |  |  |  |  |

| bit 14       | 1 = Byte                                                                                              | ata Transfer S   | ze bil          |                                 |                 |                 |         |  |  |  |  |

|              | 0 = Word                                                                                              |                  |                 |                                 |                 |                 |         |  |  |  |  |

| bit 13       | DIR: DMA Tra                                                                                          | ansfer Directior | n bit (source/d | estination bus                  | select)         |                 |         |  |  |  |  |

|              |                                                                                                       |                  |                 | eripheral addre                 | -               |                 |         |  |  |  |  |

|              | 0 = Reads fr                                                                                          | om peripheral a  | address, write  | s to RAM addre                  | SS              |                 |         |  |  |  |  |

| bit 12       | HALF: DMA                                                                                             | Block Transfer   | Interrupt Sele  | ct bit                          |                 |                 |         |  |  |  |  |

|              |                                                                                                       |                  |                 | a has been mov<br>has been move |                 |                 |         |  |  |  |  |

| bit 11       | NULLW: Null                                                                                           | Data Periphera   | al Write Mode   | Select bit                      |                 |                 |         |  |  |  |  |

|              | 1 = Null data<br>0 = Normal c                                                                         |                  | eral in additio | n to RAM write                  | (DIR bit must   | also be clear)  |         |  |  |  |  |

| bit 10-6     | Unimplemen                                                                                            | ted: Read as '   | 0'              |                                 |                 |                 |         |  |  |  |  |

| bit 5-4      | AMODE<1:0                                                                                             | >: DMA Chann     | el Addressing   | Mode Select b                   | its             |                 |         |  |  |  |  |

|              |                                                                                                       | 11 = Reserved    |                 |                                 |                 |                 |         |  |  |  |  |

|              | 10 = Peripheral Indirect Addressing mode                                                              |                  |                 |                                 |                 |                 |         |  |  |  |  |

|              | 01 = Register Indirect without Post-Increment mode<br>00 = Register Indirect with Post-Increment mode |                  |                 |                                 |                 |                 |         |  |  |  |  |

| bit 3-2      | -                                                                                                     | ited: Read as '  |                 | Thous                           |                 |                 |         |  |  |  |  |

| bit 1-0      | -                                                                                                     | DMA Channel      |                 | ode Select bits                 |                 |                 |         |  |  |  |  |

|              |                                                                                                       |                  |                 |                                 | k transfer from | n/to each DMA t | ouffer) |  |  |  |  |

|              |                                                                                                       | ous, Ping-Pong   |                 |                                 |                 |                 | ,       |  |  |  |  |

|              | 01 = One-Sh                                                                                           | ot, Ping-Pong i  | nodes are dis   | abled                           |                 |                 |         |  |  |  |  |

|              |                                                                                                       | ous, Ping-Pong   |                 |                                 |                 |                 |         |  |  |  |  |

### REGISTER 8-1: DMAXCON: DMA CHANNEL X CONTROL REGISTER

### dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0             | U-0         | U-0              | U-0             | U-0                  | U-0              | U-0                | R/W-0   |

|-----------------|-------------|------------------|-----------------|----------------------|------------------|--------------------|---------|

| _               | —           | —                | _               | —                    | —                | —                  | PLLDIV8 |

| bit 15          |             |                  |                 |                      |                  |                    | bit 8   |

|                 |             |                  |                 |                      |                  |                    |         |

| R/W-0           | R/W-0       | R/W-1            | R/W-1           | R/W-0                | R/W-0            | R/W-0              | R/W-0   |

| PLLDIV7         | PLLDIV6     | PLLDIV5          | PLLDIV4         | PLLDIV3              | PLLDIV2          | PLLDIV1            | PLLDIV0 |

| bit 7           |             |                  |                 |                      |                  |                    | bit 0   |

|                 |             |                  |                 |                      |                  |                    |         |

| Legend:         |             |                  |                 |                      |                  |                    |         |

| R = Readable    | bit         | W = Writable     | bit             | U = Unimpler         | mented bit, read | as '0'             |         |

| -n = Value at P | OR          | '1' = Bit is set |                 | '0' = Bit is cleared |                  | x = Bit is unknown |         |

|                 |             |                  |                 |                      |                  |                    |         |

| bit 15-9        | Unimplemen  | ted: Read as '   | 0'              |                      |                  |                    |         |

| bit 8-0         | PLLDIV<8:0> | : PLL Feedbad    | ck Divisor bits | (also denoted        | as 'M', PLL mul  | tiplier)           |         |

|                 | 111111111 = | = 513            |                 |                      |                  |                    |         |

|                 | •           |                  |                 |                      |                  |                    |         |

|                 | •           |                  |                 |                      |                  |                    |         |

|                 | •           |                  |                 |                      |                  |                    |         |

|                 | 000110000 = | = 50 (default)   |                 |                      |                  |                    |         |

|                 | •           |                  |                 |                      |                  |                    |         |

|                 | •           |                  |                 |                      |                  |                    |         |

|                 | 000000010 = | - 4              |                 |                      |                  |                    |         |

|                 | 000000001 = |                  |                 |                      |                  |                    |         |

|                 | 00000000 =  | = 2              |                 |                      |                  |                    |         |

|                 |             |                  |                 |                      |                  |                    |         |

### REGISTER 9-3: PLLFBD: PLL FEEDBACK DIVISOR REGISTER

| R/W-0         | U-0                                                                                                                                                                                          | R/W-0                                                                                                                                                                                                                                                                  | R/W-0                                                                                                                                                                                 | R/W-0                         | R/W-0                 | R/W-0                 | R/W-0                 |  |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-----------------------|-----------------------|-----------------------|--|--|

| ROON          |                                                                                                                                                                                              | ROSSLP                                                                                                                                                                                                                                                                 | ROSEL                                                                                                                                                                                 | RODIV3 <sup>(1)</sup>         | RODIV2 <sup>(1)</sup> | RODIV1 <sup>(1)</sup> | RODIV0 <sup>(1)</sup> |  |  |

| bit 15        |                                                                                                                                                                                              |                                                                                                                                                                                                                                                                        |                                                                                                                                                                                       |                               |                       | 1                     | bit                   |  |  |

| U-0           | U-0                                                                                                                                                                                          | U-0                                                                                                                                                                                                                                                                    | U-0                                                                                                                                                                                   | U-0                           | U-0                   | U-0                   | U-0                   |  |  |

|               | —                                                                                                                                                                                            |                                                                                                                                                                                                                                                                        |                                                                                                                                                                                       | _                             |                       |                       |                       |  |  |

| bit 7         |                                                                                                                                                                                              | 1                                                                                                                                                                                                                                                                      |                                                                                                                                                                                       |                               |                       |                       | bit                   |  |  |

| Legend:       |                                                                                                                                                                                              |                                                                                                                                                                                                                                                                        |                                                                                                                                                                                       |                               |                       |                       |                       |  |  |

| R = Readable  | e bit                                                                                                                                                                                        | W = Writable                                                                                                                                                                                                                                                           | bit                                                                                                                                                                                   | U = Unimpler                  | nented bit, read      | l as '0'              |                       |  |  |

| -n = Value at | POR                                                                                                                                                                                          | '1' = Bit is set                                                                                                                                                                                                                                                       |                                                                                                                                                                                       | '0' = Bit is cle              | ared                  | x = Bit is unkr       | iown                  |  |  |

| bit 15        | 1 = Reference                                                                                                                                                                                |                                                                                                                                                                                                                                                                        | out is enabled                                                                                                                                                                        | on the REFCL                  | K pin <sup>(2)</sup>  |                       |                       |  |  |

|               |                                                                                                                                                                                              | e oscillator out                                                                                                                                                                                                                                                       |                                                                                                                                                                                       | ł                             |                       |                       |                       |  |  |

| bit 14        | -                                                                                                                                                                                            | ted: Read as '                                                                                                                                                                                                                                                         |                                                                                                                                                                                       |                               |                       |                       |                       |  |  |

| bit 13        |                                                                                                                                                                                              | ROSSLP: Reference Oscillator Run in Sleep bit                                                                                                                                                                                                                          |                                                                                                                                                                                       |                               |                       |                       |                       |  |  |

|               |                                                                                                                                                                                              | e oscillator out <sub>l</sub><br>e oscillator out <sub>l</sub>                                                                                                                                                                                                         |                                                                                                                                                                                       | to run in Sleep<br>d in Sleep |                       |                       |                       |  |  |

| bit 12        | ROSEL: Refe                                                                                                                                                                                  | erence Oscillato                                                                                                                                                                                                                                                       | or Source Sel                                                                                                                                                                         | ect bit                       |                       |                       |                       |  |  |

|               |                                                                                                                                                                                              | crystal is used<br>lock is used as                                                                                                                                                                                                                                     |                                                                                                                                                                                       |                               |                       |                       |                       |  |  |

| bit 11-8      | RODIV<3:0>:                                                                                                                                                                                  | Reference Os                                                                                                                                                                                                                                                           | cillator Divide                                                                                                                                                                       | er bits <sup>(1)</sup>        |                       |                       |                       |  |  |

|               | 1110 = Refer<br>1101 = Refer<br>1100 = Refer<br>1011 = Refer<br>1010 = Refer<br>1001 = Refer<br>0101 = Refer<br>0111 = Refer<br>0110 = Refer<br>0101 = Refer<br>0100 = Refer<br>0101 = Refer | ence clock divi<br>ence clock divi | ded by 16,38<br>ded by 8,192<br>ded by 4,096<br>ded by 2,048<br>ded by 1,024<br>ded by 512<br>ded by 256<br>ded by 128<br>ded by 64<br>ded by 32<br>ded by 16<br>ded by 8<br>ded by 4 |                               |                       |                       |                       |  |  |

|               | 0000 = Refer                                                                                                                                                                                 |                                                                                                                                                                                                                                                                        | 464 89 2                                                                                                                                                                              |                               |                       |                       |                       |  |  |

### REGISTER 9-5: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

- **Note 1:** The reference oscillator output must be disabled (ROON = 0) before writing to these bits.

- 2: This pin is remappable. See Section 11.4 "Peripheral Pin Select (PPS)" for more information.

### **10.0 POWER-SAVING FEATURES**

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Watchdog Timer and Power-Saving Modes" (DS70615) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices provide the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of peripherals being clocked constitutes lower consumed power.

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices can manage power consumption in four ways:

- Clock Frequency

- Instruction-Based Sleep and Idle modes

- Software-Controlled Doze mode

- · Selective Peripheral Control in Software

Combinations of these methods can be used to selectively tailor an application's power consumption while still maintaining critical application features, such as timing-sensitive communications.

### EXAMPLE 10-1: PWRSAV INSTRUCTION SYNTAX

| PWRSAV | #SLEEP_MODE | ; Put the device into Sleep mode |

|--------|-------------|----------------------------------|

| PWRSAV | #IDLE_MODE  | ; Put the device into Idle mode  |

### 10.1 Clock Frequency and Clock Switching

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices allow a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or highprecision oscillators by simply changing the NOSCx bits (OSCCON<10:8>). The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in **Section 9.0 "Oscillator Configuration**".

### 10.2 Instruction-Based Power-Saving Modes

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices have two special power-saving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution. Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. The assembler syntax of the PWRSAWnstruction is shown in Example 10-1.

**Note:** SLEEP\_MODEand IDLE\_MODEare constants defined in the assembler include file for the selected device.

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to "wake-up".

| Peripheral Pin<br>Select Input<br>Register Value | Input/<br>Output | Pin Assignment | Pin Assignment Select<br>Register |          | Input/<br>Output | Pin Assignment |

|--------------------------------------------------|------------------|----------------|-----------------------------------|----------|------------------|----------------|

| 010 1000                                         | I/O              | RP40           |                                   | 101 0101 |                  |                |

| 010 1001                                         | I/O              | RP41           |                                   | 101 0110 | —                |                |

| 010 1010                                         | I/O              | RP42           |                                   | 101 0111 | —                | _              |

| 010 1011                                         | I/O              | RP43           |                                   | 101 1000 | —                | _              |

| 010 1100                                         | I                | RPI44          |                                   | 101 1001 | —                | _              |

| 101 1010                                         |                  | —              |                                   | 110 1101 | —                | _              |

| 101 1011                                         |                  | —              |                                   | 110 1110 | —                | _              |

| 101 1100                                         |                  | _              |                                   | 110 1111 | —                | _              |

| 101 1101                                         |                  | _              |                                   | 111 0000 | —                | _              |

| 101 1110                                         | I                | RPI94          |                                   | 111 0001 |                  | _              |

| 101 1111                                         | I                | RPI95          |                                   | 111 0010 |                  | _              |

| 110 0000                                         | I                | RPI96          |                                   | 111 0011 | —                | _              |

| 110 0001                                         | I/O              | RP97           |                                   | 111 0100 | —                | _              |

| 110 0010                                         | —                | _              |                                   | 111 0101 | —                | _              |

| 110 0011                                         |                  | —              |                                   | 111 0110 | I/O              | RP118          |

| 110 0100                                         |                  | _              |                                   | 111 0111 | I                | RPI119         |

| 110 0101                                         |                  | _              |                                   | 111 1000 | I/O              | RP120          |

| 110 0110                                         |                  | _              |                                   | 111 1001 | Ι                | RPI121         |

| 110 0111                                         |                  | _              |                                   | 111 1010 | —                |                |

| 110 1000                                         |                  | —              |                                   | 111 1011 | —                | _              |

| 110 1001                                         | —                | _              |                                   | 111 1100 | —                | _              |

| 110 1010                                         |                  | —              |                                   | 111 1101 | —                | _              |

| 110 1011                                         |                  | —              |                                   | 111 1110 | —                | —              |

| 110 1100                                         | —                | _              |                                   | 111 1111 | —                |                |

### TABLE 11-2: INPUT PIN SELECTION FOR SELECTABLE INPUT SOURCES (CONTINUED)

Legend: Shaded rows indicate PPS Input register values that are unimplemented.

Note 1: See Section 11.4.4.1 "Virtual Connections" for more information on selecting this pin assignment.

2: These inputs are available on dsPIC33EPXXXGP/MC50X devices only.

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0                                | U-0   | U-0   | U-0                                    | R/W-0                              | R/W-0 | R/W-0  | R/W-0 |  |

|------------------------------------|-------|-------|----------------------------------------|------------------------------------|-------|--------|-------|--|

| —                                  | _     | —     |                                        |                                    | LEB   | <11:8> |       |  |

| bit 15                             |       |       |                                        |                                    |       |        | bit 8 |  |

|                                    |       |       |                                        |                                    |       |        |       |  |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                                  | R/W-0                              | R/W-0 | R/W-0  | R/W-0 |  |

|                                    |       |       | LEE                                    | 3<7:0>                             |       |        |       |  |

| bit 7                              |       |       |                                        |                                    |       |        | bit 0 |  |

|                                    |       |       |                                        |                                    |       |        |       |  |

| Legend:                            |       |       |                                        |                                    |       |        |       |  |

| R = Readable bit W = Writable bit  |       |       | bit                                    | U = Unimplemented bit, read as '0' |       |        |       |  |

| -n = Value at POR '1' = Bit is set |       |       | '0' = Bit is cleared x = Bit is unknow |                                    |       | nown   |       |  |

### REGISTER 16-17: LEBDLYx: PWMx LEADING-EDGE BLANKING DELAY REGISTER

bit 15-12 Unimplemented: Read as '0'

bit 11-0 LEB<11:0>: Leading-Edge Blanking Delay for Current-Limit and Fault Inputs bits

### REGISTER 19-1: I2CxCON: I2Cx CONTROL REGISTER (CONTINUED)

| bit 6 | <ul> <li>STREN: SCLx Clock Stretch Enable bit (when operating as I<sup>2</sup>C slave)</li> <li>Used in conjunction with the SCLREL bit.</li> <li>1 = Enables software or receives clock stretching</li> <li>0 = Disables software or receives clock stretching</li> </ul>                                                                                           |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5 | <b>ACKDT:</b> Acknowledge Data bit (when operating as I <sup>2</sup> C master, applicable during master receive)<br>Value that is transmitted when the software initiates an Acknowledge sequence.<br>1 = Sends NACK during Acknowledge<br>0 = Sends ACK during Acknowledge                                                                                          |

| bit 4 | <ul> <li>ACKEN: Acknowledge Sequence Enable bit<br/>(when operating as I<sup>2</sup>C master, applicable during master receive)</li> <li>1 = Initiates Acknowledge sequence on SDAx and SCLx pins and transmits ACKDT data bit. Hardware<br/>is clear at the end of the master Acknowledge sequence.</li> <li>0 = Acknowledge sequence is not in progress</li> </ul> |

| bit 3 | <ul> <li>RCEN: Receive Enable bit (when operating as I<sup>2</sup>C master)</li> <li>1 = Enables Receive mode for I<sup>2</sup>C. Hardware is clear at the end of the eighth bit of the master receive data byte.</li> <li>0 = Receive sequence is not in progress</li> </ul>                                                                                        |

| bit 2 | <ul> <li>PEN: Stop Condition Enable bit (when operating as I<sup>2</sup>C master)</li> <li>1 = Initiates Stop condition on SDAx and SCLx pins. Hardware is clear at the end of the master Stop sequence.</li> <li>0 = Stop condition is not in progress</li> </ul>                                                                                                   |

| bit 1 | <ul> <li>RSEN: Repeated Start Condition Enable bit (when operating as I<sup>2</sup>C master)</li> <li>1 = Initiates Repeated Start condition on SDAx and SCLx pins. Hardware is clear at the end of the master Repeated Start sequence.</li> <li>0 = Repeated Start condition is not in progress</li> </ul>                                                          |

| bit 0 | <ul> <li>SEN: Start Condition Enable bit (when operating as I<sup>2</sup>C master)</li> <li>1 = Initiates Start condition on SDAx and SCLx pins. Hardware is clear at the end of the master Start sequence.</li> <li>0 = Start condition is not in progress</li> </ul>                                                                                               |

Note 1: When performing master operations, ensure that the IPMIEN bit is set to '0'.

| R-0                                      | R-0              | R-0     | R-0                                     | R-0                                                                                               | R-0                                                                                                           | R-0                                                                                                                                                |

|------------------------------------------|------------------|---------|-----------------------------------------|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

|                                          |                  | TERR    | CNT<7:0>                                |                                                                                                   |                                                                                                               |                                                                                                                                                    |

|                                          |                  |         |                                         |                                                                                                   |                                                                                                               | bit 8                                                                                                                                              |

|                                          |                  |         |                                         |                                                                                                   |                                                                                                               |                                                                                                                                                    |

| R-0                                      | R-0              | R-0     | R-0                                     | R-0                                                                                               | R-0                                                                                                           | R-0                                                                                                                                                |

|                                          |                  | RERR    | CNT<7:0>                                |                                                                                                   |                                                                                                               |                                                                                                                                                    |

|                                          |                  |         |                                         |                                                                                                   |                                                                                                               | bit 0                                                                                                                                              |

|                                          |                  |         |                                         |                                                                                                   |                                                                                                               |                                                                                                                                                    |

|                                          |                  |         |                                         |                                                                                                   |                                                                                                               |                                                                                                                                                    |

| t                                        | W = Writable bit |         | U = Unimplemented bit, read as '0'      |                                                                                                   |                                                                                                               |                                                                                                                                                    |

| OR '1' = Bit is set '0' = Bit is cleared |                  |         | ed                                      | x = Bit is unknown                                                                                |                                                                                                               |                                                                                                                                                    |

|                                          | R-0              | R-0 R-0 | R-0 R-0 R-0<br>RERR<br>W = Writable bit | TERRCNT<7:0>           R-0         R-0         R-0           RERRCNT<7:0>         U = Unimplement | TERRCNT<7:0>           R-0         R-0         R-0           RERRCNT<7:0>         U = Unimplemented bit, real | $R-0 \qquad R-0 \qquad RERRCNT<7:0>$ |

| bit 15-8 <b>TERRCNT&lt;7:0&gt;:</b> Transmit Error Count bits |

|---------------------------------------------------------------|

|---------------------------------------------------------------|

bit 7-0 **RERRCNT<7:0>:** Receive Error Count bits

### REGISTER 21-9: CxCFG1: ECANx BAUD RATE CONFIGURATION REGISTER 1

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| SJW1  | SJW0  | BRP5  | BRP4  | BRP3  | BRP2  | BRP1  | BRP0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 7-6 | <b>SJW&lt;1:0&gt;:</b> Synchronization Jump Width bits<br>11 = Length is 4 x TQ<br>10 = Length is 3 x TQ<br>01 = Length is 2 x TQ<br>00 = Length is 1 x TQ |  |  |  |  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| bit 5-0 | BRP<5:0>: Baud Rate Prescaler bits<br>11 1111 = TQ = 2 x 64 x 1/FCAN<br>•<br>•<br>00 0010 = TQ = 2 x 3 x 1/FCAN<br>00 0001 = TQ = 2 x 2 x 1/FCAN           |  |  |  |  |

| R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1  | R/W-1  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| FLTEN15 | FLTEN14 | FLTEN13 | FLTEN12 | FLTEN11 | FLTEN10 | FLTEN9 | FLTEN8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

|         |         |         |         |         |         |        |        |

| R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1  | R/W-1  |

| FLTEN7  | FLTEN6  | FLTEN5  | FLTEN4  | FLTEN3  | FLTEN2  | FLTEN1 | FLTEN0 |

| bit 7   |         |         |         |         |         |        | bit 0  |

|         |         |         |         |         |         |        |        |

| Legend: |         |         |         |         |         |        |        |

### REGISTER 21-11: CxFEN1: ECANx ACCEPTANCE FILTER ENABLE REGISTER 1

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-0

FLTEN<15:0>: Enable Filter n to Accept Messages bits

1 = Enables Filter n

0 = Disables Filter n

### REGISTER 21-12: CxBUFPNT1: ECANx FILTER 0-3 BUFFER POINTER REGISTER 1

| R/W-0                             | R/W-0                                                                    | R/W-0                                                                                                        | R/W-0                                           | R/W-0                                   | R/W-0          | R/W-0  | R/W-0 |  |

|-----------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------|-----------------------------------------|----------------|--------|-------|--|

|                                   | F3BP<3:0>                                                                |                                                                                                              |                                                 |                                         | F2BI           | ><3:0> |       |  |

| bit 15                            |                                                                          |                                                                                                              |                                                 |                                         |                |        | bit 8 |  |

| R/W-0                             | R/W-0                                                                    | R/W-0                                                                                                        | R/W-0                                           | R/W-0                                   | R/W-0          | R/W-0  | R/W-0 |  |

| F1BP<3:0>                         |                                                                          |                                                                                                              |                                                 | F0BI                                    | ><3:0>         |        |       |  |

| bit 7                             |                                                                          |                                                                                                              |                                                 |                                         |                |        | bit ( |  |

| Legend:                           |                                                                          |                                                                                                              |                                                 |                                         |                |        |       |  |

| R = Readable bit W = Writable bit |                                                                          |                                                                                                              |                                                 | U = Unimplemented bit, read as '0'      |                |        |       |  |

| -n = Value at                     | t POR                                                                    | '1' = Bit is set                                                                                             |                                                 | '0' = Bit is cleared x = Bit is unknown |                |        | nown  |  |

| bit 15-12                         | 1111 = Filte<br>1110 = Filte                                             | : RX Buffer Masl<br>er hits received ir<br>er hits received ir<br>er hits received ir<br>er hits received ir | n RX FIFO bu<br>n RX Buffer 14<br>n RX Buffer 1 | ffer<br>4                               |                |        |       |  |

| bit 11-8                          | F2BP<3:0>                                                                | : RX Buffer Masl                                                                                             | k for Filter 2 b                                | oits (same value                        | s as bits<15:1 | 2>)    |       |  |

| DIL II-O                          | F1BP<3:0>: RX Buffer Mask for Filter 1 bits (same values as bits<15:12>) |                                                                                                              |                                                 |                                         |                |        |       |  |

| bit 7-4                           | F1BP<3:0>                                                                | : RX Buffer Masl                                                                                             | k for Filter 1 b                                | oits (same value                        | s as bits<15:1 | 2>)    |       |  |

NOTES:

### dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

### REGISTER 27-1: DEVID: DEVICE ID REGISTER

|        | nd: R = Read-Only bit U = Unimplemented bit |   |         |                       |   |   |        |

|--------|---------------------------------------------|---|---------|-----------------------|---|---|--------|

|        |                                             |   |         |                       |   |   |        |

| bit 7  |                                             |   |         |                       |   |   | bit 0  |

|        |                                             |   | DEVID   | <7:0> <sup>(1)</sup>  |   |   |        |

| R      | R                                           | R | R       | R                     | R | R | R      |

| bit 15 |                                             |   |         |                       |   |   | bit 8  |

|        |                                             |   | DEVID<  | :15:8> <sup>(1)</sup> |   |   |        |

| R      | R                                           | R | R       | R                     | R | R | R      |

| bit 23 |                                             |   |         |                       |   |   | bit 16 |

|        |                                             |   | DEVID<2 | 23:16>(1)             |   |   |        |

| R      | R                                           | R | R       | R                     | R | R | R      |

bit 23-0 **DEVID<23:0>:** Device Identifier bits<sup>(1)</sup>

**Note 1:** Refer to the "dsPIC33E/PIC24E Flash Programming Specification for Devices with Volatile Configuration *Bits*" (DS70663) for the list of device ID values.

### **REGISTER 27-2: DEVREV: DEVICE REVISION REGISTER**

| R           | R                                           | R | R      | R                      | R | R | R      |

|-------------|---------------------------------------------|---|--------|------------------------|---|---|--------|

|             |                                             |   | DEVREV | <23:16> <sup>(1)</sup> |   |   |        |

| bit 23      |                                             |   |        |                        |   |   | bit 16 |

|             |                                             |   |        |                        |   |   |        |

| R           | R                                           | R | R      | R                      | R | R | R      |

|             |                                             |   | DEVREV | <15:8>(1)              |   |   |        |

| bit 15      |                                             |   |        |                        |   |   | bit 8  |

| R           | R                                           | R | R      | R                      | R | R | R      |

|             |                                             |   | DEVRE\ | /<7:0> <sup>(1)</sup>  |   |   |        |

| bit 7       |                                             |   |        |                        |   |   | bit 0  |

|             |                                             |   |        |                        |   |   |        |

| Legend: R = | nd: R = Read-only bit U = Unimplemented bit |   |        |                        |   |   |        |

### bit 23-0 **DEVREV<23:0>:** Device Revision bits<sup>(1)</sup>

**Note 1:** Refer to the "dsPIC33E/PIC24E Flash Programming Specification for Devices with Volatile Configuration *Bits*" (DS70663) for the list of device revision values.

### 30.2 AC Characteristics and Timing Parameters

This section defines dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X AC characteristics and timing parameters.

### TABLE 30-15: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

|                    | Standard Operating Conditions: 3.0V to 3.6V<br>(unless otherwise stated) |

|--------------------|--------------------------------------------------------------------------|

| AC CHARACTERISTICS | $\begin{array}{llllllllllllllllllllllllllllllllllll$                     |

|                    | Characteristics".                                                        |

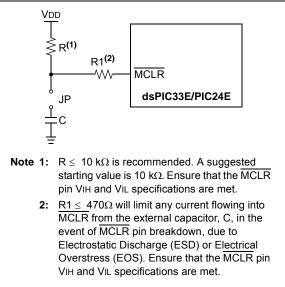

### FIGURE 30-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

### TABLE 30-16: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

| Param<br>No. | Symbol | Characteristic        | Min. | Тур. | Max. | Units | Conditions                                                          |

|--------------|--------|-----------------------|------|------|------|-------|---------------------------------------------------------------------|

| DO50         | Cosco  | OSC2 Pin              | _    | —    | 15   |       | In XT and HS modes, when<br>external clock is used to drive<br>OSC1 |

| DO56         | Сю     | All I/O Pins and OSC2 | —    | —    | 50   | pF    | EC mode                                                             |

| DO58         | Св     | SCLx, SDAx            | _    | _    | 400  | pF    | In l <sup>2</sup> C™ mode                                           |

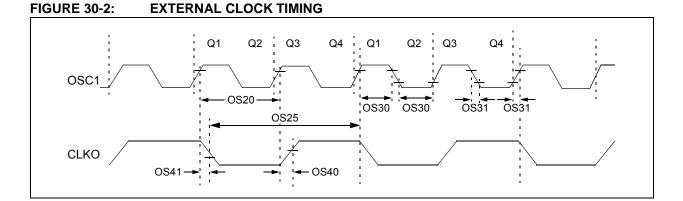

| AC CHARACTERISTICS |               |                                                                                    | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                               |             |            |                               |  |  |

|--------------------|---------------|------------------------------------------------------------------------------------|-------------------------------------------------------|-------------------------------|-------------|------------|-------------------------------|--|--|

| Param<br>No.       | Symb          | Characteristic                                                                     | Min.                                                  | Min. Typ. <sup>(1)</sup> Max. |             | Units      | Conditions                    |  |  |

| OS10               | FIN           | External CLKI Frequency<br>(External clocks allowed only<br>in EC and ECPLL modes) | DC                                                    | _                             | 60          | MHz        | EC                            |  |  |

|                    |               | Oscillator Crystal Frequency                                                       | 3.5<br>10                                             |                               | 10<br>25    | MHz<br>MHz | XT<br>HS                      |  |  |

| OS20               | Tosc          | Tosc = 1/Fosc                                                                      | 8.33                                                  | _                             | DC          | ns         | +125°C                        |  |  |

|                    |               | Tosc = 1/Fosc                                                                      | 7.14                                                  | _                             | DC          | ns         | +85°C                         |  |  |

| OS25               | Тсү           | Instruction Cycle Time <sup>(2)</sup>                                              | 16.67                                                 | _                             | DC          | ns         | +125°C                        |  |  |

|                    |               | Instruction Cycle Time <sup>(2)</sup>                                              | 14.28                                                 | _                             | DC          | ns         | +85°C                         |  |  |

| OS30               | TosL,<br>TosH | External Clock in (OSC1)<br>High or Low Time                                       | 0.45 x Tosc                                           | —                             | 0.55 x Tosc | ns         | EC                            |  |  |

| OS31               | TosR,<br>TosF | External Clock in (OSC1)<br>Rise or Fall Time                                      | —                                                     | —                             | 20          | ns         | EC                            |  |  |

| OS40               | TckR          | CLKO Rise Time <sup>(3,4)</sup>                                                    | —                                                     | 5.2                           | _           | ns         |                               |  |  |

| OS41               | TckF          | CLKO Fall Time <sup>(3,4)</sup>                                                    | —                                                     | 5.2                           |             | ns         |                               |  |  |

| OS42               | Gм            | External Oscillator<br>Transconductance <sup>(4)</sup>                             | —                                                     | 12                            | _           | mA/V       | HS, VDD = 3.3V,<br>TA = +25°C |  |  |

|                    |               |                                                                                    | —                                                     | 6                             | _           | mA/V       | XT, VDD = 3.3V,<br>TA = +25°C |  |  |