Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detuns                     |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 60 MIPs                                                                        |

| Connectivity               | I²C, IrDA, LINbus, QEI, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                  |

| Number of I/O              | 35                                                                             |

| Program Memory Size        | 256КВ (85.5К × 24)                                                             |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 9x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-VFTLA Exposed Pad                                                           |

| Supplier Device Package    | 44-VTLA (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep256mc204-h-tl |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

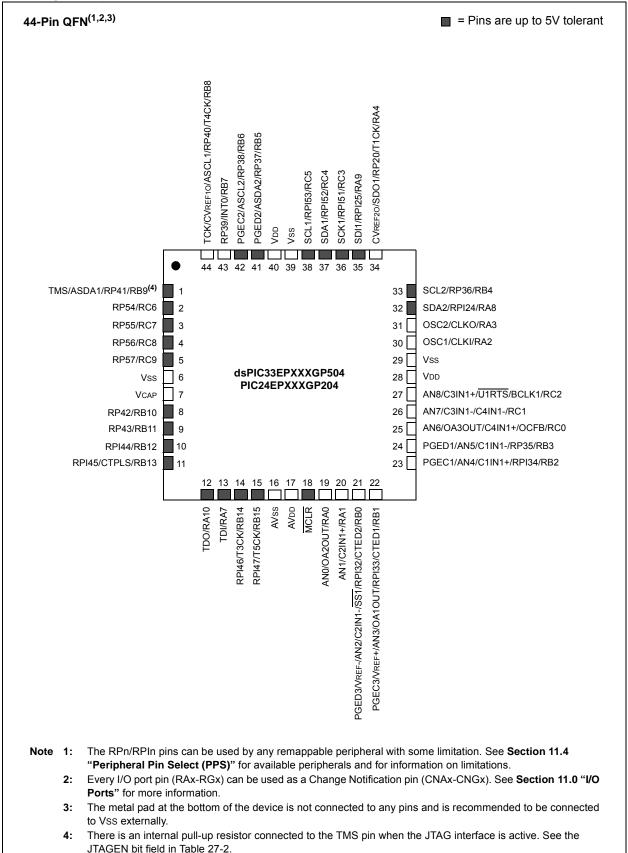

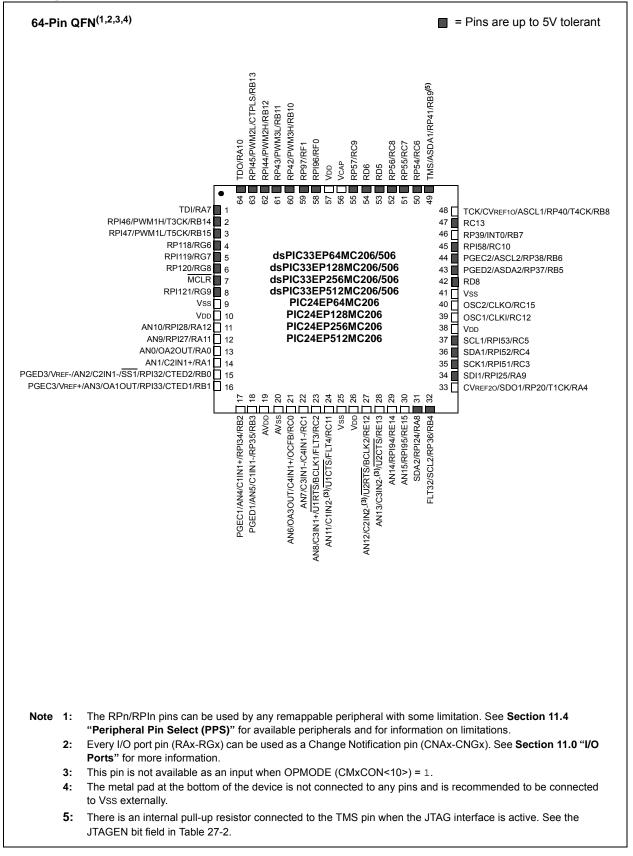

### **Pin Diagrams (Continued)**

## Pin Diagrams (Continued)

# 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT DIGITAL SIGNAL CONTROLLERS AND MICROCONTROLLERS

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section of the "dsPIC33/PIC24 Familv Reference Manual", which is available from the Microchip web site (www.microchip.com)

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

## 2.1 Basic Connection Requirements

Getting started with the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins (regardless if ADC module is not used)

(see Section 2.2 "Decoupling Capacitors")

• VCAP

(see Section 2.3 "CPU Logic Filter Capacitor Connection (VCAP)")

- MCLR pin (see Section 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.5 "ICSP Pins**")

- OSC1 and OSC2 pins when external oscillator source is used

(see Section 2.6 "External Oscillator Pins")

Additionally, the following pins may be required:

• VREF+/VREF- pins are used when external voltage reference for the ADC module is implemented

Note: The AVDD and AVSS pins must be connected, independent of the ADC voltage reference source.

# 2.2 Decoupling Capacitors

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: Recommendation of 0.1  $\mu$ F (100 nF), 10-20V. This capacitor should be a low-ESR and have resonance frequency in the range of 20 MHz and higher. It is recommended to use ceramic capacitors.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high-frequency noise: If the board is experiencing high-frequency noise, above tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of  $0.01 \ \mu\text{F}$  to  $0.001 \ \mu\text{F}$ . Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example,  $0.1 \ \mu\text{F}$  in parallel with  $0.001 \ \mu\text{F}$ .

- **Maximizing performance:** On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB track inductance.

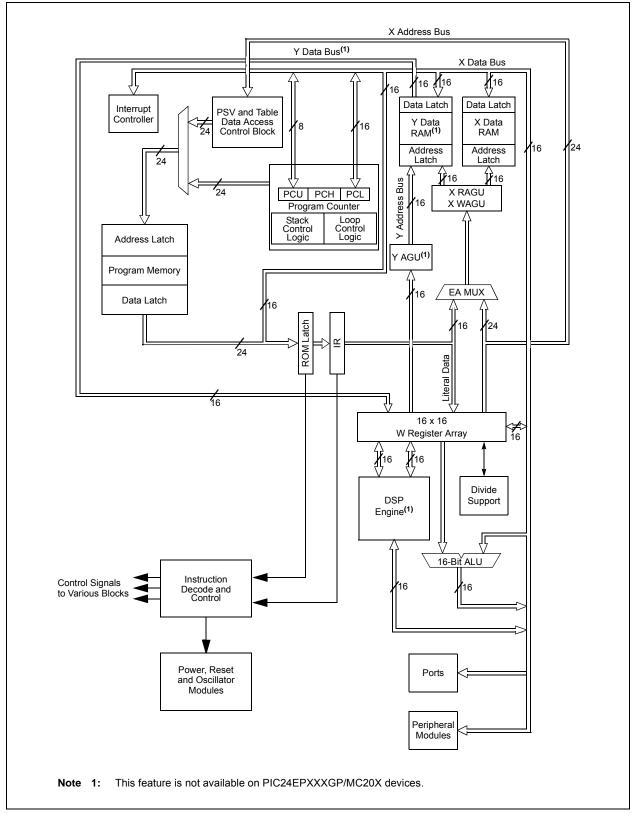

FIGURE 3-1: dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X CPU BLOCK DIAGRAM

## 4.2 Data Address Space

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X CPU has a separate 16-bit-wide data memory space. The Data Space is accessed using separate Address Generation Units (AGUs) for read and write operations. The data memory maps, which are presented by device family and memory size, are shown in Figure 4-7 through Figure 4-16.

All Effective Addresses (EAs) in the data memory space are 16 bits wide and point to bytes within the Data Space. This arrangement gives a base Data Space address range of 64 Kbytes (32K words).

The base Data Space address is used in conjunction with a Read or Write Page register (DSRPAG or DSWPAG) to form an Extended Data Space, which has a total address range of 16 Mbytes.

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices implement up to 52 Kbytes of data memory (4 Kbytes of data memory for Special Function Registers and up to 48 Kbytes of data memory for RAM). If an EA points to a location outside of this area, an all-zero word or byte is returned.

## 4.2.1 DATA SPACE WIDTH

The data memory space is organized in byteaddressable, 16-bit-wide blocks. Data is aligned in data memory and registers as 16-bit words, but all Data Space EAs resolve to bytes. The Least Significant Bytes (LSBs) of each word have even addresses, while the Most Significant Bytes (MSBs) have odd addresses.

## 4.2.2 DATA MEMORY ORGANIZATION AND ALIGNMENT

To maintain backward compatibility with PIC<sup>®</sup> MCU devices and improve Data Space memory usage efficiency, the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X instruction set supports both word and byte operations. As a consequence of byte accessibility, all Effective Address calculations are internally scaled to step through word-aligned memory. For example, the core recognizes that Post-Modified Register Indirect Addressing mode [Ws++] results in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

A data byte read, reads the complete word that contains the byte, using the LSb of any EA to determine which byte to select. The selected byte is placed onto the LSB of the data path. That is, data memory and registers are organized as two parallel, byte-wide entities with shared (word) address decode but separate write lines. Data byte writes only write to the corresponding side of the array or register that matches the byte address. All word accesses must be aligned to an even address. Misaligned word data fetches are not supported, so care must be taken when mixing byte and word operations, or translating from 8-bit MCU code. If a misaligned read or write is attempted, an address error trap is generated. If the error occurred on a read, the instruction underway is completed. If the error occurred on a write, the instruction is executed but the write does not occur. In either case, a trap is then executed, allowing the system and/or user application to examine the machine state prior to execution of the address Fault.

All byte loads into any W register are loaded into the LSB. The MSB is not modified.

A Sign-Extend (SE) instruction is provided to allow user applications to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, user applications can clear the MSB of any W register by executing a Zero-Extend (ZE) instruction on the appropriate address.

## 4.2.3 SFR SPACE

The first 4 Kbytes of the Near Data Space, from 0x0000 to 0x0FFF, is primarily occupied by Special Function Registers (SFRs). These are used by the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X core and peripheral modules for controlling the operation of the device.

SFRs are distributed among the modules that they control and are generally grouped together by module. Much of the SFR space contains unused addresses; these are read as '0'.

**Note:** The actual set of peripheral features and interrupts varies by the device. Refer to the corresponding device tables and pinout diagrams for device-specific information.

## 4.2.4 NEAR DATA SPACE

The 8-Kbyte area, between 0x0000 and 0x1FFF, is referred to as the Near Data Space. Locations in this space are directly addressable through a 13-bit absolute address field within all memory direct instructions. Additionally, the whole Data Space is addressable using MOV instructions, which support Memory Direct Addressing mode with a 16-bit address field, or by using Indirect Addressing mode using a working register as an Address Pointer.

#### REGISTER 14-2: ICxCON2: INPUT CAPTURE x CONTROL REGISTER 2 (CONTINUED)

- bit 4-0 SYNCSEL<4:0>: Input Source Select for Synchronization and Trigger Operation bits<sup>(4)</sup>

- 11111 = No Sync or Trigger source for ICx

- 11110 = Reserved

- 11101 = Reserved

- 11100 = CTMU module synchronizes or triggers ICx

- 11011 = ADC1 module synchronizes or triggers  $ICx^{(5)}$

- 11010 = CMP3 module synchronizes or triggers  $ICx^{(5)}$

- $11001 = CMP2 \text{ module synchronizes or triggers ICx}^{(5)}$

- 11000 = CMP1 module synchronizes or triggers  $ICx^{(5)}$

- 10111 = Reserved

- 10110 = Reserved

- 10101 = Reserved

- 10100 = Reserved

- 10011 = IC4 module synchronizes or triggers ICx

- 10010 = IC3 module synchronizes or triggers ICx

- 10001 = IC2 module synchronizes or triggers ICx

- 10000 = IC1 module synchronizes or triggers ICx

- 01111 = Timer5 synchronizes or triggers ICx

- 01110 = Timer4 synchronizes or triggers ICx

- 01101 = Timer3 synchronizes or triggers ICx (default)

- 01100 = Timer2 synchronizes or triggers ICx

- 01011 = Timer1 synchronizes or triggers ICx

- 01010 = PTGOx module synchronizes or triggers  $ICx^{(6)}$

- 01001 = Reserved

- 01000 = Reserved

- 00111 = Reserved

- 00110 = Reserved

- 00101 = Reserved

- 00100 = OC4 module synchronizes or triggers ICx

- 00011 = OC3 module synchronizes or triggers ICx

- 00010 = OC2 module synchronizes or triggers ICx

- 00001 = OC1 module synchronizes or triggers ICx

- 00000 = No Sync or Trigger source for ICx

- **Note 1:** The IC32 bit in both the Odd and Even IC must be set to enable Cascade mode.

- 2: The input source is selected by the SYNCSEL<4:0> bits of the ICxCON2 register.

- **3:** This bit is set by the selected input source (selected by SYNCSEL<4:0> bits). It can be read, set and cleared in software.

- 4: Do not use the ICx module as its own Sync or Trigger source.

- 5: This option should only be selected as a trigger source and not as a synchronization source.

- Each Input Capture x (ICx) module has one PTG input source. See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for more information.

PTGO8 = IC1

PTGO9 = IC2 PTGO10 = IC3 PTGO11 = IC4

| R/W-1           | R/W-1                                                                | R/W-0                                  | R/W-0                      | R/W-0                | R/W-0                     | R/W-0           | R/W-0  |

|-----------------|----------------------------------------------------------------------|----------------------------------------|----------------------------|----------------------|---------------------------|-----------------|--------|

| PENH            | PENL                                                                 | POLH                                   | POLL                       | PMOD1 <sup>(1)</sup> | PMOD0 <sup>(1)</sup>      | OVRENH          | OVRENL |

| bit 15          |                                                                      | •                                      |                            |                      |                           |                 | bit    |

| R/W-0           | R/W-0                                                                | R/W-0                                  | R/W-0                      | R/W-0                | R/W-0                     | R/W-0           |        |

| -               | -                                                                    | -                                      |                            | -                    | -                         | -               | R/W-0  |

| OVRDAT1         | OVRDAT0                                                              | FLTDAT1                                | FLTDAT0                    | CLDAT1               | CLDAT0                    | SWAP            | OSYNC  |

| bit 7           |                                                                      |                                        |                            |                      |                           |                 | bit    |

| Legend:         |                                                                      |                                        |                            |                      |                           |                 |        |

| R = Readable    | bit                                                                  | W = Writable                           | bit                        | U = Unimpler         | nented bit, read          | l as '0'        |        |

| -n = Value at F | POR                                                                  | '1' = Bit is set                       |                            | '0' = Bit is cle     | ared                      | x = Bit is unkr | nown   |

| bit 15          |                                                                      | xH Output Pin                          | Ownorshin hit              |                      |                           |                 |        |

| bit 15          |                                                                      | odule controls                         | •                          |                      |                           |                 |        |

|                 |                                                                      | dule controls F                        |                            |                      |                           |                 |        |

| bit 14          |                                                                      | L Output Pin                           | •                          |                      |                           |                 |        |

|                 | 1 = PWMx mo                                                          | odule controls                         | PWMxL pin                  |                      |                           |                 |        |

|                 | 0 = GPIO mo                                                          | dule controls F                        | WMxL pin                   |                      |                           |                 |        |

| bit 13          | POLH: PWM                                                            | xH Output Pin                          | Polarity bit               |                      |                           |                 |        |

|                 |                                                                      | oin is active-low                      |                            |                      |                           |                 |        |

|                 |                                                                      | oin is active-hig                      | •                          |                      |                           |                 |        |

| bit 12          |                                                                      | L Output Pin F                         | •                          |                      |                           |                 |        |

|                 |                                                                      | in is active-low<br>in is active-hig   |                            |                      |                           |                 |        |

| bit 11-10       | PMOD<1:0>:                                                           | PWMx # I/O F                           | in Mode bits <sup>(1</sup> | )                    |                           |                 |        |

|                 | 11 = Reserve                                                         | ,                                      |                            |                      |                           |                 |        |

|                 |                                                                      | /O pin pair is ir<br>/O pin pair is ir |                            |                      |                           |                 |        |

|                 |                                                                      | O pin pair is in<br>O pin pair is ir   |                            |                      |                           |                 |        |

| bit 9           |                                                                      | verride Enable                         | •                          |                      |                           |                 |        |

|                 |                                                                      | <1> controls or                        |                            |                      |                           |                 |        |

|                 |                                                                      | nerator contro                         | •                          | •                    |                           |                 |        |

| bit 8           | OVRENL: Ov                                                           | erride Enable                          | for PWMxL Pir              | n bit                |                           |                 |        |

|                 | 1 = OVRDAT                                                           | <0> controls or                        | utput on PWM               | xL pin               |                           |                 |        |

|                 | •                                                                    | nerator contro                         |                            |                      |                           |                 |        |

| bit 7-6         |                                                                      |                                        |                            |                      | de is Enabled b           |                 |        |

|                 |                                                                      |                                        |                            |                      | by OVRDAT<<br>by OVRDAT<0 |                 |        |

| bit 5-4         | FLTDAT<1:0>: Data for PWMxH and PWMxL Pins if FLTMOD is Enabled bits |                                        |                            |                      |                           |                 |        |

|                 | If Fault is active                                                   | ve, PWMxH is                           | driven to the s            | tate specified       | by FLTDAT<1>.             |                 |        |

|                 | If Fault is active                                                   | ve, PWMxL is                           | driven to the s            | tate specified b     | by FLTDAT<0>.             |                 |        |

| bit 3-2         | CLDAT<1:0>                                                           | : Data for PWN                         | /IxH and PWM               | xL Pins if CLM       | 10D is Enabled            | bits            |        |

|                 |                                                                      |                                        |                            | •                    | ecified by CLDA           |                 |        |

|                 |                                                                      | IS AULIVE. F VVI                       |                            |                      |                           |                 |        |

| Note 1: The     |                                                                      |                                        |                            |                      | enabled (PTEN             |                 |        |

# REGISTER 16-13: IOCONx: PWMx I/O CONTROL REGISTER<sup>(2)</sup>

2: If the PWMLOCK Configuration bit (FOSCSEL<6>) is a '1', the IOCONx register can only be written after the unlock sequence has been executed.

| U-0    | U-0   | U-0   | U-0   | U-0   | U-0   | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-------|-------|-------|-------|

| —      | —     | —     | —     | —     | —     | AMSK9 | AMSK8 |

| bit 15 |       |       |       |       |       |       | bit 8 |

|        |       |       |       |       |       |       |       |

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| AMSK7  | AMSK6 | AMSK5 | AMSK4 | AMSK3 | AMSK2 | AMSK1 | AMSK0 |

| bit 7  |       |       |       |       |       |       | bit 0 |

### REGISTER 19-3: I2CxMSK: I2Cx SLAVE MODE ADDRESS MASK REGISTER

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-10 Unimplemented: Read as '0'

bit 9-0

AMSK<9:0>: Address Mask Select bits

For 10-Bit Address:

1 = Enables masking for bit Ax of incoming message address; bit match is not required in this position

0 = Disables masking for bit Ax; bit match is required in this position

For 7-Bit Address (I2CxMSK<6:0> only):

1 = Enables masking for bit Ax + 1 of incoming message address; bit match is not required in this position

0 = Disables masking for bit Ax + 1; bit match is required in this position

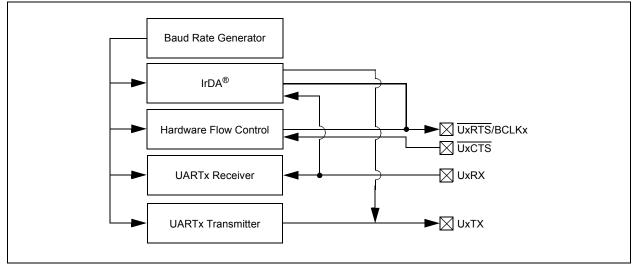

# 20.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "UART" (DS70582) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X family of devices contains two UART modules.

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X device family. The UART is a full-duplex, asynchronous system that can communicate with peripheral devices, such as personal computers, LIN/J2602, RS-232 and RS-485 interfaces. The module also supports a hardware flow control option with the UxCTS and UxRTS pins, and also includes an IrDA<sup>®</sup> encoder and decoder.

Note: <u>Hardware</u> flow control using UxRTS and UxCTS is not available on all pin count devices. See the "**Pin Diagrams**" section for availability.

The primary features of the UARTx module are:

- Full-Duplex, 8 or 9-Bit Data Transmission through the UxTX and UxRX Pins

- Even, Odd or No Parity Options (for 8-bit data)

- One or Two Stop bits

- Hardware Flow Control Option with UxCTS and UxRTS Pins

- Fully Integrated Baud Rate Generator with 16-Bit Prescaler

- Baud Rates Ranging from 4.375 Mbps to 67 bps at 16x mode at 70 MIPS

- Baud Rates Ranging from 17.5 Mbps to 267 bps at 4x mode at 70 MIPS

- 4-Deep First-In First-Out (FIFO) Transmit Data Buffer

- 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-bit mode with Address Detect (9th bit = 1)

- · Transmit and Receive Interrupts

- A Separate Interrupt for all UARTx Error Conditions

- · Loopback mode for Diagnostic Support

- · Support for Sync and Break Characters

- Support for Automatic Baud Rate Detection

- IrDA<sup>®</sup> Encoder and Decoder Logic

- 16x Baud Clock Output for IrDA Support

A simplified block diagram of the UARTx module is shown in Figure 20-1. The UARTx module consists of these key hardware elements:

- · Baud Rate Generator

- Asynchronous Transmitter

- Asynchronous Receiver

#### FIGURE 20-1: UARTx SIMPLIFIED BLOCK DIAGRAM

© 2011-2013 Microchip Technology Inc.

## DIGITAL FILTER INTERCONNECT BLOCK DIAGRAM

NOTES:

| Base<br>Instr<br># | Assembly<br>Mnemonic |       | Assembly Syntax         | Description                              | # of<br>Words | # of<br>Cycles <sup>(2)</sup> | Status Flags<br>Affected |

|--------------------|----------------------|-------|-------------------------|------------------------------------------|---------------|-------------------------------|--------------------------|

| 1                  | ADD                  | ADD   | Acc <sup>(1)</sup>      | Add Accumulators                         | 1             | 1                             | OA,OB,SA,SB              |

|                    |                      | ADD   | f                       | f = f + WREG                             | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | ADD   | f,WREG                  | WREG = f + WREG                          | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | ADD   | #lit10,Wn               | Wd = lit10 + Wd                          | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | ADD   | Wb,Ws,Wd                | Wd = Wb + Ws                             | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | ADD   | Wb,#lit5,Wd             | Wd = Wb + lit5                           | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | ADD   | Wso,#Slit4,Acc          | 16-bit Signed Add to Accumulator         | 1             | 1                             | OA,OB,SA,SE              |

| 2                  | ADDC                 | ADDC  | f                       | f = f + WREG + (C)                       | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | ADDC  | f,WREG                  | WREG = $f + WREG + (C)$                  | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | ADDC  | #lit10,Wn               | Wd = Iit10 + Wd + (C)                    | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | ADDC  | Wb,Ws,Wd                | Wd = Wb + Ws + (C)                       | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | ADDC  | Wb,#lit5,Wd             | Wd = Wb + lit5 + (C)                     | 1             | 1                             | C,DC,N,OV,Z              |

| 3                  | AND                  | AND   | f                       | f = f .AND. WREG                         | 1             | 1                             | N,Z                      |

|                    |                      | AND   | f,WREG                  | WREG = f .AND. WREG                      | 1             | 1                             | N,Z                      |

|                    |                      | AND   | #lit10,Wn               | Wd = lit10 .AND. Wd                      | 1             | 1                             | N,Z                      |

|                    |                      | AND   | Wb,Ws,Wd                | Wd = Wb .AND. Ws                         | 1             | 1                             | N,Z                      |

|                    |                      | AND   | Wb,#lit5,Wd             | Wd = Wb .AND. lit5                       | 1             | 1                             | N,Z                      |

| 4                  | ASR                  | ASR   | f                       | f = Arithmetic Right Shift f             | 1             | 1                             | C,N,OV,Z                 |

|                    | non                  | ASR   | f,WREG                  | WREG = Arithmetic Right Shift f          | 1             | 1                             | C,N,OV,Z                 |

|                    |                      | ASR   | Ws,Wd                   | Wd = Arithmetic Right Shift Ws           | 1             | 1                             | C,N,OV,Z                 |

|                    |                      | ASR   | Wb, Wns, Wnd            | Wnd = Arithmetic Right Shift Wb by Wns   | 1             | 1                             | N,Z                      |

|                    |                      | ASR   | Wb,#lit5,Wnd            | Wind = Arithmetic Right Shift Wb by Wils | 1             | 1                             | N,Z                      |

| 5                  | BCLR                 | BCLR  | f,#bit4                 | Bit Clear f                              | 1             | 1                             | None                     |

| 5                  | BCLIK                |       |                         | Bit Clear Ws                             | 1             | 1                             | None                     |

| 6                  | DD 3                 | BCLR  | Ws,#bit4                |                                          | 1             |                               | None                     |

| 6                  | BRA                  | BRA   | C,Expr                  | Branch if Carry                          |               | 1 (4)                         |                          |

|                    |                      | BRA   | GE, Expr                | Branch if greater than or equal          | 1             | 1 (4)                         | None                     |

|                    |                      | BRA   | GEU, Expr               | Branch if unsigned greater than or equal | 1             | 1 (4)                         | None                     |

|                    |                      | BRA   | GT, Expr                | Branch if greater than                   | 1             | 1 (4)                         | None                     |

|                    |                      | BRA   | GTU, Expr               | Branch if unsigned greater than          | 1             | 1 (4)                         | None                     |

|                    |                      | BRA   | LE,Expr                 | Branch if less than or equal             | 1             | 1 (4)                         | None                     |

|                    |                      | BRA   | LEU,Expr                | Branch if unsigned less than or equal    | 1             | 1 (4)                         | None                     |

|                    |                      | BRA   | LT,Expr                 | Branch if less than                      | 1             | 1 (4)                         | None                     |

|                    |                      | BRA   | LTU, Expr               | Branch if unsigned less than             | 1             | 1 (4)                         | None                     |

|                    |                      | BRA   | N,Expr                  | Branch if Negative                       | 1             | 1 (4)                         | None                     |

|                    |                      | BRA   | NC,Expr                 | Branch if Not Carry                      | 1             | 1 (4)                         | None                     |

|                    |                      | BRA   | NN,Expr                 | Branch if Not Negative                   | 1             | 1 (4)                         | None                     |

|                    |                      | BRA   | NOV,Expr                | Branch if Not Overflow                   | 1             | 1 (4)                         | None                     |

|                    |                      | BRA   | NZ,Expr                 | Branch if Not Zero                       | 1             | 1 (4)                         | None                     |

|                    |                      | BRA   | OA, Expr(1)             | Branch if Accumulator A overflow         | 1             | 1 (4)                         | None                     |

|                    |                      | BRA   | OB, Expr <sup>(1)</sup> | Branch if Accumulator B overflow         | 1             | 1 (4)                         | None                     |

|                    |                      | BRA   | OV, Expr(1)             | Branch if Overflow                       | 1             | 1 (4)                         | None                     |

|                    |                      | BRA   | SA, Expr <sup>(1)</sup> | Branch if Accumulator A saturated        | 1             | 1 (4)                         | None                     |

|                    |                      | BRA   | SB, Expr <sup>(1)</sup> | Branch if Accumulator B saturated        | 1             | 1 (4)                         | None                     |

|                    |                      | BRA   | Expr                    | Branch Unconditionally                   | 1             | 4                             | None                     |

|                    |                      | BRA   | Z,Expr                  | Branch if Zero                           | 1             | 1 (4)                         | None                     |

|                    |                      | BRA   | Wn                      | Computed Branch                          | 1             | 4                             | None                     |

| 7                  | BSET                 | BSET  | f,#bit4                 | Bit Set f                                | 1             | 1                             | None                     |

|                    |                      | BSET  | Ws,#bit4                | Bit Set Ws                               | 1             | 1                             | None                     |

| 8                  | BSW                  | BSW.C | Ws,Wb                   | Write C bit to Ws <wb></wb>              | 1             | 1                             | None                     |

|                    |                      | BSW.Z | Ws,Wb                   | Write Z bit to Ws <wb></wb>              | 1             | 1                             | None                     |

### TABLE 28-2: INSTRUCTION SET OVERVIEW

Note 1: These instructions are available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

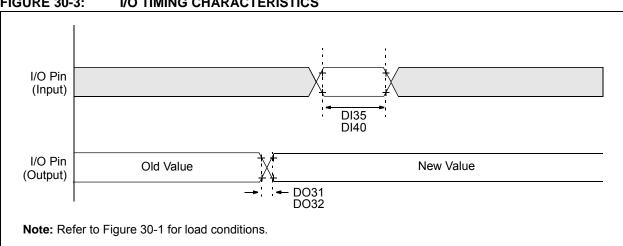

#### **FIGURE 30-3: I/O TIMING CHARACTERISTICS**

#### TABLE 30-21: I/O TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                   | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature } -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |                     |      |       |            |

|--------------------|--------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|------------|

| Param<br>No.       | Symbol | Characteristic                    | Min.                                                                                                                                                                                                                                                                             | Тур. <sup>(1)</sup> | Max. | Units | Conditions |

| DO31               | TioR   | Port Output Rise Time             |                                                                                                                                                                                                                                                                                  | 5                   | 10   | ns    |            |

| DO32               | TIOF   | Port Output Fall Time             | _                                                                                                                                                                                                                                                                                | 5                   | 10   | ns    |            |

| DI35               | TINP   | INTx Pin High or Low Time (input) | 20                                                                                                                                                                                                                                                                               | _                   | _    | ns    |            |

| DI40               | Trbp   | CNx High or Low Time (input)      | 2                                                                                                                                                                                                                                                                                | _                   | _    | Тсү   |            |

Note 1: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

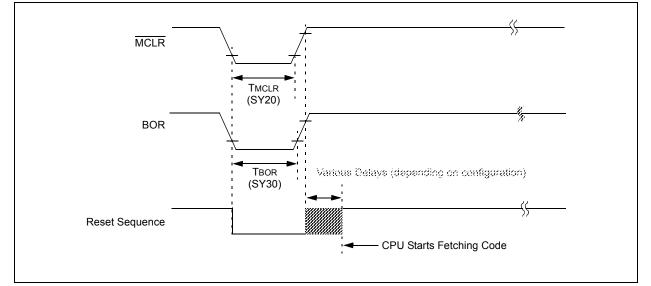

#### FIGURE 30-4: BOR AND MASTER CLEAR RESET TIMING CHARACTERISTICS

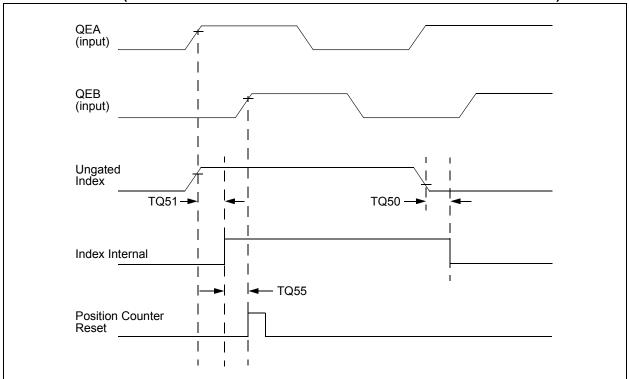

### FIGURE 30-13: QEI MODULE INDEX PULSE TIMING CHARACTERISTICS (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

## TABLE 30-32: QEI INDEX PULSE TIMING REQUIREMENTS (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

| AC CHARACTERISTICS |        |                                                                     | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |      |       |                                                         |

|--------------------|--------|---------------------------------------------------------------------|-------------------------------------------------------|------|-------|---------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>                                       | Min.                                                  | Max. | Units | Conditions                                              |

| TQ50               | TqiL   | Filter Time to Recognize Low,<br>with Digital Filter                | 3 * N * Tcy                                           | _    | ns    | N = 1, 2, 4, 16, 32, 64,<br>128 and 256 <b>(Note 2)</b> |

| TQ51               | TqiH   | Filter Time to Recognize High,<br>with Digital Filter               | 3 * N * Tcy                                           | —    | ns    | N = 1, 2, 4, 16, 32, 64,<br>128 and 256 <b>(Note 2)</b> |

| TQ55               | Tqidxr | Index Pulse Recognized to Position<br>Counter Reset (ungated index) | 3 TCY                                                 | —    | ns    |                                                         |

**Note 1:** These parameters are characterized but not tested in manufacturing.

2: Alignment of index pulses to QEA and QEB is shown for position counter Reset timing only. Shown for forward direction only (QEA leads QEB). Same timing applies for reverse direction (QEA lags QEB) but index pulse recognition occurs on the falling edge.

| AC CHARACTERISTICS   |                                          |                                             | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |     |     |     |  |

|----------------------|------------------------------------------|---------------------------------------------|-------------------------------------------------------|-----|-----|-----|--|

| Maximum<br>Data Rate | Master<br>Transmit Only<br>(Half-Duplex) | Master<br>Transmit/Receive<br>(Full-Duplex) | Slave<br>Transmit/Receive<br>(Full-Duplex)            | CKE | СКР | SMP |  |

| 15 MHz               | Table 30-42                              | _                                           | _                                                     | 0,1 | 0,1 | 0,1 |  |

| 10 MHz               | —                                        | Table 30-43                                 | —                                                     | 1   | 0,1 | 1   |  |

| 10 MHz               | —                                        | Table 30-44                                 | —                                                     | 0   | 0,1 | 1   |  |

| 15 MHz               | —                                        | —                                           | Table 30-45                                           | 1   | 0   | 0   |  |

| 11 MHz               | —                                        | —                                           | Table 30-46                                           | 1   | 1   | 0   |  |

| 15 MHz               | _                                        | —                                           | Table 30-47                                           | 0   | 1   | 0   |  |

| 11 MHz               | _                                        | _                                           | Table 30-48                                           | 0   | 0   | 0   |  |

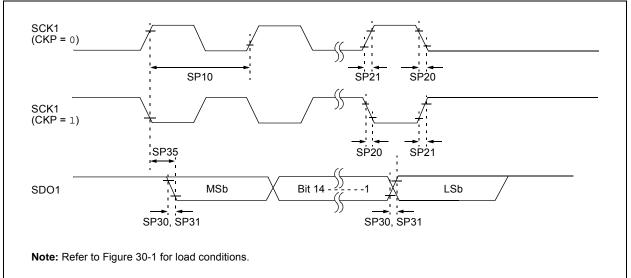

### TABLE 30-41: SPI1 MAXIMUM DATA/CLOCK RATE SUMMARY

## FIGURE 30-22: SPI1 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 0) TIMING CHARACTERISTICS

| AC CHARACTERISTICS |        |                                                                                                           | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)}^{(1)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |         |       |       | ≤ +85°C for Industrial               |

|--------------------|--------|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------|-------|--------------------------------------|

| Param<br>No.       | Symbol | Characteristic                                                                                            | Min.                                                                                                                                                                                                                                                                                        | Тур.    | Max.  | Units | Conditions                           |

|                    |        | Cloci                                                                                                     | k Paramet                                                                                                                                                                                                                                                                                   | ters    |       |       |                                      |

| AD50               | TAD    | ADC Clock Period                                                                                          | 117.6                                                                                                                                                                                                                                                                                       | _       | _     | ns    |                                      |

| AD51               | tRC    | ADC Internal RC Oscillator Period <sup>(2)</sup>                                                          |                                                                                                                                                                                                                                                                                             | 250     | _     | ns    |                                      |

|                    |        | Conv                                                                                                      | version R                                                                                                                                                                                                                                                                                   | ate     |       |       |                                      |

| AD55               | tCONV  | Conversion Time                                                                                           | _                                                                                                                                                                                                                                                                                           | 14 Tad  |       | ns    |                                      |

| AD56               | FCNV   | Throughput Rate                                                                                           | _                                                                                                                                                                                                                                                                                           | _       | 500   | ksps  |                                      |

| AD57a              | TSAMP  | Sample Time when Sampling any ANx Input                                                                   | 3 Tad                                                                                                                                                                                                                                                                                       | —       | _     |       |                                      |

| AD57b              | TSAMP  | Sample Time when Sampling the Op<br>Amp Outputs (Configuration A and<br>Configuration B) <sup>(4,5)</sup> | 3 Tad                                                                                                                                                                                                                                                                                       | —       | -     |       |                                      |

|                    |        | Timin                                                                                                     | g Parame                                                                                                                                                                                                                                                                                    | ters    |       |       |                                      |

| AD60               | tPCS   | Conversion Start from Sample<br>Trigger <sup>(2,3)</sup>                                                  | 2 Tad                                                                                                                                                                                                                                                                                       | -       | 3 Tad | —     | Auto-convert trigger is not selected |

| AD61               | tPSS   | Sample Start from Setting<br>Sample (SAMP) bit <sup>(2,3)</sup>                                           | 2 Tad                                                                                                                                                                                                                                                                                       | —       | 3 Tad |       |                                      |

| AD62               | tcss   | Conversion Completion to<br>Sample Start (ASAM = 1) <sup>(2,3)</sup>                                      |                                                                                                                                                                                                                                                                                             | 0.5 Tad | —     |       |                                      |

| AD63               | tdpu   | Time to Stabilize Analog Stage<br>from ADC Off to ADC On <sup>(2,3)</sup>                                 | —                                                                                                                                                                                                                                                                                           | —       | 20    | μS    | (Note 6)                             |

## TABLE 30-60: ADC CONVERSION (12-BIT MODE) TIMING REQUIREMENTS

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

- 2: Parameters are characterized but not tested in manufacturing.

- **3:** Because the sample caps will eventually lose charge, clock rates below 10 kHz may affect linearity performance, especially at elevated temperatures.

- 4: See Figure 25-6 for configuration information.

- 5: See Figure 25-7 for configuration information.

- **6:** The parameter, tDPU, is the time required for the ADC module to stabilize at the appropriate level when the module is turned on (ADON (AD1CON1<15>) = 1). During this time, the ADC result is indeterminate.

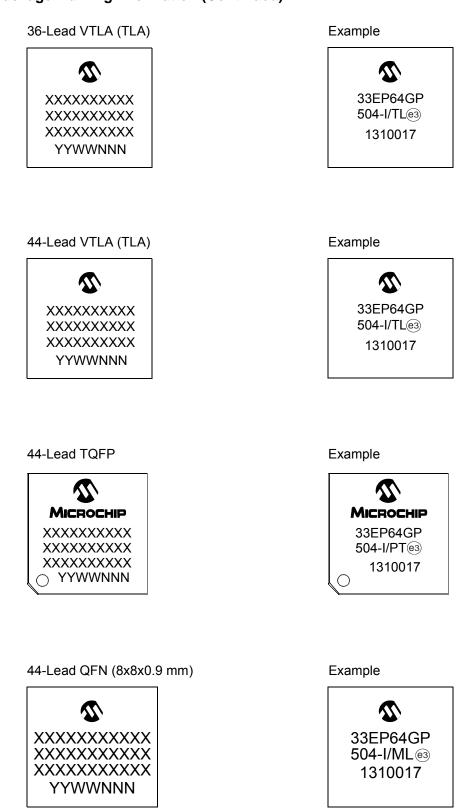

#### 33.1 Package Marking Information (Continued)

28-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

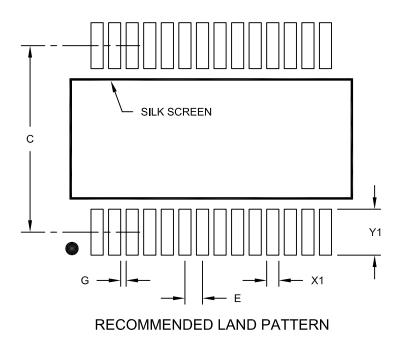

|                          | Units            | Ν    |          | S    |

|--------------------------|------------------|------|----------|------|

| Dimensior                | Dimension Limits |      |          | MAX  |

| Contact Pitch            | E                |      | 0.65 BSC |      |

| Contact Pad Spacing      | С                |      | 7.20     |      |

| Contact Pad Width (X28)  | X1               |      |          | 0.45 |

| Contact Pad Length (X28) | Y1               |      |          | 1.75 |

| Distance Between Pads    | G                | 0.20 |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2073A

## **Revision C (December 2011)**

This revision includes typographical and formatting changes throughout the data sheet text.

In addition, where applicable, new sections were added to each peripheral chapter that provide information and links to related resources, as well as helpful tips. For examples, see Section 20.1 "UART Helpful Tips" and Section 3.6 "CPU Resources". All occurrences of TLA were updated to VTLA throughout the document, with the exception of the pin diagrams (updated diagrams were not available at time of publication).

A new chapter, Section 31.0 "DC and AC Device Characteristics Graphs", was added.

All other major changes are referenced by their respective section in Table A-2.

| Section Name                                                                                                                                                            | Update Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "16-bit Microcontrollers<br>and Digital Signal<br>Controllers (up to<br>256-Kbyte Flash and<br>32-Kbyte SRAM) with High-<br>Speed PWM, Op amps, and<br>Advanced Analog" | The content on the first page of this section was extensively reworked to provide the reader with the key features and functionality of this device family in an "at-a-glance" format.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Section 1.0 "Device<br>Overview"                                                                                                                                        | Updated the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X, and<br>PIC24EPXXXGP/MC20X Block Diagram (see Figure 1-1), which now contains a CPU<br>block and a reference to the CPU diagram.<br>Updated the description and Note references in the Pinout I/O Descriptions for these                                                                                                                                                                                                                                                                                                                                                              |

| Section 2.0 "Guidelines for<br>Getting Started with 16-bit<br>Digital Signal Controllers<br>and Microcontrollers"                                                       | pins: C1IN2-, C2IN2-, C3IN2-, OA1OUT, OA2OUT, and OA3OUT (see Table 1-1).<br>Updated the Recommended Minimum Connection diagram (see Figure 2-1).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Section 3.0 "CPU"                                                                                                                                                       | Updated the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X, and<br>PIC24EPXXXGP/MC20X CPU Block Diagram (see Figure 3-1).<br>Updated the Status register definition in the Programmer's Model (see Figure 3-2).                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Section 4.0 "Memory<br>Organization"                                                                                                                                    | Updated the Data Memory Maps (see Figure 4-6 and Figure 4-11).<br>Removed the DCB<1:0> bits from the OC1CON2, OC2CON2, OC3CON2, and<br>OC4CON2 registers in the Output Compare 1 Through Output Compare 4 Register<br>Map (see Table 4-10).<br>Added the TRIG1 and TRGCON1 registers to the PWM Generator 1 Register Map<br>(see Table 4-13).<br>Added the TRIG2 and TRGCON2 registers to the PWM Generator 2 Register Map<br>(see Table 4-14).<br>Added the TRIG3 and TRGCON3 registers to the PWM Generator 3 Register Map<br>(see Table 4-15).<br>Updated the second note in Section 4.7.1 "Bit-Reversed Addressing<br>Implementation". |

| Section 8.0 "Direct Memory<br>Access (DMA)"                                                                                                                             | Updated the DMA Controller diagram (see Figure 8-1).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Section 14.0 "Input<br>Capture"                                                                                                                                         | Updated the bit values for the ICx clock source of the ICTSEL<12:10> bits in the ICxCON1 register (see Register 14-1).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Section 15.0 "Output<br>Compare"                                                                                                                                        | Updated the bit values for the OCx clock source of the OCTSEL<2:0> bits in the OCxCON1 register (see Register 15-1).<br>Removed the DCB<1:0> bits from the Output Compare x Control Register 2 (see Register 15-2).                                                                                                                                                                                                                                                                                                                                                                                                                        |

TABLE A-2: MAJOR SECTION UPDATES

| Section Name                                                                                              | Update Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Section 16.0 "High-Speed<br>PWM Module<br>(dsPIC33EPXXXMC20X/50X<br>and PIC24EPXXXMC20X<br>Devices Only)" | Updated the High-Speed PWM Module Register Interconnection Diagram (see Figure 16-2).<br>Added the TRGCONx and TRIGx registers (see Register 16-12 and Register 16-14, respectively).                                                                                                                                                                                                                                                                                                         |

| Section 21.0 "Enhanced<br>CAN (ECAN™) Module<br>(dsPIC33EPXXXGP/MC50X<br>Devices Only)"                   | Updated the CANCKS bit value definitions in CiCTRL1: ECAN Control Register 1 (see Register 21-1).                                                                                                                                                                                                                                                                                                                                                                                             |

| Section 22.0 "Charge Time<br>Measurement Unit (CTMU)"                                                     | Updated the IRNG<1:0> bit value definitions and added Note 2 in the CTMU Current Control Register (see Register 22-3).                                                                                                                                                                                                                                                                                                                                                                        |

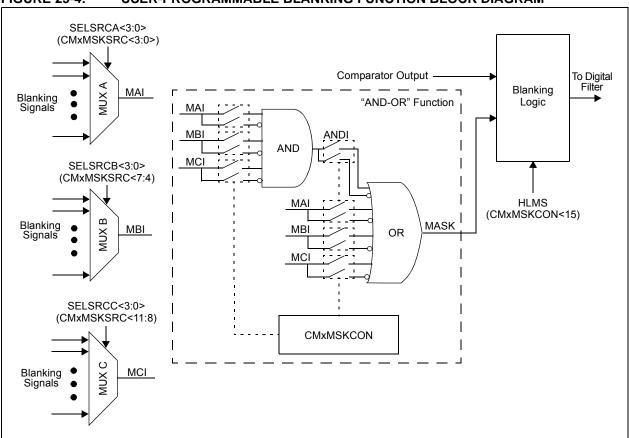

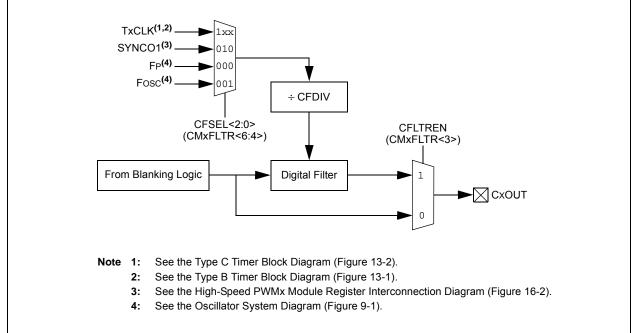

| Section 25.0 "Op amp/<br>Comparator Module"                                                               | Updated the Op amp/Comparator I/O Operating Modes Diagram (see Figure 25-1).<br>Updated the User-programmable Blanking Function Block Diagram (see Figure 25-3).<br>Updated the Digital Filter Interconnect Block Diagram (see Figure 25-4).<br>Added <b>Section 25.1 "Op amp Application Considerations</b> ".<br>Added Note 2 to the Comparator Control Register (see Register 25-2).<br>Updated the bit definitions in the Comparator Mask Gating Control Register (see<br>Register 25-5). |

| Section 27.0 "Special<br>Features"                                                                        | Updated the FICD Configuration Register, updated Note 1, and added Note 3 in the Configuration Byte Register Map (see Table 27-1).<br>Added <b>Section 27.2 "User ID Words"</b> .                                                                                                                                                                                                                                                                                                             |

| Section 30.0 "Electrical<br>Characteristics"                                                              | <ul> <li>Updated the following Absolute Maximum Ratings:</li> <li>Maximum current out of Vss pin</li> <li>Maximum current into VDD pin</li> <li>Added Note 1 to the Operating MIPS vs. Voltage (see Table 30-1).</li> </ul>                                                                                                                                                                                                                                                                   |

|                                                                                                           | Updated all Idle Current (IIDLE) Typical and Maximum DC Characteristics values (see Table 30-7).                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                           | Updated all Doze Current (IDOZE) Typical and Maximum DC Characteristics values (see Table 30-9).                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                           | Added Note 2, removed Parameter CM24, updated the Typical values Parameters CM10, CM20, CM21, CM32, CM41, CM44, and CM45, and updated the Minimum values for CM40 and CM41, and the Maximum value for CM40 in the AC/DC Characteristics: Op amp/Comparator (see Table 30-14).                                                                                                                                                                                                                 |

|                                                                                                           | Updated Note 2 and the Typical value for Parameter VR310 in the Op amp/<br>Comparator Reference Voltage Settling Time Specifications (see Table 30-15).                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                           | Added Note 1, removed Parameter VRD312, and added Parameter VRD314 to the Op amp/Comparator Voltage Reference DC Specifications (see Table 30-16).                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                           | Updated the Minimum, Typical, and Maximum values for Internal LPRC Accuracy (see Table 30-22).                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                           | Updated the Minimum, Typical, and Maximum values for Parameter SY37 in the Reset, Watchdog Timer, Oscillator Start-up Timer, Power-up Timer Timing Requirements (see Table 30-24).                                                                                                                                                                                                                                                                                                            |

|                                                                                                           | The Maximum Data Rate values were updated for the SPI2 Maximum Data/Clock Rate Summary (see Table 30-35)                                                                                                                                                                                                                                                                                                                                                                                      |

## TABLE A-2: MAJOR SECTION UPDATES (CONTINUED)