Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

|                            |                                                                                |

| Speed                      | 70 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                  |

| Number of I/O              | 35                                                                             |

| Program Memory Size        | 256KB (85.5K x 24)                                                             |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 16                                                                       |

| /oltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 9x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 48-UFQFN Exposed Pad                                                           |

| Supplier Device Package    | 48-UQFN (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep256mc204-i-mv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 3.7 CPU Control Registers

#### REGISTER 3-1: SR: CPU STATUS REGISTER

| R/W-0             | R/W-0             | R/W-0               | R/W-0               | R/C-0              | R/C-0              | R-0               | R/W-0 |

|-------------------|-------------------|---------------------|---------------------|--------------------|--------------------|-------------------|-------|

| OA <sup>(1)</sup> | OB <sup>(1)</sup> | SA <sup>(1,4)</sup> | SB <sup>(1,4)</sup> | OAB <sup>(1)</sup> | SAB <sup>(1)</sup> | DA <sup>(1)</sup> | DC    |

| bit 15            |                   |                     |                     |                    |                    |                   | bit 8 |

| R/W-0 <sup>(2,3)</sup> | R/W-0 <sup>(2,3)</sup> | R/W-0 <sup>(2,3)</sup> | R-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|------------------------|------------------------|------------------------|-----|-------|-------|-------|-------|

| IPL2                   | IPL1                   | IPL0                   | RA  | N     | OV    | Z     | С     |

| bit 7                  |                        |                        |     |       |       |       | bit 0 |

| Legend:           | C = Clearable bit |                             |                    |

|-------------------|-------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1'= Bit is set   | '0' = Bit is cleared        | x = Bit is unknown |

bit 15 OA: Accumulator A Overflow Status bit<sup>(1)</sup>

1 = Accumulator A has overflowed

0 = Accumulator A has not overflowed

bit 14 **OB:** Accumulator B Overflow Status bit<sup>(1)</sup>

1 = Accumulator B has overflowed

0 = Accumulator B has not overflowed

bit 13 **SA:** Accumulator A Saturation 'Sticky' Status bit<sup>(1,4)</sup>

1 = Accumulator A is saturated or has been saturated at some time

0 = Accumulator A is not saturated

bit 12 SB: Accumulator B Saturation 'Sticky' Status bit (1,4)

1 = Accumulator B is saturated or has been saturated at some time

0 = Accumulator B is not saturated

bit 11 OAB: OA || OB Combined Accumulator Overflow Status bit (1)

1 = Accumulators A or B have overflowed

0 = Neither Accumulators A or B have overflowed

bit 10 SAB: SA || SB Combined Accumulator 'Sticky' Status bit (1)

1 = Accumulators A or B are saturated or have been saturated at some time

0 = Neither Accumulators A or B are saturated

bit 9 **DA:** DO Loop Active bit<sup>(1)</sup>

1 = DO loop is in progress

0 = DO loop is not in progress

bit 8 **DC:** MCU ALU Half Carry/Borrow bit

- 1 = A carry-out from the 4th low-order bit (for byte-sized data) or 8th low-order bit (for word-sized data) of the result occurred

- 0 = No carry-out from the 4th low-order bit (for byte-sized data) or 8th low-order bit (for word-sized data) of the result occurred

- Note 1: This bit is available on dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices only.

- 2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL, if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- 3: The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

- **4:** A data write to the SR register can modify the SA and SB bits by either a data write to SA and SB or by clearing the SAB bit. To avoid a possible SA or SB bit write race condition, the SA and SB bits should not be modified using bit operations.

TABLE 4-9: INPUT CAPTURE 1 THROUGH INPUT CAPTURE 4 REGISTER MAP

| File Name | Addr. | Bit 15                                  | Bit 14                                    | Bit 13 | Bit 12 | Bit 11    | Bit 10 | Bit 9 | Bit 8        | Bit 7       | Bit 6    | Bit 5 | Bit 4               | Bit 3 | Bit 2     | Bit 1    | Bit 0 | All<br>Resets |

|-----------|-------|-----------------------------------------|-------------------------------------------|--------|--------|-----------|--------|-------|--------------|-------------|----------|-------|---------------------|-------|-----------|----------|-------|---------------|

| IC1CON1   | 0140  | _                                       | _                                         | ICSIDL | I      | CTSEL<2:0 | >      | _     | _            | _           | ICI<1    | :0>   | ICOV ICBNE ICM<2:0> |       |           |          | 0000  |               |

| IC1CON2   | 0142  | _                                       | _                                         | _      | _      | _         | -      | _     | IC32         | ICTRIG      | TRIGSTAT | _     |                     | SY    | NCSEL<4:  | 0>       |       | 000D          |

| IC1BUF    | 0144  |                                         |                                           |        |        |           |        | Inpu  | ıt Capture 1 | Buffer Reg  | gister   |       |                     |       |           |          |       | xxxx          |

| IC1TMR    | 0146  |                                         |                                           |        |        |           |        |       | Input Capt   | ure 1 Timer | •        |       |                     |       |           |          |       | 0000          |

| IC2CON1   | 0148  | _                                       | _                                         | ICSIDL | 10     | CTSEL<2:0 | >      | _     | -            | _           | ICI<1    | :0>   | ICOV ICBNE ICM<2:0> |       |           |          | 0000  |               |

| IC2CON2   | 014A  | IC32   ICTRIG   TRIGSTAT _ SYNCSEL<4:0> |                                           |        |        |           |        |       |              | 000D        |          |       |                     |       |           |          |       |               |

| IC2BUF    | 014C  |                                         | Input Capture 2 Buffer Register           |        |        |           |        |       |              |             |          |       |                     | xxxx  |           |          |       |               |

| IC2TMR    | 014E  |                                         |                                           |        |        |           |        |       | Input Capt   | ure 2 Timer | •        |       |                     |       |           |          |       | 0000          |

| IC3CON1   | 0150  | _                                       | _                                         | ICSIDL | 10     | CTSEL<2:0 | >      | -     | 1            | -           | ICI<1    | 1:0>  | ICOV                | ICBNE |           | ICM<2:0> |       | 0000          |

| IC3CON2   | 0152  | _                                       | _                                         | _      | -      | _         | ı      | -     | IC32         | ICTRIG      | TRIGSTAT | -     |                     | SY    | 'NCSEL<4: | 0>       |       | 000D          |

| IC3BUF    | 0154  |                                         |                                           |        |        |           |        | Inpu  | ut Capture 3 | Buffer Reg  | gister   |       |                     |       |           |          |       | xxxx          |

| IC3TMR    | 0156  |                                         |                                           |        |        |           |        |       | Input Capt   | ure 3 Timer | •        |       |                     |       |           |          |       | 0000          |

| IC4CON1   | 0158  | _                                       | _                                         | ICSIDL | 10     | CTSEL<2:0 | >      | -     | 1            | -           | ICI<1    | 1:0>  | ICOV                | ICBNE |           | ICM<2:0> |       | 0000          |

| IC4CON2   | 015A  | _                                       | IC32   ICTRIG   TRIGSTAT   _ SYNCSEL<4:0> |        |        |           |        |       |              |             | 000D     |       |                     |       |           |          |       |               |

| IC4BUF    | 015C  | Input Capture 4 Buffer Register         |                                           |        |        |           |        |       |              |             |          | xxxx  |                     |       |           |          |       |               |

| IC4TMR    | 015E  | ·                                       | Input Capture 4 Timer                     |        |        |           |        |       |              |             |          | 0000  |                     |       |           |          |       |               |

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| S                     |

|-----------------------|

| 7                     |

| 0                     |

| 0                     |

| 0                     |

| 0                     |

| 0                     |

| $^{\circ}$            |

| 7                     |

| $\overline{}$         |

| _                     |

| $\boldsymbol{\sigma}$ |

| а                     |

| g                     |

| Ф                     |

| φ                     |

| S                     |

|                       |

TABLE 4-21: ECAN1 REGISTER MAP WHEN WIN (C1CTRL1<0>) = 0 OR 1 FOR dsPIC33EPXXXMC/GP50X DEVICES ONLY

| File Name  | Addr. | Bit 15  | Bit 14   | Bit 13      | Bit 12  | Bit 11  | Bit 10             | Bit 9    | Bit 8           | Bit 7                                        | Bit 6    | Bit 5          | Bit 4     | Bit 3             | Bit 2    | Bit 1    | Bit 0  | All<br>Resets |

|------------|-------|---------|----------|-------------|---------|---------|--------------------|----------|-----------------|----------------------------------------------|----------|----------------|-----------|-------------------|----------|----------|--------|---------------|

| C1CTRL1    | 0400  | _       | _        | CSIDL       | ABAT    | CANCKS  | R                  | EQOP<2:0 | )>              | OPM                                          | MODE<2:0 | >              | _         | CANCAP            | _        | _        | WIN    | 0480          |

| C1CTRL2    | 0402  | _       | _        | _           | _       | -       | _                  | _        | _               | _                                            | _        | _              |           | D                 | NCNT<4:0 | >        | =      | 0000          |

| C1VEC      | 0404  | _       | _        | _           |         | F       | ILHIT<4:0>         |          |                 | _                                            |          |                |           | ICODE<6:0         | >        |          |        | 0040          |

| C1FCTRL    | 0406  |         | MABS<2:0 | <b>&gt;</b> | _       | 1       | _                  | _        | _               | _                                            | _        | _              |           |                   | FSA<4:0> |          |        | 0000          |

| C1FIFO     | 0408  | _       | _        |             |         | FBP<    | 5:0>               |          |                 | _                                            | _        |                | FNRB<5:0> |                   |          |          | 0000   |               |

| C1INTF     | 040A  | _       | -        | TXBO        | TXBP    | RXBP    | TXWAR              | RXWAR    | EWARN           | IVRIF                                        | WAKIF    | ERRIF          | _         | FIFOIF            | RBOVIF   | RBIF     | TBIF   | 0000          |

| C1INTE     | 040C  | _       | -        | _           | _       | _       | _                  | _        | _               | IVRIE                                        | WAKIE    | ERRIE          | _         | FIFOIE            | RBOVIE   | RBIE     | TBIE   | 0000          |

| C1EC       | 040E  |         |          |             | TERRON  | Γ<7:0>  |                    |          |                 |                                              |          |                | RERRCN    | IT<7:0>           |          |          |        | 0000          |

| C1CFG1     | 0410  | _       | _        | _           | _       | _       | _                  | _        | _               | SJW<1                                        | :0>      |                |           | BRP<              | <5:0>    |          |        | 0000          |

| C1CFG2     | 0412  | _       | WAKFIL   | _           | _       | _       | SE                 | G2PH<2:0 | )>              | SEG2PHTS                                     | SAM      | S              | EG1PH<2   | :0>               | Р        | RSEG<2:0 | >      | 0000          |

| C1FEN1     | 0414  | FLTEN15 | FLTEN14  | FLTEN13     | FLTEN12 | FLTEN11 | FLTEN10            | FLTEN9   | FLTEN8          | FLTEN7                                       | FLTEN6   | FLTEN5         | FLTEN4    | FLTEN3            | FLTEN2   | FLTEN1   | FLTEN0 | FFFF          |

| C1FMSKSEL1 | 0418  | F7MSł   | <<1:0>   | F6MSk       | <<1:0>  | F5MSI   | SK<1:0> F4MSK<1:0> |          | F3MSK<1:0> F2MS |                                              | F2MSk    | SK<1:0> F1MSK< |           | K<1:0> F0MSK<1:0> |          | <<1:0>   | 0000   |               |

| C1FMSKSEL2 | 041A  | F15MS   | K<1:0>   | F14MS       | K<1:0>  | F13MS   | K<1:0>             | F12MS    | K<1:0>          | > F11MSK<1:0> F10MSK<1:0> F9MSK<1:0> F8MSK<1 |          | <<1:0>         | 0000      |                   |          |          |        |               |

- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-22: ECAN1 REGISTER MAP WHEN WIN (C1CTRL1<0>) = 0 FOR dsPIC33EPXXXMC/GP50X DEVICES ONLY

| File Name | Addr          | Bit 15                     | Bit 14                      | Bit 13  | Bit 12  | Bit 11  | Bit 10                                                                    | Bit 9   | Bit 8   | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|-----------|---------------|----------------------------|-----------------------------|---------|---------|---------|---------------------------------------------------------------------------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------------|

|           | 0400-<br>041E |                            | See definition when WIN = x |         |         |         |                                                                           |         |         |         |         |         |         |         |         |         |         |               |

| C1RXFUL1  | 0420          | RXFUL15                    | RXFUL14                     | RXFUL13 | RXFUL12 | RXFUL11 | RXFUL10                                                                   | RXFUL9  | RXFUL8  | RXFUL7  | RXFUL6  | RXFUL5  | RXFUL4  | RXFUL3  | RXFUL2  | RXFUL1  | RXFUL0  | 0000          |

| C1RXFUL2  | 0422          | RXFUL31                    | RXFUL30                     | RXFUL29 | RXFUL28 | RXFUL27 | RXFUL26                                                                   | RXFUL25 | RXFUL24 | RXFUL23 | RXFUL22 | RXFUL21 | RXFUL20 | RXFUL19 | RXFUL18 | RXFUL17 | RXFUL16 | 0000          |

| C1RXOVF1  | 0428          | RXOVF15                    | RXOVF14                     | RXOVF13 | RXOVF12 | RXOVF11 | RXOVF10                                                                   | RXOVF9  | RXOVF8  | RXOVF7  | RXOVF6  | RXOVF5  | RXOVF4  | RXOVF3  | RXOVF2  | RXOVF1  | RXOVF0  | 0000          |

| C1RXOVF2  | 042A          | RXOVF31                    | RXOVF30                     | RXOVF29 | RXOVF28 | RXOVF27 | RXOVF26                                                                   | RXOVF25 | RXOVF24 | RXOVF23 | RXOVF22 | RXOVF21 | RXOVF20 | RXOVF19 | RXOVF18 | RXOVF17 | RXOVF16 | 0000          |

| C1TR01CON | 0430          | TXEN1                      | TXABT1                      | TXLARB1 | TXERR1  | TXREQ1  | RTREN1                                                                    | TX1PF   | RI<1:0> | TXEN0   | TXABAT0 | TXLARB0 | TXERR0  | TXREQ0  | RTREN0  | TX0PF   | RI<1:0> | 0000          |

| C1TR23CON | 0432          | TXEN3                      | TXABT3                      | TXLARB3 | TXERR3  | TXREQ3  | RTREN3                                                                    | TX3PF   | RI<1:0> | TXEN2   | TXABAT2 | TXLARB2 | TXERR2  | TXREQ2  | RTREN2  | TX2PF   | RI<1:0> | 0000          |

| C1TR45CON | 0434          | TXEN5                      | TXABT5                      | TXLARB5 | TXERR5  | TXREQ5  | RTREN5                                                                    | TX5PF   | RI<1:0> | TXEN4   | TXABAT4 | TXLARB4 | TXERR4  | TXREQ4  | RTREN4  | TX4PF   | RI<1:0> | 0000          |

| C1TR67CON | 0436          | TXEN7                      | TXABT7                      | TXLARB7 | TXERR7  | TXREQ7  | RTREN7 TX7PRI<1:0> TXEN6 TXABAT6 TXLARB6 TXERR6 TXREQ6 RTREN6 TX6PRI<1:0: |         |         |         | RI<1:0> | xxxx    |         |         |         |         |         |               |

| C1RXD     | 0440          |                            | ECAN1 Receive Data Word     |         |         |         |                                                                           |         |         |         |         |         |         | xxxx    |         |         |         |               |

| C1TXD     | 0442          | ECAN1 Transmit Data Word 2 |                             |         |         |         |                                                                           |         |         |         |         | xxxx    |         |         |         |         |         |               |

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

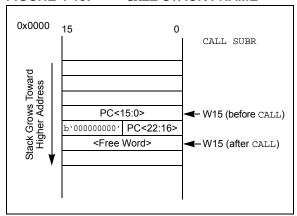

#### 4.4.4 SOFTWARE STACK

The W15 register serves as a dedicated Software Stack Pointer (SSP) and is automatically modified by exception processing, subroutine calls and returns; however, W15 can be referenced by any instruction in the same manner as all other W registers. This simplifies reading, writing and manipulating of the Stack Pointer (for example, creating stack frames).

**Note:** To protect against misaligned stack accesses, W15<0> is fixed to '0' by the hardware.

W15 is initialized to 0x1000 during all Resets. This address ensures that the SSP points to valid RAM in all dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices, and permits stack availability for non-maskable trap exceptions. These can occur before the SSP is initialized by the user software. You can reprogram the SSP during initialization to any location within Data Space.

The Software Stack Pointer always points to the first available free word and fills the software stack working from lower toward higher addresses. Figure 4-19 illustrates how it pre-decrements for a stack pop (read) and post-increments for a stack push (writes).

When the PC is pushed onto the stack, PC<15:0> are pushed onto the first available stack word, then PC<22:16> are pushed into the second available stack location. For a PC push during any CALL instruction, the MSB of the PC is zero-extended before the push, as shown in Figure 4-19. During exception processing, the MSB of the PC is concatenated with the lower 8 bits of the CPU STATUS Register, SR. This allows the contents of SRL to be preserved automatically during interrupt processing.

- Note 1: To maintain system Stack Pointer (W15) coherency, W15 is never subject to (EDS) paging, and is therefore restricted to an address range of 0x0000 to 0xFFFF. The same applies to the W14 when used as a Stack Frame Pointer (SFA = 1).

- 2: As the stack can be placed in, and can access X and Y spaces, care must be taken regarding its use, particularly with regard to local automatic variables in a C development environment

#### FIGURE 4-19: CALL STACK FRAME

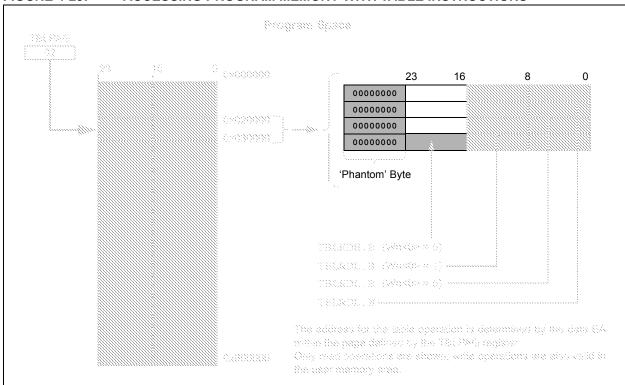

## 4.8.1 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the Program Space without going through Data Space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a Program Space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to Data Space addresses. Program memory can thus be regarded as two 16-bit-wide word address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space that contains the least significant data word. TBLRDH and TBLWTH access the space that contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from Program Space. Both function as either byte or word operations.

- TBLRDL (Table Read Low):

- In Word mode, this instruction maps the lower word of the Program Space location (P<15:0>) to a data address (D<15:0>)

- In Byte mode, either the upper or lower byte

of the lower program word is mapped to the

lower byte of a data address. The upper byte

is selected when Byte Select is '1'; the lower

byte is selected when it is '0'.

- TBLRDH (Table Read High):

- In Word mode, this instruction maps the entire upper word of a program address (P<23:16>) to a data address. The 'phantom' byte (D<15:8>) is always '0'.

- In Byte mode, this instruction maps the upper or lower byte of the program word to D<7:0> of the data address in the TBLRDL instruction. The data is always '0' when the upper 'phantom' byte is selected (Byte Select = 1).

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a Program Space address. The details of their operation are explained in **Section 5.0 "Flash Program Memory"**.

For all table operations, the area of program memory space to be accessed is determined by the Table Page register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user application and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

FIGURE 4-23: ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS

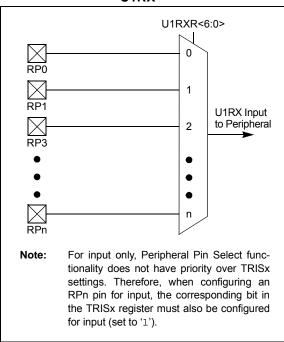

#### 11.4.4 INPUT MAPPING

The inputs of the Peripheral Pin Select options are mapped on the basis of the peripheral. That is, a control register associated with a peripheral dictates the pin it will be mapped to. The RPINRx registers are used to configure peripheral input mapping (see Register 11-1 through Register 11-17). Each register contains sets of 7-bit fields, with each set associated with one of the remappable peripherals. Programming a given peripheral's bit field with an appropriate 7-bit value maps the RPn pin with the corresponding value to that peripheral. For any given device, the valid range of values for any bit field corresponds to the maximum number of Peripheral Pin Selections supported by the device.

For example, Figure 11-2 illustrates remappable pin selection for the U1RX input.

FIGURE 11-2: REMAPPABLE INPUT FOR U1RX

#### 11.4.4.1 Virtual Connections

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices support virtual (internal) connections to the output of the op amp/comparator module (see Figure 25-1 in Section 25.0 "Op Amp/Comparator Module"), and the PTG module (see Section 24.0 "Peripheral Trigger Generator (PTG) Module").

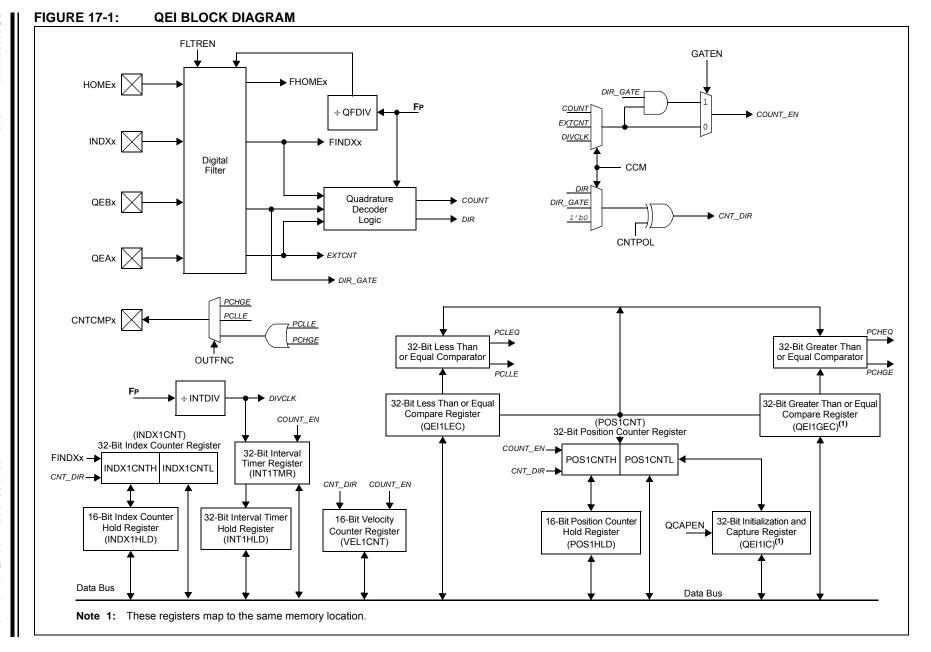

In addition, dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices support virtual connections to the filtered QEI module inputs: FINDX1, FHOME1, FINDX2 and FHOME2 (see Figure 17-1 in Section 17.0 "Quadrature Encoder Interface (QEI) Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)".

Virtual connections provide a simple way of interperipheral connection without utilizing a physical pin. For example, by setting the FLT1R<6:0> bits of the RPINR12 register to the value of 'b0000001, the output of the analog comparator, C1OUT, will be connected to the PWM Fault 1 input, which allows the analog comparator to trigger PWM Faults without the use of an actual physical pin on the device.

Virtual connection to the QEI module allows peripherals to be connected to the QEI digital filter input. To utilize this filter, the QEI module must be enabled and its inputs must be connected to a physical RPn pin. Example 11-2 illustrates how the input capture module can be connected to the QEI digital filter.

## EXAMPLE 11-2: CONNECTING IC1 TO THE HOME1 QEI1 DIGITAL FILTER INPUT ON PIN 43 OF THE dsPIC33EPXXXMC206 DEVICE

#### 11.4.4.2 Output Mapping

In contrast to inputs, the outputs of the Peripheral Pin Select options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPORx registers are used to control output mapping. Like the RPINRx registers, each register contains sets of 6-bit fields, with each set associated with one RPn pin (see Register 11-18 through Register 11-27). The value of the bit field corresponds to one of the peripherals and that peripheral's output is mapped to the pin (see Table 11-3 and Figure 11-3).

A null output is associated with the output register Reset value of '0'. This is done to ensure that remappable outputs remain disconnected from all output pins by default.

FIGURE 11-3: MULTIPLEXING REMAPPABLE OUTPUT FOR RPn

#### 11.4.4.3 Mapping Limitations

The control schema of the peripheral select pins is not limited to a small range of fixed peripheral configurations. There are no mutual or hardware-enforced lockouts between any of the peripheral mapping SFRs. Literally any combination of peripheral mappings across any or all of the RPn pins is possible. This includes both many-to-one and one-to-many mappings of peripheral inputs and outputs to pins. While such mappings may be technically possible from a configuration point of view, they may not be supportable from an electrical point of view.

TABLE 11-3: OUTPUT SELECTION FOR REMAPPABLE PINS (RPn)

| Function                | RPxR<5:0> | Output Name                                   |

|-------------------------|-----------|-----------------------------------------------|

| Default PORT            | 000000    | RPn tied to Default Pin                       |

| U1TX                    | 000001    | RPn tied to UART1 Transmit                    |

| U2TX                    | 000011    | RPn tied to UART2 Transmit                    |

| SDO2                    | 001000    | RPn tied to SPI2 Data Output                  |

| SCK2                    | 001001    | RPn tied to SPI2 Clock Output                 |

| SS2                     | 001010    | RPn tied to SPI2 Slave Select                 |

| C1TX <sup>(2)</sup>     | 001110    | RPn tied to CAN1 Transmit                     |

| OC1                     | 010000    | RPn tied to Output Compare 1 Output           |

| OC2                     | 010001    | RPn tied to Output Compare 2 Output           |

| OC3                     | 010010    | RPn tied to Output Compare 3 Output           |

| OC4                     | 010011    | RPn tied to Output Compare 4 Output           |

| C1OUT                   | 011000    | RPn tied to Comparator Output 1               |

| C2OUT                   | 011001    | RPn tied to Comparator Output 2               |

| C3OUT                   | 011010    | RPn tied to Comparator Output 3               |

| SYNCO1 <sup>(1)</sup>   | 101101    | RPn tied to PWM Primary Time Base Sync Output |

| QEI1CCMP <sup>(1)</sup> | 101111    | RPn tied to QEI 1 Counter Comparator Output   |

| REFCLKO                 | 110001    | RPn tied to Reference Clock Output            |

| C4OUT                   | 110010    | RPn tied to Comparator Output 4               |

Note 1: This function is available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This function is available in dsPIC33EPXXXGP/MC50X devices only.

- g) The TRISx registers control only the digital I/O output buffer. Any other dedicated or remappable active "output" will automatically override the TRIS setting. The TRISx register does not control the digital logic "input" buffer. Remappable digital "inputs" do not automatically override TRIS settings, which means that the TRISx bit must be set to input for pins with only remappable input function(s) assigned

- h) All analog pins are enabled by default after any Reset and the corresponding digital input buffer on the pin has been disabled. Only the Analog Pin Select registers control the digital input buffer, *not* the TRISx register. The user must disable the analog function on a pin using the Analog Pin Select registers in order to use any "digital input(s)" on a corresponding pin, no exceptions.

#### 11.6 I/O Ports Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser:

http://www.microchip.com/wwwproducts/

Devices.aspx?dDocName=en555464

#### 11.6.1 KEY RESOURCES

- "I/O Ports" (DS70598) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- · Development Tools

#### REGISTER 11-24: RPOR6: PERIPHERAL PIN SELECT OUTPUT REGISTER 6

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| _      | _   |       |       | RP57  | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|--------|-------|-------|

| _     | _   |       |       | RP56  | R<5:0> |       |       |

| bit 7 |     |       |       |       |        |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 **Unimplemented:** Read as '0'

bit 13-8 RP57R<5:0>: Peripheral Output Function is Assigned to RP57 Output Pin bits

(see Table 11-3 for peripheral function numbers)

bit 7-6 **Unimplemented:** Read as '0'

bit 5-0 RP56R<5:0>: Peripheral Output Function is Assigned to RP56 Output Pin bits

(see Table 11-3 for peripheral function numbers)

#### REGISTER 11-25: RPOR7: PERIPHERAL PIN SELECT OUTPUT REGISTER 7

| U-0    | U-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|--------|-----|-------|------------|-------|-------|-------|-------|--|--|

| _      | _   |       | RP97R<5:0> |       |       |       |       |  |  |

| bit 15 | _   | _     |            |       | _     |       | bit 8 |  |  |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| _     | _   | _   | _   | _   |     | _   | _     |

| bit 7 |     |     |     |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 Unimplemented: Read as '0'

bit 13-8 RP97R<5:0>: Peripheral Output Function is Assigned to RP97 Output Pin bits

(see Table 11-3 for peripheral function numbers)

bit 7-0 **Unimplemented:** Read as '0'

#### REGISTER 16-2: PTCON2: PWMx PRIMARY MASTER CLOCK DIVIDER SELECT REGISTER 2

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | -   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0                   | R/W-0                   | R/W-0                   |

|-------|-----|-----|-----|-----|-------------------------|-------------------------|-------------------------|

| _     | _   | _   | _   | _   | PCLKDIV2 <sup>(1)</sup> | PCLKDIV1 <sup>(1)</sup> | PCLKDIV0 <sup>(1)</sup> |

| bit 7 |     |     |     |     |                         |                         | bit 0                   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-3 **Unimplemented:** Read as '0'

bit 2-0 PCLKDIV<2:0>: PWMx Input Clock Prescaler (Divider) Select bits<sup>(1)</sup>

111 = Reserved

110 = Divide-by-64

101 = Divide-by-32

100 = Divide-by-16

011 = Divide-by-8

010 = Divide-by-4

001 = Divide-by-2

000 = Divide-by-1, maximum PWMx timing resolution (power-on default)

**Note 1:** These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

#### REGISTER 17-13: QEI1LECH: QEI1 LESS THAN OR EQUAL COMPARE HIGH WORD REGISTER

| R/W-0         | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|---------------|-------|-------|-------|-------|-------|-------|-------|

| QEILEC<31:24> |       |       |       |       |       |       |       |

| bit 15        |       |       |       |       |       |       | bit 8 |

| R/W-0         | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|---------------|-------|-------|-------|-------|-------|-------|-------|

| QEILEC<23:16> |       |       |       |       |       |       |       |

| bit 7         |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 QEILEC<31:16>: High Word Used to Form 32-Bit Less Than or Equal Compare Register (QEI1LEC) bits

#### REGISTER 17-14: QEI1LECL: QEI1 LESS THAN OR EQUAL COMPARE LOW WORD REGISTER

| R/W-0        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------------|-------|-------|-------|-------|-------|-------|-------|

| QEILEC<15:8> |       |       |       |       |       |       |       |

| bit 15       |       |       |       |       |       |       | bit 8 |

| R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------------|-------|-------|-------|-------|-------|-------|-------|

| QEILEC<7:0> |       |       |       |       |       |       |       |

| bit 7       |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 QEILEC<15:0>: Low Word Used to Form 32-Bit Less Than or Equal Compare Register (QEI1LEC) bits

#### REGISTER 20-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

bit 5 ABAUD: Auto-Baud Enable bit

1 = Enables baud rate measurement on the next character – requires reception of a Sync field (55h) before other data; cleared in hardware upon completion

0 = Baud rate measurement is disabled or completed

bit 4 URXINV: UARTx Receive Polarity Inversion bit

1 = UxRX Idle state is '0' 0 = UxRX Idle state is '1'

BRGH: High Baud Rate Enable bit

1 = BRG generates 4 clocks per bit period (4x baud clock, High-Speed mode)

0 = BRG generates 16 clocks per bit period (16x baud clock, Standard mode)

bit 2-1 PDSEL<1:0>: Parity and Data Selection bits

11 = 9-bit data, no parity 10 = 8-bit data, odd parity 01 = 8-bit data, even parity 00 = 8-bit data, no parity

bit 0 STSEL: Stop Bit Selection bit

bit 3

1 = Two Stop bits 0 = One Stop bit

**Note 1:** Refer to the "**UART**" (DS70582) section in the "dsPIC33/PIC24 Family Reference Manual" for information on enabling the UARTx module for receive or transmit operation.

2: This feature is only available for the 16x BRG mode (BRGH = 0).

3: This feature is only available on 44-pin and 64-pin devices.

4: This feature is only available on 64-pin devices.

## REGISTER 21-16: CxRXFnSID: ECANx ACCEPTANCE FILTER n STANDARD IDENTIFIER REGISTER (n = 0-15)

| R/W-x  | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|--------|-------|-------|-------|-------|-------|-------|-------|

| SID10  | SID9  | SID8  | SID7  | SID6  | SID5  | SID4  | SID3  |

| bit 15 |       |       |       |       |       |       | bit 8 |

| R/W-x | R/W-x | R/W-x | U-0 | R/W-x | U-0 | R/W-x | R/W-x |

|-------|-------|-------|-----|-------|-----|-------|-------|

| SID2  | SID1  | SID0  | _   | EXIDE | _   | EID17 | EID16 |

| bit 7 |       |       |     |       |     |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-5 SID<10:0>: Standard Identifier bits

1 = Message address bit, SIDx, must be '1' to match filter 0 = Message address bit, SIDx, must be '0' to match filter

bit 4 Unimplemented: Read as '0'

bit 3 **EXIDE:** Extended Identifier Enable bit

If MIDE = 1:

1 = Matches only messages with Extended Identifier addresses0 = Matches only messages with Standard Identifier addresses

If MIDE = 0:

Ignores EXIDE bit.

bit 2 Unimplemented: Read as '0'

bit 1-0 **EID<17:16>:** Extended Identifier bits

1 = Message address bit, EIDx, must be '1' to match filter 0 = Message address bit, EIDx, must be '0' to match filter

# 23.0 10-BIT/12-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. complement the information in this data sheet. refer to "Analog-to-Digital Converter (ADC)" (DS70621) in the "dsPIC33/PIC24 Family Reference Manual', which is available from the Microchip web site (www.microchip.com).

2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices have one ADC module. The ADC module supports up to 16 analog input channels.

On ADC1, the AD12B bit (AD1CON1<10>) allows the ADC module to be configured by the user as either a 10-bit, 4 Sample-and-Hold (S&H) ADC (default configuration) or a 12-bit, 1 S&H ADC.

**Note:** The ADC module needs to be disabled before modifying the AD12B bit.

#### 23.1 Key Features

#### 23.1.1 10-BIT ADC CONFIGURATION

The 10-bit ADC configuration has the following key features:

- Successive Approximation (SAR) conversion

- · Conversion speeds of up to 1.1 Msps

- · Up to 16 analog input pins

- Connections to three internal op amps

- Connections to the Charge Time Measurement Unit (CTMU) and temperature measurement diode

- Channel selection and triggering can be controlled by the Peripheral Trigger Generator (PTG)

- · External voltage reference input pins

- · Simultaneous sampling of:

- Up to four analog input pins

- Three op amp outputs

- Combinations of analog inputs and op amp outputs

- · Automatic Channel Scan mode

- Selectable conversion Trigger source

- · Selectable Buffer Fill modes

- Four result alignment options (signed/unsigned, fractional/integer)

- · Operation during CPU Sleep and Idle modes

#### 23.1.2 12-BIT ADC CONFIGURATION

The 12-bit ADC configuration supports all the features listed above, with the exception of the following:

- In the 12-bit configuration, conversion speeds of up to 500 ksps are supported

- There is only one S&H amplifier in the 12-bit configuration; therefore, simultaneous sampling of multiple channels is not supported.

Depending on the particular device pinout, the ADC can have up to 16 analog input pins, designated AN0 through AN15. These analog inputs are shared with op amp inputs and outputs, comparator inputs, and external voltage references. When op amp/comparator functionality is enabled, or an external voltage reference is used, the analog input that shares that pin is no longer available. The actual number of analog input pins, op amps and external voltage reference input configuration depends on the specific device.

A block diagram of the ADC module is shown in Figure 23-1. Figure 23-2 provides a diagram of the ADC conversion clock period.

#### 24.3 PTG Control Registers

#### REGISTER 24-1: PTGCST: PTG CONTROL/STATUS REGISTER

| R/W-0  | U-0 | R/W-0   | R/W-0   | U-0 | R/W-0                 | R/W-0                  | R/W-0   |

|--------|-----|---------|---------|-----|-----------------------|------------------------|---------|

| PTGEN  | _   | PTGSIDL | PTGTOGL | _   | PTGSWT <sup>(2)</sup> | PTGSSEN <sup>(3)</sup> | PTGIVIS |

| bit 15 |     |         |         |     |                       |                        | bit 8   |

| R/W-0   | HS-0    | U-0 | U-0 | U-0 | U-0 | R/V                    | V-0                    |

|---------|---------|-----|-----|-----|-----|------------------------|------------------------|

| PTGSTRT | PTGWDTO | _   | _   | _   | _   | PTGITM1 <sup>(1)</sup> | PTGITM0 <sup>(1)</sup> |

| bit 7   |         |     |     |     |     |                        | bit 0                  |

| Legend:           | HS = Hardware Settable bit |                             |                    |  |  |

|-------------------|----------------------------|-----------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read | d as '0'           |  |  |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown |  |  |

bit 15 **PTGEN:** Module Enable bit

1 = PTG module is enabled 0 = PTG module is disabled

0 - PTG Module is disabled

bit 14 **Unimplemented:** Read as '0'

bit 13 **PTGSIDL:** PTG Stop in Idle Mode bit

1 = Discontinues module operation when device enters Idle mode

0 = Continues module operation in Idle mode

bit 12 PTGTOGL: PTG TRIG Output Toggle Mode bit

1 = Toggle state of the PTGOx for each execution of the PTGTRIG command

0 = Each execution of the PTGTRIG command will generate a single PTGOx pulse determined by the value in the PTGPWDx bits

bit 11 **Unimplemented:** Read as '0'

bit 10 **PTGSWT:** PTG Software Trigger bit<sup>(2)</sup>

1 = Triggers the PTG module

0 = No action (clearing this bit will have no effect)

bit 9 **PTGSSEN:** PTG Enable Single-Step bit<sup>(3)</sup>

1 = Enables Single-Step mode

0 = Disables Single-Step mode

bit 8 **PTGIVIS:** PTG Counter/Timer Visibility Control bit

1 = Reads of the PTGSDLIM, PTGCxLIM or PTGTxLIM registers return the current values of their corresponding counter/timer registers (PTGSD, PTGCx, PTGTx)

0 = Reads of the PTGSDLIM, PTGCxLIM or PTGTxLIM registers return the value previously written to those limit registers

bit 7 PTGSTRT: PTG Start Sequencer bit

1 = Starts to sequentially execute commands (Continuous mode)

0 = Stops executing commands

bit 6 **PTGWDTO:** PTG Watchdog Timer Time-out Status bit

1 = PTG Watchdog Timer has timed out 0 = PTG Watchdog Timer has not timed out.

bit 5-2 **Unimplemented:** Read as '0'

**Note 1:** These bits apply to the PTGWHI and PTGWLO commands only.

2: This bit is only used with the PTGCTRL step command software trigger option.

3: Use of the PTG Single-Step mode is reserved for debugging tools only.

#### REGISTER 25-2: CMxCON: COMPARATOR x CONTROL REGISTER (x = 1, 2 OR 3) (CONTINUED)

bit 7-6 **EVPOL<1:0>:** Trigger/Event/Interrupt Polarity Select bits

- 11 = Trigger/event/interrupt generated on any change of the comparator output (while CEVT = 0)

- 10 = Trigger/event/interrupt generated only on high-to-low transition of the polarity selected comparator output (while CEVT = 0)

If CPOL = 1 (inverted polarity):

Low-to-high transition of the comparator output.

If CPOL = 0 (non-inverted polarity):

High-to-low transition of the comparator output.

01 = Trigger/event/interrupt generated only on low-to-high transition of the polarity-selected comparator output (while CEVT = 0)

If CPOL = 1 (inverted polarity):

High-to-low transition of the comparator output.

If CPOL = 0 (non-inverted polarity):

Low-to-high transition of the comparator output

00 = Trigger/event/interrupt generation is disabled

- bit 5 **Unimplemented:** Read as '0'

- bit 4 CREF: Comparator Reference Select bit (VIN+ input)<sup>(1)</sup>

- 1 = VIN+ input connects to internal CVREFIN voltage(2)

- 0 = VIN+ input connects to CxIN1+ pin

- bit 3-2 **Unimplemented:** Read as '0'

- bit 1-0 CCH<1:0>: Op Amp/Comparator Channel Select bits<sup>(1)</sup>

- 11 = Unimplemented

- 10 = Unimplemented

- 01 = Inverting input of the comparator connects to the CxIN2- pin<sup>(2)</sup>

- 00 = Inverting input of the op amp/comparator connects to the CxIN1- pin

- **Note 1:** Inputs that are selected and not available will be tied to Vss. See the "**Pin Diagrams**" section for available inputs for each package.

- 2: This output is not available when OPMODE (CMxCON<10>) = 1.

#### TABLE 30-54: OP AMP/COMPARATOR VOLTAGE REFERENCE SETTLING TIME SPECIFICATIONS

|        |        |                | Standard Operating Conditions (see Note 2): 3.0V to 3.6V (unless otherwise stated)  Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |      |      |       |            |

|--------|--------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|------------|

| Param. | Symbol | Characteristic | Min.                                                                                                                                                                                                                                                           | Тур. | Max. | Units | Conditions |

| VR310  | TSET   | Settling Time  | _                                                                                                                                                                                                                                                              | 1    | 10   | μS    | (Note 1)   |

- Note 1: Settling time is measured while CVRR = 1 and CVR<3:0> bits transition from '0000' to '1111'.

- 2: Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

#### TABLE 30-55: OP AMP/COMPARATOR VOLTAGE REFERENCE SPECIFICATIONS

| DC CHARACTERISTICS |        |                                            | Standard Operating Conditions (see Note 1): 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{Ta} \le +125^{\circ}\text{C}$ for Extended |                |            |       |               |  |  |

|--------------------|--------|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------|-------|---------------|--|--|

| Param<br>No.       | Symbol | Characteristics                            | Min.                                                                                                                                                                                                                                                          | Min. Typ. Max. |            | Units | Conditions    |  |  |

| VRD310             | CVRES  | Resolution                                 | CVRSRC/24                                                                                                                                                                                                                                                     | _              | CVRSRC/32  | LSb   |               |  |  |

| VRD311             | CVRAA  | Absolute Accuracy <sup>(2)</sup>           | _                                                                                                                                                                                                                                                             | ±25            | _          | mV    | CVRSRC = 3.3V |  |  |

| VRD313             | CVRSRC | Input Reference Voltage                    | 0                                                                                                                                                                                                                                                             | _              | AVDD + 0.3 | V     |               |  |  |

| VRD314             | CVRout | Buffer Output<br>Resistance <sup>(2)</sup> | _                                                                                                                                                                                                                                                             | 1.5k           | _          | Ω     |               |  |  |

- Note 1: Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

- 2: Parameter is characterized but not tested in manufacturing.

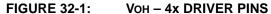

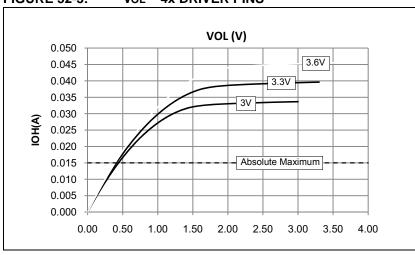

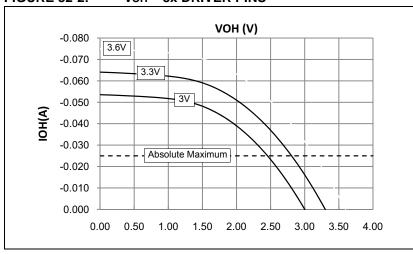

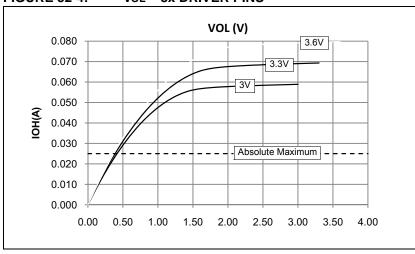

#### 32.0 DC AND AC DEVICE CHARACTERISTICS GRAPHS

**Note:** The graphs provided following this note are a statistical summary based on a limited number of samples and are provided for design guidance purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

FIGURE 32-2: VOH – 8x DRIVER PINS

FIGURE 32-4: Vol – 8x DRIVER PINS

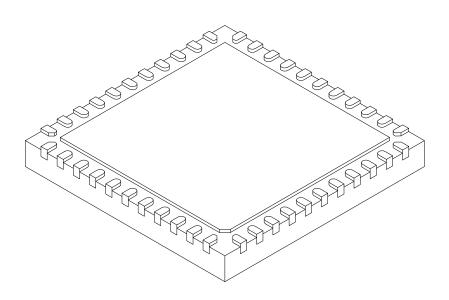

#### 44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | MILLIMETERS |           |          |      |  |  |

|-------------------------|-------------|-----------|----------|------|--|--|

| Dimension               | MIN         | NOM       | MAX      |      |  |  |

| Number of Pins          | N           | 44        |          |      |  |  |

| Pitch                   | е           |           | 0.65 BSC |      |  |  |

| Overall Height          | Α           | 0.80 0.90 |          | 1.00 |  |  |

| Standoff                | A1          | 0.00      | 0.02     | 0.05 |  |  |

| Terminal Thickness      | A3          | 0.20 REF  |          |      |  |  |

| Overall Width           | E           | 8.00 BSC  |          |      |  |  |

| Exposed Pad Width       | E2          | 6.25      | 6.45     | 6.60 |  |  |

| Overall Length          | D           | 8.00 BSC  |          |      |  |  |

| Exposed Pad Length      | D2          | 6.25      | 6.45     | 6.60 |  |  |

| Terminal Width          | р           | 0.20      | 0.30     | 0.35 |  |  |

| Terminal Length         | L           | 0.30      | 0.40     | 0.50 |  |  |

| Terminal-to-Exposed-Pad | K           | 0.20      | -        | -    |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated

- 3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension. usually without tolerance. for information purposes only.

Microchip Technology Drawing C04-103C Sheet 2 of 2