#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 70 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                  |

| Number of I/O              | 35                                                                             |

| Program Memory Size        | 256KB (85.5K x 24)                                                             |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 9x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-TQFP                                                                        |

| Supplier Device Package    | 44-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep256mc204-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

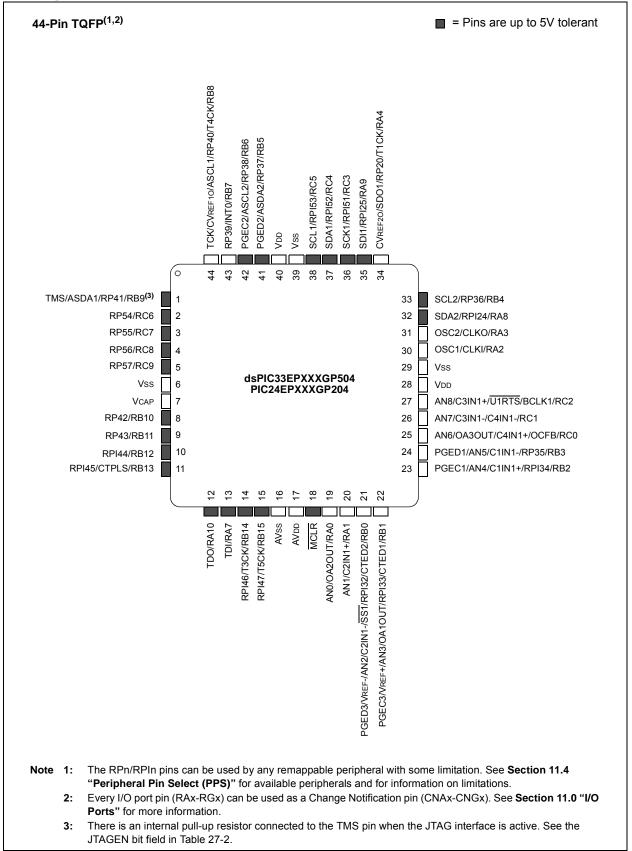

## **Pin Diagrams (Continued)**

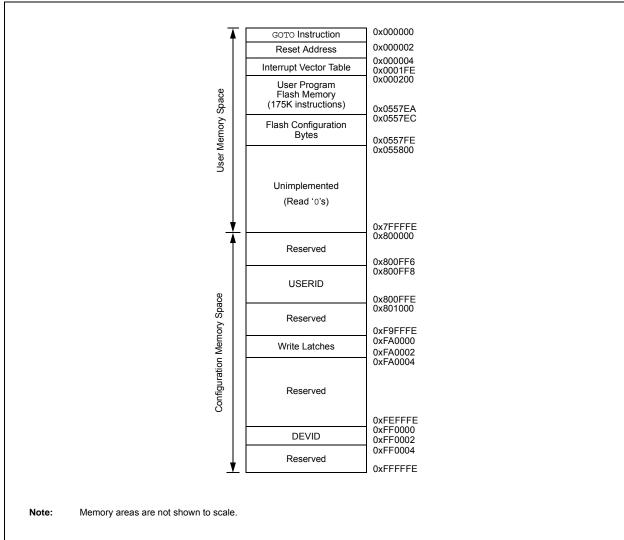

#### FIGURE 4-5: PROGRAM MEMORY MAP FOR dsPIC33EP512GP50X, dsPIC33EP512MC20X/50X AND PIC24EP512GP/MC20X DEVICES

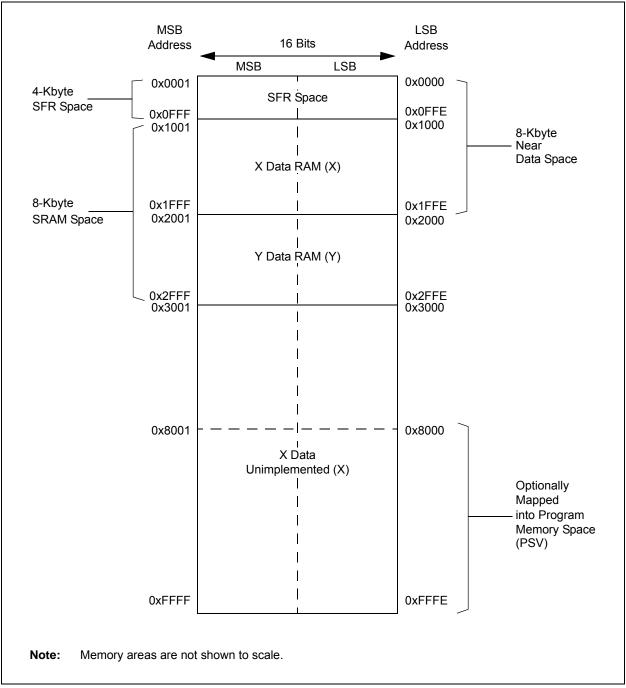

# FIGURE 4-8: DATA MEMORY MAP FOR dsPIC33EP64MC20X/50X AND dsPIC33EP64GP50X DEVICES

| <b>TABLE 4-33</b> : | PERIPHERAL PIN SELECT INPUT REGISTER MAP FOR dsPIC33EPXXXMC20X DEVICES ONLY |

|---------------------|-----------------------------------------------------------------------------|

|---------------------|-----------------------------------------------------------------------------|

|              |       |        |              | -          | -      | -          |        |       |       |       |              |       |       |            |        |       |       |               |

|--------------|-------|--------|--------------|------------|--------|------------|--------|-------|-------|-------|--------------|-------|-------|------------|--------|-------|-------|---------------|

| File<br>Name | Addr. | Bit 15 | Bit 14       | Bit 13     | Bit 12 | Bit 11     | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6        | Bit 5 | Bit 4 | Bit 3      | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

| RPINR0       | 06A0  | _      |              | INT1R<6:0> |        |            |        |       |       | _     | _            | _     | _     |            | _      | _     | 0000  |               |

| RPINR1       | 06A2  |        | —            | —          | -      |            | -      |       |       | -     |              |       |       | INT2R<6:0> |        |       |       | 0000          |

| RPINR3       | 06A6  |        | _            | _          | _      | _          | _      | _     | _     | _     |              |       | -     | [2CKR<6:0> | >      |       |       | 0000          |

| RPINR7       | 06AE  | _      |              |            |        | IC2R<6:0>  |        |       |       | —     |              |       |       | IC1R<6:0>  |        |       |       | 0000          |

| RPINR8       | 06B0  | _      |              |            |        | IC4R<6:0>  |        |       |       | —     | IC3R<6:0>    |       |       |            |        | 0000  |       |               |

| RPINR11      | 06B6  | _      | _            | _          | —      | _          | _      | _     | _     | —     | OCFAR<6:0>   |       |       |            | 0000   |       |       |               |

| RPINR12      | 06B8  | _      |              |            | l      | =LT2R<6:0> |        |       |       | —     | — FLT1       |       |       |            | R<6:0> |       |       | 0000          |

| RPINR14      | 06BC  | _      |              |            | (      | QEB1R<6:0  | >      |       |       | —     | QEA1R<6:0>   |       |       |            |        | 0000  |       |               |

| RPINR15      | 06BE  | _      |              |            | Н      | OME1R<6:0  | )>     |       |       | —     | INDX1R<6:0>  |       |       |            | 0000   |       |       |               |

| RPINR18      | 06C4  | _      | _            | _          | —      | —          | _      | _     | _     | —     |              |       | ι     | J1RXR<6:0> | >      |       |       | 0000          |

| RPINR19      | 06C6  | _      | _            | _          | _      | _          | _      | _     | _     | —     |              |       | ι     | J2RXR<6:0> | >      |       |       | 0000          |

| RPINR22      | 06CC  | _      |              | •          | S      | CK2INR<6:0 | )>     |       |       | _     |              |       |       | SDI2R<6:0> | •      |       |       | 0000          |

| RPINR23      | 06CE  | _      | _            |            | _      | _          | _      | _     | _     | _     | SS2R<6:0>    |       |       |            |        | 0000  |       |               |

| RPINR37      | 06EA  | _      | SYNCI1R<6:0> |            |        |            |        |       | _     | _     | _            | _     | _     | _          | _      | _     | 0000  |               |

| RPINR38      | 06EC  | _      |              |            | DI     | CMP1R<6:   | 0>     |       |       | _     | _            | _     | _     |            | _      | _     | _     | 0000          |

| RPINR39      | 06EE  | _      |              |            | DT     | CMP3R<6:   | 0>     |       |       | —     | DTCMP2R<6:0> |       |       |            | 0000   |       |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-0  | U-0   | R/W-0 | R/W-0  | R/W-0               | R-0 | R-0   | R-0   |

|--------|-------|-------|--------|---------------------|-----|-------|-------|

| VAR    | —     | US1   | US0    | EDT                 | DL2 | DL1   | DL0   |

| bit 15 | -     | •     |        |                     |     |       | bit 8 |

|        |       |       |        |                     |     |       |       |

| R/W-0  | R/W-0 | R/W-1 | R/W-0  | R/C-0               | R-0 | R/W-0 | R/W-0 |

| SATA   | SATB  | SATDW | ACCSAT | IPL3 <sup>(2)</sup> | SFA | RND   | IF    |

| bit 7  |       | •     |        |                     |     |       | bit 0 |

|        |       |       |        |                     |     |       |       |

|        |       |       |        |                     |     |       |       |

# **REGISTER 7-2:** CORCON: CORE CONTROL REGISTER<sup>(1)</sup>

| Legend:           | C = Clearable bit |                      |                    |

|-------------------|-------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bi | t, read as '0'     |

| -n = Value at POR | '1'= Bit is set   | '0' = Bit is cleared | x = Bit is unknown |

bit

| VAR: Variable Exception Processing Latency Control                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------|

| <ol> <li>1 = Variable exception processing is enabled</li> </ol>                                                              |

| 0 = Fixed exception processing is enabled                                                                                     |

| IPL3: CPU Interrupt Priority Level Status bit 3 <sup>(2)</sup>                                                                |

| <ul> <li>1 = CPU Interrupt Priority Level is greater than 7</li> <li>0 = CPU Interrupt Priority Level is 7 or less</li> </ul> |

|                                                                                                                               |

**Note 1:** For complete register details, see Register 3-2.

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

|                 | 12. 2007.00    |                                       |              |                   |                  |                 |        |

|-----------------|----------------|---------------------------------------|--------------|-------------------|------------------|-----------------|--------|

| U-0             | U-0            | U-0                                   | U-0          | U-0               | U-0              | U-0             | U-0    |

| —               | —              | —                                     | —            | —                 | —                | —               | —      |

| bit 15          |                |                                       |              |                   |                  |                 | bit 8  |

|                 |                |                                       |              |                   |                  |                 |        |

| U-0             | U-0            | U-0                                   | U-0          | R-0               | R-0              | R-0             | R-0    |

| —               |                | —                                     | —            | RQCOL3            | RQCOL2           | RQCOL1          | RQCOL0 |

| bit 7           |                |                                       |              |                   |                  |                 | bit 0  |

|                 |                |                                       |              |                   |                  |                 |        |

| Legend:         |                |                                       |              |                   |                  |                 |        |

| R = Readable    | bit            | W = Writable                          | bit          | U = Unimpler      | mented bit, read | l as '0'        |        |

| -n = Value at F | POR            | '1' = Bit is set                      |              | '0' = Bit is cle  | ared             | x = Bit is unkr | nown   |

|                 |                |                                       |              |                   |                  |                 |        |

| bit 15-4        | Unimplemen     | ted: Read as '                        | כ'           |                   |                  |                 |        |

| bit 3           | RQCOL3: DN     | /IA Channel 3 T                       | ransfer Requ | est Collision F   | ag bit           |                 |        |

|                 |                | e and interrupt<br>est collision is d |              | st collision is d | etected          |                 |        |

| <b>h</b> # 0    | •              |                                       |              | est Callisian Fl  | aa hit           |                 |        |

| bit 2           |                | /IA Channel 2 T<br>ce and interrupt   | •            |                   | 0                |                 |        |

|                 |                | e and interrupt<br>est collision is d |              |                   | elecieu          |                 |        |

| bit 1           | RQCOL1: DN     | /IA Channel 1 T                       | ransfer Requ | est Collision F   | ag bit           |                 |        |

|                 | 1 = User for   | e and interrupt                       | -based reque | st collision is d | etected          |                 |        |

|                 | 0 = No reque   | est collision is d                    | etected      |                   |                  |                 |        |

| bit 0           | RQCOLO: DN     | /IA Channel 0 T                       | ransfer Requ | est Collision F   | lag bit          |                 |        |

|                 | 1 = User force | e and interrupt                       | -based reque | st collision is d | etected          |                 |        |

## REGISTER 8-12: DMARQC: DMA REQUEST COLLISION STATUS REGISTER

0 = No request collision is detected

NOTES:

## 10.2.1 SLEEP MODE

The following occurs in Sleep mode:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption is reduced to a minimum, provided that no I/O pin is sourcing current.

- The Fail-Safe Clock Monitor does not operate, since the system clock source is disabled.

- The LPRC clock continues to run in Sleep mode if the WDT is enabled.

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode.

- Some device features or peripherals can continue to operate. This includes items such as the Input Change Notification (ICN) on the I/O ports or peripherals that use an external clock input.

- Any peripheral that requires the system clock source for its operation is disabled.

The device wakes up from Sleep mode on any of these events:

- Any interrupt source that is individually enabled

- · Any form of device Reset

- A WDT time-out

On wake-up from Sleep mode, the processor restarts with the same clock source that was active when Sleep mode was entered.

For optimal power savings, the internal regulator and the Flash regulator can be configured to go into Standby when Sleep mode is entered by clearing the VREGS (RCON<8>) and VREGSF (RCON<11>) bits (default configuration).

If the application requires a faster wake-up time, and can accept higher current requirements, the VREGS (RCON<8>) and VREGSF (RCON<11>) bits can be set to keep the internal regulator and the Flash regulator active during Sleep mode.

## 10.2.2 IDLE MODE

The following occurs in Idle mode:

- The CPU stops executing instructions.

- · The WDT is automatically cleared.

- The system clock source remains active. By default, all peripheral modules continue to operate normally from the system clock source, but can also be selectively disabled (see Section 10.4 "Peripheral Module Disable").

- If the WDT or FSCM is enabled, the LPRC also remains active.

The device wakes from Idle mode on any of these events:

- · Any interrupt that is individually enabled

- Any device Reset

- · A WDT time-out

On wake-up from Idle mode, the clock is reapplied to the CPU and instruction execution will begin (2-4 clock cycles later), starting with the instruction following the PWRSAV instruction or the first instruction in the Interrupt Service Routine (ISR).

All peripherals also have the option to discontinue operation when Idle mode is entered to allow for increased power savings. This option is selectable in the control register of each peripheral; for example, the TSIDL bit in the Timer1 Control register (T1CON<13>).

## 10.2.3 INTERRUPTS COINCIDENT WITH POWER SAVE INSTRUCTIONS

Any interrupt that coincides with the execution of a PWRSAV instruction is held off until entry into Sleep or Idle mode has completed. The device then wakes up from Sleep or Idle mode.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

# REGISTER 11-26: RPOR8: PERIPHERAL PIN SELECT OUTPUT REGISTER 8

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|---------|-------|-------|

| —      | —   |       |       | RP118 | 3R<5:0> |       |       |

| bit 15 |     |       |       |       |         |       | bit 8 |

|        |     |       |       |       |         |       |       |

| U-0    | U-0 | U-0   | U-0   | U-0   | U-0     | U-0   | U-0   |

| —      | —   |       | —     | _     | _       | —     | _     |

| bit 7  |     |       |       |       |         |       | bit 0 |

|        |     |       |       |       |         |       |       |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                 |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP118R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP118 Output Pin bits (see Table 11-3 for peripheral function numbers) |

bit 7-0 Unimplemented: Read as '0'

#### REGISTER 11-27: RPOR9: PERIPHERAL PIN SELECT OUTPUT REGISTER 9

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | _   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|---------|-------|-------|

| —     | —   |       |       | RP120 | )R<5:0> |       |       |

| bit 7 |     |       |       |       |         |       | bit 0 |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-6 Unimplemented: Read as '0'

bit 5-0 **RP120R<5:0>:** Peripheral Output Function is Assigned to RP120 Output Pin bits (see Table 11-3 for peripheral function numbers)

# 15.1 Output Compare Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

#### 15.1.1 KEY RESOURCES

- "Output Compare" (DS70358) in the "dsPIC33/ PIC24 Family Reference Manual"

- · Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

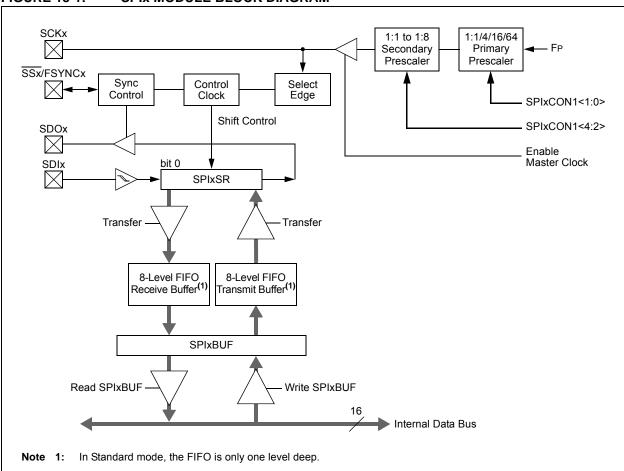

#### FIGURE 18-1: SPIX MODULE BLOCK DIAGRAM

# **19.2** I<sup>2</sup>C Control Registers

#### REGISTER 19-1: I2CxCON: I2Cx CONTROL REGISTER

| R/W-0            | U-0                                                                   | R/W-0                                                             | R/W-1, HC            | R/W-0                        | R/W-0             | R/W-0           | R/W-0          |  |

|------------------|-----------------------------------------------------------------------|-------------------------------------------------------------------|----------------------|------------------------------|-------------------|-----------------|----------------|--|

| I2CEN            | —                                                                     | I2CSIDL                                                           | SCLREL               | IPMIEN <sup>(1)</sup>        | A10M              | DISSLW          | SMEN           |  |

| bit 15           |                                                                       |                                                                   |                      |                              |                   |                 | bit 8          |  |

|                  |                                                                       |                                                                   |                      |                              |                   |                 |                |  |

| R/W-0            | R/W-0                                                                 | R/W-0                                                             | R/W-0, HC            | R/W-0, HC                    | R/W-0, HC         | R/W-0, HC       | R/W-0, HC      |  |

| GCEN             | STREN                                                                 | ACKDT                                                             | ACKEN                | RCEN                         | PEN               | RSEN            | SEN            |  |

| bit 7            |                                                                       |                                                                   |                      |                              |                   |                 | bit 0          |  |

| Legend:          |                                                                       | HC = Hardware                                                     | Clearable bit        |                              |                   |                 |                |  |

| R = Readab       | le bit                                                                | W = Writable bi                                                   |                      | U = Unimpler                 | mented bit, rea   | d as '0'        |                |  |

| -n = Value a     | It POR                                                                | '1' = Bit is set                                                  |                      | '0' = Bit is cle             |                   | x = Bit is unk  | nown           |  |

|                  |                                                                       |                                                                   |                      |                              |                   |                 |                |  |

| bit 15           | I2CEN: I2Cx                                                           | Enable bit                                                        |                      |                              |                   |                 |                |  |

|                  |                                                                       | the I2Cx module                                                   |                      |                              |                   |                 | ;              |  |

| L:1 4 4          |                                                                       | the I2Cx module                                                   | ; all I-C ™ pins a   | are controlled               | by port function  | IS              |                |  |

| bit 14<br>bit 13 | -                                                                     | ited: Read as '0'                                                 | do bit               |                              |                   |                 |                |  |

| DIC 13           |                                                                       | Stop in Idle Mo<br>ues module oper                                |                      | rice enters an l             | dle mode          |                 |                |  |

|                  |                                                                       | s module operati                                                  |                      |                              |                   |                 |                |  |

| bit 12           | SCLREL: SC                                                            | Lx Release Con                                                    | rol bit (when op     | perating as I <sup>2</sup> C | slave)            |                 |                |  |

|                  | 1 = Releases                                                          |                                                                   |                      |                              |                   |                 |                |  |

|                  |                                                                       | Lx clock low (clo                                                 | ck stretch)          |                              |                   |                 |                |  |

|                  | If STREN = 1<br>Bit is R/W (i e                                       | <u>.:</u><br>e., software can w                                   | rite '0' to initiate | e stretch and w              | rite '1' to relea | se clock) Harr  | lware is clear |  |

|                  | at the beginn                                                         | ing of every slav<br>reception. Hardv                             | ve data byte tra     | ansmission. Ha               | ardware is clea   | r at the end o  |                |  |

|                  | If STREN = 0                                                          |                                                                   |                      |                              |                   |                 |                |  |

|                  |                                                                       | ., software can or                                                |                      |                              |                   |                 |                |  |

| hit 11           | -                                                                     | te transmission.<br>Iligent Peripheral                            |                      |                              | -                 | address byte re | eception.      |  |

| bit 11           |                                                                       | le is enabled; all                                                |                      |                              |                   |                 |                |  |

|                  | $0 = IPMI \mod$                                                       |                                                                   |                      | , lon no me agea             |                   |                 |                |  |

| bit 10           | A10M: 10-Bit                                                          | Slave Address b                                                   | oit                  |                              |                   |                 |                |  |

|                  |                                                                       | is a 10-bit slave                                                 |                      |                              |                   |                 |                |  |

|                  |                                                                       | is a 7-bit slave a                                                |                      |                              |                   |                 |                |  |

| bit 9            |                                                                       | able Slew Rate (                                                  |                      |                              |                   |                 |                |  |

|                  | 1 = Slew rate control is disabled<br>0 = Slew rate control is enabled |                                                                   |                      |                              |                   |                 |                |  |

| bit 8            |                                                                       | SMEN: SMBus Input Levels bit                                      |                      |                              |                   |                 |                |  |

|                  |                                                                       | 1 = Enables I/O pin thresholds compliant with SMBus specification |                      |                              |                   |                 |                |  |

|                  |                                                                       | SMBus input thre                                                  |                      | ,                            |                   |                 |                |  |

| bit 7            | GCEN: Gene                                                            | eral Call Enable b                                                | it (when operat      | ing as I <sup>2</sup> C slav | /e)               |                 |                |  |

|                  |                                                                       | nterrupt when a ge<br>call address disal                          |                      | ss is received ir            | n I2CxRSR (mo     | dule is enabled | for reception) |  |

|                  |                                                                       |                                                                   |                      |                              |                   |                 |                |  |

Note 1: When performing master operations, ensure that the IPMIEN bit is set to '0'.

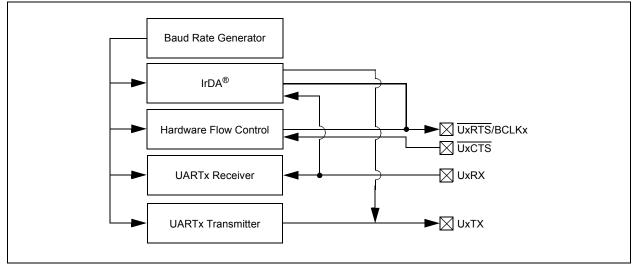

# 20.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "UART" (DS70582) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X family of devices contains two UART modules.

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X device family. The UART is a full-duplex, asynchronous system that can communicate with peripheral devices, such as personal computers, LIN/J2602, RS-232 and RS-485 interfaces. The module also supports a hardware flow control option with the UxCTS and UxRTS pins, and also includes an IrDA<sup>®</sup> encoder and decoder.

Note: <u>Hardware</u> flow control using UxRTS and UxCTS is not available on all pin count devices. See the "**Pin Diagrams**" section for availability.

The primary features of the UARTx module are:

- Full-Duplex, 8 or 9-Bit Data Transmission through the UxTX and UxRX Pins

- Even, Odd or No Parity Options (for 8-bit data)

- One or Two Stop bits

- Hardware Flow Control Option with UxCTS and UxRTS Pins

- Fully Integrated Baud Rate Generator with 16-Bit Prescaler

- Baud Rates Ranging from 4.375 Mbps to 67 bps at 16x mode at 70 MIPS

- Baud Rates Ranging from 17.5 Mbps to 267 bps at 4x mode at 70 MIPS

- 4-Deep First-In First-Out (FIFO) Transmit Data Buffer

- 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-bit mode with Address Detect (9th bit = 1)

- · Transmit and Receive Interrupts

- A Separate Interrupt for all UARTx Error Conditions

- · Loopback mode for Diagnostic Support

- · Support for Sync and Break Characters

- Support for Automatic Baud Rate Detection

- IrDA<sup>®</sup> Encoder and Decoder Logic

- 16x Baud Clock Output for IrDA Support

A simplified block diagram of the UARTx module is shown in Figure 20-1. The UARTx module consists of these key hardware elements:

- · Baud Rate Generator

- Asynchronous Transmitter

- Asynchronous Receiver

#### FIGURE 20-1: UARTx SIMPLIFIED BLOCK DIAGRAM

© 2011-2013 Microchip Technology Inc.

| R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1  | R/W-1  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| FLTEN15 | FLTEN14 | FLTEN13 | FLTEN12 | FLTEN11 | FLTEN10 | FLTEN9 | FLTEN8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

|         |         |         |         |         |         |        |        |

| R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1  | R/W-1  |

| FLTEN7  | FLTEN6  | FLTEN5  | FLTEN4  | FLTEN3  | FLTEN2  | FLTEN1 | FLTEN0 |

| bit 7   |         |         |         |         |         |        | bit 0  |

|         |         |         |         |         |         |        |        |

| Legend: |         |         |         |         |         |        |        |

### REGISTER 21-11: CxFEN1: ECANx ACCEPTANCE FILTER ENABLE REGISTER 1

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-0

FLTEN<15:0>: Enable Filter n to Accept Messages bits

1 = Enables Filter n

0 = Disables Filter n

REGISTER 21-12: CxBUFPNT1: ECANx FILTER 0-3 BUFFER POINTER REGISTER 1

| R/W-0         | R/W-0                                                 | R/W-0                                                                                                       | R/W-0                                          | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|---------------|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|------------------------------------------------|-------------------|-----------------|-----------------|-------|

|               | F3BI                                                  | P<3:0>                                                                                                      |                                                |                   | F2BI            | P<3:0>          |       |

| bit 15        |                                                       |                                                                                                             |                                                |                   |                 |                 | bit 8 |

| R/W-0         | R/W-0                                                 | R/W-0                                                                                                       | R/W-0                                          | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

| F1BP<3:0>     |                                                       |                                                                                                             |                                                |                   | F0BI            | P<3:0>          |       |

| bit 7         |                                                       |                                                                                                             |                                                |                   |                 |                 | bit ( |

| Legend:       |                                                       |                                                                                                             |                                                |                   |                 |                 |       |

| R = Readable  | e bit                                                 | W = Writable                                                                                                | bit                                            | U = Unimplem      | nented bit, rea | d as '0'        |       |

| -n = Value at | POR                                                   | '1' = Bit is set                                                                                            |                                                | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

| bit 15-12     | 1111 = Filte<br>1110 = Filte<br>•<br>•<br>•<br>•<br>• | : RX Buffer Mas<br>er hits received in<br>er hits received in<br>er hits received in<br>er hits received in | n RX FIFO bu<br>n RX Buffer 1<br>n RX Buffer 1 | iffer             |                 |                 |       |

| bit 11-8      | F2BP<3:0>                                             | : RX Buffer Mas                                                                                             | k for Filter 2 b                               | oits (same value  | s as bits<15:1  | 2>)             |       |

| bit 7-4       | F1BP<3:0>                                             | : RX Buffer Mas                                                                                             | k for Filter 1 k                               | oits (same value  | s as bits<15:1  | 2>)             |       |

|               |                                                       | F0BP<3:0>: RX Buffer Mask for Filter 0 bits (same values as bits<15:12>)                                    |                                                |                   |                 |                 |       |

## FIGURE 22-1: CTMU BLOCK DIAGRAM

5: The switch connected to ADC CH0 is closed when IDISSEN (CTMUCON1<9>) = 1, and opened when IDISSEN = 0.

# 22.1 CTMU Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 22.1.1 KEY RESOURCES

- "Charge Time Measurement Unit (CTMU)" (DS70661) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- · Development Tools

# **30.0 ELECTRICAL CHARACTERISTICS**

This section provides an overview of dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X electrical characteristics. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X family are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these or any other conditions above the parameters indicated in the operation listings of this specification is not implied.

# Absolute Maximum Ratings<sup>(1)</sup>

| Ambient temperature under bias                                                    | 40°C to +125°C       |

|-----------------------------------------------------------------------------------|----------------------|

| Storage temperature                                                               | 65°C to +150°C       |

| Voltage on VDD with respect to Vss                                                | -0.3V to +4.0V       |

| Voltage on any pin that is not 5V tolerant, with respect to Vss <sup>(3)</sup>    | 0.3V to (VDD + 0.3V) |

| Voltage on any 5V tolerant pin with respect to Vss when $VDD \ge 3.0V^{(3)}$      | 0.3V to +5.5V        |

| Voltage on any 5V tolerant pin with respect to Vss when VDD < 3.0V <sup>(3)</sup> | -0.3V to +3.6V       |

| Maximum current out of Vss pin                                                    |                      |

| Maximum current into Vod pin <sup>(2)</sup>                                       |                      |

| Maximum current sunk/sourced by any 4x I/O pin                                    | 15 mA                |

| Maximum current sunk/sourced by any 8x I/O pin                                    | 25 mA                |

| Maximum current sunk by all ports <sup>(2,4)</sup>                                | 200 mA               |

- **Note 1:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

- 2: Maximum allowable current is a function of device maximum power dissipation (see Table 30-2).

- 3: See the "Pin Diagrams" section for the 5V tolerant pins.

- 4: Exceptions are: dsPIC33EPXXXGP502, dsPIC33EPXXXMC202/502 and PIC24EPXXXGP/MC202 devices, which have a maximum sink/source capability of 130 mA.

| DC CHARACTERISTICS |                               |               | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                       |                 |  |  |

|--------------------|-------------------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------|--|--|

| Parameter<br>No.   | Тур.                          | Max.          | Units                                                                                                                                                                                                                                                                                   | Units Conditions      |                 |  |  |

| Power-Down Cu      | urrent (IPD) <sup>(1)</sup> - | dsPIC33EP32GI | P50X, dsPIC33EF                                                                                                                                                                                                                                                                         | P32MC20X/50X and PIC2 | 4EP32GP/MC20X   |  |  |

| DC60d              | 30                            | 100           | μA                                                                                                                                                                                                                                                                                      | -40°C                 |                 |  |  |

| DC60a              | 35                            | 100           | μA                                                                                                                                                                                                                                                                                      | +25°C                 | 3.3V            |  |  |

| DC60b              | 150                           | 200           | μA                                                                                                                                                                                                                                                                                      | +85°C                 | 3.3V            |  |  |

| DC60c              | 250                           | 500           | μA                                                                                                                                                                                                                                                                                      | +125°C                |                 |  |  |

| Power-Down Cu      | urrent (IPD) <sup>(1)</sup> – | dsPIC33EP64GI | P50X, dsPIC33EF                                                                                                                                                                                                                                                                         | P64MC20X/50X and PIC2 | 4EP64GP/MC20X   |  |  |

| DC60d              | 25                            | 100           | μA                                                                                                                                                                                                                                                                                      | -40°C                 |                 |  |  |

| DC60a              | 30                            | 100           | μA                                                                                                                                                                                                                                                                                      | +25°C                 | 3.3V            |  |  |

| DC60b              | 150                           | 350           | μΑ                                                                                                                                                                                                                                                                                      | +85°C                 | 3.3V            |  |  |

| DC60c              | 350                           | 800           | μΑ                                                                                                                                                                                                                                                                                      | +125°C                |                 |  |  |

| Power-Down Cu      | urrent (IPD) <sup>(1)</sup> – | dsPIC33EP128G | P50X, dsPIC33E                                                                                                                                                                                                                                                                          | P128MC20X/50X and PIC | 24EP128GP/MC20X |  |  |

| DC60d              | 30                            | 100           | μΑ                                                                                                                                                                                                                                                                                      | -40°C                 |                 |  |  |

| DC60a              | 35                            | 100           | μΑ                                                                                                                                                                                                                                                                                      | +25°C                 | 3.3V            |  |  |

| DC60b              | 150                           | 350           | μΑ                                                                                                                                                                                                                                                                                      | +85°C                 | 5.50            |  |  |

| DC60c              | 550                           | 1000          | μΑ                                                                                                                                                                                                                                                                                      | +125°C                |                 |  |  |

| Power-Down Cu      | urrent (IPD) <sup>(1)</sup> – | dsPIC33EP256G | P50X, dsPIC33E                                                                                                                                                                                                                                                                          | P256MC20X/50X and PIC | 24EP256GP/MC20X |  |  |

| DC60d              | 35                            | 100           | μΑ                                                                                                                                                                                                                                                                                      | -40°C                 |                 |  |  |

| DC60a              | 40                            | 100           | μΑ                                                                                                                                                                                                                                                                                      | +25°C                 | 3.3V            |  |  |

| DC60b              | 250                           | 450           | μΑ                                                                                                                                                                                                                                                                                      | +85°C                 | 5.57            |  |  |

| DC60c              | 1000                          | 1200          | μΑ                                                                                                                                                                                                                                                                                      | +125°C                |                 |  |  |

| Power-Down Cu      | urrent (IPD) <sup>(1)</sup> – | dsPIC33EP512G | P50X, dsPIC33E                                                                                                                                                                                                                                                                          | P512MC20X/50X and PIC | 24EP512GP/MC20X |  |  |

| DC60d              | 40                            | 100           | μΑ                                                                                                                                                                                                                                                                                      | -40°C                 |                 |  |  |

| DC60a              | 45                            | 100           | μΑ                                                                                                                                                                                                                                                                                      | +25°C                 | 3.3V            |  |  |

| DC60b              | 350                           | 800           | μΑ                                                                                                                                                                                                                                                                                      | +85°C                 | 0.0 v           |  |  |

| DC60c              | 1100                          | 1500          | μA                                                                                                                                                                                                                                                                                      | +125°C                |                 |  |  |

## TABLE 30-8: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

Note 1: IPD (Sleep) current is measured as follows:

• CPU core is off, oscillator is configured in EC mode and external clock is active; OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)

- · CLKO is configured as an I/O input pin in the Configuration Word

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- All peripheral modules are disabled (PMDx bits are all set)

- The VREGS bit (RCON<8>) = 0 (i.e., core regulator is set to standby while the device is in Sleep mode)

- The VREGSF bit (RCON<11>) = 0 (i.e., Flash regulator is set to standby while the device is in Sleep mode)

- JTAG is disabled

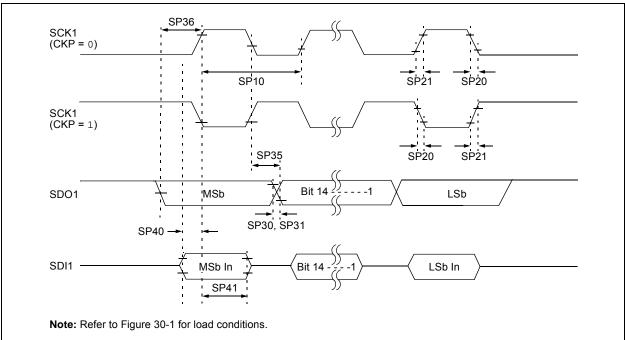

### FIGURE 30-24: SPI1 MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = x, SMP = 1) TIMING CHARACTERISTICS

# TABLE 30-43:SPI1 MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = x, SMP = 1)TIMING REQUIREMENTS

| AC CHA | RACTERIST             | ICS                                           |      | Operatin<br>otherwise<br>temperat | <b>stated)</b><br>ture -40 | °C ≤ Ta ≤ | 7 <b>to 3.6V</b><br>+85°C for Industrial<br>+125°C for Extended |

|--------|-----------------------|-----------------------------------------------|------|-----------------------------------|----------------------------|-----------|-----------------------------------------------------------------|

| Param. | Symbol                | Characteristic <sup>(1)</sup>                 | Min. | Typ. <sup>(2)</sup>               | Max.                       | Units     | Conditions                                                      |

| SP10   | FscP                  | Maximum SCK1 Frequency                        | _    | —                                 | 10                         | MHz       | (Note 3)                                                        |

| SP20   | TscF                  | SCK1 Output Fall Time                         | —    | —                                 | _                          | ns        | See Parameter DO32 (Note 4)                                     |

| SP21   | TscR                  | SCK1 Output Rise Time                         | —    | —                                 | _                          | ns        | See Parameter DO31 (Note 4)                                     |

| SP30   | TdoF                  | SDO1 Data Output Fall Time                    | —    | —                                 | _                          | ns        | See Parameter DO32 (Note 4)                                     |

| SP31   | TdoR                  | SDO1 Data Output Rise Time                    | —    | _                                 | _                          | ns        | See Parameter DO31 (Note 4)                                     |

| SP35   | TscH2doV,<br>TscL2doV | SDO1 Data Output Valid after<br>SCK1 Edge     | —    | 6                                 | 20                         | ns        |                                                                 |

| SP36   | TdoV2sc,<br>TdoV2scL  | SDO1 Data Output Setup to<br>First SCK1 Edge  | 30   | —                                 | _                          | ns        |                                                                 |

| SP40   | TdiV2scH,<br>TdiV2scL | Setup Time of SDI1 Data<br>Input to SCK1 Edge | 30   | —                                 | _                          | ns        |                                                                 |

| SP41   | TscH2diL,<br>TscL2diL | Hold Time of SDI1 Data Input to SCK1 Edge     | 30   |                                   |                            | ns        |                                                                 |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The minimum clock period for SCK1 is 100 ns. The clock generated in Master mode must not violate this specification.

- **4:** Assumes 50 pF load on all SPI1 pins.

| AC CHARACTERISTICS |        |                                               |           |          |           |       | Ta ≤ +85°C for Industrial                               |

|--------------------|--------|-----------------------------------------------|-----------|----------|-----------|-------|---------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic                                | Min.      | Тур.     | Max.      | Units | Conditions                                              |

|                    |        | ADC A                                         | ccuracy ( | 10-Bit N | lode)     |       |                                                         |

| AD20b              | Nr     | Resolution                                    | 10        | ) Data B | its       | bits  |                                                         |

| AD21b              | INL    | Integral Nonlinearity                         | -0.625    |          | 0.625     | LSb   | -40°C ≤ TA ≤ +85°C (Note 2)                             |

|                    |        |                                               | -1.5      |          | 1.5       | LSb   | +85°C < TA ≤ +125°C (Note 2)                            |

| AD22b              | DNL    | Differential Nonlinearity                     | -0.25     | —        | 0.25      | LSb   | -40°C ≤ TA ≤ +85°C (Note 2)                             |

|                    |        |                                               | -0.25     | —        | 0.25      | LSb   | +85°C < TA $\leq$ +125°C (Note 2)                       |

| AD23b              | Gerr   | Gain Error                                    | -2.5      | —        | 2.5       | LSb   | -40°C $\leq$ TA $\leq$ +85°C (Note 2)                   |

|                    |        |                                               | -2.5      |          | 2.5       | LSb   | +85°C < TA $\leq$ +125°C (Note 2)                       |

| AD24b              | EOFF   | Offset Error                                  | -1.25     | —        | 1.25      | LSb   | $-40^{\circ}C \le TA \le +85^{\circ}C \text{ (Note 2)}$ |

|                    |        |                                               | -1.25     | —        | 1.25      | LSb   | +85°C < TA $\leq$ +125°C (Note 2)                       |

| AD25b              | —      | Monotonicity                                  | _         |          | _         | —     | Guaranteed                                              |

|                    |        | Dynamic P                                     | erforman  | ce (10-E | Bit Mode) |       |                                                         |

| AD30b              | THD    | Total Harmonic Distortion <sup>(3)</sup>      | _         | 64       |           | dB    |                                                         |

| AD31b              | SINAD  | Signal to Noise and Distortion <sup>(3)</sup> |           | 57       |           | dB    |                                                         |

| AD32b              | SFDR   | Spurious Free Dynamic<br>Range <sup>(3)</sup> | —         | 72       | —         | dB    |                                                         |

| AD33b              | Fnyq   | Input Signal Bandwidth <sup>(3)</sup>         | —         | 550      | —         | kHz   |                                                         |

| AD34b              | ENOB   | Effective Number of Bits <sup>(3)</sup>       | _         | 9.4      | —         | bits  |                                                         |

## TABLE 30-59: ADC MODULE SPECIFICATIONS (10-BIT MODE)

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

2: For all accuracy specifications, VINL = AVSS = VREFL = 0V and AVDD = VREFH = 3.6V.

**3:** Parameters are characterized but not tested in manufacturing.

# TABLE A-1:MAJOR SECTION UPDATES (CONTINUED)

| Section Name                                 | Update Description                                                                                                                                                       |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Section 30.0 "Electrical<br>Characteristics" | Removed Voltage on VCAP with respect to Vss and added Note 5 in Absolute Maximum Ratings <sup>(1)</sup> .                                                                |

|                                              | Removed Parameter DC18 (VCORE) and Note 3 from the DC Temperature and Voltage Specifications (see Table 30-4).                                                           |

|                                              | Updated Note 1 in the DC Characteristics: Operating Current (IDD) (see Table 30-6).                                                                                      |

|                                              | Updated Note 1 in the DC Characteristics: Idle Current (IIDLE) (see Table 30-7).                                                                                         |

|                                              | Changed the Typical values for Parameters DC60a-DC60d and updated Note 1 in the DC Characteristics: Power-down Current (IPD) (see Table 30-8).                           |

|                                              | Updated Note 1 in the DC Characteristics: Doze Current (IDOZE) (see Table 30-9).                                                                                         |

|                                              | Updated Note 2 in the Electrical Characteristics: BOR (see Table 30-12).                                                                                                 |

|                                              | Updated Parameters CM20 and CM31, and added Parameters CM44 and CM45 in the AC/DC Characteristics: Op amp/Comparator (see Table 30-14).                                  |

|                                              | Added the Op amp/Comparator Reference Voltage Settling Time Specifications (see Table 30-15).                                                                            |

|                                              | Added Op amp/Comparator Voltage Reference DC Specifications (see Table 30-16).                                                                                           |

|                                              | Updated Internal FRC Accuracy Parameter F20a (see Table 30-21).                                                                                                          |

|                                              | Updated the Typical value and Units for Parameter CTMUI1, and added Parameters CTMUI4, CTMUFV1, and CTMUFV2 to the CTMU Current Source Specifications (see Table 30-55). |

| Section 31.0 "Packaging<br>Information"      | Updated packages by replacing references of VLAP with TLA.                                                                                                               |

| "Product Identification<br>System"           | Changed VLAP to TLA.                                                                                                                                                     |