Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                        |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 256KB (85.5K x 24)                                                              |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 16K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 9x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-TQFP                                                                         |

| Supplier Device Package    | 44-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep256mc204t-e-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

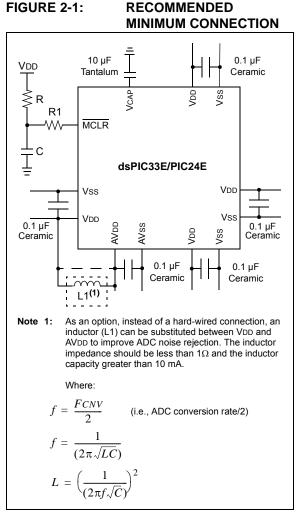

#### 2.2.1 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits including DSCs to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

## 2.3 CPU Logic Filter Capacitor Connection (VCAP)

A low-ESR (< 1 Ohm) capacitor is required on the VCAP pin, which is used to stabilize the voltage regulator output voltage. The VCAP pin must not be connected to VDD and must have a capacitor greater than 4.7  $\mu$ F (10  $\mu$ F is recommended), 16V connected to ground. The type can be ceramic or tantalum. See **Section 30.0** "**Electrical Characteristics**" for additional information.

The placement of this capacitor should be close to the VCAP pin. It is recommended that the trace length not exceeds one-quarter inch (6 mm). See **Section 27.3 "On-Chip Voltage Regulator"** for details.

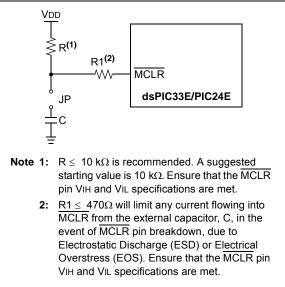

# 2.4 Master Clear (MCLR) Pin

The MCLR pin provides two specific device functions:

- Device Reset

- Device Programming and Debugging.

During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as shown in Figure 2-2, it is recommended that the capacitor, C, be isolated from the  $\overline{\text{MCLR}}$  pin during programming and debugging operations.

Place the components as shown in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

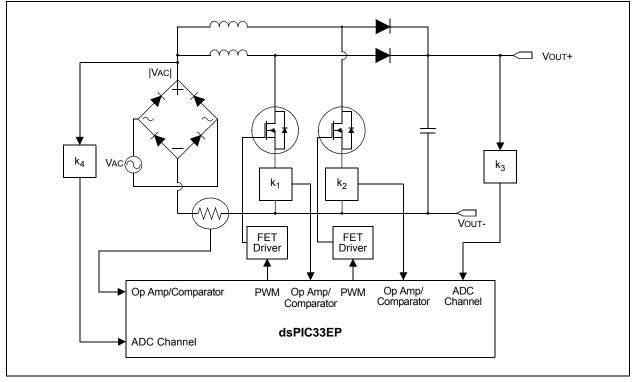

#### FIGURE 2-7: INTERLEAVED PFC

| <b>TABLE 4-33</b> : | PERIPHERAL PIN SELECT INPUT REGISTER MAP FOR dsPIC33EPXXXMC20X DEVICES ONLY |

|---------------------|-----------------------------------------------------------------------------|

|---------------------|-----------------------------------------------------------------------------|

| File<br>Name | Addr. | Bit 15 | Bit 14       | Bit 13                  | Bit 12 | Bit 11     | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6        | Bit 5      | Bit 4 | Bit 3      | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------------|-------------------------|--------|------------|--------|-------|-------|-------|--------------|------------|-------|------------|-------|-------|-------|---------------|

| RPINR0       | 06A0  | _      |              |                         |        | NT1R<6:0>  |        |       |       |       | _            | _          | _     | _          |       | _     | _     | 0000          |

| RPINR1       | 06A2  |        | —            | —                       | -      |            | -      |       | -     | -     |              |            |       | INT2R<6:0> |       |       |       | 0000          |

| RPINR3       | 06A6  | -      | _            | _                       | _      | _          | _      | _     | _     | _     |              |            | -     | [2CKR<6:0> | >     |       |       | 0000          |

| RPINR7       | 06AE  | _      |              |                         |        | IC2R<6:0>  |        |       |       | —     |              |            |       | IC1R<6:0>  |       |       |       | 0000          |

| RPINR8       | 06B0  | _      |              |                         |        | IC4R<6:0>  |        |       |       | —     | IC3R<6:0>    |            |       |            | 0000  |       |       |               |

| RPINR11      | 06B6  | _      | _            | _                       | —      | _          | _      | _     | _     | —     | OCFAR<6:0>   |            |       | 0000       |       |       |       |               |

| RPINR12      | 06B8  | _      |              | FLT2R<6:0> — FLT1R<6:0> |        |            |        |       |       | 0000  |              |            |       |            |       |       |       |               |

| RPINR14      | 06BC  | _      | QEB1R<6:0>   |                         |        |            |        | —     |       |       | (            | QEA1R<6:0> | >     |            |       | 0000  |       |               |

| RPINR15      | 06BE  | _      |              |                         | Н      | OME1R<6:0  | )>     |       |       | —     |              |            | I     | NDX1R<6:0  | >     |       |       | 0000          |

| RPINR18      | 06C4  | _      | _            | _                       | —      | _          | _      | _     | _     | —     |              |            | ι     | J1RXR<6:0> | >     |       |       | 0000          |

| RPINR19      | 06C6  | _      | _            | _                       | _      | _          | _      | _     | _     | —     |              |            | ι     | J2RXR<6:0> | >     |       |       | 0000          |

| RPINR22      | 06CC  | _      |              | •                       | S      | CK2INR<6:0 | )>     |       |       | _     | - SDI2R<6:0> |            |       |            | 0000  |       |       |               |

| RPINR23      | 06CE  | _      | _            |                         | _      | _          | _      | _     | _     | _     | SS2R<6:0>    |            |       | 0000       |       |       |       |               |

| RPINR37      | 06EA  | _      | SYNCI1R<6:0> |                         |        |            | _      | _     | _     | _     | _            | _          | _     | _          | 0000  |       |       |               |

| RPINR38      | 06EC  | _      | DTCMP1R<6:0> |                         |        |            | _      | _     | 0000  |       |              |            |       |            |       |       |       |               |

| RPINR39      | 06EE  | _      |              |                         | DT     | CMP3R<6:   | 0>     |       |       | —     |              |            | D     | CMP2R<6:   | 0>    |       |       | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## 5.2 RTSP Operation

RTSP allows the user application to erase a single page of memory and to program two instruction words at a time. See the General Purpose and Motor Control Family tables (Table 1 and Table 2, respectively) for the page sizes of each device.

For more information on erasing and programming Flash memory, refer to "Flash Programming" (DS70609) in the "dsPIC33/PIC24 Family Reference Manual".

#### 5.3 **Programming Operations**

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. The processor stalls (waits) until the programming operation is finished.

For erase and program times, refer to Parameters D137a and D137b (Page Erase Time), and D138a and D138b (Word Write Cycle Time) in Table 30-14 in **Section 30.0 "Electrical Characteristics"**.

Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

#### 5.3.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

Programmers can program two adjacent words (24 bits x 2) of program Flash memory at a time on every other word address boundary (0x000002, 0x000006, 0x00000A, etc.). To do this, it is necessary to erase the page that contains the desired address of the location the user wants to change.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user application must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS.

Refer to **Flash Programming**" (DS70609) in the "*dsPIC33/PIC24 Family Reference Manual*" for details and codes examples on programming using RTSP.

#### 5.4 Flash Memory Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter |

|-------|--------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                            |

|       | http://www.microchip.com/wwwproducts/                                                |

|       | Devices.aspx?dDocName=en555464                                                       |

#### 5.4.1 KEY RESOURCES

- "Flash Programming" (DS70609) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

## 5.5 Control Registers

Four SFRs are used to erase and write the program Flash memory: NVMCON, NVMKEY, NVMADRH and NVMADRL.

The NVMCON register (Register 5-1) enables and initiates Flash memory erase and write operations.

NVMKEY (Register 5-4) is a write-only register that is used for write protection. To start a programming or erase sequence, the user application must consecutively write 0x55 and 0xAA to the NVMKEY register.

There are two NVM Address registers: NVMADRH and NVMADRL. These two registers, when concatenated, form the 24-bit Effective Address (EA) of the selected word for programming operations or the selected page for erase operations.

The NVMADRH register is used to hold the upper 8 bits of the EA, while the NVMADRL register is used to hold the lower 16 bits of the EA.

|                                                     | Vector  | IRQ        |                   | Inte     | Interrupt Bit Location |              |  |  |

|-----------------------------------------------------|---------|------------|-------------------|----------|------------------------|--------------|--|--|

| Interrupt Source                                    | # #     |            | IVT Address       | Flag     | Enable                 | Priority     |  |  |

| QEI1 – QEI1 Position Counter Compare <sup>(2)</sup> | 66      | 58         | 0x000088          | IFS3<10> | IEC3<10>               | IPC14<10:8>  |  |  |

| Reserved                                            | 67-72   | 59-64      | 0x00008A-0x000094 | _        | _                      | _            |  |  |

| U1E – UART1 Error Interrupt                         | 73      | 65         | 0x000096          | IFS4<1>  | IEC4<1>                | IPC16<6:4>   |  |  |

| U2E – UART2 Error Interrupt                         | 74      | 66         | 0x000098          | IFS4<2>  | IEC4<2>                | IPC16<10:8>  |  |  |

| CRC – CRC Generator Interrupt                       | 75      | 67         | 0x00009A          | IFS4<3>  | IEC4<3>                | IPC16<14:12> |  |  |

| Reserved                                            | 76-77   | 68-69      | 0x00009C-0x00009E | —        | _                      | —            |  |  |

| C1TX – CAN1 TX Data Request <sup>(1)</sup>          | 78      | 70         | 0x000A0           | IFS4<6>  | IEC4<6>                | IPC17<10:8>  |  |  |

| Reserved                                            | 79-84   | 71-76      | 0x0000A2-0x0000AC | —        | _                      | —            |  |  |

| CTMU – CTMU Interrupt                               | 85      | 77         | 0x0000AE          | IFS4<13> | IEC4<13>               | IPC19<6:4>   |  |  |

| Reserved                                            | 86-101  | 78-93      | 0x0000B0-0x0000CE | —        | _                      | —            |  |  |

| PWM1 – PWM Generator 1 <sup>(2)</sup>               | 102     | 94         | 0x0000D0          | IFS5<14> | IEC5<14>               | IPC23<10:8>  |  |  |

| PWM2 – PWM Generator 2 <sup>(2)</sup>               | 103     | 95         | 0x0000D2          | IFS5<15> | IEC5<15>               | IPC23<14:12> |  |  |

| PWM3 – PWM Generator 3 <sup>(2)</sup>               | 104     | 96         | 0x0000D4          | IFS6<0>  | IEC6<0>                | IPC24<2:0>   |  |  |

| Reserved                                            | 105-149 | 97-141     | 0x0001D6-0x00012E | —        | _                      | —            |  |  |

| ICD – ICD Application                               | 150     | 142        | 0x000142          | IFS8<14> | IEC8<14>               | IPC35<10:8>  |  |  |

| JTAG – JTAG Programming                             | 151     | 143        | 0x000130          | IFS8<15> | IEC8<15>               | IPC35<14:12> |  |  |

| Reserved                                            | 152     | 144        | 0x000134          | —        | —                      | _            |  |  |

| PTGSTEP – PTG Step                                  | 153     | 145        | 0x000136          | IFS9<1>  | IEC9<1>                | IPC36<6:4>   |  |  |

| PTGWDT – PTG Watchdog Time-out                      | 154     | 146        | 0x000138          | IFS9<2>  | IEC9<2>                | IPC36<10:8>  |  |  |

| PTG0 – PTG Interrupt 0                              | 155     | 147        | 0x00013A          | IFS9<3>  | IEC9<3>                | IPC36<14:12> |  |  |

| PTG1 – PTG Interrupt 1                              | 156     | 148        | 0x00013C          | IFS9<4>  | IEC9<4>                | IPC37<2:0>   |  |  |

| PTG2 – PTG Interrupt 2                              | 157     | 149        | 0x00013E          | IFS9<5>  | IEC9<5>                | IPC37<6:4>   |  |  |

| PTG3 – PTG Interrupt 3                              | 158     | 150        | 0x000140          | IFS9<6>  | IEC9<6>                | IPC37<10:8>  |  |  |

| Reserved                                            | 159-245 | 151-245    | 0x000142-0x0001FE | —        | —                      | _            |  |  |

|                                                     | Lowe    | est Natura | I Order Priority  |          |                        |              |  |  |

## TABLE 7-1: INTERRUPT VECTOR DETAILS (CONTINUED)

Note 1: This interrupt source is available on dsPIC33EPXXXGP50X and dsPIC33EPXXXMC50X devices only.

2: This interrupt source is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

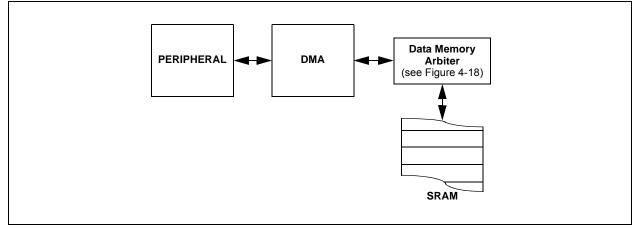

# 8.0 DIRECT MEMORY ACCESS (DMA)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Direct Memory Access (DMA)" (DS70348) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The DMA Controller transfers data between Peripheral Data registers and Data Space SRAM

In addition, DMA can access the entire data memory space. The Data Memory Bus Arbiter is utilized when either the CPU or DMA attempts to access SRAM, resulting in potential DMA or CPU stalls.

The DMA Controller supports 4 independent channels. Each channel can be configured for transfers to or from selected peripherals. Some of the peripherals supported by the DMA Controller include:

- ECAN<sup>™</sup>

- Analog-to-Digital Converter (ADC)

- Serial Peripheral Interface (SPI)

- UART

- Input Capture

- Output Compare

Refer to Table 8-1 for a complete list of supported peripherals.

## FIGURE 8-1: DMA CONTROLLER MODULE

# 13.0 TIMER2/3 AND TIMER4/5

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70362) of the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The Timer2/3 and Timer4/5 modules are 32-bit timers, which can also be configured as four independent 16-bit timers with selectable operating modes.

As 32-bit timers, Timer2/3 and Timer4/5 operate in three modes:

- Two Independent 16-Bit Timers (e.g., Timer2 and Timer3) with all 16-Bit Operating modes (except Asynchronous Counter mode)

- Single 32-Bit Timer

- Single 32-Bit Synchronous Counter

- They also support these features:

- Timer Gate Operation

- Selectable Prescaler Settings

- Timer Operation during Idle and Sleep modes

- Interrupt on a 32-Bit Period Register Match

- Time Base for Input Capture and Output Compare Modules (Timer2 and Timer3 only)

- ADC1 Event Trigger (32-bit timer pairs, and Timer3 and Timer5 only)

Individually, all four of the 16-bit timers can function as synchronous timers or counters. They also offer the features listed previously, except for the event trigger; this is implemented only with Timer2/3. The operating modes and enabled features are determined by setting the appropriate bit(s) in the T2CON, T3CON, and T4CON, T5CON registers. T2CON and T4CON are shown in generic form in Register 13-1. T3CON and T5CON are shown in Register 13-2.

For 32-bit timer/counter operation, Timer2 and Timer4 are the least significant word (lsw); Timer3 and Timer5 are the most significant word (msw) of the 32-bit timers.

Note: For 32-bit operation, T3CON and T5CON control bits are ignored. Only T2CON and T4CON control bits are used for setup and control. Timer2 and Timer4 clock and gate inputs are utilized for the 32-bit timer modules, but an interrupt is generated with the Timer3 and Timer5 interrupt flags.

A block diagram for an example 32-bit timer pair (Timer2/3 and Timer4/5) is shown in Figure 13-3.

**Note:** Only Timer2, 3, 4 and 5 can trigger a DMA data transfer.

# 19.0 INTER-INTEGRATED CIRCUIT<sup>™</sup> (I<sup>2</sup>C<sup>™</sup>)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXGP50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS70330) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

- 3: There are minimum bit rates of approximately FCY/512. As a result, high processor speeds may not support 100 Kbit/second operation. See timing specifications, IM10 and IM11, and the "Baud Rate Generator" in the "dsPIC33/PIC24 Family Reference Manual".

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X family of devices contains two Inter-Integrated Circuit (I<sup>2</sup>C) modules: I2C1 and I2C2.

The  $l^2C$  module provides complete hardware support for both Slave and Multi-Master modes of the  $l^2C$  serial communication standard, with a 16-bit interface.

The  $I^2C$  module has a 2-pin interface:

- · The SCLx pin is clock

- The SDAx pin is data

The I<sup>2</sup>C module offers the following key features:

- I<sup>2</sup>C interface supporting both Master and Slave modes of operation

- I<sup>2</sup>C Slave mode supports 7 and 10-bit addressing

- I<sup>2</sup>C Master mode supports 7 and 10-bit addressing

- I<sup>2</sup>C port allows bidirectional transfers between master and slaves

- Serial clock synchronization for I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control)

- I<sup>2</sup>C supports multi-master operation, detects bus collision and arbitrates accordingly

- Intelligent Platform Management Interface (IPMI)

support

- System Management Bus (SMBus) support

| U-0          | U-0               | R-0                        | R-0            | R-0               | R-0              | R-0             | R-0   |  |  |  |  |  |

|--------------|-------------------|----------------------------|----------------|-------------------|------------------|-----------------|-------|--|--|--|--|--|

| _            |                   | FBP5                       | FBP4           | FBP3              | FBP2             | FBP1            | FBP0  |  |  |  |  |  |

| bit 15       |                   |                            |                |                   |                  |                 | bit 8 |  |  |  |  |  |

|              |                   |                            |                |                   |                  |                 |       |  |  |  |  |  |

| U-0          | U-0               | R-0                        | R-0            | R-0               | R-0              | R-0             | R-0   |  |  |  |  |  |

|              |                   | FNRB5                      | FNRB4          | FNRB3             | FNRB2            | FNRB1           | FNRB0 |  |  |  |  |  |

| bit 7        |                   |                            |                |                   |                  |                 | bit ( |  |  |  |  |  |

| Legend:      |                   |                            |                |                   |                  |                 |       |  |  |  |  |  |

| R = Readab   | le bit            | W = Writable               | bit            | U = Unimplen      | nented bit, read | d as '0'        |       |  |  |  |  |  |

| -n = Value a | t POR             | '1' = Bit is set           |                | '0' = Bit is clea |                  | x = Bit is unkr | iown  |  |  |  |  |  |

|              |                   |                            |                |                   |                  |                 |       |  |  |  |  |  |

| bit 15-14    | Unimpleme         | ented: Read as '           | 0'             |                   |                  |                 |       |  |  |  |  |  |

| bit 13-8     | FBP<5:0>:         | FIFO Buffer Poir           | nter bits      |                   |                  |                 |       |  |  |  |  |  |

|              |                   | 011111 = RB31 buffer       |                |                   |                  |                 |       |  |  |  |  |  |

|              | 011110 <b>= F</b> | RB30 buffer                |                |                   |                  |                 |       |  |  |  |  |  |

|              | •                 |                            |                |                   |                  |                 |       |  |  |  |  |  |

|              | •                 |                            |                |                   |                  |                 |       |  |  |  |  |  |

|              | •                 | TRB1 buffer                |                |                   |                  |                 |       |  |  |  |  |  |

|              |                   | TRB0 buffer                |                |                   |                  |                 |       |  |  |  |  |  |

| bit 7-6      | Unimpleme         | ented: Read as '           | 0'             |                   |                  |                 |       |  |  |  |  |  |

| bit 5-0      | FNRB<5:0          | >: FIFO Next Rea           | ad Buffer Poir | iter bits         |                  |                 |       |  |  |  |  |  |

|              | 011111 <b>= F</b> | RB31 buffer                |                |                   |                  |                 |       |  |  |  |  |  |

|              | 011110 <b>= F</b> | RB30 buffer                |                |                   |                  |                 |       |  |  |  |  |  |

|              | •                 |                            |                |                   |                  |                 |       |  |  |  |  |  |

|              | •                 |                            |                |                   |                  |                 |       |  |  |  |  |  |

|              | •                 |                            |                |                   |                  |                 |       |  |  |  |  |  |

|              |                   |                            |                |                   |                  |                 |       |  |  |  |  |  |

|              |                   | FRB1 buffer<br>FRB0 buffer |                |                   |                  |                 |       |  |  |  |  |  |

#### REGISTER 21-5: CxFIFO: ECANx FIFO STATUS REGISTER

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

#### REGISTER 23-5: AD1CHS123: ADC1 INPUT CHANNEL 1, 2, 3 SELECT REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-0    | R/W-0    | R/W-0   |

|--------|-----|-----|-----|-----|----------|----------|---------|

| —      | —   | —   | —   | -   | CH123NB1 | CH123NB0 | CH123SB |

| bit 15 |     |     |     |     |          |          | bit 8   |

|        |     |     |     |     |          |          |         |

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-0    | R/W-0    | R/W-0   |

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0    | R/W-0    | R/W-0   |

|-------|-----|-----|-----|-----|----------|----------|---------|

| —     | —   | —   | —   | —   | CH123NA1 | CH123NA0 | CH123SA |

| bit 7 |     |     |     |     |          |          | bit 0   |

# Legend:

| Legena.           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-11 Unimplemented: Read as '0'

bit 10-9

**CH123NB<1:0>:** Channel 1, 2, 3 Negative Input Select for Sample MUXB bits In 12-bit mode (AD21B = 1), CH123NB is Unimplemented and is Read as '0':

| Value           | ADC Channel |       |       |  |  |  |

|-----------------|-------------|-------|-------|--|--|--|

| value           | CH1         | CH2   | CH3   |  |  |  |

| 11              | AN9         | AN10  | AN11  |  |  |  |

| 10 <b>(1,2)</b> | OA3/AN6     | AN7   | AN8   |  |  |  |

| 0x              | Vrefl       | VREFL | Vrefl |  |  |  |

bit 8 **CH123SB:** Channel 1, 2, 3 Positive Input Select for Sample MUXB bit In 12-bit mode (AD21B = 1), CH123SB is Unimplemented and is Read as '0':

| Value          | ADC Channel |         |         |  |  |  |  |

|----------------|-------------|---------|---------|--|--|--|--|

| value          | CH1 CH2 CH3 |         |         |  |  |  |  |

| 1 <b>(2)</b>   | OA1/AN3     | OA2/AN0 | OA3/AN6 |  |  |  |  |

| 0 <b>(1,2)</b> | OA2/AN0     | AN1     | AN2     |  |  |  |  |

bit 7-3 Unimplemented: Read as '0'

bit 2-1 **CH123NA<1:0>:** Channel 1, 2, 3 Negative Input Select for Sample MUXA bits In 12-bit mode (AD21B = 1), CH123NA is Unimplemented and is Read as '0':

| Value           | ADC Channel |       |       |  |  |  |

|-----------------|-------------|-------|-------|--|--|--|

| value           | CH1         | CH2   | CH3   |  |  |  |

| 11              | AN9         | AN10  | AN11  |  |  |  |

| 10 <b>(1,2)</b> | OA3/AN6     | AN7   | AN8   |  |  |  |

| 0x              | VREFL       | VREFL | VREFL |  |  |  |

- **Note 1:** AN0 through AN7 are repurposed when comparator and op amp functionality is enabled. See Figure 23-1 to determine how enabling a particular op amp or comparator affects selection choices for Channels 1, 2 and 3.

- 2: The OAx input is used if the corresponding op amp is selected (OPMODE (CMxCON<10>) = 1); otherwise, the ANx input is used.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-0      | U-0                                                                                            | U-0                                                                                                              | R/W-0                           | R/W-0                 | R/W-0                    | R/W-0                 | R/W-0                 |  |  |  |  |  |

|------------|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|---------------------------------|-----------------------|--------------------------|-----------------------|-----------------------|--|--|--|--|--|

| CH0NB      |                                                                                                | _                                                                                                                | CH0SB4 <sup>(1)</sup>           | CH0SB3 <sup>(1)</sup> | CH0SB2 <sup>(1)</sup>    | CH0SB1 <sup>(1)</sup> | CH0SB0 <sup>(1)</sup> |  |  |  |  |  |

| bit 15     |                                                                                                | -                                                                                                                |                                 |                       |                          |                       | bit 8                 |  |  |  |  |  |

|            |                                                                                                |                                                                                                                  |                                 |                       |                          |                       |                       |  |  |  |  |  |

| R/W-0      | U-0                                                                                            | U-0                                                                                                              | R/W-0                           | R/W-0                 | R/W-0                    | R/W-0                 | R/W-0                 |  |  |  |  |  |

| CH0NA      |                                                                                                | _                                                                                                                | CH0SA4 <sup>(1)</sup>           | CH0SA3 <sup>(1)</sup> | CH0SA2 <sup>(1)</sup>    | CH0SA1 <sup>(1)</sup> | CH0SA0 <sup>(1)</sup> |  |  |  |  |  |

| bit 7      |                                                                                                |                                                                                                                  |                                 |                       |                          |                       | bit C                 |  |  |  |  |  |

|            |                                                                                                |                                                                                                                  |                                 |                       |                          |                       |                       |  |  |  |  |  |

| Legend:    |                                                                                                |                                                                                                                  |                                 |                       |                          |                       |                       |  |  |  |  |  |

| R = Reada  |                                                                                                | W = Writable                                                                                                     |                                 |                       | nented bit, read         |                       |                       |  |  |  |  |  |

| -n = Value | e at POR                                                                                       | '1' = Bit is set                                                                                                 |                                 | '0' = Bit is clea     | ared                     | x = Bit is unkn       | own                   |  |  |  |  |  |

| hit 15     |                                                                                                |                                                                                                                  | Input Coloct for                | r Comple MUX          |                          |                       |                       |  |  |  |  |  |

| bit 15     |                                                                                                | nannel 0 Negative<br>el 0 negative input                                                                         |                                 |                       |                          |                       |                       |  |  |  |  |  |

|            |                                                                                                | el 0 negative input                                                                                              |                                 |                       |                          |                       |                       |  |  |  |  |  |

| bit 14-13  | Unimpleme                                                                                      | ented: Read as '0                                                                                                | )'                              |                       |                          |                       |                       |  |  |  |  |  |

| bit 12-8   | CH0SB<4:0                                                                                      | 0>: Channel 0 Po:                                                                                                | sitive Input Sele               | ect for Sample I      | MUXB bits <sup>(1)</sup> |                       |                       |  |  |  |  |  |

|            |                                                                                                | pen; use this sele                                                                                               |                                 |                       |                          | ement                 |                       |  |  |  |  |  |

|            | 11110 <b>= Ch</b>                                                                              | 11110 = Channel 0 positive input is connected to the CTMU temperature measurement diode (CTMU TEMP)              |                                 |                       |                          |                       |                       |  |  |  |  |  |

|            |                                                                                                | 11101 = Reserved                                                                                                 |                                 |                       |                          |                       |                       |  |  |  |  |  |

|            |                                                                                                | 11100 = Reserved<br>11011 = Reserved                                                                             |                                 |                       |                          |                       |                       |  |  |  |  |  |

|            | 11011 = Reserved<br>11010 = Channel 0 positive input is the output of OA3/AN6 <sup>(2,3)</sup> |                                                                                                                  |                                 |                       |                          |                       |                       |  |  |  |  |  |

|            |                                                                                                | 11001 = Channel 0 positive input is the output of OA2/AN0 <sup>(2)</sup>                                         |                                 |                       |                          |                       |                       |  |  |  |  |  |

|            |                                                                                                | nannel 0 positive i                                                                                              | input is the outp               | out of OA1/AN3        | (2)                      |                       |                       |  |  |  |  |  |

|            | 10111 <b>= Re</b>                                                                              | served                                                                                                           |                                 |                       |                          |                       |                       |  |  |  |  |  |

|            | •                                                                                              |                                                                                                                  |                                 |                       |                          |                       |                       |  |  |  |  |  |

|            | •                                                                                              |                                                                                                                  |                                 |                       |                          |                       |                       |  |  |  |  |  |

|            | 10000 <b>= Re</b>                                                                              |                                                                                                                  |                                 |                       |                          |                       |                       |  |  |  |  |  |

|            | 01111 = Ch                                                                                     | nannel 0 positive i                                                                                              | input is AN15 <sup>(3)</sup>    |                       |                          |                       |                       |  |  |  |  |  |

|            | 01110 = Cr                                                                                     | nannel 0 positive i<br>nannel 0 positive i                                                                       | input is AN14 <sup>(3)</sup>    |                       |                          |                       |                       |  |  |  |  |  |

|            | •                                                                                              |                                                                                                                  |                                 |                       |                          |                       |                       |  |  |  |  |  |

|            | •                                                                                              |                                                                                                                  |                                 |                       |                          |                       |                       |  |  |  |  |  |

|            | •                                                                                              |                                                                                                                  | (2)                             |                       |                          |                       |                       |  |  |  |  |  |

|            | 00010 = Ch                                                                                     | nannel 0 positive i                                                                                              | input is AN2 <sup>(3)</sup>     |                       |                          |                       |                       |  |  |  |  |  |

|            |                                                                                                | 00001 = Channel 0 positive input is AN1 <sup>(3)</sup><br>00000 = Channel 0 positive input is AN0 <sup>(3)</sup> |                                 |                       |                          |                       |                       |  |  |  |  |  |

| bit 7      |                                                                                                | nannel 0 Negative                                                                                                | •                               | r Samnle MI IX        | Δ hit                    |                       |                       |  |  |  |  |  |

|            | CINIA. OI                                                                                      | lanner o Negative                                                                                                | •                               |                       | A DIL                    |                       |                       |  |  |  |  |  |

|            | 1 = Channell                                                                                   | 1 0 negative input                                                                                               | is AN1(1)                       |                       |                          |                       |                       |  |  |  |  |  |

|            |                                                                                                | el 0 negative input<br>el 0 negative input                                                                       |                                 |                       |                          |                       |                       |  |  |  |  |  |

| bit 6-5    | 0 = Channe                                                                                     | el 0 negative input<br>el 0 negative input<br>ented: Read as '0                                                  | is Vrefl                        |                       |                          |                       |                       |  |  |  |  |  |

|            | 0 = Channe<br>Unimpleme<br>AN0 through A                                                       | el 0 negative input                                                                                              | is VREFL<br>,'<br>ed when compa |                       |                          |                       |                       |  |  |  |  |  |

#### REGISTER 23-6: AD1CHS0: ADC1 INPUT CHANNEL 0 SELECT REGISTER

3: See the "**Pin Diagrams**" section for the available analog channels for each device.

otherwise, the ANx input is used.

## 24.2 PTG Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 24.2.1 KEY RESOURCES

- "Peripheral Trigger Generator" (DS70669) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

# **REGISTER 24-3: PTGBTE: PTG BROADCAST TRIGGER ENABLE REGISTER**<sup>(1,2)</sup> (CONTINUED)

| bit 4 | OC1CS: Clock Source for OC1 bit                                                                                                                                                                |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Generates clock pulse when the broadcast command is executed</li> <li>0 = Does not generate clock pulse when the broadcast command is executed</li> </ul>                         |

| bit 3 | OC4TSS: Trigger/Synchronization Source for OC4 bit                                                                                                                                             |

|       | <ul> <li>1 = Generates Trigger/Synchronization when the broadcast command is executed</li> <li>0 = Does not generate Trigger/Synchronization when the broadcast command is executed</li> </ul> |

| bit 2 | OC3TSS: Trigger/Synchronization Source for OC3 bit                                                                                                                                             |

|       | <ul> <li>1 = Generates Trigger/Synchronization when the broadcast command is executed</li> <li>0 = Does not generate Trigger/Synchronization when the broadcast command is executed</li> </ul> |

| bit 1 | OC2TSS: Trigger/Synchronization Source for OC2 bit                                                                                                                                             |

|       | <ul> <li>1 = Generates Trigger/Synchronization when the broadcast command is executed</li> <li>0 = Does not generate Trigger/Synchronization when the broadcast command is executed</li> </ul> |

| bit 0 | OC1TSS: Trigger/Synchronization Source for OC1 bit                                                                                                                                             |

|       | <ul> <li>1 = Generates Trigger/Synchronization when the broadcast command is executed</li> <li>0 = Does not generate Trigger/Synchronization when the broadcast command is executed</li> </ul> |

|       |                                                                                                                                                                                                |

- **Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

- 2: This register is only used with the PTGCTRL OPTION = 1111 Step command.

# REGISTER 24-10: PTGADJ: PTG ADJUST REGISTER<sup>(1)</sup>

| R/W-0                                                                      | R/W-0 | R/W-0 | R/W-0 | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|----------------------------------------------------------------------------|-------|-------|-------|----------|-------|-------|-------|

|                                                                            |       |       | PTGA  | DJ<15:8> |       |       |       |

| bit 15                                                                     |       |       |       |          |       |       | bit 8 |

|                                                                            |       |       |       |          |       |       |       |

| R/W-0                                                                      | R/W-0 | R/W-0 | R/W-0 | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|                                                                            |       |       | PTGA  | DJ<7:0>  |       |       |       |

| bit 7                                                                      |       |       |       |          |       |       | bit 0 |

|                                                                            |       |       |       |          |       |       |       |

| Legend:                                                                    |       |       |       |          |       |       |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'       |       |       |       |          |       |       |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |       |       |       | nown     |       |       |       |

bit 15-0 **PTGADJ<15:0>:** PTG Adjust Register bits This register holds user-supplied data to be added to the PTGTxLIM, PTGCxLIM, PTGSDLIM or PTGL0 registers with the PTGADD command.

# REGISTER 24-11: PTGL0: PTG LITERAL 0 REGISTER<sup>(1)</sup>

| R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|-------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| PTGL0<15:8> |       |       |       |       |       |       |       |  |  |

| bit 15      |       |       |       |       |       |       | bit 8 |  |  |

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|--------|-------|-------|-------|

|       |       |       | PTGL  | )<7:0> |       |       |       |

| bit 7 |       |       |       |        |       |       | bit 0 |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | id as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

#### bit 15-0 PTGL0<15:0>: PTG Literal 0 Register bits

This register holds the 16-bit value to be written to the AD1CHS0 register with the  ${\tt PTGCTRL}$  Step command.

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

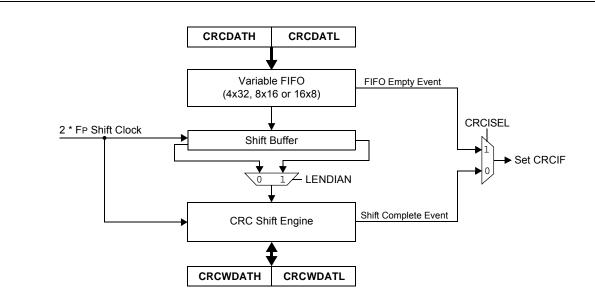

# 26.0 PROGRAMMABLE CYCLIC REDUNDANCY CHECK (CRC) GENERATOR

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Programmable Cyclic Redundancy Check (CRC)" (DS70346) of the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The programmable CRC generator offers the following features:

- User-programmable (up to 32nd order) polynomial CRC equation

- Interrupt output

- Data FIFO

The programmable CRC generator provides a hardware implemented method of quickly generating checksums for various networking and security applications. It offers the following features:

- User-programmable CRC polynomial equation, up to 32 bits

- Programmable shift direction (little or big-endian)

- · Independent data and polynomial lengths

- Configurable interrupt output

- Data FIFO

A simplified block diagram of the CRC generator is shown in Figure 26-1. A simple version of the CRC shift engine is shown in Figure 26-2.

#### FIGURE 26-1: CRC BLOCK DIAGRAM

#### 29.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16 and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

#### 29.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline

assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

#### 29.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

## 29.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- · Command-line interface

- · Rich directive set

- Flexible macro language

- · MPLAB X IDE compatibility

|        |        |                                                             | (unless            | s otherw | ating Covinse stat | <b>ed)</b><br>-40°C | s: 3.0V to 3.6V<br>$\leq$ TA $\leq$ +85°C for Industrial<br>$\leq$ TA $\leq$ +125°C for Extended                                                                       |

|--------|--------|-------------------------------------------------------------|--------------------|----------|--------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param. | Symbol | Characteristic                                              | Min.               | Тур.     | Max.               | Units               | Conditions                                                                                                                                                             |

| DO10   | Vol    | Output Low Voltage<br>4x Sink Driver Pins <sup>(2)</sup>    |                    |          | 0.4                | V                   | VDD = 3.3V,<br>$IOL \le 6 \text{ mA}, -40^{\circ}\text{C} \le Ta \le +85^{\circ}\text{C}$<br>$IOL \le 5 \text{ mA}, +85^{\circ}\text{C} < Ta \le +125^{\circ}\text{C}$ |

|        |        | Output Low Voltage<br>8x Sink Driver Pins <sup>(3)</sup>    | _                  |          | 0.4                | V                   |                                                                                                                                                                        |

| DO20   | Vон    | Output High Voltage<br>4x Source Driver Pins <sup>(2)</sup> | 2.4                |          | _                  | V                   | $IOH \ge -10 \text{ mA}, \text{ VDD} = 3.3 \text{ V}$                                                                                                                  |

|        |        | Output High Voltage<br>8x Source Driver Pins <sup>(3)</sup> | 2.4                | _        | —                  | V                   | $IOH \ge -15 \text{ mA}, \text{ VDD} = 3.3 \text{ V}$                                                                                                                  |

| DO20A  | Von1   | Output High Voltage                                         | 1.5(1)             | _        |                    | V                   | $IOH \ge -14 \text{ mA}, \text{ VDD} = 3.3 \text{V}$                                                                                                                   |

|        |        | 4x Source Driver Pins <sup>(2)</sup>                        | 2.0 <sup>(1)</sup> | _        | —                  |                     | $IOH \ge -12 \text{ mA}, \text{ VDD} = 3.3 \text{V}$                                                                                                                   |

|        |        |                                                             | 3.0(1)             |          | —                  |                     | $IOH \ge -7 \text{ mA}, \text{ VDD} = 3.3 \text{V}$                                                                                                                    |

|        |        | Output High Voltage                                         | 1.5 <sup>(1)</sup> | —        | —                  | V                   | $IOH \geq -22  mA,  VDD = 3.3  V$                                                                                                                                      |

|        |        | 8x Source Driver Pins <sup>(3)</sup>                        | 2.0 <sup>(1)</sup> | —        | —                  |                     | IOH $\geq$ -18 mA, VDD = 3.3V                                                                                                                                          |

|        |        |                                                             | 3.0(1)             | —        | —                  | 1                   | IOH $\geq$ -10 mA, VDD = 3.3V                                                                                                                                          |

## TABLE 30-12: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

Note 1: Parameters are characterized but not tested.

2: Includes all I/O pins that are not 8x Sink Driver pins (see below).

Includes the following pins:

For devices with less than 64 pins: RA3, RA4, RA9, RB<7:15> and RC3

For 64-pin devices: RA4, RA9, RB<7:15>, RC3 and RC15

#### TABLE 30-13: ELECTRICAL CHARACTERISTICS: BOR

| DC CHAR      | DC CHARACTERISTICS |                                            | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)}^{(1)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |      |       |                        |  |

|--------------|--------------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|------------------------|--|

| Param<br>No. | Symbol             | Characteristic                             | Min. <sup>(2)</sup>                                                                                                                                                                                                                                                                           | Тур. | Max. | Units | Conditions             |  |

| BO10         | VBOR               | BOR Event on VDD Transition<br>High-to-Low | 2.65                                                                                                                                                                                                                                                                                          | _    | 2.95 | V     | VDD<br>(Notes 2 and 3) |  |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance.

**2:** Parameters are for design guidance only and are not tested in manufacturing.

3: The VBOR specification is relative to VDD.

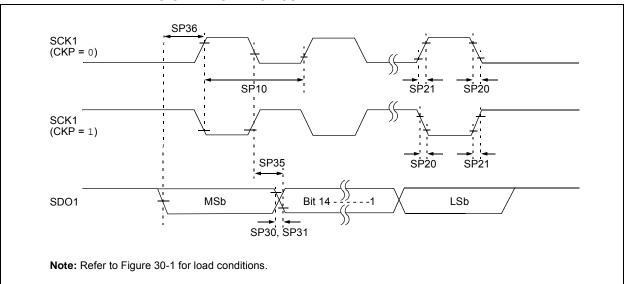

#### FIGURE 30-23: SPI1 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 1) TIMING CHARACTERISTICS

#### TABLE 30-42: SPI1 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                              | (unless o | I Operatin<br>otherwise<br>g tempera | stated)<br>ature -4 | 0°C ≤ Ta | <b>0V to 3.6V</b><br>≤ +85°C for Industrial<br>≤ +125°C for Extended |

|--------------------|-----------------------|----------------------------------------------|-----------|--------------------------------------|---------------------|----------|----------------------------------------------------------------------|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>                | Min.      | Typ. <sup>(2)</sup>                  | Max.                | Units    | Conditions                                                           |

| SP10               | FscP                  | Maximum SCK1 Frequency                       | —         |                                      | 15                  | MHz      | (Note 3)                                                             |

| SP20               | TscF                  | SCK1 Output Fall Time                        | -         | -                                    | _                   | ns       | See Parameter DO32<br>(Note 4)                                       |

| SP21               | TscR                  | SCK1 Output Rise Time                        | —         | —                                    | _                   | ns       | See Parameter DO31 (Note 4)                                          |

| SP30               | TdoF                  | SDO1 Data Output Fall Time                   | -         | -                                    | _                   | ns       | See Parameter DO32<br>(Note 4)                                       |

| SP31               | TdoR                  | SDO1 Data Output Rise Time                   | —         | —                                    | _                   | ns       | See Parameter DO31<br>(Note 4)                                       |

| SP35               | TscH2doV,<br>TscL2doV | SDO1 Data Output Valid after<br>SCK1 Edge    | —         | 6                                    | 20                  | ns       |                                                                      |

| SP36               | TdiV2scH,<br>TdiV2scL | SDO1 Data Output Setup to<br>First SCK1 Edge | 30        |                                      |                     | ns       |                                                                      |

Note 1: These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCK1 is 66.7 ns. Therefore, the clock generated in Master mode must not violate this specification.

4: Assumes 50 pF load on all SPI1 pins.

| AC CHARACTERISTICS |        |                                                      | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated) <sup>(1)</sup> Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |         |                                   |          |                                                                                               |  |  |

|--------------------|--------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------------------------------|----------|-----------------------------------------------------------------------------------------------|--|--|

| Param<br>No.       | Symbol | Characteristic                                       | Min.                                                                                                                                                                                                                 | Тур.    | Max.                              | Units    | Conditions                                                                                    |  |  |

|                    |        |                                                      | Devi                                                                                                                                                                                                                 | ce Sup  | ply                               |          |                                                                                               |  |  |

| AD01               | AVDD   | Module VDD Supply                                    | Greater of:<br>VDD – 0.3<br>or 3.0                                                                                                                                                                                   |         | Lesser of:<br>VDD + 0.3<br>or 3.6 | V        |                                                                                               |  |  |

| AD02               | AVss   | Module Vss Supply                                    | Vss – 0.3                                                                                                                                                                                                            |         | Vss + 0.3                         | V        |                                                                                               |  |  |

|                    |        |                                                      | Refere                                                                                                                                                                                                               | ence In | puts                              |          |                                                                                               |  |  |

| AD05               | Vrefh  | Reference Voltage High                               | AVss + 2.5                                                                                                                                                                                                           |         | AVDD                              | V        | VREFH = VREF+<br>VREFL = VREF- <b>(Note 1)</b>                                                |  |  |

| AD05a              |        |                                                      | 3.0                                                                                                                                                                                                                  | _       | 3.6                               | V        | VREFH = AVDD<br>VREFL = AVSS = 0                                                              |  |  |

| AD06               | VREFL  | Reference Voltage Low                                | AVss                                                                                                                                                                                                                 |         | AVDD - 2.5                        | V        | (Note 1)                                                                                      |  |  |

| AD06a              |        |                                                      | 0                                                                                                                                                                                                                    |         | 0                                 | V        | VREFH = AVDD<br>VREFL = AVSS = 0                                                              |  |  |

| AD07               | VREF   | Absolute Reference<br>Voltage                        | 2.5                                                                                                                                                                                                                  | _       | 3.6                               | V        | VREF = VREFH - VREFL                                                                          |  |  |

| AD08               | IREF   | Current Drain                                        |                                                                                                                                                                                                                      |         | 10<br>600                         | μΑ<br>μΑ | ADC off<br>ADC on                                                                             |  |  |

| AD09               | Iad    | Operating Current <sup>(2)</sup>                     | —                                                                                                                                                                                                                    | 5       | _                                 | mA       | ADC operating in 10-bit mode (Note 1)                                                         |  |  |

|                    |        |                                                      | —                                                                                                                                                                                                                    | 2       | —                                 | mA       | ADC operating in 12-bit mode (Note 1)                                                         |  |  |

|                    | •      |                                                      | Ana                                                                                                                                                                                                                  | log Inp | ut                                |          |                                                                                               |  |  |

| AD12               | Vinh   | Input Voltage Range<br>VinH                          | VINL                                                                                                                                                                                                                 |         | Vrefh                             | V        | This voltage reflects Sample-and-<br>Hold Channels 0, 1, 2 and 3<br>(CH0-CH3), positive input |  |  |

| AD13               | VINL   | Input Voltage Range<br>VINL                          | Vrefl                                                                                                                                                                                                                | _       | AVss + 1V                         | V        | This voltage reflects Sample-and-<br>Hold Channels 0, 1, 2 and 3<br>(CH0-CH3), negative input |  |  |