Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 256КВ (85.5К х 24)                                                              |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 16K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 9x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

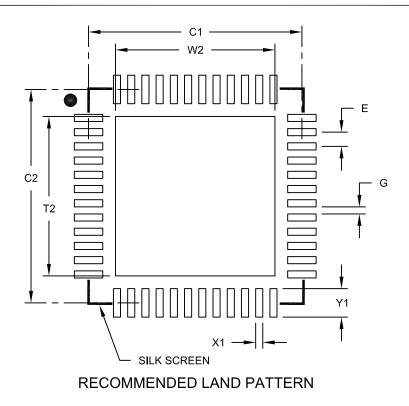

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-VFTLA Exposed Pad                                                            |

| Supplier Device Package    | 44-VTLA (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep256mc204t-e-tl |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

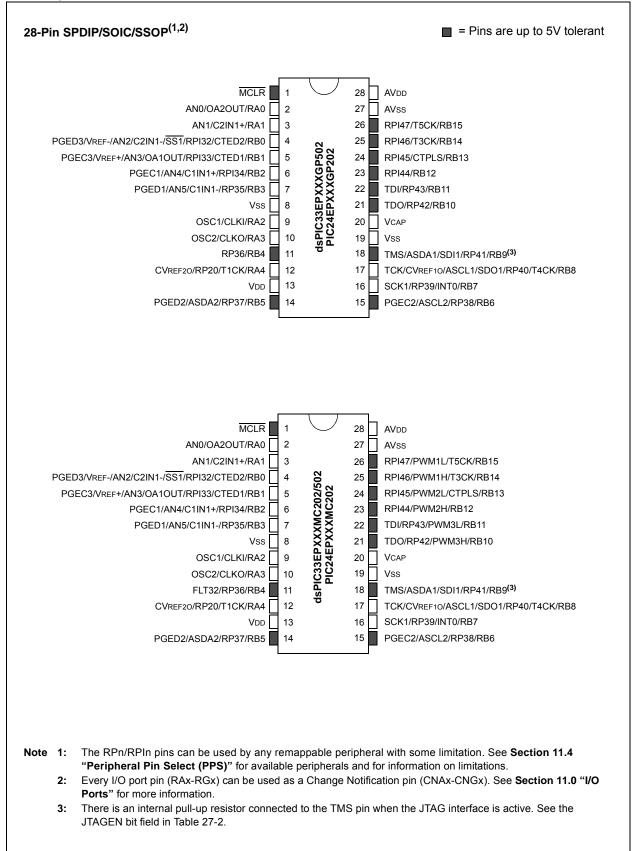

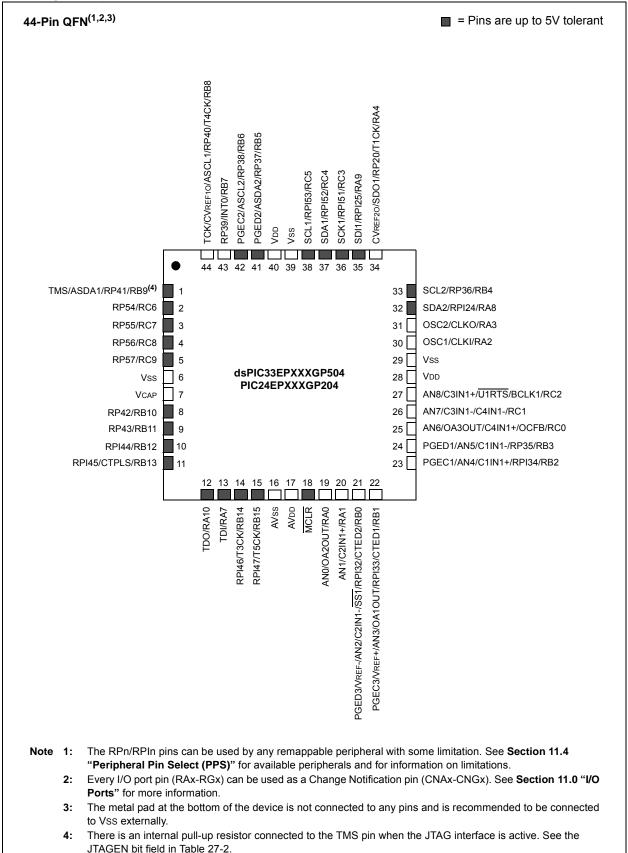

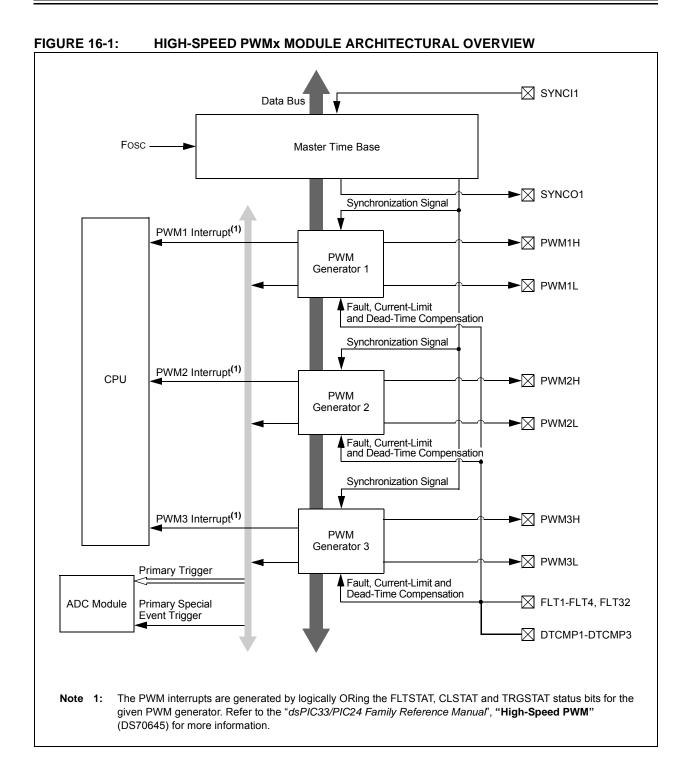

### dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

#### **Pin Diagrams**

#### **Pin Diagrams (Continued)**

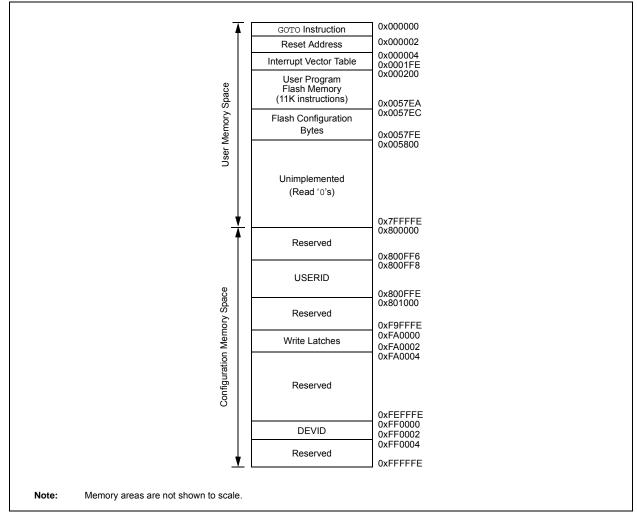

### 4.0 MEMORY ORGANIZATION

Note: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXGP/MC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Program Memory" (DS70613) in the "dsPIC33/PIC24 Family Reference Manual', which is available from the Microchip web site (www.microchip.com).

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X architecture features separate program and data memory spaces, and buses. This architecture also allows the direct access of program memory from the Data Space (DS) during code execution.

### 4.1 Program Address Space

The program address memory space of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices is 4M instructions. The space is addressable by a 24-bit value derived either from the 23-bit PC during program execution, or from table operation or Data Space remapping, as described in Section 4.8 "Interfacing Program and Data Memory Spaces".

User application access to the program memory space is restricted to the lower half of the address range (0x000000 to 0x7FFFF). The exception is the use of TBLRD operations, which use TBLPAG<7> to read Device ID sections of the configuration memory space.

The program memory maps, which are presented by device family and memory size, are shown in Figure 4-1 through Figure 4-5.

# FIGURE 4-1: PROGRAM MEMORY MAP FOR dsPIC33EP32GP50X, dsPIC33EP32MC20X/50X AND PIC24EP32GP/MC20X DEVICES

|             |       |        |                   |        |        |        |        | •            |              |               |              |       |        |       |       |       |       |               |

|-------------|-------|--------|-------------------|--------|--------|--------|--------|--------------|--------------|---------------|--------------|-------|--------|-------|-------|-------|-------|---------------|

| SFR<br>Name | Addr. | Bit 15 | Bit 14            | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9        | Bit 8        | Bit 7         | Bit 6        | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| TMR1        | 0100  |        |                   |        |        |        |        |              | Timer1       | Register      |              |       |        |       |       |       |       | xxxx          |

| PR1         | 0102  |        |                   |        |        |        |        |              | Period F     | Register 1    |              |       |        |       |       |       |       | FFFF          |

| T1CON       | 0104  | TON    | _                 | TSIDL  | _      | _      | _      | _            | _            | _             | TGATE        | TCKP  | S<1:0> | —     | TSYNC | TCS   |       | 0000          |

| TMR2        | 0106  |        |                   |        |        |        |        |              | Timer2       | Register      |              |       |        |       |       |       |       | xxxx          |

| TMR3HLD     | 0108  |        |                   |        |        |        | Time   | er3 Holding  | Register (fo | r 32-bit time | r operations | only) |        |       |       |       |       | xxxx          |

| TMR3        | 010A  |        |                   |        |        |        |        |              | Timer3       | Register      |              |       |        |       |       |       |       | xxxx          |

| PR2         | 010C  |        |                   |        |        |        |        |              | Period F     | Register 2    |              |       |        |       |       |       |       | FFFF          |

| PR3         | 010E  |        |                   |        |        |        |        |              | Period F     | Register 3    |              |       |        |       |       |       |       | FFFF          |

| T2CON       | 0110  | TON    | —                 | TSIDL  | —      | —      | —      | _            | —            | —             | TGATE        | TCKP  | S<1:0> | T32   | _     | TCS   |       | 0000          |

| T3CON       | 0112  | TON    | -                 | TSIDL  | _      | _      | _      | _            | -            | _             | TGATE        | TCKP  | S<1:0> | _     | _     | TCS   |       | 0000          |

| TMR4        | 0114  |        |                   | •      | •      | •      | •      | •            | Timer4       | Register      |              |       |        | •     |       | •     |       | xxxx          |

| TMR5HLD     | 0116  |        |                   |        |        |        | Т      | imer5 Holdir | ng Register  | (for 32-bit o | perations on | ly)   |        |       |       |       |       | xxxx          |

| TMR5        | 0118  |        |                   |        |        |        |        |              | Timer5       | Register      |              |       |        |       |       |       |       | xxxx          |

| PR4         | 011A  |        |                   |        |        |        |        |              | Period F     | Register 4    |              |       |        |       |       |       |       | FFFF          |

| PR5         | 011C  |        | Period Register 5 |        |        |        |        |              | FFFF         |               |              |       |        |       |       |       |       |               |

| T4CON       | 011E  | TON    | —                 | TSIDL  | —      | —      | —      | —            | _            | —             | TGATE        | TCKP  | S<1:0> | T32   | —     | TCS   | —     | 0000          |

| T5CON       | 0120  | TON    | _                 | TSIDL  | _      | _      | _      | _            | _            | _             | TGATE        | TCKP  | S<1:0> | _     | _     | TCS   | _     | 0000          |

### TABLE 4-8: TIMER1 THROUGH TIMER5 REGISTER MAP

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-59: PORTA REGISTER MAP FOR PIC24EPXXXGP/MC202 AND dsPIC33EPXXXGP/MC202/502 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|--------|--------|--------|--------|--------|---------------|

| TRISA        | 0E00  | _      | —      | _      | _      | _      | -      | _     | _     | _     | _     | _     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 001F          |

| PORTA        | 0E02  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | RA4    | RA3    | RA2    | RA1    | RA0    | 0000          |

| LATA         | 0E04  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | LATA4  | LATA3  | LATA2  | LA1TA1 | LA0TA0 | 0000          |

| ODCA         | 0E06  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | ODCA4  | ODCA3  | ODCA2  | ODCA1  | ODCA0  | 0000          |

| CNENA        | 0E08  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | CNIEA4 | CNIEA3 | CNIEA2 | CNIEA1 | CNIEA0 | 0000          |

| CNPUA        | 0E0A  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | CNPUA4 | CNPUA3 | CNPUA2 | CNPUA1 | CNPUA0 | 0000          |

| CNPDA        | 0E0C  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | CNPDA4 | CNPDA3 | CNPDA2 | CNPDA1 | CNPDA0 | 0000          |

| ANSELA       | 0E0E  | _      | —      | _      | —      | _      | _      | _     | _     | _     | _     | _     | ANSA4  | _      | _      | ANSA1  | ANSA0  | 0013          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-60: PORTB REGISTER MAP FOR PIC24EPXXXGP/MC202 AND dsPIC33EPXXXGP/MC202/502 DEVICES ONLY

| File<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISB        | 0E10  | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF          |

| PORTB        | 0E12  | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx          |

| LATB         | 0E14  | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | xxxx          |

| ODCB         | 0E16  | ODCB15  | ODCB14  | ODCB13  | ODCB12  | ODCB11  | ODCB10  | ODCB9  | ODCB8  | ODCB7  | ODCB6  | ODCB5  | ODCB4  | ODCB3  | ODCB2  | ODCB1  | ODCB0  | 0000          |

| CNENB        | 0E18  | CNIEB15 | CNIEB14 | CNIEB13 | CNIEB12 | CNIEB11 | CNIEB10 | CNIEB9 | CNIEB8 | CNIEB7 | CNIEB6 | CNIEB5 | CNIEB4 | CNIEB3 | CNIEB2 | CNIEB1 | CNIEB0 | 0000          |

| CNPUB        | 0E1A  | CNPUB15 | CNPUB14 | CNPUB13 | CNPUB12 | CNPUB11 | CNPUB10 | CNPUB9 | CNPUB8 | CNPUB7 | CNPUB6 | CNPUB5 | CNPUB4 | CNPUB3 | CNPUB2 | CNPUB1 | CNPUB0 | 0000          |

| CNPDB        | 0E1C  | CNPDB15 | CNPDB14 | CNPDB13 | CNPDB12 | CNPDB11 | CNPDB10 | CNPDB9 | CNPDB8 | CNPDB7 | CNPDB6 | CNPDB5 | CNPDB4 | CNPDB3 | CNPDB2 | CNPDB1 | CNPDB0 | 0000          |

| ANSELB       | 0E1E  | _       | _       | _       | _       | _       | _       | -      | ANSB8  | _      |        | _      | _      | ANSB3  | ANSB2  | ANSB1  | ANSB0  | 010F          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Allocating different Page registers for read and write access allows the architecture to support data movement between different pages in data memory. This is accomplished by setting the DSRPAG register value to the page from which you want to read, and configuring the DSWPAG register to the page to which it needs to be written. Data can also be moved from different PSV to EDS pages, by configuring the DSRPAG and DSWPAG registers to address PSV and EDS space, respectively. The data can be moved between pages by a single instruction.

When an EDS or PSV page overflow or underflow occurs, EA<15> is cleared as a result of the register indirect EA calculation. An overflow or underflow of the EA in the EDS or PSV pages can occur at the page boundaries when:

- The initial address prior to modification addresses an EDS or PSV page

- The EA calculation uses Pre-Modified or Post-Modified Register Indirect Addressing; however, this does not include Register Offset Addressing

In general, when an overflow is detected, the DSxPAG register is incremented and the EA<15> bit is set to keep the base address within the EDS or PSV window. When an underflow is detected, the DSxPAG register is decremented and the EA<15> bit is set to keep the base address within the EDS or PSV window. This creates a linear EDS and PSV address space, but only when using Register Indirect Addressing modes.

Exceptions to the operation described above arise when entering and exiting the boundaries of Page 0, EDS and PSV spaces. Table 4-61 lists the effects of overflow and underflow scenarios at different boundaries.

In the following cases, when overflow or underflow occurs, the EA<15> bit is set and the DSxPAG is not modified; therefore, the EA will wrap to the beginning of the current page:

- · Register Indirect with Register Offset Addressing

- Modulo Addressing

- · Bit-Reversed Addressing

|             | -                   | SV SI ACE BOON |              |                        |                |              |                        |

|-------------|---------------------|----------------|--------------|------------------------|----------------|--------------|------------------------|

| 0/11        |                     |                | Before       |                        |                | After        |                        |

| O/U,<br>R/W | Operation           | DSxPAG         | DS<br>EA<15> | Page<br>Description    | DSxPAG         | DS<br>EA<15> | Page<br>Description    |

| O,<br>Read  |                     | DSRPAG = 0x1FF | 1            | EDS: Last page         | DSRPAG = 0x1FF | 0            | See Note 1             |

| O,<br>Read  | [++Wn]              | DSRPAG = 0x2FF | 1            | PSV: Last lsw<br>page  | DSRPAG = 0x300 | 1            | PSV: First MSB<br>page |

| O,<br>Read  | <b>Or</b><br>[Wn++] | DSRPAG = 0x3FF | 1            | PSV: Last MSB<br>page  | DSRPAG = 0x3FF | 0            | See Note 1             |

| O,<br>Write |                     | DSWPAG = 0x1FF | 1            | EDS: Last page         | DSWPAG = 0x1FF | 0            | See Note 1             |

| U,<br>Read  |                     | DSRPAG = 0x001 | 1            | PSV page               | DSRPAG = 0x001 | 0            | See Note 1             |

| U,<br>Read  | [Wn]<br>Or<br>[Wn]  | DSRPAG = 0x200 | 1            | PSV: First Isw<br>page | DSRPAG = 0x200 | 0            | See Note 1             |

| U,<br>Read  | [ //11 - ]          | DSRPAG = 0x300 | 1            | PSV: First MSB<br>page | DSRPAG = 0x2FF | 1            | PSV: Last Isw<br>page  |

# TABLE 4-61: OVERFLOW AND UNDERFLOW SCENARIOS AT PAGE 0, EDS and PSV SPACE BOUNDARIES<sup>(2,3,4)</sup>

Legend: O = Overflow, U = Underflow, R = Read, W = Write

Note 1: The Register Indirect Addressing now addresses a location in the base Data Space (0x0000-0x8000).

2: An EDS access with DSxPAG = 0x000 will generate an address error trap.

- **3:** Only reads from PS are supported using DSRPAG. An attempt to write to PS using DSWPAG will generate an address error trap.

- 4: Pseudo-Linear Addressing is not supported for large offsets.

| R/W-0                 | R/W-0                                         | R/W-0                                                | R/W-0                                         | R/W-0                              | U-0              | U-0             | U-0     |

|-----------------------|-----------------------------------------------|------------------------------------------------------|-----------------------------------------------|------------------------------------|------------------|-----------------|---------|

| CHEN                  | SIZE                                          | DIR                                                  | HALF                                          | NULLW                              |                  |                 |         |

| bit 15                |                                               |                                                      |                                               |                                    |                  |                 | bit     |

| U-0                   | U-0                                           | R/W-0                                                | R/W-0                                         | U-0                                | U-0              | R/W-0           | R/W-0   |

|                       | 0-0                                           | AMODE1                                               | AMODE0                                        | 0-0                                | 0-0              | MODE1           | MODE0   |

| bit 7                 |                                               | AWODET                                               | 7 WIODE0                                      |                                    |                  | MODET           | bit     |

| Lovende               |                                               |                                                      |                                               |                                    |                  |                 |         |

| Legend:<br>R = Readab | lo hit                                        | M - Mritabla                                         | hit.                                          |                                    | monted bit rec   | ud aa '0'       |         |

|                       |                                               | W = Writable                                         |                                               | -                                  | mented bit, rea  |                 |         |

| -n = Value a          | IT POR                                        | '1' = Bit is set                                     |                                               | '0' = Bit is cle                   | ared             | x = Bit is unkr | nown    |

| bit 15                | CHEN: DMA                                     | Channel Enabl                                        | e bit                                         |                                    |                  |                 |         |

|                       | 1 = Channel<br>0 = Channel                    |                                                      |                                               |                                    |                  |                 |         |

| bit 14                |                                               | ata Transfer S                                       | ze hit                                        |                                    |                  |                 |         |

|                       | 1 = Byte                                      |                                                      |                                               |                                    |                  |                 |         |

|                       | 0 = Word                                      |                                                      |                                               |                                    |                  |                 |         |

| bit 13                | DIR: DMA Tra                                  | ansfer Directior                                     | n bit (source/d                               | estination bus                     | select)          |                 |         |

|                       |                                               | om RAM addre<br>om peripheral a                      |                                               |                                    |                  |                 |         |

| bit 12                |                                               | Block Transfer                                       |                                               |                                    |                  |                 |         |

|                       | 1 = Initiates i                               | nterrupt when                                        | half of the data                              | a has been mo                      |                  |                 |         |

| bit 11                |                                               | Data Periphera                                       |                                               |                                    |                  |                 |         |

|                       |                                               | write to periph                                      |                                               |                                    | e (DIR bit must  | also be clear)  |         |

| bit 10-6              | Unimplemen                                    | ted: Read as '                                       | 0'                                            |                                    |                  |                 |         |

| bit 5-4               | AMODE<1:0                                     | -: DMA Chann                                         | el Addressing                                 | Mode Select b                      | oits             |                 |         |

|                       | 11 = Reserve<br>10 = Periphe<br>01 = Register |                                                      | ressing mode<br>ut Post-Increm                | nent mode                          |                  |                 |         |

| bit 3-2               | Unimplemen                                    | ted: Read as '                                       | 0'                                            |                                    |                  |                 |         |

| bit 1-0               | -                                             | DMA Channel                                          |                                               | de Select bits                     |                  |                 |         |

|                       | 11 = One-Sho<br>10 = Continue                 | ot, Ping-Pong r<br>ous, Ping-Pong<br>ot, Ping-Pong r | nodes are ena<br>modes are e<br>nodes are dis | abled (one bloc<br>nabled<br>abled | ck transfer fror | n/to each DMA t | ouffer) |

#### REGISTER 8-1: DMAXCON: DMA CHANNEL X CONTROL REGISTER

#### 10.3 Doze Mode

The preferred strategies for reducing power consumption are changing clock speed and invoking one of the powersaving modes. In some circumstances, this cannot be practical. For example, it may be necessary for an application to maintain uninterrupted synchronous communication, even while it is doing nothing else. Reducing system clock speed can introduce communication errors, while using a power-saving mode can stop communications completely.

Doze mode is a simple and effective alternative method to reduce power consumption while the device is still executing code. In this mode, the system clock continues to operate from the same source and at the same speed. Peripheral modules continue to be clocked at the same speed, while the CPU clock speed is reduced. Synchronization between the two clock domains is maintained, allowing the peripherals to access the SFRs while the CPU executes code at a slower rate.

Doze mode is enabled by setting the DOZEN bit (CLKDIV<11>). The ratio between peripheral and core clock speed is determined by the DOZE<2:0> bits (CLKDIV<14:12>). There are eight possible configurations, from 1:1 to 1:128, with 1:1 being the default setting.

Programs can use Doze mode to selectively reduce power consumption in event-driven applications. This allows clock-sensitive functions, such as synchronous communications, to continue without interruption while the CPU Idles, waiting for something to invoke an interrupt routine. An automatic return to full-speed CPU operation on interrupts can be enabled by setting the ROI bit (CLKDIV<15>). By default, interrupt events have no effect on Doze mode operation.

For example, suppose the device is operating at 20 MIPS and the ECAN<sup>™</sup> module has been configured for 500 kbps, based on this device operating speed. If the device is placed in Doze mode with a clock frequency ratio of 1:4, the ECAN module continues to communicate at the required bit rate of 500 kbps, but the CPU now starts executing instructions at a frequency of 5 MIPS.

#### 10.4 Peripheral Module Disable

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled using the appropriate PMD control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers do not have effect and read values are invalid.

A peripheral module is enabled only if both the associated bit in the PMD register is cleared and the peripheral is supported by the specific dsPIC<sup>®</sup> DSC variant. If the peripheral is present in the device, it is enabled in the PMD register by default.

| Note: | If a PMD bit is set, the corresponding        |

|-------|-----------------------------------------------|

|       | module is disabled after a delay of one       |

|       | instruction cycle. Similarly, if a PMD bit is |

|       | cleared, the corresponding module is          |

|       | enabled after a delay of one instruction      |

|       | cycle (assuming the module control regis-     |

|       | ters are already configured to enable         |

|       | module operation).                            |

### 10.5 Power-Saving Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

#### 10.5.1 KEY RESOURCES

- "Watchdog Timer and Power-Saving Modes" (DS70615) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| REGISTER     | TU-5: PIVID6                       | . PERIPHER       |                           | DISABLE C         | UNIROL RE             | GISIER 6              |                       |

|--------------|------------------------------------|------------------|---------------------------|-------------------|-----------------------|-----------------------|-----------------------|

| U-0          | U-0                                | U-0              | U-0                       | U-0               | R/W-0                 | R/W-0                 | R/W-0                 |

| —            | —                                  | —                | —                         | _                 | PWM3MD <sup>(1)</sup> | PWM2MD <sup>(1)</sup> | PWM1MD <sup>(1)</sup> |

| bit 15       |                                    |                  |                           |                   |                       |                       | bit 8                 |

|              |                                    |                  |                           |                   |                       |                       |                       |

| U-0          | U-0                                | U-0              | U-0                       | U-0               | U-0                   | U-0                   | U-0                   |

|              |                                    |                  |                           |                   |                       |                       |                       |

| bit 7        |                                    |                  |                           |                   |                       |                       | bit 0                 |

|              |                                    |                  |                           |                   |                       |                       |                       |

| Legend:      |                                    |                  |                           |                   |                       |                       |                       |

| R = Readab   | le bit                             | W = Writable     | bit                       | U = Unimplen      | nented bit, read      | l as '0'              |                       |

| -n = Value a | -n = Value at POR '1' = Bit is set |                  |                           | '0' = Bit is clea | ared                  | x = Bit is unkr       | iown                  |

|              |                                    |                  |                           |                   |                       |                       |                       |

| bit 15-11    | Unimplement                        | ted: Read as '   | כ'                        |                   |                       |                       |                       |

| bit 10       | PWM3MD: P\                         | NM3 Module D     | isable bit <sup>(1)</sup> |                   |                       |                       |                       |

|              | 1 = PWM3 mo                        | odule is disable | ed                        |                   |                       |                       |                       |

|              | 0 = PWM3 mo                        | odule is enable  | d                         |                   |                       |                       |                       |

| bit 9        | PWM2MD: P\                         | NM2 Module D     | isable bit <sup>(1)</sup> |                   |                       |                       |                       |

|              | 1 = PWM2 mo                        | odule is disable | ed                        |                   |                       |                       |                       |

|              | 0 = PWM2 mo                        | odule is enable  | d                         |                   |                       |                       |                       |

| bit 8        | PWM1MD: P\                         | NM1 Module D     | isable bit <sup>(1)</sup> |                   |                       |                       |                       |

|              |                                    | odule is disable |                           |                   |                       |                       |                       |

|              | 0 = PWM1 mo                        | odule is enable  | d                         |                   |                       |                       |                       |

| bit 7-0      | Unimplement                        | ted: Read as '   | כ'                        |                   |                       |                       |                       |

### REGISTER 10-5: PMD6: PERIPHERAL MODULE DISABLE CONTROL REGISTER 6

Note 1: This bit is available on dsPIC33EPXXXMC50X/20X and PIC24EPXXXMC20X devices only.

### dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

### REGISTER 19-1: I2CxCON: I2Cx CONTROL REGISTER (CONTINUED)

| bit 6         | <b>STREN:</b> SCLx Clock Stretch Enable bit (when operating as I <sup>2</sup> C slave)<br>Used in conjunction with the SCLREL bit.<br>1 = Enables software or receives clock stretching<br>0 = Disables software or receives clock stretching |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5         | ACKDT: Acknowledge Data bit (when operating as I <sup>2</sup> C master, applicable during master receive)                                                                                                                                     |

|               | Value that is transmitted when the software initiates an Acknowledge sequence.<br>1 = Sends NACK during Acknowledge<br>0 = Sends ACK during Acknowledge                                                                                       |

| bit 4         | <b>ACKEN:</b> Acknowledge Sequence Enable bit (when operating as I <sup>2</sup> C master, applicable during master receive)                                                                                                                   |

|               | <ul> <li>1 = Initiates Acknowledge sequence on SDAx and SCLx pins and transmits ACKDT data bit. Hardware is clear at the end of the master Acknowledge sequence.</li> <li>0 = Acknowledge sequence is not in progress</li> </ul>              |

| bit 3         | <b>RCEN:</b> Receive Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                                   |

|               | <ul> <li>1 = Enables Receive mode for I<sup>2</sup>C. Hardware is clear at the end of the eighth bit of the master receive data byte.</li> <li>0 = Receive sequence is not in progress</li> </ul>                                             |

| bit 2         | <b>PEN:</b> Stop Condition Enable bit (when operating as $I^2C$ master)                                                                                                                                                                       |

| 511 2         | 1 = Initiates Stop condition on SDAx and SCLx pins. Hardware is clear at the end of the master Stop sequence.                                                                                                                                 |

| <b>h</b> :+ 4 | 0 = Stop condition is not in progress                                                                                                                                                                                                         |

| bit 1         | <b>RSEN:</b> Repeated Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                  |

|               | <ul> <li>1 = Initiates Repeated Start condition on SDAx and SCLx pins. Hardware is clear at the end of the master Repeated Start sequence.</li> <li>0 = Repeated Start condition is not in progress</li> </ul>                                |

| bit 0         | <b>SEN:</b> Start Condition Enable bit (when operating as $l^2C$ master)                                                                                                                                                                      |

|               | <ul> <li>1 = Initiates Start condition on SDAx and SCLx pins. Hardware is clear at the end of the master Start sequence.</li> <li>0 = Start condition is not in progress</li> </ul>                                                           |

**Note 1:** When performing master operations, ensure that the IPMIEN bit is set to '0'.

| R/W-0       R/W-0       U-0       U-0       U-0       U-0         DMABS2       DMABS1       DMABS0                                                                                                                                                                                                                                                                                                                                                                                                                |       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| bit 15<br>U-0 U-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0<br>FSA4 FSA3 FSA2 FSA1<br>bit 7<br>Legend:<br>R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'<br>-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknov<br>bit 15-13 DMABS<2:0>: DMA Buffer Size bits<br>111 = Reserved<br>110 = 32 buffers in RAM<br>101 = 24 buffers in RAM                                                                                                                                               | U-0   |

| U-0       U-0       U-0       R/W-0       R/W-0       R/W-0       R/W-0         —       —       —       FSA4       FSA3       FSA2       FSA1         bit 7         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-13       DMABS<2:0>: DMA Buffer Size bits       111 = Reserved       110 = 32 buffers in RAM       101 = 24 buffers in RAM | —     |

| FSA4     FSA3     FSA2     FSA1       bit 7       Legend:       R = Readable bit     W = Writable bit     U = Unimplemented bit, read as '0'       -n = Value at POR     '1' = Bit is set     '0' = Bit is cleared     x = Bit is unknown       bit 15-13     DMABS<2:0>: DMA Buffer Size bits       111 = Reserved       110 = 32 buffers in RAM       101 = 24 buffers in RAM                                                                                                                                   | bit 8 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |

| bit 7  Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknow bit 15-13 DMABS<2:0>: DMA Buffer Size bits 111 = Reserved 110 = 32 buffers in RAM 101 = 24 buffers in RAM                                                                                                                                                                                                                                           | R/W-0 |

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-13       DMABS<2:0>: DMA Buffer Size bits         111 = Reserved       110 = 32 buffers in RAM         101 = 24 buffers in RAM                                                                                                                                                               | FSA0  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknow         bit 15-13       DMABS<2:0>: DMA Buffer Size bits       111 = Reserved         110 = 32 buffers in RAM       101 = 24 buffers in RAM                                                                                                                                                                                  | bit C |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknow         bit 15-13       DMABS<2:0>: DMA Buffer Size bits       111 = Reserved         110 = 32 buffers in RAM       101 = 24 buffers in RAM                                                                                                                                                                                  |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknow<br>bit 15-13 DMABS<2:0>: DMA Buffer Size bits<br>111 = Reserved<br>110 = 32 buffers in RAM<br>101 = 24 buffers in RAM                                                                                                                                                                                                                                                                                                                   |       |

| bit 15-13 DMABS<2:0>: DMA Buffer Size bits<br>111 = Reserved<br>110 = 32 buffers in RAM<br>101 = 24 buffers in RAM                                                                                                                                                                                                                                                                                                                                                                                                |       |

| 111 = Reserved<br>110 = 32 buffers in RAM<br>101 = 24 buffers in RAM                                                                                                                                                                                                                                                                                                                                                                                                                                              | wn    |

| 111 = Reserved<br>110 = 32 buffers in RAM<br>101 = 24 buffers in RAM                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |

| 111 = Reserved<br>110 = 32 buffers in RAM<br>101 = 24 buffers in RAM                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |

| 110 = 32 buffers in RAM<br>101 = 24 buffers in RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |

| 100 - 16 huffers in DAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

| 100 = 16 builds in RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       |

| 011 = 12 buffers in RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

| 010 = 8 buffers in RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       |

| 001 = 6 buffers in RAM<br>000 = 4 buffers in RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |

| bit 12-5 Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |

| bit 4-0 <b>FSA&lt;4:0&gt;:</b> FIFO Area Starts with Buffer bits                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |

| 11111 = Read Buffer RB31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |

| 11110 = Read Buffer RB30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |

| 00001 = TX/RX Buffer TRB1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |

| 00000 = TX/RX Buffer TRB0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |

### REGISTER 21-4: CxFCTRL: ECANx FIFO CONTROL REGISTER

| R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1  | R/W-1  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| FLTEN15 | FLTEN14 | FLTEN13 | FLTEN12 | FLTEN11 | FLTEN10 | FLTEN9 | FLTEN8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

|         |         |         |         |         |         |        |        |

| R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1  | R/W-1  |

| FLTEN7  | FLTEN6  | FLTEN5  | FLTEN4  | FLTEN3  | FLTEN2  | FLTEN1 | FLTEN0 |

| bit 7   |         |         |         |         |         |        | bit 0  |

|         |         |         |         |         |         |        |        |

| Legend: |         |         |         |         |         |        |        |

#### REGISTER 21-11: CxFEN1: ECANx ACCEPTANCE FILTER ENABLE REGISTER 1

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-0

FLTEN<15:0>: Enable Filter n to Accept Messages bits

1 = Enables Filter n

0 = Disables Filter n

REGISTER 21-12: CxBUFPNT1: ECANx FILTER 0-3 BUFFER POINTER REGISTER 1

| R/W-0         | R/W-0                                                 | R/W-0                                                                                                       | R/W-0                                          | R/W-0             | R/W-0                              | R/W-0           | R/W-0 |  |  |

|---------------|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|------------------------------------------------|-------------------|------------------------------------|-----------------|-------|--|--|

| F3BP<3:0>     |                                                       |                                                                                                             | F2BP<3:0>                                      |                   |                                    |                 |       |  |  |

| bit 15        |                                                       |                                                                                                             |                                                |                   |                                    |                 | bit 8 |  |  |

| R/W-0         | R/W-0                                                 | R/W-0                                                                                                       | R/W-0                                          | R/W-0             | R/W-0                              | R/W-0           | R/W-0 |  |  |

|               | F1BI                                                  | P<3:0>                                                                                                      | 3:0> F0BP<3:0>                                 |                   |                                    |                 |       |  |  |

| bit 7         |                                                       |                                                                                                             |                                                |                   |                                    |                 | bit ( |  |  |

| Legend:       |                                                       |                                                                                                             |                                                |                   |                                    |                 |       |  |  |

| R = Readable  | e bit                                                 | W = Writable                                                                                                | bit                                            | U = Unimplem      | U = Unimplemented bit, read as '0' |                 |       |  |  |

| -n = Value at | POR                                                   | '1' = Bit is set                                                                                            |                                                | '0' = Bit is clea | ared                               | x = Bit is unkr | nown  |  |  |

| bit 15-12     | 1111 = Filte<br>1110 = Filte<br>•<br>•<br>•<br>•<br>• | : RX Buffer Mas<br>er hits received in<br>er hits received in<br>er hits received in<br>er hits received in | n RX FIFO bu<br>n RX Buffer 1<br>n RX Buffer 1 | iffer             |                                    |                 |       |  |  |

| bit 11-8      | F2BP<3:0>                                             | : RX Buffer Mas                                                                                             | k for Filter 2 b                               | oits (same value  | s as bits<15:1                     | 2>)             |       |  |  |

| bit 7-4       | F1BP<3:0>                                             | : RX Buffer Mas                                                                                             | k for Filter 1 k                               | oits (same value  | s as bits<15:1                     | 2>)             |       |  |  |

|               |                                                       |                                                                                                             |                                                |                   |                                    |                 |       |  |  |

| oit 3-0 | Step<br>Command        | OPTION<3:0> | Option Description                                                                                             |

|---------|------------------------|-------------|----------------------------------------------------------------------------------------------------------------|

|         | PTGCTRL(1)             | 0000        | Reserved.                                                                                                      |

|         |                        | 0001        | Reserved.                                                                                                      |

|         |                        | 0010        | Disable Step Delay Timer (PTGSD).                                                                              |

|         |                        | 0011        | Reserved.                                                                                                      |

|         |                        | 0100        | Reserved.                                                                                                      |

|         |                        | 0101        | Reserved.                                                                                                      |

|         |                        | 0110        | Enable Step Delay Timer (PTGSD).                                                                               |

|         |                        | 0111        | Reserved.                                                                                                      |

|         |                        | 1000        | Start and wait for the PTG Timer0 to match the Timer0 Limit Register.                                          |

|         |                        | 1001        | Start and wait for the PTG Timer1 to match the Timer1 Limit Register.                                          |

|         |                        | 1010        | Reserved.                                                                                                      |

|         |                        | 1011        | Wait for the software trigger bit transition from low-to-high before continuing $(PTGSWT = 0 \text{ to } 1)$ . |

|         |                        | 1100        | Copy contents of the Counter 0 register to the AD1CHS0 register.                                               |

|         |                        | 1101        | Copy contents of the Counter 1 register to the AD1CHS0 register.                                               |

|         |                        | 1110        | Copy contents of the Literal 0 register to the AD1CHS0 register.                                               |

|         |                        | 1111        | Generate triggers indicated in the Broadcast Trigger Enable register (PTGBTE).                                 |

|         | PTGADD <sup>(1)</sup>  | 0000        | Add contents of the PTGADJ register to the Counter 0 Limit register (PTGC0LIM).                                |

|         |                        | 0001        | Add contents of the PTGADJ register to the Counter 1 Limit register (PTGC1LIM).                                |

|         |                        | 0010        | Add contents of the PTGADJ register to the Timer0 Limit register (PTGT0LIM).                                   |

|         |                        | 0011        | Add contents of the PTGADJ register to the Timer1 Limit register (PTGT1LIM).                                   |

|         |                        | 0100        | Add contents of the PTGADJ register to the Step Delay Limit register (PTGSDLIM)                                |

|         |                        | 0101        | Add contents of the PTGADJ register to the Literal 0 register (PTGL0).                                         |

|         |                        | 0110        | Reserved.                                                                                                      |

|         |                        | 0111        | Reserved.                                                                                                      |

|         | PTGCOPY <sup>(1)</sup> | 1000        | Copy contents of the PTGHOLD register to the Counter 0 Limit register (PTGC0LIM).                              |

|         |                        | 1001        | Copy contents of the PTGHOLD register to the Counter 1 Limit register (PTGC1LIM).                              |

|         |                        | 1010        | Copy contents of the PTGHOLD register to the Timer0 Limit register (PTGT0LIM).                                 |

|         |                        | 1011        | Copy contents of the PTGHOLD register to the Timer1 Limit register (PTGT1LIM).                                 |

|         |                        | 1100        | Copy contents of the PTGHOLD register to the Step Delay Limit register (PTGSDLIM).                             |

|         |                        | 1101        | Copy contents of the PTGHOLD register to the Literal 0 register (PTGL0).                                       |

|         |                        | 1110        | Reserved.                                                                                                      |

|         |                        | 1111        | Reserved.                                                                                                      |

#### TABLE 24-1: PTG STEP COMMAND FORMAT (CONTINUED)

Note 1: All reserved commands or options will execute but have no effect (i.e., execute as a NOP instruction).

2: Refer to Table 24-2 for the trigger output descriptions.

3: This feature is only available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| REGISTER      | 25-3: CM40                                                                                                                           | CON: COMPA                                                                               | RATOR 4 CO          | ONTROL RE        | GISTER           |                                          |                     |  |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|---------------------|------------------|------------------|------------------------------------------|---------------------|--|--|--|--|

| R/W-0         | R/W-0                                                                                                                                | R/W-0                                                                                    | U-0                 | U-0              | U-0              | R/W-0                                    | R/W-0               |  |  |  |  |

| CON           | COE                                                                                                                                  | CPOL                                                                                     | —                   | —                | —                | CEVT                                     | COUT                |  |  |  |  |

| bit 15        |                                                                                                                                      |                                                                                          |                     |                  |                  |                                          | bit 8               |  |  |  |  |

| R/W-0         | DAM 0                                                                                                                                | U-0                                                                                      | DAM 0               | U-0              | U-0              |                                          | R/W-0               |  |  |  |  |

|               | R/W-0                                                                                                                                | 0-0                                                                                      | R/W-0               | 0-0              | 0-0              | R/W-0                                    |                     |  |  |  |  |

| EVPOL1        | EVPOL0                                                                                                                               | —                                                                                        | CREF <sup>(1)</sup> | —                | —                | CCH1 <sup>(1)</sup>                      | CCH0 <sup>(1)</sup> |  |  |  |  |

| bit 7         |                                                                                                                                      |                                                                                          |                     |                  |                  |                                          | bit (               |  |  |  |  |

| Legend:       |                                                                                                                                      |                                                                                          |                     |                  |                  |                                          |                     |  |  |  |  |

| R = Readable  | e bit                                                                                                                                | W = Writable                                                                             | bit                 | U = Unimple      | mented bit, rea  | d as '0'                                 |                     |  |  |  |  |

| -n = Value at |                                                                                                                                      | '1' = Bit is se                                                                          |                     | '0' = Bit is cle |                  | x = Bit is unkn                          | iown                |  |  |  |  |

|               |                                                                                                                                      |                                                                                          |                     | 0 200000         |                  |                                          |                     |  |  |  |  |

| bit 15        | CON: Comp                                                                                                                            | arator Enable b                                                                          | oit                 |                  |                  |                                          |                     |  |  |  |  |

|               |                                                                                                                                      | ator is enabled                                                                          |                     |                  |                  |                                          |                     |  |  |  |  |

|               |                                                                                                                                      | ator is disabled                                                                         |                     |                  |                  |                                          |                     |  |  |  |  |

| bit 14        | COE: Comp                                                                                                                            | arator Output E                                                                          | nable bit           |                  |                  |                                          |                     |  |  |  |  |

|               |                                                                                                                                      | ator output is pr<br>ator output is in                                                   |                     | xOUT pin         |                  |                                          |                     |  |  |  |  |

| bit 13        | CPOL: Com                                                                                                                            | parator Output                                                                           | Polarity Select     | bit              |                  |                                          |                     |  |  |  |  |

|               | 1 = Compara                                                                                                                          | ator output is in                                                                        | verted              |                  |                  |                                          |                     |  |  |  |  |

|               | 0 = Compara                                                                                                                          | ator output is no                                                                        | ot inverted         |                  |                  |                                          |                     |  |  |  |  |

| bit 12-10     | Unimpleme                                                                                                                            | nted: Read as                                                                            | '0'                 |                  |                  |                                          |                     |  |  |  |  |

| bit 9         | CEVT: Comparator Event bit                                                                                                           |                                                                                          |                     |                  |                  |                                          |                     |  |  |  |  |

|               | interrup                                                                                                                             | ts until the bit is                                                                      | cleared             | POL<1:0> set     | tings occurred;  | disables future                          | triggers and        |  |  |  |  |

|               | •                                                                                                                                    | ator event did r                                                                         |                     |                  |                  |                                          |                     |  |  |  |  |

| bit 8         |                                                                                                                                      | COUT: Comparator Output bit                                                              |                     |                  |                  |                                          |                     |  |  |  |  |

|               |                                                                                                                                      | When CPOL = 0 (non-inverted polarity):<br>1 = VIN+ > VIN-                                |                     |                  |                  |                                          |                     |  |  |  |  |

|               |                                                                                                                                      | 1 = VIN + > VIN - 0 = VIN + < VIN - 0                                                    |                     |                  |                  |                                          |                     |  |  |  |  |

|               |                                                                                                                                      | When CPOL = 1 (inverted polarity):                                                       |                     |                  |                  |                                          |                     |  |  |  |  |