Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 256КВ (85.5К х 24)                                                              |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 16K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 9x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-VFTLA Exposed Pad                                                            |

| Supplier Device Package    | 44-VTLA (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep256mc204t-i-tl |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

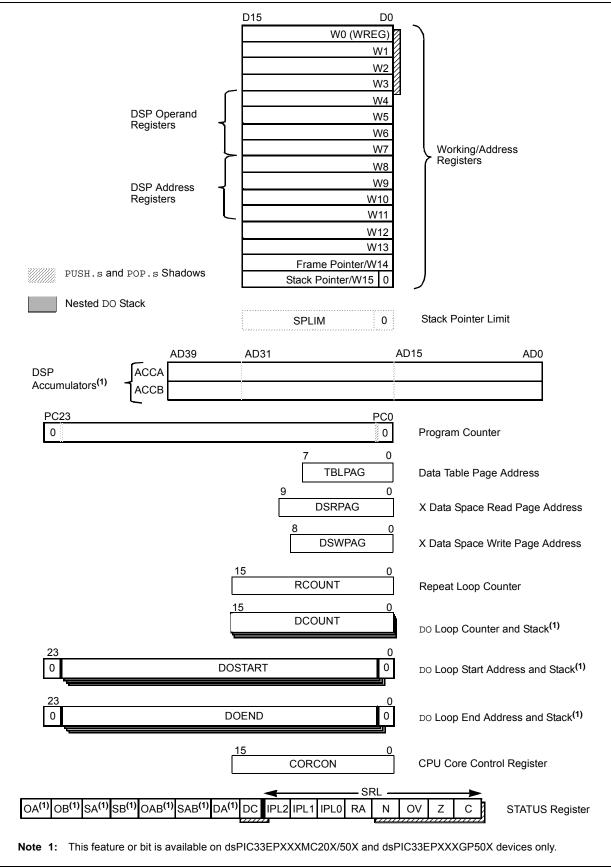

## FIGURE 4-10: DATA MEMORY MAP FOR dsPIC33EP256MC20X/50X AND dsPIC33EP256GP50X DEVICES

| TABLE 4 | 4-31: | PER | IPHERA | L PIN S | ELECT | INPUT F | REGISTI | ER MAP | FOR de | sPIC33E | EPXXXG | P50X D | EVICES | SONLY |  |

|---------|-------|-----|--------|---------|-------|---------|---------|--------|--------|---------|--------|--------|--------|-------|--|

|         |       |     |        |         |       |         |         |        |        |         |        |        |        |       |  |

| File<br>Name | Addr. | Bit 15 | Bit 14    | Bit 13    | Bit 12 | Bit 11     | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6      | Bit 5 | Bit 4 | Bit 3     | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|-----------|-----------|--------|------------|--------|-------|-------|-------|------------|-------|-------|-----------|-------|-------|-------|---------------|

| RPINR0       | 06A0  | —      |           |           |        | INT1R<6:0> |        |       |       | _     | _          | —     | —     | —         | —     | —     | _     | 0000          |

| RPINR1       | 06A2  |        | _         | _         | _      | _          | _      | _     | _     | _     | INT2R<6:0> |       |       |           |       |       | 0000  |               |

| RPINR3       | 06A6  |        | _         | _         | _      | _          | _      | _     | _     | _     |            |       | ٦     | [2CKR<6:0 | >     |       |       | 0000          |

| RPINR7       | 06AE  |        |           | IC2R<6:0> |        |            |        |       |       | _     | IC1R<6:0>  |       |       |           |       |       | 0000  |               |

| RPINR8       | 06B0  |        |           | IC4R<6:0> |        |            |        |       |       | _     | IC3R<6:0>  |       |       |           |       | 0000  |       |               |

| RPINR11      | 06B6  |        | _         | _         | _      | _          | _      | _     | _     | _     |            |       | (     | DCFAR<6:0 | >     |       |       | 0000          |

| RPINR18      | 06C4  |        | _         | _         | _      | _          | _      | _     | _     | _     |            |       | ι     | J1RXR<6:0 | >     |       |       | 0000          |

| RPINR19      | 06C6  |        | _         | _         | _      | _          | _      | _     | _     | _     |            |       | ι     | J2RXR<6:0 | >     |       |       | 0000          |

| RPINR22      | 06CC  |        |           |           | S      | CK2INR<6:0 | )>     |       |       | _     | SDI2R<6:0> |       |       |           |       |       | 0000  |               |

| RPINR23      | 06CE  | _      | SS2R<6:0> |           |        |            |        | 0000  |       |       |            |       |       |           |       |       |       |               |

| RPINR26      | 06D4  | —      | _         | _         | -      | _          | _      | —     |       | —     | C1RXR<6:0> |       |       | 0000      |       |       |       |               |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### **TABLE 4-32:** PERIPHERAL PIN SELECT INPUT REGISTER MAP FOR dsPIC33EPXXXMC50X DEVICES ONLY

| File Name | Addr. | Bit 15 | Bit 14       | Bit 13       | Bit 12 | Bit 11     | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6      | Bit 5 | Bit 4     | Bit 3      | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------|--------|--------------|--------------|--------|------------|--------|-------|-------|-------|------------|-------|-----------|------------|-------|-------|-------|---------------|

| RPINR0    | 06A0  | _      |              |              |        | INT1R<6:0> |        |       |       | —     | —          | —     | —         | —          | —     | —     | _     | 0000          |

| RPINR1    | 06A2  |        | _            | _            | _      | _          | _      | _     | _     | _     | INT2R<6:0> |       |           |            |       | 0000  |       |               |

| RPINR3    | 06A6  |        | _            | _            | _      | _          | _      | _     | _     | _     |            |       | -         | F2CKR<6:0  | >     |       |       | 0000          |

| RPINR7    | 06AE  |        | IC2R<6:0>    |              |        |            |        |       | _     |       |            |       | IC1R<6:0> |            |       |       | 0000  |               |

| RPINR8    | 06B0  |        |              | IC4R<6:0>    |        |            |        |       | _     |       |            |       | IC3R<6:0> |            |       |       | 0000  |               |

| RPINR11   | 06B6  |        | _            | _            | _      | _          | _      | _     | _     | _     |            |       | (         | DCFAR<6:0  | >     |       |       | 0000          |

| RPINR12   | 06B8  |        |              | FLT2R<6:0>   |        |            |        |       |       | _     | FLT1R<6:0> |       |           |            |       | 0000  |       |               |

| RPINR14   | 06BC  |        |              |              | (      | QEB1R<6:0  | >      |       |       | _     |            |       | (         | QEA1R<6:0  | >     |       |       | 0000          |

| RPINR15   | 06BE  |        |              |              | Н      | OME1R<6:0  | )>     |       |       | _     |            |       | I         | NDX1R<6:0  | >     |       |       | 0000          |

| RPINR18   | 06C4  |        | _            | _            | _      | _          | _      | _     | _     | _     |            |       | ι         | J1RXR<6:0  | >     |       |       | 0000          |

| RPINR19   | 06C6  |        | _            | _            | _      | _          | _      | _     | _     | _     |            |       | ι         | J2RXR<6:0  | >     |       |       | 0000          |

| RPINR22   | 06CC  | _      |              |              | S      | CK2INR<6:( | )>     |       |       | —     |            |       |           | SDI2R<6:0> | •     |       |       | 0000          |

| RPINR23   | 06CE  | _      | —            | —            |        | —          | —      |       | —     | —     |            |       |           | SS2R<6:0>  |       |       |       | 0000          |

| RPINR26   | 06D4  | _      | —            | —            |        | —          | —      |       | —     | —     |            |       | (         | C1RXR<6:0  | >     |       |       | 0000          |

| RPINR37   | 06EA  | _      | SYNCI1R<6:0> |              |        |            |        |       | —     | —     | —          | —     | —         |            |       |       | 0000  |               |

| RPINR38   | 06EC  | _      | DTCMP1R<6:0> |              |        |            |        |       | —     | —     | —          | —     | _         |            |       |       | 0000  |               |

| RPINR39   | 06EE  | _      |              | DTCMP3R<6:0> |        |            |        |       |       | _     |            |       | D         | CMP2R<6:   | 0>    |       |       | 0000          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

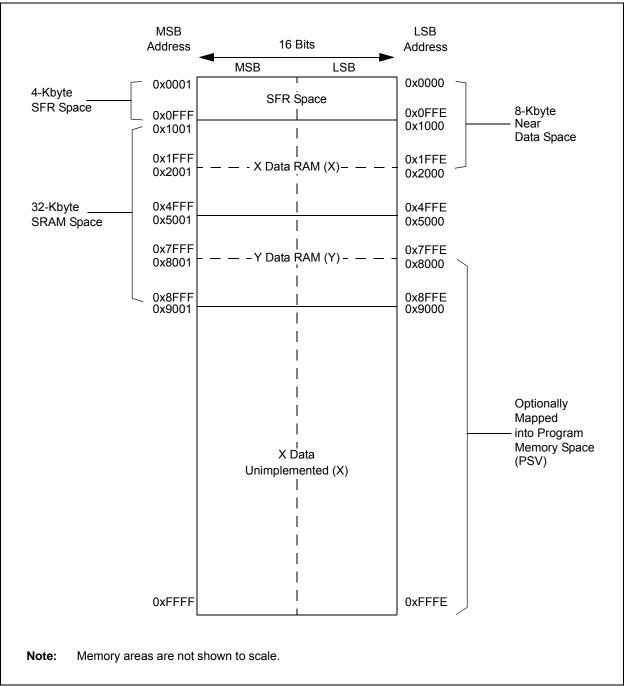

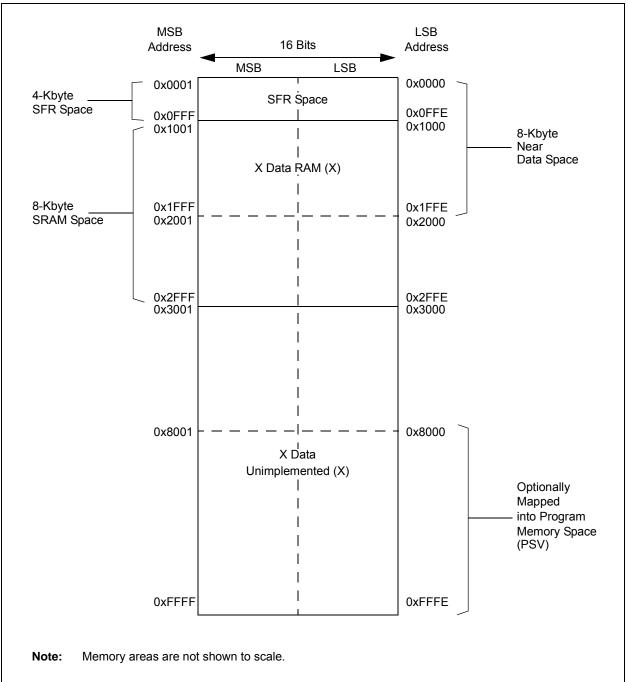

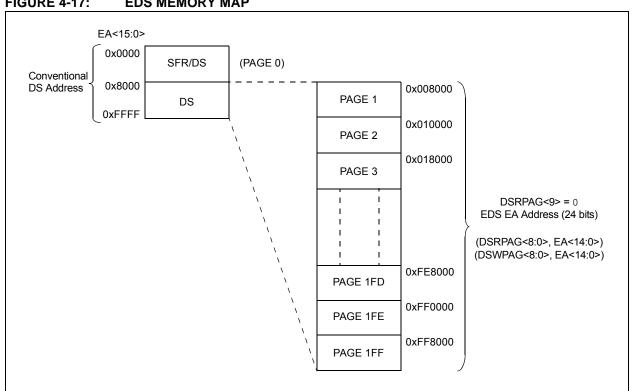

## 4.4.2 EXTENDED X DATA SPACE

The lower portion of the base address space range, between 0x0000 and 0x7FFF, is always accessible regardless of the contents of the Data Space Page registers. It is indirectly addressable through the register indirect instructions. It can be regarded as being located in the default EDS Page 0 (i.e., EDS address range of 0x000000 to 0x007FFF with the base address bit, EA<15> = 0, for this address range). However, Page 0 cannot be accessed through the upper 32 Kbytes, 0x8000 to 0xFFFF, of base Data Space, in combination with DSRPAG = 0x000 or DSWPAG = 0x000. Consequently, DSRPAG and DSWPAG are initialized to 0x001 at Reset.

- Note 1: DSxPAG should not be used to access Page 0. An EDS access with DSxPAG set to 0x000 will generate an address error trap.

- 2: Clearing the DSxPAG in software has no effect.

The remaining pages, including both EDS and PSV pages, are only accessible using the DSRPAG or DSWPAG registers in combination with the upper 32 Kbytes, 0x8000 to 0xFFFF, of the base address, where base address bit, EA<15> = 1.

For example, when DSRPAG = 0x001 or DSWPAG = 0x001, accesses to the upper 32 Kbytes, 0x8000 to 0xFFFF, of the Data Space will map to the EDS address range of 0x008000 to 0x00FFFF. When DSRPAG = 0x002 or DSWPAG = 0x002, accesses to the upper 32 Kbytes of the Data Space will map to the EDS address range of 0x010000 to 0x017FFF and so on, as shown in the EDS memory map in Figure 4-17.

For more information on the PSV page access using Data Space Page registers, refer to the "**Program Space Visibility from Data Space**" section in "**Program Memory**" (DS70613) of the "*dsPIC33/ PIC24 Family Reference Manual*".

## FIGURE 4-17: EDS MEMORY MAP

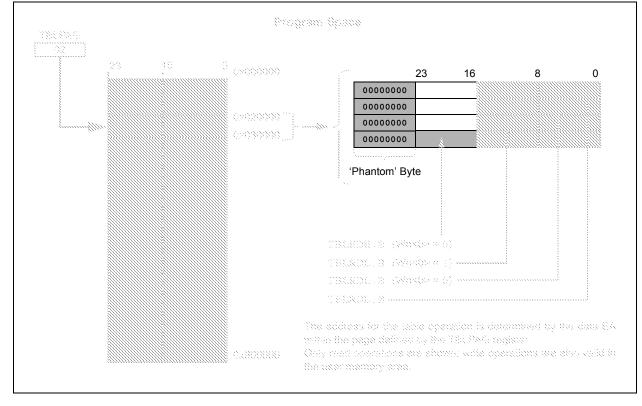

## 4.8.1 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the Program Space without going through Data Space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a Program Space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to Data Space addresses. Program memory can thus be regarded as two 16-bit-wide word address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space that contains the least significant data word. TBLRDH and TBLWTH access the space that contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from Program Space. Both function as either byte or word operations.

- TBLRDL (Table Read Low):

- In Word mode, this instruction maps the lower word of the Program Space location (P<15:0>) to a data address (D<15:0>)

- In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when Byte Select is '1'; the lower byte is selected when it is '0'.

- TBLRDH (Table Read High):

- In Word mode, this instruction maps the entire upper word of a program address (P<23:16>) to a data address. The 'phantom' byte (D<15:8>) is always '0'.

- In Byte mode, this instruction maps the upper or lower byte of the program word to D<7:0> of the data address in the TBLRDL instruction. The data is always '0' when the upper 'phantom' byte is selected (Byte Select = 1).

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a Program Space address. The details of their operation are explained in **Section 5.0 "Flash Program Memory"**.

For all table operations, the area of program memory space to be accessed is determined by the Table Page register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user application and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

## FIGURE 4-23: ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

## REGISTER 8-9: DSADRH: DMA MOST RECENT RAM HIGH ADDRESS REGISTER

| U-0            | U-0 | U-0             | U-0   | U-0          | U-0              | U-0    | U-0   |

|----------------|-----|-----------------|-------|--------------|------------------|--------|-------|

| —              | —   | —               | —     | —            | —                | -      | —     |

| bit 15         |     |                 |       |              |                  |        | bit 8 |

|                |     |                 |       |              |                  |        |       |

| R-0            | R-0 | R-0             | R-0   | R-0          | R-0              | R-0    | R-0   |

|                |     |                 | DSADR | <23:16>      |                  |        |       |

| bit 7          |     |                 |       |              |                  |        | bit 0 |

|                |     |                 |       |              |                  |        |       |

| Legend:        |     |                 |       |              |                  |        |       |

| R = Readable b | it  | W = Writable bi | t     | U = Unimpler | nented bit, read | as '0' |       |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |  |

|-------------------|------------------|------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |  |

### bit 15-8 Unimplemented: Read as '0'

bit 7-0 DSADR<23:16>: Most Recent DMA Address Accessed by DMA bits

#### REGISTER 8-10: DSADRL: DMA MOST RECENT RAM LOW ADDRESS REGISTER

| R-0              | R-0 | R-0              | R-0  | R-0                  | R-0         | R-0             | R-0   |

|------------------|-----|------------------|------|----------------------|-------------|-----------------|-------|

|                  |     |                  | DSAD | DR<15:8>             |             |                 |       |

| bit 15           |     |                  |      |                      |             |                 | bit 8 |

|                  |     |                  |      |                      |             |                 |       |

| R-0              | R-0 | R-0              | R-0  | R-0                  | R-0         | R-0             | R-0   |

|                  |     |                  | DSA  | DR<7:0>              |             |                 |       |

| bit 7            |     |                  |      |                      |             |                 | bit 0 |

|                  |     |                  |      |                      |             |                 |       |

| Legend:          |     |                  |      |                      |             |                 |       |

| R = Readable b   | it  | W = Writable bit |      | U = Unimplemen       | ted bit, re | ad as '0'       |       |

| -n = Value at PC | OR  | '1' = Bit is set |      | '0' = Bit is cleared | d           | x = Bit is unkn | own   |

bit 15-0 DSADR<15:0>: Most Recent DMA Address Accessed by DMA bits

| U-0          | U-0                         | U-0                                          | U-0            | U-0              | U-0              | U-0             | U-0   |

|--------------|-----------------------------|----------------------------------------------|----------------|------------------|------------------|-----------------|-------|

| -            | —                           | —                                            | —              | —                | —                | —               | —     |

| bit 15       |                             |                                              |                |                  |                  |                 | bit 8 |

| U-0          | U-0                         | U-0                                          | U-0            | R-1              | R-1              | R-1             | R-1   |

| _            | _                           | _                                            | _              |                  | LSTC             | H<3:0>          |       |

| bit 7        |                             |                                              |                |                  |                  |                 | bit 0 |

| Legend:      |                             |                                              |                |                  |                  |                 |       |

| R = Readat   | ole bit                     | W = Writable                                 | bit            | U = Unimpler     | mented bit, read | 1 as '0'        |       |

| -n = Value a | at POR                      | '1' = Bit is set                             |                | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

|              |                             |                                              |                |                  |                  |                 |       |

| bit 15-4     | Unimplemen                  | ted: Read as '                               | 0'             |                  |                  |                 |       |

| bit 3-0      | LSTCH<3:0>                  | : Last DMAC C                                | hannel Active  | e Status bits    |                  |                 |       |

|              | 1111 = No DI<br>1110 = Rese | MA transfer has<br>rved                      | s occurred sir | nce system Res   | set              |                 |       |

|              | •                           |                                              |                |                  |                  |                 |       |

|              | •                           |                                              |                |                  |                  |                 |       |

|              | •                           |                                              |                |                  |                  |                 |       |

|              |                             | rved<br>data transfer wa<br>data transfer wa |                |                  |                  |                 |       |

|              |                             | data transfer wa                             |                |                  |                  |                 |       |

## REGISTER 8-13: DMALCA: DMA LAST CHANNEL ACTIVE STATUS REGISTER

0000 = Last data transfer was handled by Channel 0 0000 = Last data transfer was handled by Channel 0

## 10.3 Doze Mode

The preferred strategies for reducing power consumption are changing clock speed and invoking one of the powersaving modes. In some circumstances, this cannot be practical. For example, it may be necessary for an application to maintain uninterrupted synchronous communication, even while it is doing nothing else. Reducing system clock speed can introduce communication errors, while using a power-saving mode can stop communications completely.

Doze mode is a simple and effective alternative method to reduce power consumption while the device is still executing code. In this mode, the system clock continues to operate from the same source and at the same speed. Peripheral modules continue to be clocked at the same speed, while the CPU clock speed is reduced. Synchronization between the two clock domains is maintained, allowing the peripherals to access the SFRs while the CPU executes code at a slower rate.

Doze mode is enabled by setting the DOZEN bit (CLKDIV<11>). The ratio between peripheral and core clock speed is determined by the DOZE<2:0> bits (CLKDIV<14:12>). There are eight possible configurations, from 1:1 to 1:128, with 1:1 being the default setting.

Programs can use Doze mode to selectively reduce power consumption in event-driven applications. This allows clock-sensitive functions, such as synchronous communications, to continue without interruption while the CPU Idles, waiting for something to invoke an interrupt routine. An automatic return to full-speed CPU operation on interrupts can be enabled by setting the ROI bit (CLKDIV<15>). By default, interrupt events have no effect on Doze mode operation.

For example, suppose the device is operating at 20 MIPS and the ECAN<sup>™</sup> module has been configured for 500 kbps, based on this device operating speed. If the device is placed in Doze mode with a clock frequency ratio of 1:4, the ECAN module continues to communicate at the required bit rate of 500 kbps, but the CPU now starts executing instructions at a frequency of 5 MIPS.

## 10.4 Peripheral Module Disable

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled using the appropriate PMD control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers do not have effect and read values are invalid.

A peripheral module is enabled only if both the associated bit in the PMD register is cleared and the peripheral is supported by the specific dsPIC<sup>®</sup> DSC variant. If the peripheral is present in the device, it is enabled in the PMD register by default.

| Note: | If a PMD bit is set, the corresponding        |

|-------|-----------------------------------------------|

|       | module is disabled after a delay of one       |

|       | instruction cycle. Similarly, if a PMD bit is |

|       | cleared, the corresponding module is          |

|       | enabled after a delay of one instruction      |

|       | cycle (assuming the module control regis-     |

|       | ters are already configured to enable         |

|       | module operation).                            |

## 10.5 Power-Saving Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

## 10.5.1 KEY RESOURCES

- "Watchdog Timer and Power-Saving Modes" (DS70615) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

## REGISTER 11-17: RPINR39: PERIPHERAL PIN SELECT INPUT REGISTER 39 (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

| U-0               | R/W-0            | R/W-0                                                    | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|-------------------|------------------|----------------------------------------------------------|-------|-------------------|-----------------|-----------------|-------|

|                   |                  |                                                          |       | DTCMP3R<6:0       | )>              |                 |       |

| bit 15            |                  |                                                          |       |                   |                 |                 | bit 8 |

| U-0               | R/W-0            | R/W-0                                                    | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

| 0-0               | R/W-0            | R/W-0                                                    | -     | DTCMP2R<6:0       |                 | R/W-0           | R/W-U |

| bit 7             |                  |                                                          |       |                   | 17              |                 | bit 0 |

| bit i             |                  |                                                          |       |                   |                 |                 | bit 0 |

| Legend:           |                  |                                                          |       |                   |                 |                 |       |

| R = Readab        | ole bit          | W = Writable                                             | bit   | U = Unimplem      | nented bit, rea | ad as '0'       |       |

| -n = Value at POR |                  | '1' = Bit is set                                         |       | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

|                   |                  |                                                          |       |                   |                 |                 |       |

|                   |                  | nput tied to CMI                                         |       |                   |                 |                 |       |

| bit 7             | 1 = 0000000 = Ir | nput tied to CMI<br>nput tied to Vss<br>nted: Read as '( |       |                   |                 |                 |       |

| REGISTE       | R 16-7: PWMC                            | CONX: PWMX (                                                                        | CONTROL R      | EGISTER          |                      |                      |                     |  |  |  |  |  |

|---------------|-----------------------------------------|-------------------------------------------------------------------------------------|----------------|------------------|----------------------|----------------------|---------------------|--|--|--|--|--|

| HS/HC-        | 0 HS/HC-0                               | HS/HC-0                                                                             | R/W-0          | R/W-0            | R/W-0                | R/W-0                | R/W-0               |  |  |  |  |  |

| FLTSTAT       | -(1) CLSTAT <sup>(1)</sup>              | TRGSTAT                                                                             | FLTIEN         | CLIEN            | TRGIEN               | ITB <sup>(2)</sup>   | MDCS <sup>(2)</sup> |  |  |  |  |  |

| bit 15        | ·                                       | •                                                                                   |                | ÷                |                      |                      | bit                 |  |  |  |  |  |

| R/W-0         | R/W-0                                   | R/W-0                                                                               | U-0            | R/W-0            | R/W-0                | R/W-0                | R/W-0               |  |  |  |  |  |

| DTC1          |                                         | DTCP <sup>(3)</sup>                                                                 | 0-0            | MTBS             | CAM <sup>(2,4)</sup> | XPRES <sup>(5)</sup> | IUE <sup>(2)</sup>  |  |  |  |  |  |

| bit 7         | DICO                                    | DICE                                                                                | _              | INT DO           | CAIM                 | AFRES'               | bit                 |  |  |  |  |  |

|               |                                         |                                                                                     |                |                  |                      |                      | <u> </u>            |  |  |  |  |  |

| Legend:       |                                         | HC = Hardware                                                                       | Clearable bit  | HS = Hardwa      | are Settable bit     |                      |                     |  |  |  |  |  |

| R = Reada     | able bit                                | W = Writable bi                                                                     | t              | U = Unimple      | mented bit, rea      | ıd as '0'            |                     |  |  |  |  |  |

| -n = Value    | at POR                                  | '1' = Bit is set                                                                    |                | '0' = Bit is cle | eared                | x = Bit is unk       | nown                |  |  |  |  |  |

| bit 15        | ELTSTAT: ES                             | ult Interrupt Statu                                                                 | is hit(1)      |                  |                      |                      |                     |  |  |  |  |  |

| DIL 15        |                                         | rrupt is pending                                                                    |                |                  |                      |                      |                     |  |  |  |  |  |

|               |                                         | interrupt is pendi                                                                  | ng             |                  |                      |                      |                     |  |  |  |  |  |

|               |                                         | ared by setting F                                                                   |                |                  |                      |                      |                     |  |  |  |  |  |

| bit 14        |                                         | rent-Limit Interru                                                                  | •              |                  |                      |                      |                     |  |  |  |  |  |

|               |                                         | 1 = Current-limit interrupt is pending<br>0 = No current-limit interrupt is pending |                |                  |                      |                      |                     |  |  |  |  |  |

|               |                                         | ared by setting C                                                                   |                |                  |                      |                      |                     |  |  |  |  |  |

| bit 13        |                                         | igger Interrupt S                                                                   |                |                  |                      |                      |                     |  |  |  |  |  |

|               |                                         | 1 = Trigger interrupt is pending                                                    |                |                  |                      |                      |                     |  |  |  |  |  |

|               |                                         | 0 = No trigger interrupt is pending<br>This bit is cleared by setting TRGIEN = 0.   |                |                  |                      |                      |                     |  |  |  |  |  |

|               |                                         |                                                                                     |                |                  |                      |                      |                     |  |  |  |  |  |

| bit 12        |                                         | t Interrupt Enable                                                                  | e bit          |                  |                      |                      |                     |  |  |  |  |  |

|               |                                         | rrupt is enabled rrupt is disabled                                                  | and the FLTS   | TAT bit is clear | ed                   |                      |                     |  |  |  |  |  |

| bit 11        |                                         | ent-Limit Interrup                                                                  |                |                  | cu .                 |                      |                     |  |  |  |  |  |

|               |                                         | mit interrupt is er                                                                 |                |                  |                      |                      |                     |  |  |  |  |  |

|               |                                         | mit interrupt is di                                                                 |                | e CLSTAT bit is  | s cleared            |                      |                     |  |  |  |  |  |

| bit 10        | TRGIEN: Trig                            | ger Interrupt En                                                                    | able bit       |                  |                      |                      |                     |  |  |  |  |  |

|               |                                         | event generates                                                                     |                |                  | T hit is cleared     |                      |                     |  |  |  |  |  |

| bit 9         |                                         | vent interrupts ar<br>dent Time Base I                                              |                |                  | i bit is cleared     |                      |                     |  |  |  |  |  |

| DIL 9         |                                         | register provides                                                                   |                | riad for this PM | VM generator         |                      |                     |  |  |  |  |  |

|               |                                         | egister provides f                                                                  | •              |                  | •                    |                      |                     |  |  |  |  |  |

| bit 8         |                                         | er Duty Cycle Re                                                                    |                |                  |                      |                      |                     |  |  |  |  |  |

|               |                                         | ister provides du<br>jister provides du                                             |                |                  |                      | r                    |                     |  |  |  |  |  |

| Note 1:       | Software must clea                      |                                                                                     |                |                  | -                    |                      | t controller        |  |  |  |  |  |

| Note 1.<br>2: | These bits should                       | -                                                                                   |                | -                | -                    | the interrup         |                     |  |  |  |  |  |

| 3:            | DTC<1:0> = 11 fo                        | -                                                                                   |                | -                | -                    |                      |                     |  |  |  |  |  |

| 4:            | The Independent T<br>CAM bit is ignored | Time Base (ITB =                                                                    |                | •                |                      | igned mode. If       | TTB = 0, the        |  |  |  |  |  |

| 5:            | To operate in Exter                     |                                                                                     | t mode, the IT | B bit must be '  | 1' and the CLM       | 10D bit in the I     | FCLCONx             |  |  |  |  |  |

## REGISTER 16-7: PWMCONx: PWMx CONTROL REGISTER

5: To operate in External Period Reset mode, the ITB bit must be '1' and the CLMOD bit in the FCLCONx register must be '0'.

## 19.1 I<sup>2</sup>C Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this UDL increases |

|-------|---------------------------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                                               |

|       | http://www.microchip.com/wwwproducts/                                                                   |

|       | Devices.aspx?dDocName=en555464                                                                          |

## 19.1.1 KEY RESOURCES

- "Inter-Integrated Circuit (I<sup>2</sup>C)" (DS70330) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

## REGISTER 23-1: AD1CON1: ADC1 CONTROL REGISTER 1 (CONTINUED)

| bit 7-5 | SSRC<2:0>: Sample Trigger Source Select bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | If SSRCG = 1:<br>111 = Reserved<br>110 = PTGO15 primary trigger compare ends sampling and starts conversion <sup>(1)</sup><br>101 = PTGO14 primary trigger compare ends sampling and starts conversion <sup>(1)</sup><br>100 = PTGO13 primary trigger compare ends sampling and starts conversion <sup>(1)</sup><br>011 = PTGO12 primary trigger compare ends sampling and starts conversion <sup>(1)</sup><br>010 = PWM Generator 3 primary trigger compare ends sampling and starts conversion <sup>(2)</sup><br>001 = PWM Generator 2 primary trigger compare ends sampling and starts conversion <sup>(2)</sup><br>000 = PWM Generator 1 primary trigger compare ends sampling and starts conversion <sup>(2)</sup> |

|         | If SSRCG = 0:<br>111 = Internal counter ends sampling and starts conversion (auto-convert)<br>110 = CTMU ends sampling and starts conversion<br>101 = Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         | <ul> <li>101 - Reserved</li> <li>100 = Timer5 compare ends sampling and starts conversion</li> <li>011 = PWM primary Special Event Trigger ends sampling and starts conversion</li> <li>010 = Timer3 compare ends sampling and starts conversion</li> <li>001 = Active transition on the INT0 pin ends sampling and starts conversion</li> <li>000 = Clearing the Sample bit (SAMP) ends sampling and starts conversion (Manual mode)</li> </ul>                                                                                                                                                                                                                                                                        |

| bit 4   | SSRCG: Sample Trigger Source Group bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|         | See SSRC<2:0> for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| bit 3   | <ul> <li>SIMSAM: Simultaneous Sample Select bit (only applicable when CHPS&lt;1:0&gt; = 01 or 1x)</li> <li><u>In 12-bit mode (AD21B = 1), SIMSAM is Unimplemented and is Read as '0':</u></li> <li>1 = Samples CH0, CH1, CH2, CH3 simultaneously (when CHPS&lt;1:0&gt; = 1x); or samples CH0 and CH1 simultaneously (when CHPS&lt;1:0&gt; = 01)</li> <li>0 = Samples multiple channels individually in sequence</li> </ul>                                                                                                                                                                                                                                                                                              |

| bit 2   | ASAM: ADC1 Sample Auto-Start bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|         | <ul> <li>1 = Sampling begins immediately after the last conversion; SAMP bit is auto-set</li> <li>0 = Sampling begins when the SAMP bit is set</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| bit 1   | SAMP: ADC1 Sample Enable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|         | <ul> <li>1 = ADC Sample-and-Hold amplifiers are sampling</li> <li>0 = ADC Sample-and-Hold amplifiers are holding</li> <li>If ASAM = 0, software can write '1' to begin sampling. Automatically set by hardware if ASAM = 1. If SSRC&lt;2:0&gt; = 000, software can write '0' to end sampling and start conversion. If SSRC&lt;2:0&gt; ≠ 000, automatically cleared by hardware to end sampling and start conversion.</li> </ul>                                                                                                                                                                                                                                                                                         |

| bit 0   | DONE: ADC1 Conversion Status bit <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|         | <ul> <li>1 = ADC conversion cycle has completed</li> <li>0 = ADC conversion has not started or is in progress</li> <li>Automatically set by hardware when the ADC conversion is complete. Software can write '0' to clear the DONE status bit (software is not allowed to write '1'). Clearing this bit does NOT affect any operation in progress. Automatically cleared by hardware at the start of a new conversion.</li> </ul>                                                                                                                                                                                                                                                                                       |

| Note 1: | See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for information on this selection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

- 2: This setting is available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

- **3:** Do not clear the DONE bit in software if Auto-Sample is enabled (ASAM = 1).

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

## REGISTER 23-5: AD1CHS123: ADC1 INPUT CHANNEL 1, 2, 3 SELECT REGISTER

| 11.0   | 11.0 | 11.0 | 11.0 | 11.0 |          |          |         |

|--------|------|------|------|------|----------|----------|---------|

| U-0    | U-0  | U-0  | U-0  | U-0  | R/W-0    | R/W-0    | R/W-0   |

| —      | _    |      |      |      | CH123NB1 | CH123NB0 | CH123SB |

| bit 15 |      |      |      |      |          |          | bit 8   |

|        |      |      |      |      |          |          |         |

| U-0    | U-0  | U-0  | U-0  | U-0  | R/W-0    | R/W-0    | R/W-0   |

| 0-0   | 0-0 | 0-0 | 0-0 | U-0 | R/W-0    | R/W-0    | R/W-0   |

|-------|-----|-----|-----|-----|----------|----------|---------|

| —     | —   | —   | _   |     | CH123NA1 | CH123NA0 | CH123SA |

| bit 7 |     |     |     |     |          |          | bit 0   |

## Legend:

| Legenu.           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-11 Unimplemented: Read as '0'

bit 10-9

CH123NB<1:0>: Channel 1, 2, 3 Negative Input Select for Sample MUXB bits

In 12-bit mode (AD21B = 1), CH123NB is Unimplemented and is Read as '0':

| Value           | ADC Channel |       |       |  |  |  |

|-----------------|-------------|-------|-------|--|--|--|

| value           | CH1         | CH2   | CH3   |  |  |  |

| 11              | AN9         | AN10  | AN11  |  |  |  |

| 10 <b>(1,2)</b> | OA3/AN6     | AN7   | AN8   |  |  |  |

| 0x              | Vrefl       | Vrefl | VREFL |  |  |  |

bit 8 **CH123SB:** Channel 1, 2, 3 Positive Input Select for Sample MUXB bit In 12-bit mode (AD21B = 1), CH123SB is Unimplemented and is Read as '0':

| Value          | ADC Channel |         |         |  |  |  |

|----------------|-------------|---------|---------|--|--|--|

| value          | CH1         | CH2     | CH3     |  |  |  |

| 1 <b>(2)</b>   | OA1/AN3     | OA2/AN0 | OA3/AN6 |  |  |  |

| 0 <b>(1,2)</b> | OA2/AN0     | AN1     | AN2     |  |  |  |

bit 7-3 Unimplemented: Read as '0'

bit 2-1 **CH123NA<1:0>:** Channel 1, 2, 3 Negative Input Select for Sample MUXA bits In 12-bit mode (AD21B = 1), CH123NA is Unimplemented and is Read as '<u>0</u>':

| Value           | ADC Channel |       |       |  |  |  |

|-----------------|-------------|-------|-------|--|--|--|

|                 | CH1         | CH2   | CH3   |  |  |  |

| 11              | AN9         | AN10  | AN11  |  |  |  |

| 10 <b>(1,2)</b> | OA3/AN6     | AN7   | AN8   |  |  |  |

| 0x              | VREFL       | VREFL | Vrefl |  |  |  |

- **Note 1:** AN0 through AN7 are repurposed when comparator and op amp functionality is enabled. See Figure 23-1 to determine how enabling a particular op amp or comparator affects selection choices for Channels 1, 2 and 3.

- 2: The OAx input is used if the corresponding op amp is selected (OPMODE (CMxCON<10>) = 1); otherwise, the ANx input is used.

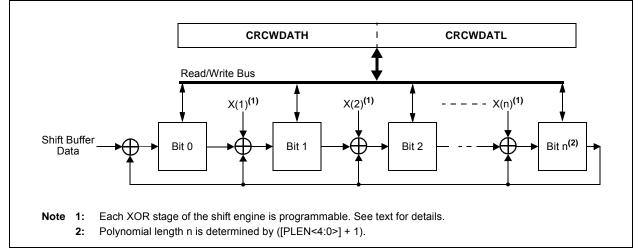

## 26.1 Overview

The CRC module can be programmed for CRC polynomials of up to the 32nd order, using up to 32 bits. Polynomial length, which reflects the highest exponent in the equation, is selected by the PLEN<4:0> bits (CRCCON2<4:0>).

The CRCXORL and CRCXORH registers control which exponent terms are included in the equation. Setting a particular bit includes that exponent term in the equation; functionally, this includes an XOR operation on the corresponding bit in the CRC engine. Clearing the bit disables the XOR.

For example, consider two CRC polynomials, one a 16-bit equation and the other a 32-bit equation:

$$\begin{array}{c} x16+x12+x5+1\\ \text{and}\\ x32+x26+x23+x22+x16+x12+x11+x10+x8+x7\\ +x5+x4+x2+x+1 \end{array}$$

To program these polynomials into the CRC generator, set the register bits as shown in Table 26-1.

Note that the appropriate positions are set to '1' to indicate that they are used in the equation (for example, X26 and X23). The 0 bit required by the equation is always XORed; thus, X0 is a don't care. For a polynomial of length N, it is assumed that the *N*th bit will always be used, regardless of the bit setting. Therefore, for a polynomial length of 32, there is no 32nd bit in the CRCxOR register.

## TABLE 26-1:CRC SETUP EXAMPLES FOR16 AND 32-BIT POLYNOMIAL

| CRC Control | Bit Values             |                        |  |  |  |

|-------------|------------------------|------------------------|--|--|--|

| Bits        | 16-bit<br>Polynomial   | 32-bit<br>Polynomial   |  |  |  |

| PLEN<4:0>   | 01111                  | 11111                  |  |  |  |

| X<31:16>    | 0000 0000<br>0000 000x | 0000 0100<br>1100 0001 |  |  |  |

| X<15:0>     | 0001 0000<br>0010 000x | 0001 1101<br>1011 011x |  |  |  |

## 26.2 Programmable CRC Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

## 26.2.1 KEY RESOURCES

- "Programmable Cyclic Redundancy Check (CRC)" (DS70346) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

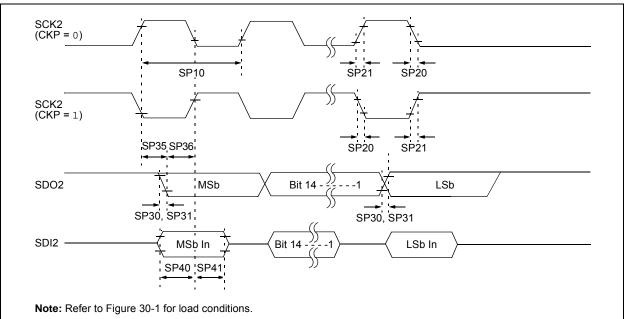

## FIGURE 30-17: SPI2 MASTER MODE (FULL-DUPLEX, CKE = 0, CKP = x, SMP = 1) TIMING CHARACTERISTICS

## TABLE 30-36:SPI2 MASTER MODE (FULL-DUPLEX, CKE = 0, CKP = x, SMP = 1)TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                               | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                     |      |       |                             |

|--------------------|-----------------------|-----------------------------------------------|-------------------------------------------------------|---------------------|------|-------|-----------------------------|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>                 | Min.                                                  | Typ. <sup>(2)</sup> | Max. | Units | Conditions                  |

| SP10               | FscP                  | Maximum SCK2 Frequency                        |                                                       | —                   | 9    | MHz   | -40°C to +125°C<br>(Note 3) |

| SP20               | TscF                  | SCK2 Output Fall Time                         | _                                                     | —                   | _    | ns    | See Parameter DO32 (Note 4) |

| SP21               | TscR                  | SCK2 Output Rise Time                         | _                                                     | —                   | _    | ns    | See Parameter DO31 (Note 4) |

| SP30               | TdoF                  | SDO2 Data Output Fall Time                    | _                                                     | —                   | _    | ns    | See Parameter DO32 (Note 4) |

| SP31               | TdoR                  | SDO2 Data Output Rise Time                    | _                                                     | —                   | _    | ns    | See Parameter DO31 (Note 4) |

| SP35               | TscH2doV,<br>TscL2doV | SDO2 Data Output Valid after<br>SCK2 Edge     | _                                                     | 6                   | 20   | ns    |                             |

| SP36               | TdoV2scH,<br>TdoV2scL | SDO2 Data Output Setup to<br>First SCK2 Edge  | 30                                                    | —                   | _    | ns    |                             |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDI2 Data<br>Input to SCK2 Edge | 30                                                    | —                   | _    | ns    |                             |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDI2 Data Input to SCK2 Edge     | 30                                                    | —                   |      | ns    |                             |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The minimum clock period for SCK2 is 111 ns. The clock generated in Master mode must not violate this specification.

- 4: Assumes 50 pF load on all SPI2 pins.

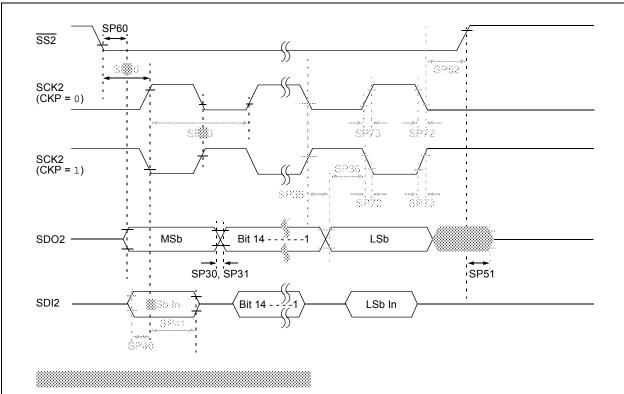

## FIGURE 30-18: SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0) TIMING CHARACTERISTICS

## TABLE 30-48:SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0)TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                              | Standard Op<br>(unless othe<br>Operating te | erwise st           | <b>ated)</b><br>e -40° | C ≤ TA ≤ | <b>V to 3.6V</b><br>+85°C for Industrial<br>+125°C for Extended |

|--------------------|-----------------------|----------------------------------------------|---------------------------------------------|---------------------|------------------------|----------|-----------------------------------------------------------------|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>                | Min.                                        | Typ. <sup>(2)</sup> | Max.                   | Units    | Conditions                                                      |

| SP70               | FscP                  | Maximum SCK1 Input Frequency                 | —                                           |                     | 11                     | MHz      | (Note 3)                                                        |

| SP72               | TscF                  | SCK1 Input Fall Time                         | —                                           | —                   | _                      | ns       | See Parameter DO32 (Note 4)                                     |

| SP73               | TscR                  | SCK1 Input Rise Time                         | —                                           | —                   | _                      | ns       | See Parameter DO31 (Note 4)                                     |

| SP30               | TdoF                  | SDO1 Data Output Fall Time                   | _                                           | —                   | _                      | ns       | See Parameter DO32 (Note 4)                                     |

| SP31               | TdoR                  | SDO1 Data Output Rise Time                   | —                                           | —                   | _                      | ns       | See Parameter DO31 (Note 4)                                     |

| SP35               | TscH2doV,<br>TscL2doV | SDO1 Data Output Valid after<br>SCK1 Edge    | —                                           | 6                   | 20                     | ns       |                                                                 |

| SP36               | TdoV2scH,<br>TdoV2scL | SDO1 Data Output Setup to<br>First SCK1 Edge | 30                                          | —                   | _                      | ns       |                                                                 |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDI1 Data Input to SCK1 Edge   | 30                                          | —                   | _                      | ns       |                                                                 |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDI1 Data Input to SCK1 Edge    | 30                                          | —                   | _                      | ns       |                                                                 |

| SP50               | TssL2scH,<br>TssL2scL | SS1 ↓ to SCK1 ↑ or SCK1 ↓<br>Input           | 120                                         | —                   | _                      | ns       |                                                                 |

| SP51               | TssH2doZ              | SS1 ↑ to SDO1 Output<br>High-Impedance       | 10                                          | —                   | 50                     | ns       | (Note 4)                                                        |

| SP52               | TscH2ssH,<br>TscL2ssH | SS1                                          | 1.5 TCY + 40                                | —                   |                        | ns       | (Note 4)                                                        |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCK1 is 91 ns. Therefore, the SCK1 clock generated by the master must not violate this specification.

4: Assumes 50 pF load on all SPI1 pins.

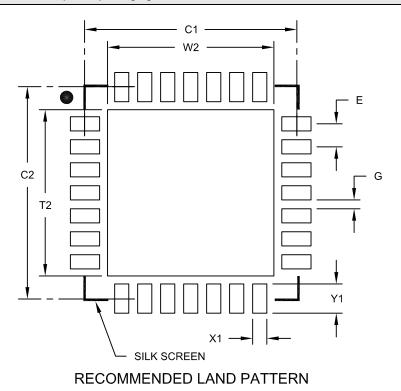

# 28-Lead Plastic Quad Flat, No Lead Package (MM) – 6x6x0.9 mm Body [QFN-S] with 0.40 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            |        | MILLIM | ETERS    |      |

|----------------------------|--------|--------|----------|------|

| Dimensior                  | Limits | MIN    | NOM      | MAX  |

| Contact Pitch              | E      |        | 0.65 BSC |      |

| Optional Center Pad Width  | W2     |        |          | 4.70 |

| Optional Center Pad Length | T2     |        |          | 4.70 |

| Contact Pad Spacing        | C1     |        | 6.00     |      |

| Contact Pad Spacing        | C2     |        | 6.00     |      |

| Contact Pad Width (X28)    | X1     |        |          | 0.40 |

| Contact Pad Length (X28)   | Y1     |        |          | 0.85 |

| Distance Between Pads      | G      | 0.25   |          |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2124A

| DMAxSTAH (DMA Channel x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Start Address A, High)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 144                                                                                                                                                                                                            |

| DMAxSTAL (DMA Channel x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                |

| Start Address A, Low)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 144                                                                                                                                                                                                            |

| DMAxSTBH (DMA Channel x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                |

| Start Address B, High)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 145                                                                                                                                                                                                            |

| DMAxSTBL (DMA Channel x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                |