Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Detuns                     |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 60 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                  |

| Number of I/O              | 53                                                                             |

| Program Memory Size        | 256KB (85.5K x 24)                                                             |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | ·                                                                              |

| RAM Size                   | 16K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-VFQFN Exposed Pad                                                           |

| Supplier Device Package    | 64-QFN (9x9)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep256mc206-e-mr |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

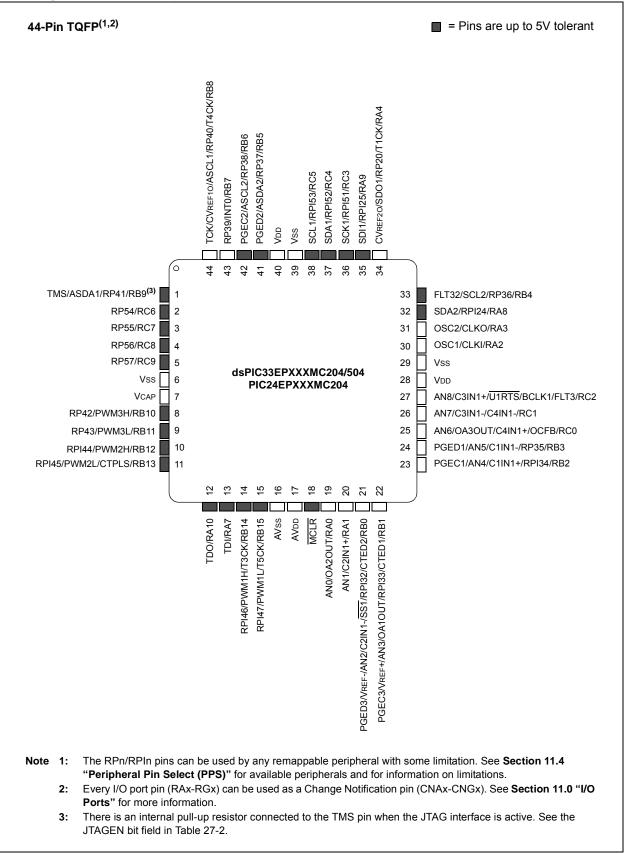

## Pin Diagrams (Continued)

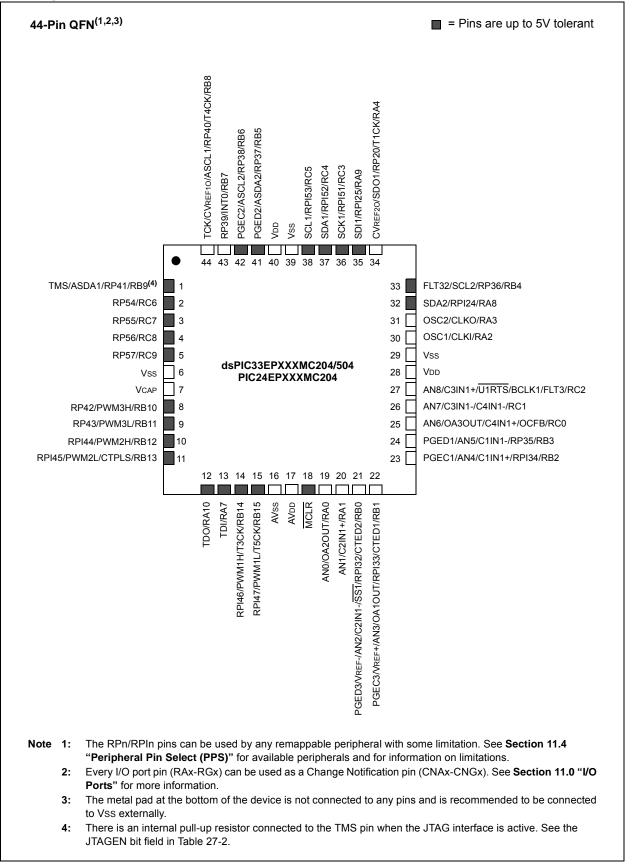

## Pin Diagrams (Continued)

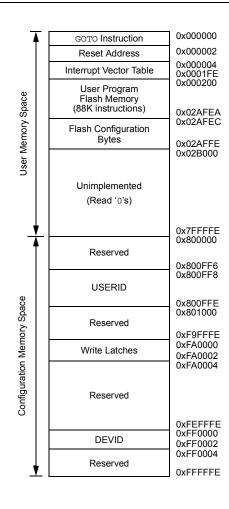

#### FIGURE 4-4: PROGRAM MEMORY MAP FOR dsPIC33EP256GP50X, dsPIC33EP256MC20X/50X AND PIC24EP256GP/MC20X DEVICES

Note: Memory areas are not shown to scale.

# TABLE 4-4: INTERRUPT CONTROLLER REGISTER MAP FOR PIC24EPXXXMC20X DEVICES ONLY (CONTINUED)

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8 | Bit 7 | Bit 6   | Bit 5       | Bit 4   | Bit 3   | Bit 2  | Bit 1       | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|------------|--------|--------|--------|------------|-------|-------|---------|-------------|---------|---------|--------|-------------|--------|---------------|

| IPC35        | 0886  | _      |        | JTAGIP<2:0 | >      | _      |        | ICDIP<2:0  | >     |       | —       | _           | _       | —       | _      | —           |        | 4400          |

| IPC36        | 0888  | _      | F      | PTG0IP<2:0 | >      | _      | PT     | GWDTIP<    | 2:0>  |       | PT      | GSTEPIP<2   | :0>     | —       | —      | —           | -      | 4440          |

| IPC37        | 088A  | _      | —      | —          | _      | _      | F      | PTG3IP<2:0 | )>    |       |         | PTG2IP<2:0> | >       | _       |        | PTG1IP<2:0> |        | 0444          |

| INTCON1      | 08C0  | NSTDIS | OVAERR | OVBERR     |        |        |        | _          | _     | _     | DIV0ERR | DMACERR     | MATHERR | ADDRERR | STKERR | OSCFAIL     | _      | 0000          |

| INTCON2      | 08C2  | GIE    | DISI   | SWTRAP     | _      | _      |        |            | —     |       | _       | —           | —       | _       | INT2EP | INT1EP      | INT0EP | 8000          |

| INTCON3      | 08C4  | _      | —      | —          | _      | _      |        |            | —     |       | _       | DAE         | DOOVR   | _       | —      | —           |        | 0000          |

| INTCON4      | 08C6  | _      | _      | _          | _      | _      | -      | _          | —     | _     | _       | _           | _       | —       | —      | _           | SGHT   | 0000          |

| INTTREG      | 08C8  | Ι      | _      | _          | _      |        | ILR<   | 3:0>       |       |       |         |             | VECN    | UM<7:0> |        |             |        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

|             |       |        |        |        |        |        |        | •            |              |               |              |       |        |       |       |       |       |               |

|-------------|-------|--------|--------|--------|--------|--------|--------|--------------|--------------|---------------|--------------|-------|--------|-------|-------|-------|-------|---------------|

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9        | Bit 8        | Bit 7         | Bit 6        | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| TMR1        | 0100  |        |        |        |        |        |        |              | Timer1       | Register      |              |       |        |       |       |       |       | xxxx          |

| PR1         | 0102  |        |        |        |        |        |        |              | Period F     | Register 1    |              |       |        |       |       |       |       | FFFF          |

| T1CON       | 0104  | TON    | _      | TSIDL  | _      | _      | _      | _            | _            | _             | TGATE        | TCKP  | S<1:0> | —     | TSYNC | TCS   |       | 0000          |

| TMR2        | 0106  |        |        |        |        |        |        |              | Timer2       | Register      |              |       |        |       |       |       |       | xxxx          |

| TMR3HLD     | 0108  |        |        |        |        |        | Time   | er3 Holding  | Register (fo | r 32-bit time | r operations | only) |        |       |       |       |       | xxxx          |

| TMR3        | 010A  |        |        |        |        |        |        |              | Timer3       | Register      |              |       |        |       |       |       |       | xxxx          |

| PR2         | 010C  |        |        |        |        |        |        |              | Period F     | Register 2    |              |       |        |       |       |       |       | FFFF          |

| PR3         | 010E  |        |        |        |        |        |        |              | Period F     | Register 3    |              |       |        |       |       |       |       | FFFF          |

| T2CON       | 0110  | TON    | —      | TSIDL  | —      | —      | —      | _            | —            | —             | TGATE        | TCKP  | S<1:0> | T32   | _     | TCS   |       | 0000          |

| T3CON       | 0112  | TON    | -      | TSIDL  | _      | _      | _      | _            | _            | _             | TGATE        | TCKP  | S<1:0> | _     | _     | TCS   |       | 0000          |

| TMR4        | 0114  |        |        | •      | •      | •      | •      | •            | Timer4       | Register      |              |       |        | •     |       | •     |       | xxxx          |

| TMR5HLD     | 0116  |        |        |        |        |        | Т      | imer5 Holdir | ng Register  | (for 32-bit o | perations on | ly)   |        |       |       |       |       | xxxx          |

| TMR5        | 0118  |        |        |        |        |        |        |              | Timer5       | Register      |              |       |        |       |       |       |       | xxxx          |

| PR4         | 011A  |        |        |        |        |        |        |              | Period F     | Register 4    |              |       |        |       |       |       |       | FFFF          |

| PR5         | 011C  |        |        |        |        |        |        |              | Period F     | Register 5    |              |       |        |       |       |       |       | FFFF          |

| T4CON       | 011E  | TON    | —      | TSIDL  | —      | —      | —      | —            | _            | —             | TGATE        | TCKP  | S<1:0> | T32   | —     | TCS   | —     | 0000          |

| T5CON       | 0120  | TON    | _      | TSIDL  | _      | _      | _      | _            | _            | _             | TGATE        | TCKP  | S<1:0> | _     | _     | TCS   | _     | 0000          |

# TABLE 4-8: TIMER1 THROUGH TIMER5 REGISTER MAP

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-56: PORTA REGISTER MAP FOR PIC24EPXXXGP/MC203 AND dsPIC33EPXXXGP/MC203/503 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|--------|-------|-------|-------|--------|--------|--------|--------|--------|---------------|

| TRISA        | 0E00  | _      | _      | _      | _      |        | _      | _     | TRISA8 | _     | —     | —     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 011F          |

| PORTA        | 0E02  | _      | _      | _      | _      | _      | _      | _     | RA8    | _     | _     | _     | RA4    | RA3    | RA2    | RA1    | RA0    | 0000          |

| LATA         | 0E04  | _      | _      | _      | _      | _      | _      | _     | LATA8  | _     | _     | _     | LATA4  | LATA3  | LATA2  | LA1TA1 | LA0TA0 | 0000          |

| ODCA         | 0E06  | _      | _      | _      | _      | _      | _      | _     | ODCA8  | _     | _     | _     | ODCA4  | ODCA3  | ODCA2  | ODCA1  | ODCA0  | 0000          |

| CNENA        | 0E08  | _      | _      | _      | _      | _      | _      | _     | CNIEA8 | _     | _     | _     | CNIEA4 | CNIEA3 | CNIEA2 | CNIEA1 | CNIEA0 | 0000          |

| CNPUA        | 0E0A  | _      | _      | _      | _      | _      | _      | _     | CNPUA8 | _     | _     | _     | CNPUA4 | CNPUA3 | CNPUA2 | CNPUA1 | CNPUA0 | 0000          |

| CNPDA        | 0E0C  | _      | _      | _      | _      | _      | _      | _     | CNPDA8 | _     | _     | _     | CNPDA4 | CNPDA3 | CNPDA2 | CNPDA1 | CNPDA0 | 0000          |

| ANSELA       | 0E0E  | _      | —      | _      | —      | _      | —      | _     | —      | _     | —     | —     | ANSA4  | —      | —      | ANSA1  | ANSA0  | 0013          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-57: PORTB REGISTER MAP FOR PIC24EPXXXGP/MC203 AND dsPIC33EPXXXGP/MC203/503 DEVICES ONLY

| File<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISB        | 0E10  | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF          |

| PORTB        | 0E12  | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx          |

| LATB         | 0E14  | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | xxxx          |

| ODCB         | 0E16  | ODCB15  | ODCB14  | ODCB13  | ODCB12  | ODCB11  | ODCB10  | ODCB9  | ODCB8  | ODCB7  | ODCB6  | ODCB5  | ODCB4  | ODCB3  | ODCB2  | ODCB1  | ODCB0  | 0000          |

| CNENB        | 0E18  | CNIEB15 | CNIEB14 | CNIEB13 | CNIEB12 | CNIEB11 | CNIEB10 | CNIEB9 | CNIEB8 | CNIEB7 | CNIEB6 | CNIEB5 | CNIEB4 | CNIEB3 | CNIEB2 | CNIEB1 | CNIEB0 | 0000          |

| CNPUB        | 0E1A  | CNPUB15 | CNPUB14 | CNPUB13 | CNPUB12 | CNPUB11 | CNPUB10 | CNPUB9 | CNPUB8 | CNPUB7 | CNPUB6 | CNPUB5 | CNPUB4 | CNPUB3 | CNPUB2 | CNPUB1 | CNPUB0 | 0000          |

| CNPDB        | 0E1C  | CNPDB15 | CNPDB14 | CNPDB13 | CNPDB12 | CNPDB11 | CNPDB10 | CNPDB9 | CNPDB8 | CNPDB7 | CNPDB6 | CNPDB5 | CNPDB4 | CNPDB3 | CNPDB2 | CNPDB1 | CNPDB0 | 0000          |

| ANSELB       | 0E1E  | _       | _       | -       | _       | -       | —       | -      | ANSB8  | _      | _      | _      | _      | ANSB3  | ANSB2  | ANSB1  | ANSB0  | 010F          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-58: PORTC REGISTER MAP FOR PIC24EPXXXGP/MC203 AND dsPIC33EPXXXGP/MC203/503 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|--------|-------|-------|-------|-------|-------|-------|--------|--------|---------------|

| TRISC        | 0E20  | _      | _      | _      | _      | _      | —      | —     | TRISC8 | _     | -     |       | _     |       | -     | TRISC1 | TRISC0 | 0103          |

| PORTC        | 0E22  |        |        | -      | -      |        | —      | _     | RC8    | —     | -     |       | _     |       |       | RC1    | RC0    | xxxx          |

| LATC         | 0E24  |        |        | _      | _      | _      | _      | _     | LATC8  | _     | _     | _     | _     | _     | _     | LATC1  | LATC0  | xxxx          |

| ODCC         | 0E26  |        |        | _      | _      | _      | _      | _     | ODCC8  | _     | _     | _     | _     | _     | _     | ODCC1  | ODCC0  | 0000          |

| CNENC        | 0E28  | —      | _      | -      | _      |        | _      | _     | CNIEC8 | —     |       |       | _     |       |       | CNIEC1 | CNIEC0 | 0000          |

| CNPUC        | 0E2A  |        |        | _      | _      | _      | _      | _     | CNPUC8 | _     | _     | _     | _     | _     | _     | CNPUC1 | CNPUC0 | 0000          |

| CNPDC        | 0E2C  |        |        | _      | _      | _      | _      | _     | CNPDC8 | _     | _     | _     | _     | _     | _     | CNPDC1 | CNPDC0 | 0000          |

| ANSELC       | 0E2E  | -      | _      | _      | _      | _      | —      | —     | _      | —     |       | _     | _     | _     |       | ANSC1  | ANSC0  | 0003          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## 10.2.1 SLEEP MODE

The following occurs in Sleep mode:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption is reduced to a minimum, provided that no I/O pin is sourcing current.

- The Fail-Safe Clock Monitor does not operate, since the system clock source is disabled.

- The LPRC clock continues to run in Sleep mode if the WDT is enabled.

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode.

- Some device features or peripherals can continue to operate. This includes items such as the Input Change Notification (ICN) on the I/O ports or peripherals that use an external clock input.

- Any peripheral that requires the system clock source for its operation is disabled.

The device wakes up from Sleep mode on any of these events:

- Any interrupt source that is individually enabled

- · Any form of device Reset

- A WDT time-out

On wake-up from Sleep mode, the processor restarts with the same clock source that was active when Sleep mode was entered.

For optimal power savings, the internal regulator and the Flash regulator can be configured to go into Standby when Sleep mode is entered by clearing the VREGS (RCON<8>) and VREGSF (RCON<11>) bits (default configuration).

If the application requires a faster wake-up time, and can accept higher current requirements, the VREGS (RCON<8>) and VREGSF (RCON<11>) bits can be set to keep the internal regulator and the Flash regulator active during Sleep mode.

## 10.2.2 IDLE MODE

The following occurs in Idle mode:

- The CPU stops executing instructions.

- · The WDT is automatically cleared.

- The system clock source remains active. By default, all peripheral modules continue to operate normally from the system clock source, but can also be selectively disabled (see Section 10.4 "Peripheral Module Disable").

- If the WDT or FSCM is enabled, the LPRC also remains active.

The device wakes from Idle mode on any of these events:

- · Any interrupt that is individually enabled

- Any device Reset

- · A WDT time-out

On wake-up from Idle mode, the clock is reapplied to the CPU and instruction execution will begin (2-4 clock cycles later), starting with the instruction following the PWRSAV instruction or the first instruction in the Interrupt Service Routine (ISR).

All peripherals also have the option to discontinue operation when Idle mode is entered to allow for increased power savings. This option is selectable in the control register of each peripheral; for example, the TSIDL bit in the Timer1 Control register (T1CON<13>).

### 10.2.3 INTERRUPTS COINCIDENT WITH POWER SAVE INSTRUCTIONS

Any interrupt that coincides with the execution of a PWRSAV instruction is held off until entry into Sleep or Idle mode has completed. The device then wakes up from Sleep or Idle mode.

| R/W-0         | R/W-0        | R/W-0                                                 | R/W-0   | R/W-0             | R/W-0                 | R/W-0                | U-0   |

|---------------|--------------|-------------------------------------------------------|---------|-------------------|-----------------------|----------------------|-------|

| T5MD          | T4MD         | T3MD                                                  | T2MD    | T1MD              | QEI1MD <sup>(1)</sup> | PWMMD <sup>(1)</sup> | _     |

| bit 15        |              |                                                       |         |                   |                       |                      | bit   |

|               |              |                                                       |         |                   |                       |                      |       |

| R/W-0         | R/W-0        | R/W-0                                                 | R/W-0   | R/W-0             | U-0                   | R/W-0                | R/W-0 |

| I2C1MD        | U2MD         | U1MD                                                  | SPI2MD  | SPI1MD            | —                     | C1MD <sup>(2)</sup>  | AD1MD |

| bit 7         |              |                                                       |         |                   |                       |                      | bit   |

| Legend:       |              |                                                       |         |                   |                       |                      |       |

| R = Readabl   | e bit        | W = Writable                                          | bit     | U = Unimplen      | nented bit, read      | d as '0'             |       |

| -n = Value at | POR          | '1' = Bit is set                                      |         | '0' = Bit is clea | ared                  | x = Bit is unkno     | own   |

| bit 15        | 1 = Timer5 m | 5 Module Disal<br>odule is disable<br>odule is enable | ed      |                   |                       |                      |       |

| bit 14        | 1 = Timer4 m | 4 Module Disal<br>odule is disable<br>odule is enable | ed      |                   |                       |                      |       |

| bit 13        | 1 = Timer3 m | 3 Module Disal<br>odule is disable<br>odule is enable | ed      |                   |                       |                      |       |

| bit 12        | 1 = Timer2 m | 2 Module Disal<br>odule is disable<br>odule is enable | ed      |                   |                       |                      |       |

| bit 11        | 1 = Timer1 m | 1 Module Disal<br>odule is disable<br>odule is enable | ed      |                   |                       |                      |       |

| bit 10        | 1 = QEI1 mod | 11 Module Disa<br>Iule is disablec<br>Iule is enabled |         |                   |                       |                      |       |

| bit 9         | 1 = PWM mod  | /M Module Dis<br>dule is disabled<br>dule is enabled  | 1       |                   |                       |                      |       |

| bit 8         | Unimplemen   | ted: Read as '                                        | כי      |                   |                       |                      |       |

| bit 7         | 1 = I2C1 mod | 1 Module Disal<br>ule is disabled<br>ule is enabled   | ble bit |                   |                       |                      |       |

| bit 6         | 1 = UART2 m  | 2 Module Disa<br>odule is disabl<br>odule is enable   | ed      |                   |                       |                      |       |

| bit 5         | 1 = UART1 m  | 1 Module Disa<br>odule is disabl<br>odule is enable   | ed      |                   |                       |                      |       |

| bit 4         | 1 = SPI2 mod | 2 Module Disa<br>lule is disabled<br>lule is enabled  | ole bit |                   |                       |                      |       |

# REGISTER 10-1: PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1

Note 1: This bit is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This bit is available on dsPIC33EPXXXGP50X and dsPIC33EPXXXMC50X devices only.

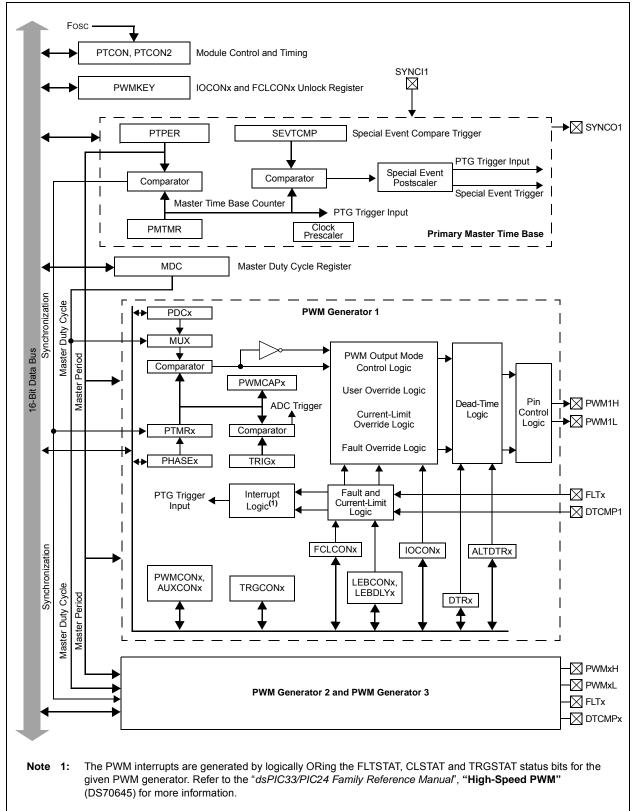

#### FIGURE 16-2: HIGH-SPEED PWMx MODULE REGISTER INTERCONNECTION DIAGRAM

# 16.3 PWMx Control Registers

#### REGISTER 16-1: PTCON: PWMx TIME BASE CONTROL REGISTER

| R/W-0  | U-0 | R/W-0  | HS/HC-0 | R/W-0 | R/W-0               | R/W-0                  | R/W-0                  |

|--------|-----|--------|---------|-------|---------------------|------------------------|------------------------|

| PTEN   | —   | PTSIDL | SESTAT  | SEIEN | EIPU <sup>(1)</sup> | SYNCPOL <sup>(1)</sup> | SYNCOEN <sup>(1)</sup> |

| bit 15 |     |        |         |       |                     |                        | bit 8                  |

| R/W-0                 | R/W-0                   | R/W-0                   | R/W-0                   | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  |

|-----------------------|-------------------------|-------------------------|-------------------------|------------------------|------------------------|------------------------|------------------------|

| SYNCEN <sup>(1)</sup> | SYNCSRC2 <sup>(1)</sup> | SYNCSRC1 <sup>(1)</sup> | SYNCSRC0 <sup>(1)</sup> | SEVTPS3 <sup>(1)</sup> | SEVTPS2 <sup>(1)</sup> | SEVTPS1 <sup>(1)</sup> | SEVTPS0 <sup>(1)</sup> |

| bit 7                 | •                       |                         |                         |                        |                        |                        | bit 0                  |

| Legend:           | HC = Hardware Clearable bit | HS = Hardware Settable bit | t                  |

|-------------------|-----------------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, re  | ad as '0'          |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared       | x = Bit is unknown |

| bit 15  | PTEN: PWMx Module Enable bit                                                                                                                            |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = PWMx module is enabled</li> <li>0 = PWMx module is disabled</li> </ul>                                                                     |

| bit 14  | Unimplemented: Read as '0'                                                                                                                              |

| bit 13  | PTSIDL: PWMx Time Base Stop in Idle Mode bit                                                                                                            |

|         | <ul> <li>1 = PWMx time base halts in CPU Idle mode</li> <li>0 = PWMx time base runs in CPU Idle mode</li> </ul>                                         |

| bit 12  | SESTAT: Special Event Interrupt Status bit                                                                                                              |

|         | <ul> <li>1 = Special event interrupt is pending</li> <li>0 = Special event interrupt is not pending</li> </ul>                                          |

| bit 11  | SEIEN: Special Event Interrupt Enable bit                                                                                                               |

|         | 1 = Special event interrupt is enabled                                                                                                                  |

|         | 0 = Special event interrupt is disabled                                                                                                                 |

| bit 10  | EIPU: Enable Immediate Period Updates bit <sup>(1)</sup>                                                                                                |

|         | <ul> <li>1 = Active Period register is updated immediately</li> <li>0 = Active Period register updates occur on PWMx cycle boundaries</li> </ul>        |

| bit 9   | SYNCPOL: Synchronize Input and Output Polarity bit <sup>(1)</sup>                                                                                       |

|         | 1 = SYNCI1/SYNCO1 polarity is inverted (active-low)                                                                                                     |

|         | 0 = SYNCI1/SYNCO1 is active-high                                                                                                                        |

| bit 8   | SYNCOEN: Primary Time Base Sync Enable bit <sup>(1)</sup>                                                                                               |

|         | 1 = SYNCO1 output is enabled                                                                                                                            |

| L:1 7   | 0 = SYNCO1 output is disabled                                                                                                                           |

| bit 7   | SYNCEN: External Time Base Synchronization Enable bit <sup>(1)</sup>                                                                                    |

|         | <ul> <li>1 = External synchronization of primary time base is enabled</li> <li>0 = External synchronization of primary time base is disabled</li> </ul> |

|         |                                                                                                                                                         |

| Note 1: | These bits should be changed only when PTEN = 0. In addition, when using the SYNCI1 feature, the user                                                   |

|         | application must program the period register with a value that is slightly larger than the expected period of                                           |

the external synchronization input signal.

2: See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for information on this selection.

## REGISTER 17-2: QEI1IOC: QEI1 I/O CONTROL REGISTER (CONTINUED)

- bit 2 INDEX: Status of INDXx Input Pin After Polarity Control

- 1 = Pin is at logic '1'

- 0 = Pin is at logic '0'

- bit 1 QEB: Status of QEBx Input Pin After Polarity Control And SWPAB Pin Swapping 1 = Pin is at logic '1' 0 = Pin is at logic '0'

- bit 0 **QEA:** Status of QEAx Input Pin After Polarity Control And SWPAB Pin Swapping 1 = Pin is at logic '1'

- 0 = Pin is at logic '0'

# 20.3 UARTx Control Registers

#### REGISTER 20-1: UXMODE: UARTX MODE REGISTER

| R/W-0                | U-0                                           | R/W-0                                                                                          | R/W-0                                                    | R/W-0                              | U-0                        | R/W-0                   | R/W-0                     |

|----------------------|-----------------------------------------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------|------------------------------------|----------------------------|-------------------------|---------------------------|

| UARTEN <sup>(1</sup> | ) _                                           | USIDL                                                                                          | IREN <sup>(2)</sup>                                      | RTSMD                              |                            | UEN1                    | UEN0                      |

| bit 15               |                                               |                                                                                                |                                                          |                                    |                            |                         | bit                       |

|                      |                                               |                                                                                                |                                                          |                                    | <b>D</b> 444 A             |                         |                           |

| R/W-0, HC            |                                               | R/W-0, HC                                                                                      | R/W-0                                                    | R/W-0                              | R/W-0                      | R/W-0                   | R/W-0                     |

| WAKE                 | LPBACK                                        | ABAUD                                                                                          | URXINV                                                   | BRGH                               | PDSEL1                     | PDSEL0                  | STSEL                     |

| bit 7                |                                               |                                                                                                |                                                          |                                    |                            |                         | bit                       |

| Legend:              |                                               | HC = Hardwar                                                                                   | e Clearable b                                            | it                                 |                            |                         |                           |

| R = Readal           | ole bit                                       | W = Writable b                                                                                 | it                                                       | U = Unimplem                       | nented bit, read           | as '0'                  |                           |

| -n = Value a         | at POR                                        | '1' = Bit is set                                                                               |                                                          | '0' = Bit is clea                  |                            | x = Bit is unkn         | iown                      |

| bit 15               | 1 = UARTx is                                  | ARTx Enable bit<br>s enabled; all UA<br>s disabled; all UA                                     | ARTx pins are                                            |                                    |                            |                         |                           |

| bit 14               | Unimplemen                                    | ted: Read as '0                                                                                | ,                                                        |                                    |                            |                         |                           |

| bit 13               | USIDL: UAR                                    | Tx Stop in Idle M                                                                              | lode bit                                                 |                                    |                            |                         |                           |

|                      |                                               | nues module opera                                                                              |                                                          |                                    | le mode                    |                         |                           |

| bit 12               | 1 = IrDA end                                  | Encoder and De<br>oder and decod<br>oder and decod                                             | er are enable                                            | d                                  |                            |                         |                           |

| bit 11               | $1 = \overline{\text{UxRTS}} p$               | le Selection for<br>bin is in Simplex<br>bin is in Flow Co                                     | mode                                                     | t                                  |                            |                         |                           |

| bit 10               | Unimplemen                                    | ted: Read as '0                                                                                | ,                                                        |                                    |                            |                         |                           |

| bit 9-8              | 11 = UxTX, U<br>10 = UxTX, U<br>01 = UxTX, U  | JARTx Pin Enab<br>JxRX and BCLK<br>JxRX, UxCTS ar<br>JxRX and UxRT<br>nd UxRX pins a<br>atches | x p <u>ins are</u> ena<br>nd UxRTS pin<br>S pins are ena | s are enabled a<br>abled and used; | nd used <sup>(4)</sup><br> | controlled by PC        | ORT latches <sup>(4</sup> |

| bit 7                | WAKE: Wake                                    | e-up on Start bit                                                                              | Detect During                                            | Sleep Mode E                       | nable bit                  |                         |                           |

|                      | in hardw                                      | continues to sam<br>are on the follow<br>-up is enabled                                        |                                                          |                                    | generated on t             | the falling edge        | ; bit is cleare           |

| bit 6                | LPBACK: UA                                    | ARTx Loopback                                                                                  | Mode Select I                                            | bit                                |                            |                         |                           |

|                      |                                               | Loopback mode<br>k mode is disabl                                                              |                                                          |                                    |                            |                         |                           |

| e                    | Refer to the " <b>UAI</b><br>enabling the UAF | RTx module for re                                                                              | ceive or trans                                           | mit operation.                     | -                          | <i>ce Manual"</i> for i | nformation or             |

| 2:                   | This feature is or                            | nly available for                                                                              | the 16x BRG                                              | mode (BRGH =                       | 0).                        |                         |                           |

|                      | This feature is or                            | -                                                                                              | =                                                        | -                                  |                            |                         |                           |

| 4                    | This fasture is ar                            | ly available on (                                                                              | 24 nin dovice                                            | -                                  |                            |                         |                           |

4: This feature is only available on 64-pin devices.

| U-0               | U-0                                           | R-0                                                 | R-0   | R-0                  | R-0   | R-0                | R-0   |  |  |

|-------------------|-----------------------------------------------|-----------------------------------------------------|-------|----------------------|-------|--------------------|-------|--|--|

| _                 | _                                             | FBP5                                                | FBP4  | FBP3                 | FBP2  | FBP1               | FBP0  |  |  |

| bit 15            |                                               |                                                     |       |                      |       |                    | bit 8 |  |  |

|                   |                                               |                                                     |       |                      |       |                    |       |  |  |

| U-0               | U-0                                           | R-0                                                 | R-0   | R-0                  | R-0   | R-0                | R-0   |  |  |

|                   | —                                             | FNRB5                                               | FNRB4 | FNRB3                | FNRB2 | FNRB1              | FNRB0 |  |  |

| bit 7             |                                               |                                                     |       |                      |       |                    | bit ( |  |  |

| Legend:           |                                               |                                                     |       |                      |       |                    |       |  |  |

| R = Readab        | le bit                                        | W = Writable bit U = Unimplemented bit, read as '0' |       |                      |       |                    |       |  |  |

| -n = Value at POR |                                               | '1' = Bit is set                                    |       | '0' = Bit is cleared |       | x = Bit is unknown |       |  |  |

|                   |                                               |                                                     |       |                      |       |                    |       |  |  |

| bit 15-14         | Unimpleme                                     | ented: Read as '                                    | 0'    |                      |       |                    |       |  |  |

| bit 13-8          | FBP<5:0>: FIFO Buffer Pointer bits            |                                                     |       |                      |       |                    |       |  |  |

|                   | 011111 = RB31 buffer                          |                                                     |       |                      |       |                    |       |  |  |

|                   | 011110 <b>= F</b>                             | RB30 buffer                                         |       |                      |       |                    |       |  |  |

|                   | •                                             |                                                     |       |                      |       |                    |       |  |  |

|                   | •                                             |                                                     |       |                      |       |                    |       |  |  |

|                   | • $000001 - TPP1 huffer$                      |                                                     |       |                      |       |                    |       |  |  |

|                   | 000001 = TRB1 buffer<br>000000 = TRB0 buffer  |                                                     |       |                      |       |                    |       |  |  |

| bit 7-6           | Unimplemented: Read as '0'                    |                                                     |       |                      |       |                    |       |  |  |

| bit 5-0           | FNRB<5:0>: FIFO Next Read Buffer Pointer bits |                                                     |       |                      |       |                    |       |  |  |

|                   | 011111 = RB31 buffer                          |                                                     |       |                      |       |                    |       |  |  |

|                   | 011110 = RB30 buffer                          |                                                     |       |                      |       |                    |       |  |  |

|                   | •                                             |                                                     |       |                      |       |                    |       |  |  |

|                   | •                                             |                                                     |       |                      |       |                    |       |  |  |

|                   |                                               |                                                     |       |                      |       |                    |       |  |  |

|                   | •                                             |                                                     |       |                      |       |                    |       |  |  |

|                   |                                               | FRB1 buffer<br>FRB0 buffer                          |       |                      |       |                    |       |  |  |

#### REGISTER 21-5: CxFIFO: ECANx FIFO STATUS REGISTER

## REGISTER 21-6: CxINTF: ECANx INTERRUPT FLAG REGISTER (CONTINUED)

- bit 1 **RBIF:** RX Buffer Interrupt Flag bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

- bit 0 **TBIF:** TX Buffer Interrupt Flag bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| REGISTER 21-26: | CxTRmnCON: ECANx TX/RX BUFFER mn CONTROL REGISTER |

|-----------------|---------------------------------------------------|

|                 | (m = 0,2,4,6; n = 1,3,5,7)                        |

|                                               | ( •                                                                                                                                                     | ,_, ., ., .,                                    | -,-,-,                         |                  |                  |                    |                 |  |  |

|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|--------------------------------|------------------|------------------|--------------------|-----------------|--|--|

| R/W-0                                         | R-0                                                                                                                                                     | R-0                                             | R-0                            | R/W-0            | R/W-0            | R/W-0              | R/W-0           |  |  |

| TXENn                                         | TXABTn                                                                                                                                                  | TXLARBn                                         | TXERRn                         | TXREQn           | RTRENn           | TXnPRI1            | TXnPRI0         |  |  |

| bit 15                                        |                                                                                                                                                         |                                                 |                                |                  |                  |                    | bit 8           |  |  |

| R/W-0                                         | R-0                                                                                                                                                     | R-0                                             | R-0                            | R/W-0            | R/W-0            | R/W-0              | R/W-0           |  |  |

| TXENm                                         | TXABTm <sup>(1)</sup>                                                                                                                                   | TXLARBm <sup>(1)</sup>                          | TXERRm <sup>(1)</sup>          | TXREQm           | RTRENm           | TXmPRI1            | TXmPRI0         |  |  |

| bit 7                                         |                                                                                                                                                         |                                                 | •                              |                  |                  |                    | bit 0           |  |  |

| Legend:                                       |                                                                                                                                                         |                                                 |                                |                  |                  |                    |                 |  |  |

| R = Readab                                    | le bit                                                                                                                                                  | W = Writable                                    | bit                            | U = Unimpler     | mented bit, read | d as '0'           |                 |  |  |

| -n = Value a                                  | t POR                                                                                                                                                   | '1' = Bit is set                                |                                | '0' = Bit is cle | ared             | x = Bit is unknown |                 |  |  |

| bit 15-8                                      | See Definitio                                                                                                                                           | n for bits<7:0>,                                | Controls Buffe                 | ar n             |                  |                    |                 |  |  |

| bit 7                                         |                                                                                                                                                         | RX Buffer Sele                                  |                                | 51 11            |                  |                    |                 |  |  |

|                                               |                                                                                                                                                         |                                                 |                                |                  |                  |                    |                 |  |  |

|                                               | 1 = Buffer TRBn is a transmit buffer<br>0 = Buffer TRBn is a receive buffer                                                                             |                                                 |                                |                  |                  |                    |                 |  |  |

| bit 6                                         | TXABTm: M                                                                                                                                               | TXABTm: Message Aborted bit <sup>(1)</sup>      |                                |                  |                  |                    |                 |  |  |

|                                               |                                                                                                                                                         | 1 = Message was aborted                         |                                |                  |                  |                    |                 |  |  |

|                                               | 0 = Message                                                                                                                                             | completed tran                                  | nsmission succ                 | cessfully        |                  |                    |                 |  |  |

| bit 5                                         | TXLARBm: N                                                                                                                                              | Message Lost A                                  | Arbitration bit <sup>(1)</sup> | )                |                  |                    |                 |  |  |

|                                               |                                                                                                                                                         | lost arbitration did not lose ar                |                                |                  |                  |                    |                 |  |  |

| bit 4                                         | <ul> <li>0 = Message did not lose arbitration while being sent</li> <li>TXERRm: Error Detected During Transmission bit<sup>(1)</sup></li> </ul>         |                                                 |                                |                  |                  |                    |                 |  |  |

|                                               | 1 = A bus error occurred while the message was being sent                                                                                               |                                                 |                                |                  |                  |                    |                 |  |  |

|                                               | 0 = A bus err                                                                                                                                           | or did not occu                                 | r while the me                 | ssage was bei    | ing sent         |                    |                 |  |  |

| bit 3                                         | TXREQm: M                                                                                                                                               | TXREQm: Message Send Request bit                |                                |                  |                  |                    |                 |  |  |

|                                               | sent                                                                                                                                                    |                                                 | -                              |                  | ally clears wher | n the message      | is successfully |  |  |

|                                               | 0 = Clearing the bit to '0' while set requests a message abort                                                                                          |                                                 |                                |                  |                  |                    |                 |  |  |

| bit 2 RTRENm: Auto-Remote Transmit Enable bit |                                                                                                                                                         |                                                 |                                |                  |                  |                    |                 |  |  |

|                                               | <ul> <li>1 = When a remote transmit is received, TXREQ will be set</li> <li>0 = When a remote transmit is received, TXREQ will be unaffected</li> </ul> |                                                 |                                |                  |                  |                    |                 |  |  |

| bit 1-0                                       | TXmPRI<1:0                                                                                                                                              | TXmPRI<1:0>: Message Transmission Priority bits |                                |                  |                  |                    |                 |  |  |

|                                               | -                                                                                                                                                       | message prior                                   | •                              |                  |                  |                    |                 |  |  |

|                                               | 0                                                                                                                                                       | ermediate mes                                   |                                |                  |                  |                    |                 |  |  |

|                                               |                                                                                                                                                         | ermediate mess<br>message priori                |                                |                  |                  |                    |                 |  |  |

| <b>.</b> –                                    |                                                                                                                                                         |                                                 | -                              |                  |                  |                    |                 |  |  |

| Note 1: ⊤                                     | his bit is cleared                                                                                                                                      | when IXREQ                                      | s set.                         |                  |                  |                    |                 |  |  |

Note: The buffers, SID, EID, DLC, Data Field, and Receive Status registers are located in DMA RAM.

## 25.3 Op Amp/Comparator Registers

| R/W-0         | U-0                                                                                                                          | U-0                                                 | U-0                          | R-0                     | R-0                  | R-0                  | R-0                  |  |  |

|---------------|------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|------------------------------|-------------------------|----------------------|----------------------|----------------------|--|--|

| PSIDL         |                                                                                                                              | _                                                   | _                            | C4EVT <sup>(1)</sup>    | C3EVT <sup>(1)</sup> | C2EVT <sup>(1)</sup> | C1EVT <sup>(1)</sup> |  |  |

| bit 15        |                                                                                                                              |                                                     | •                            |                         |                      |                      | bit                  |  |  |

|               |                                                                                                                              |                                                     |                              |                         |                      |                      |                      |  |  |

| U-0           | U-0                                                                                                                          | U-0                                                 | U-0                          | R-0                     | R-0                  | R-0                  | R-0                  |  |  |

| _             | —                                                                                                                            | _                                                   | _                            | C4OUT <sup>(2)</sup>    | C3OUT <sup>(2)</sup> | C2OUT <sup>(2)</sup> | C10UT <sup>(2)</sup> |  |  |

| bit 7         |                                                                                                                              |                                                     |                              |                         |                      |                      | bit                  |  |  |

|               |                                                                                                                              |                                                     |                              |                         |                      |                      |                      |  |  |

| Legend:       | - 1-:4                                                                                                                       |                                                     | L:4                          |                         |                      |                      |                      |  |  |

| R = Readabl   |                                                                                                                              | W = Writable                                        |                              | -                       | nented bit, read     |                      |                      |  |  |

| -n = Value at | PUR                                                                                                                          | '1' = Bit is se                                     | [                            | '0' = Bit is clea       | ared                 | x = Bit is unkr      | IOWN                 |  |  |

| bit 15        |                                                                                                                              | narator Ston in                                     | Idle Mode hit                |                         |                      |                      |                      |  |  |

|               | <b>PSIDL:</b> Comparator Stop in Idle Mode bit<br>1 = Discontinues operation of all comparators when device enters Idle mode |                                                     |                              |                         |                      |                      |                      |  |  |

|               | <ul> <li>0 = Continues operation of all comparators in Idle mode</li> </ul>                                                  |                                                     |                              |                         |                      |                      |                      |  |  |

| bit 14-12     | Unimplemented: Read as '0'                                                                                                   |                                                     |                              |                         |                      |                      |                      |  |  |

| bit 11        | C4EVT: Op A                                                                                                                  | mp/Comparate                                        | or 4 Event Sta               | atus bit <sup>(1)</sup> |                      |                      |                      |  |  |

|               | 1 = Op amp/comparator event occurred                                                                                         |                                                     |                              |                         |                      |                      |                      |  |  |

|               | 0 = Op amp/comparator event did not occur                                                                                    |                                                     |                              |                         |                      |                      |                      |  |  |

| bit 10        | C3EVT: Comparator 3 Event Status bit <sup>(1)</sup>                                                                          |                                                     |                              |                         |                      |                      |                      |  |  |

|               | 1 = Comparator event occurred<br>0 = Comparator event did not occur                                                          |                                                     |                              |                         |                      |                      |                      |  |  |

| bit 9         | C2EVT: Comparator 2 Event Status bit <sup>(1)</sup>                                                                          |                                                     |                              |                         |                      |                      |                      |  |  |

|               | 1 = Comparator event occurred                                                                                                |                                                     |                              |                         |                      |                      |                      |  |  |

|               |                                                                                                                              | tor event did n                                     |                              |                         |                      |                      |                      |  |  |

| bit 8         |                                                                                                                              | C1EVT: Comparator 1 Event Status bit <sup>(1)</sup> |                              |                         |                      |                      |                      |  |  |

|               | 1 = Comparator event occurred<br>0 = Comparator event did not occur                                                          |                                                     |                              |                         |                      |                      |                      |  |  |

| bit 7-4       | 0 = Comparator event did not occur<br>Unimplemented: Read as '0'                                                             |                                                     |                              |                         |                      |                      |                      |  |  |

| bit 3         | <b>C4OUT:</b> Comparator 4 Output Status bit <sup>(2)</sup>                                                                  |                                                     |                              |                         |                      |                      |                      |  |  |

| bit 3         | When CPOL                                                                                                                    |                                                     |                              |                         |                      |                      |                      |  |  |

|               | 1 = VIN+ > VI                                                                                                                | N-                                                  |                              |                         |                      |                      |                      |  |  |

|               | 0 = VIN + < VI                                                                                                               |                                                     |                              |                         |                      |                      |                      |  |  |

|               | $\frac{\text{When CPOL} = 1:}{1 = \text{VIN} + < \text{VIN}}$                                                                |                                                     |                              |                         |                      |                      |                      |  |  |

|               | 0 = VIN + > VIN -                                                                                                            |                                                     |                              |                         |                      |                      |                      |  |  |

| bit 2         | C3OUT: Com                                                                                                                   | parator 3 Outp                                      | out Status bit <sup>(;</sup> | 2)                      |                      |                      |                      |  |  |

|               | When CPOL                                                                                                                    |                                                     |                              |                         |                      |                      |                      |  |  |

|               | 1 = VIN+ > VI<br>0 = VIN+ < VI                                                                                               |                                                     |                              |                         |                      |                      |                      |  |  |

|               | 0 = VIN + < VI<br>When CPOL                                                                                                  |                                                     |                              |                         |                      |                      |                      |  |  |

|               | 1 = VIN + < VII                                                                                                              |                                                     |                              |                         |                      |                      |                      |  |  |

|               | $\perp = VIN + < VI$                                                                                                         | N-                                                  |                              |                         |                      |                      |                      |  |  |

#### REGISTER 25-1: CMSTAT: OP AMP/COMPARATOR STATUS REGISTER

- **Note 1:** Reflects the value of the of the CEVT bit in the respective Op Amp/Comparator Control register, CMxCON<9>.

- 2: Reflects the value of the COUT bit in the respective Op Amp/Comparator Control register, CMxCON<8>.

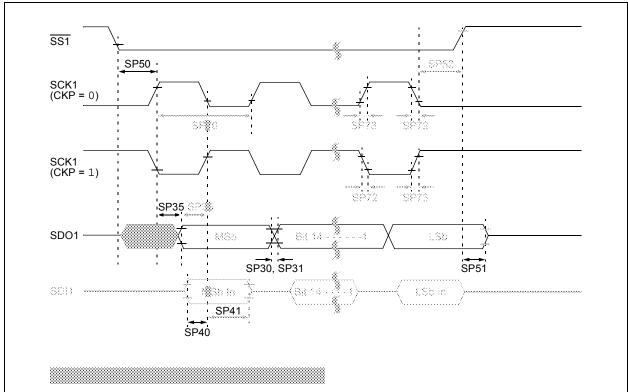

### FIGURE 30-28: SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0) TIMING CHARACTERISTICS

# APPENDIX A: REVISION HISTORY

# **Revision A (April 2011)**

This is the initial released version of the document.

## Revision B (July 2011)

This revision includes minor typographical and formatting changes throughout the data sheet text.

All other major changes are referenced by their respective section in Table A-1.

## TABLE A-1: MAJOR SECTION UPDATES

| Section Name                                                                     | Update Description                                                                                                                                                                                                                                                                                                      |

|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "High-Performance, 16-bit<br>Digital Signal Controllers<br>and Microcontrollers" | Changed all pin diagrams references of VLAP to TLA.                                                                                                                                                                                                                                                                     |

| Section 4.0 "Memory<br>Organization"                                             | Updated the All Resets values for CLKDIV and PLLFBD in the System Control Register Map (see Table 4-35).                                                                                                                                                                                                                |

| Section 5.0 "Flash Program<br>Memory"                                            | Updated "one word" to "two words" in the first paragraph of <b>Section 5.2 "RTSP Operation"</b> .                                                                                                                                                                                                                       |

| Section 9.0 "Oscillator<br>Configuration"                                        | Updated the PLL Block Diagram (see Figure 9-2).<br>Updated the Oscillator Mode, Fast RC Oscillator (FRC) with divide-by-N and PLL<br>(FRCPLL), by changing (FRCDIVN + PLL) to (FRCPLL).                                                                                                                                 |

|                                                                                  | Changed (FRCDIVN + PLL) to (FRCPLL) for COSC<2:0> = 001 and NOSC<2:0> = 001 in the Oscillator Control Register (see Register 9-1).                                                                                                                                                                                      |

|                                                                                  | Changed the POR value from 0 to 1 for the DOZE<1:0> bits, from 1 to 0 for the FRCDIV<0> bit, and from 0 to 1 for the PLLPOST<0> bit; Updated the default definitions for the DOZE<2:0> and FRCDIV<2:0> bits and updated all bit definitions for the PLLPOST<1:0> bits in the Clock Divisor Register (see Register 9-2). |

|                                                                                  | Changed the POR value from 0 to 1 for the PLLDIV<5:4> bits and updated the default definitions for all PLLDIV<8:0> bits in the PLL Feedback Division Register (see Register 9-2).                                                                                                                                       |

| Section 22.0 "Charge Time<br>Measurement Unit (CTMU)"                            | Updated the bit definitions for the IRNG<1:0> bits in the CTMU Current Control Register (see Register 22-3).                                                                                                                                                                                                            |

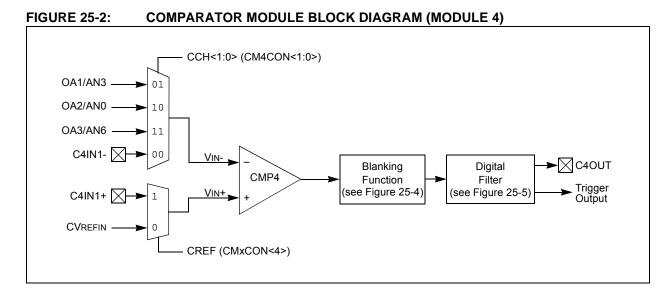

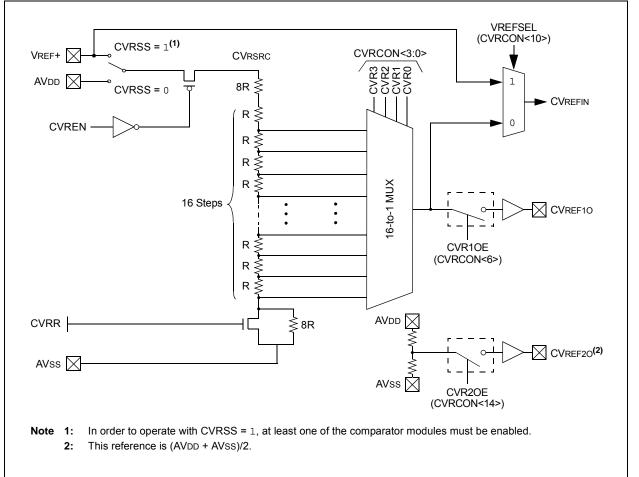

| Section 25.0 "Op amp/<br>Comparator Module"                                      | Updated the voltage reference block diagrams (see Figure 25-1 and Figure 25-2).                                                                                                                                                                                                                                         |

| Section Name                                                                                              | Update Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|