Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 60 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                  |

| Number of I/O              | 53                                                                             |

| Program Memory Size        | 256KB (85.5K x 24)                                                             |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | · · · · · · · · · · · · · · · · · · ·                                          |

| RAM Size                   | 16K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-VFQFN Exposed Pad                                                           |

| Supplier Device Package    | 64-QFN (9x9)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep256mc206-h-mr |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.0 DEVICE OVERVIEW

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive resource. To complement the information in this data sheet, refer to the related section of the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com)

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This document contains device-specific information for the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X Digital Signal Controller (DSC) and Microcontroller (MCU) devices.

dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices contain extensive Digital Signal Processor (DSP) functionality with a high-performance, 16-bit MCU architecture.

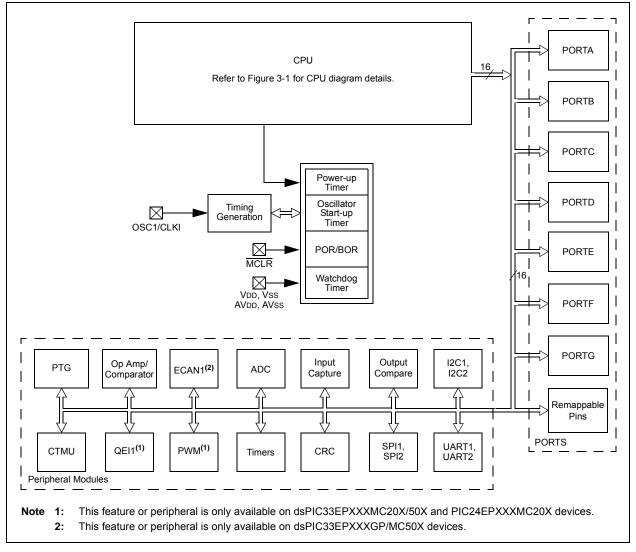

Figure 1-1 shows a general block diagram of the core and peripheral modules. Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

#### FIGURE 1-1: dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X BLOCK DIAGRAM

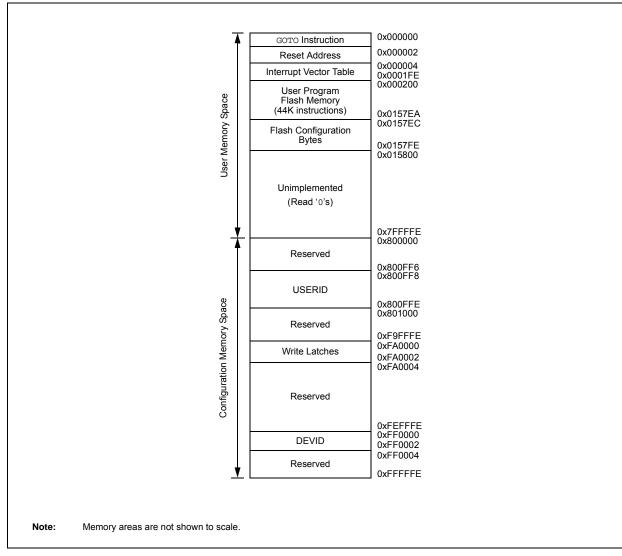

#### FIGURE 4-3: PROGRAM MEMORY MAP FOR dsPIC33EP128GP50X, dsPIC33EP128MC20X/50X AND PIC24EP128GP/MC20X DEVICES

## TABLE 4-19: SPI1 AND SPI2 REGISTER MAP

| SFR Name | Addr. | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8        | Bit 7       | Bit 6      | Bit 5  | Bit 4     | Bit 3      | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|----------|-------|--------|--------|---------|--------|--------|--------|------------|--------------|-------------|------------|--------|-----------|------------|-------|--------|--------|---------------|

| SPI1STAT | 0240  | SPIEN  | _      | SPISIDL | _      | _      | 5      | SPIBEC<2:0 | >            | SRMPT       | SPIROV     | SRXMPT |           | SISEL<2:0> |       | SPITBF | SPIRBF | 0000          |

| SPI1CON1 | 0242  | _      | _      | _       | DISSCK | DISSDO | MODE16 | SMP        | CKE          | SSEN        | CKP        | MSTEN  | SPRE<2:0> |            | PPRE  | <1:0>  | 0000   |               |

| SPI1CON2 | 0244  | FRMEN  | SPIFSD | FRMPOL  | _      | _      |        | _          | _            | —           | _          | _      | _         | _          | _     | FRMDLY | SPIBEN | 0000          |

| SPI1BUF  | 0248  |        |        |         |        |        |        | SPI1 Tra   | insmit and R | eceive Buff | er Registe | r      |           |            |       |        |        | 0000          |

| SPI2STAT | 0260  | SPIEN  | _      | SPISIDL | _      | _      | ŝ      | SPIBEC<2:0 | >            | SRMPT       | SPIROV     | SRXMPT |           | SISEL<2:0> |       | SPITBF | SPIRBF | 0000          |

| SPI2CON1 | 0262  | _      | _      | _       | DISSCK | DISSDO | MODE16 | SMP        | CKE          | SSEN        | CKP        | MSTEN  |           | SPRE<2:0>  |       | PPRE   | <1:0>  | 0000          |

| SPI2CON2 | 0264  | FRMEN  | SPIFSD | FRMPOL  | _      | _      |        | _          | _            | —           | _          | _      | _         | _          | _     | FRMDLY | SPIBEN | 0000          |

| SPI2BUF  | 0268  |        |        |         |        |        |        | SPI2 Tra   | insmit and R | eceive Buff | er Registe | r      |           |            |       |        |        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

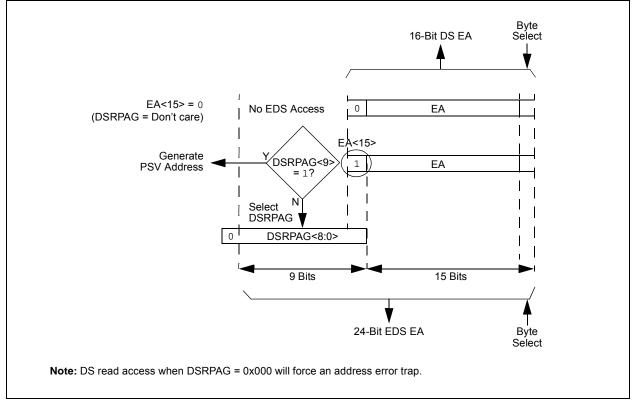

#### 4.4.1 PAGED MEMORY SCHEME

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X architecture extends the available Data Space through a paging scheme, which allows the available Data Space to be accessed using MOV instructions in a linear fashion for pre-modified and post-modified Effective Addresses (EA). The upper half of the base Data Space address is used in conjunction with the Data Space Page registers, the 10-bit Read Page register (DSRPAG) or the 9-bit Write Page register (DSWPAG), to form an Extended Data Space (EDS) address or Program Space Visibility (PSV) address. The Data Space Page registers are located in the SFR space.

Construction of the EDS address is shown in Example 4-1. When DSRPAG<9> = 0 and the base address bit, EA<15> = 1, the DSRPAG<8:0> bits are concatenated onto EA<14:0> to form the 24-bit EDS read address. Similarly, when base address bit, EA<15> = 1, DSWPAG<8:0> are concatenated onto EA<14:0> to form the 24-bit EDS write address.

## 7.0 INTERRUPT CONTROLLER

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXGP/MC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Interrupts" (DS70600) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X interrupt controller reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X CPU.

The interrupt controller has the following features:

- Up to eight processor exceptions and software traps

- Eight user-selectable priority levels

- Interrupt Vector Table (IVT) with a unique vector for each interrupt or exception source

- Fixed priority within a specified user priority level

- Fixed interrupt entry and return latencies

## 7.1 Interrupt Vector Table

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X Interrupt Vector Table (IVT), shown in Figure 7-1, resides in program memory starting at location, 000004h. The IVT contains seven non-maskable trap vectors and up to 246 sources of interrupt. In general, each interrupt source has its own vector. Each interrupt vector contains a 24-bit-wide address. The value programmed into each interrupt vector location is the starting address of the associated Interrupt Service Routine (ISR).

Interrupt vectors are prioritized in terms of their natural priority. This priority is linked to their position in the vector table. Lower addresses generally have a higher natural priority. For example, the interrupt associated with Vector 0 takes priority over interrupts at any other vector address.

## 7.2 Reset Sequence

A device Reset is not a true exception because the interrupt controller is not involved in the Reset process. The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices clear their registers in response to a Reset, which forces the PC to zero. The device then begins program execution at location, 0x000000. A GOTO instruction at the Reset address can redirect program execution to the appropriate start-up routine.

**Note:** Any unimplemented or unused vector locations in the IVT should be programmed with the address of a default interrupt handler routine that contains a RESET instruction.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

|                 | 12. 2007.00                                                                                                                        |                                                           |              |                                   |                  |          |        |  |  |  |  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|--------------|-----------------------------------|------------------|----------|--------|--|--|--|--|

| U-0             | U-0                                                                                                                                | U-0                                                       | U-0          | U-0                               | U-0              | U-0      | U-0    |  |  |  |  |

| —               | —                                                                                                                                  | —                                                         | —            | —                                 | —                | —        | —      |  |  |  |  |

| bit 15          |                                                                                                                                    |                                                           |              |                                   |                  |          | bit 8  |  |  |  |  |

|                 |                                                                                                                                    |                                                           |              |                                   |                  |          |        |  |  |  |  |

| U-0             | U-0                                                                                                                                | U-0                                                       | U-0          | R-0                               | R-0              | R-0      | R-0    |  |  |  |  |

| —               |                                                                                                                                    | —                                                         | —            | RQCOL3                            | RQCOL2           | RQCOL1   | RQCOL0 |  |  |  |  |

| bit 7           |                                                                                                                                    |                                                           |              |                                   |                  |          | bit 0  |  |  |  |  |

|                 |                                                                                                                                    |                                                           |              |                                   |                  |          |        |  |  |  |  |

| Legend:         |                                                                                                                                    |                                                           |              |                                   |                  |          |        |  |  |  |  |

| R = Readable    | bit                                                                                                                                | W = Writable                                              | bit          | U = Unimpler                      | mented bit, read | l as '0' |        |  |  |  |  |

| -n = Value at F | POR                                                                                                                                | '1' = Bit is set                                          |              | '0' = Bit is cleared x = Bit is u |                  |          | nown   |  |  |  |  |

|                 |                                                                                                                                    |                                                           |              |                                   |                  |          |        |  |  |  |  |

| bit 15-4        | Unimplemen                                                                                                                         | ted: Read as '                                            | כ'           |                                   |                  |          |        |  |  |  |  |

| bit 3           | RQCOL3: DMA Channel 3 Transfer Request Collision Flag bit                                                                          |                                                           |              |                                   |                  |          |        |  |  |  |  |

|                 |                                                                                                                                    | e and interrupt<br>est collision is d                     |              | st collision is d                 | etected          |          |        |  |  |  |  |

| <b>h</b> # 0    | •                                                                                                                                  |                                                           |              | est Callisian Fl                  | aa hit           |          |        |  |  |  |  |

| bit 2           | RQCOL2: DMA Channel 2 Transfer Request Collision Flag bit                                                                          |                                                           |              |                                   |                  |          |        |  |  |  |  |

|                 | <ul> <li>1 = User force and interrupt-based request collision is detected</li> <li>0 = No request collision is detected</li> </ul> |                                                           |              |                                   |                  |          |        |  |  |  |  |

| bit 1           | RQCOL1: DN                                                                                                                         | RQCOL1: DMA Channel 1 Transfer Request Collision Flag bit |              |                                   |                  |          |        |  |  |  |  |

|                 | 1 = User force and interrupt-based request collision is detected                                                                   |                                                           |              |                                   |                  |          |        |  |  |  |  |

|                 | 0 = No reque                                                                                                                       | est collision is d                                        | etected      |                                   |                  |          |        |  |  |  |  |

| bit 0           | RQCOLO: DN                                                                                                                         | /IA Channel 0 T                                           | ransfer Requ | est Collision F                   | lag bit          |          |        |  |  |  |  |

|                 | 1 = User force                                                                                                                     | e and interrupt                                           | -based reque | st collision is d                 | etected          |          |        |  |  |  |  |

#### REGISTER 8-12: DMARQC: DMA REQUEST COLLISION STATUS REGISTER

0 = No request collision is detected

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0    | U-0   | U-0   | U-0   | U-0        | U-0   | U-0   | U-0   |

|--------|-------|-------|-------|------------|-------|-------|-------|

| —      | —     |       |       | —          | —     | —     | —     |

| bit 15 |       |       |       |            |       |       | bit 8 |

|        |       |       |       |            |       |       |       |

| U-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

| —      |       |       |       | U1RXR<6:0> | >     |       |       |

| bit 7  |       |       |       |            |       |       | bit 0 |

|        |       |       |       |            |       |       |       |

#### REGISTER 11-10: RPINR18: PERIPHERAL PIN SELECT INPUT REGISTER 18

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-7 Unimplemented: Read as '0' bit 6-0 U1RXR<6:0>: Assign UART1 Receive (U1RX) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) 1111001 = Input tied to RPI121 . . . . . . . . . .

#### REGISTER 11-11: RPINR19: PERIPHERAL PIN SELECT INPUT REGISTER 19

| U-0     | U-0   | U-0   | U-0   | U-0        | U-0   | U-0   | U-0   |

|---------|-------|-------|-------|------------|-------|-------|-------|

| 0-0     | 0-0   | 0-0   | 0-0   | 0-0        | 0-0   | 0-0   | 0-0   |

|         | —     |       | _     | _          | —     | —     |       |

| bit 15  |       |       |       |            |       |       | bit 8 |

|         |       |       |       |            |       |       |       |

| U-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

| —       |       |       |       | U2RXR<6:0> | >     |       |       |

| bit 7   |       |       |       |            |       |       | bit 0 |

|         |       |       |       |            |       |       |       |

| Legend: |       |       |       |            |       |       |       |

|         |       |       |       |            |       |       |       |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

|-------------------|------------------|----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-7 Unimplemented: Read as '0'

<sup>0000000 =</sup> Input tied to Vss

#### 20.1 UART Helpful Tips

- 1. In multi-node, direct-connect UART networks, receive inputs UART react to the complementary logic level defined by the URXINV bit (UxMODE<4>), which defines the Idle state, the default of which is logic high (i.e., URXINV = 0). Because remote devices do not initialize at the same time, it is likely that one of the devices, because the RX line is floating, will trigger a Start bit detection and will cause the first byte received, after the device has been initialized, to be invalid. To avoid this situation, the user should use a pull-up or pull-down resistor on the RX pin depending on the value of the URXINV bit.

- a) If URXINV = 0, use a pull-up resistor on the RX pin.

- b) If URXINV = 1, use a pull-down resistor on the RX pin.

- 2. The first character received on a wake-up from Sleep mode caused by activity on the UxRX pin of the UARTx module will be invalid. In Sleep mode, peripheral clocks are disabled. By the time the oscillator system has restarted and stabilized from Sleep mode, the baud rate bit sampling clock, relative to the incoming UxRX bit timing, is no longer synchronized, resulting in the first character being invalid; this is to be expected.

#### 20.2 UART Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter |

|-------|--------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                            |

|       | http://www.microchip.com/wwwproducts/                                                |

|       | Devices.aspx?dDocName=en555464                                                       |

#### 20.2.1 KEY RESOURCES

- "UART" (DS70582) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

#### REGISTER 21-13: CxBUFPNT2: ECANx FILTER 4-7 BUFFER POINTER REGISTER 2

| R/W-0                              |       |              |                                         |                                    |       |       |       |  |  |

|------------------------------------|-------|--------------|-----------------------------------------|------------------------------------|-------|-------|-------|--|--|

|                                    | R/W-0 | R/W-0        | R/W-0                                   | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |  |

|                                    | F7BF  | °<3:0>       |                                         | F6BP<3:0>                          |       |       |       |  |  |

| bit 15                             |       |              |                                         |                                    |       |       | bit 8 |  |  |

| R/W-0                              | R/W-0 | R/W-0        | R/W-0                                   | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |  |

|                                    | F5BF  | °<3:0>       |                                         | F4BP<3:0>                          |       |       |       |  |  |

| bit 7                              |       |              |                                         |                                    |       |       | bit 0 |  |  |

| Legend:                            |       |              |                                         |                                    |       |       |       |  |  |

| R = Readable bi                    | t     | W = Writable | bit                                     | U = Unimplemented bit, read as '0' |       |       |       |  |  |

| -n = Value at POR '1' = Bit is set |       |              | '0' = Bit is cleared x = Bit is unknown |                                    |       |       |       |  |  |

|          | 1110 = Filter hits received in RX Buffer 14                              |

|----------|--------------------------------------------------------------------------|

|          |                                                                          |

|          | •                                                                        |

|          | 0001 = Filter hits received in RX Buffer 1                               |

|          | 0000 = Filter hits received in RX Buffer 0                               |

| bit 11-8 | F6BP<3:0>: RX Buffer Mask for Filter 6 bits (same values as bits<15:12>) |

| bit 7-4  | F5BP<3:0>: RX Buffer Mask for Filter 5 bits (same values as bits<15:12>) |

| bit 3-0  | F4BP<3:0>: RX Buffer Mask for Filter 4 bits (same values as bits<15:12>) |

#### REGISTER 21-14: CxBUFPNT3: ECANx FILTER 8-11 BUFFER POINTER REGISTER 3

| R/W-0         | R/W-0                                              | R/W-0                                                                                         | R/W-0                                          | R/W-0            | R/W-0           | R/W-0           | R/W-0 |  |  |

|---------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------|------------------------------------------------|------------------|-----------------|-----------------|-------|--|--|

|               | F11BF                                              | P<3:0>                                                                                        |                                                | F10BP<3:0>       |                 |                 |       |  |  |

| bit 15        |                                                    |                                                                                               |                                                |                  |                 |                 | bit 8 |  |  |

| R/W-0         | R/W-0                                              | R/W-0                                                                                         | R/W-0                                          | R/W-0            | R/W-0           | R/W-0           | R/W-0 |  |  |

|               | F9BP                                               | 2<3:0>                                                                                        |                                                | F8BP<3:0>        |                 |                 |       |  |  |

| bit 7         |                                                    |                                                                                               |                                                |                  |                 |                 | bit 0 |  |  |

| Legend:       |                                                    |                                                                                               |                                                |                  |                 |                 |       |  |  |

| R = Readabl   | R = Readable bit W = Writable bit                  |                                                                                               |                                                | U = Unimplen     | nented bit, rea | d as '0'        |       |  |  |

| -n = Value at | t POR                                              | '1' = Bit is set                                                                              |                                                | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |  |  |

| bit 15-12     | 1111 = Filter<br>1110 = Filter<br>•<br>•<br>•<br>• | RX Buffer Mar<br>hits received ir<br>hits received ir<br>hits received ir<br>hits received ir | n RX FIFO bu<br>n RX Buffer 1<br>n RX Buffer 1 | iffer<br>4       |                 |                 |       |  |  |

| bit 11-8      | F10BP<3:0>                                         | : RX Buffer Ma                                                                                | sk for Filter 1                                | 0 bits (same val | ues as bits<1   | 5:12>)          |       |  |  |

| bit 7-4       | F9BP<3:0>:                                         | RX Buffer Mas                                                                                 | k for Filter 9 b                               | oits (same value | s as bits<15:1  | 2>)             |       |  |  |

| bit 3-0       | F8BP<3:0>:                                         | RX Buffer Mas                                                                                 | k for Filter 8 k                               | oits (same value | s as bits<15:1  | 2>)             |       |  |  |

|               |                                                    |                                                                                               |                                                |                  |                 |                 |       |  |  |

© 2011-2013 Microchip Technology Inc.

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| RXOVF15 | RXOVF14 | RXOVF13 | RXOVF12 | RXOVF11 | RXOVF10 | RXOVF9 | RXOVF8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

|         |         |         |         |         |         |        |        |

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

#### REGISTER 21-24: CxRXOVF1: ECANx RECEIVE BUFFER OVERFLOW REGISTER 1

| RXOVF7                                                                | RXOVF6 | RXOVF5 | RXOVF4 | RXOVF3 | RXOVF2 | RXOVF1 | RXOVF0 |

|-----------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|--------|

| bit 7                                                                 |        |        |        |        |        |        | bit 0  |

|                                                                       |        |        |        |        |        |        |        |

| Legend:C = Writable bit, but only '0' can be written to clear the bit |        |        |        |        |        |        |        |

| Legend:           | C = Writable bit, but only '0' | can be written to clear the bit |                    |

|-------------------|--------------------------------|---------------------------------|--------------------|

| R = Readable bit  | W = Writable bit               | U = Unimplemented bit, read     | l as '0'           |

| -n = Value at POR | '1' = Bit is set               | '0' = Bit is cleared            | x = Bit is unknown |

bit 15-0 RXOVF<15:0>: Receive Buffer n Overflow bits

1 = Module attempted to write to a full buffer (set by module)

0 = No overflow condition (cleared by user software)

#### REGISTER 21-25: CxRXOVF2: ECANx RECEIVE BUFFER OVERFLOW REGISTER 2

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXOVF31 | RXOVF30 | RXOVF29 | RXOVF28 | RXOVF27 | RXOVF26 | RXOVF25 | RXOVF24 |

| bit 15  |         |         |         |         |         |         | bit 8   |

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXOVF23 | RXOVF22 | RXOVF21 | RXOVF20 | RXOVF19 | RXOVF18 | RXOVF17 | RXOVF16 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           | C = Writable bit, but or | C = Writable bit, but only '0' can be written to clear the bit |                                    |  |  |  |  |

|-------------------|--------------------------|----------------------------------------------------------------|------------------------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit         | U = Unimplemented bit                                          | U = Unimplemented bit, read as '0' |  |  |  |  |

| -n = Value at POR | '1' = Bit is set         | '0' = Bit is cleared                                           | x = Bit is unknown                 |  |  |  |  |

bit 15-0 RXOVF<31:16>: Receive Buffer n Overflow bits

1 = Module attempted to write to a full buffer (set by module)

0 = No overflow condition (cleared by user software)

## 23.0 10-BIT/12-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

- **Note 1:** This data sheet summarizes the features of the dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. То complement the information in this data sheet. refer to "Analog-to-Digital Converter (ADC)" (DS70621) in the "dsPIC33/PIC24 Family Reference Manual', which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices have one ADC module. The ADC module supports up to 16 analog input channels.

On ADC1, the AD12B bit (AD1CON1<10>) allows the ADC module to be configured by the user as either a 10-bit, 4 Sample-and-Hold (S&H) ADC (default configuration) or a 12-bit, 1 S&H ADC.

Note: The ADC module needs to be disabled before modifying the AD12B bit.

## 23.1 Key Features

#### 23.1.1 10-BIT ADC CONFIGURATION

The 10-bit ADC configuration has the following key features:

- Successive Approximation (SAR) conversion

- · Conversion speeds of up to 1.1 Msps

- · Up to 16 analog input pins

- Connections to three internal op amps

- Connections to the Charge Time Measurement Unit (CTMU) and temperature measurement diode

- Channel selection and triggering can be controlled by the Peripheral Trigger Generator (PTG)

- External voltage reference input pins

- · Simultaneous sampling of:

- Up to four analog input pins

- Three op amp outputs

- Combinations of analog inputs and op amp outputs

- Automatic Channel Scan mode

- Selectable conversion Trigger source

- · Selectable Buffer Fill modes

- Four result alignment options (signed/unsigned, fractional/integer)

- Operation during CPU Sleep and Idle modes

#### 23.1.2 12-BIT ADC CONFIGURATION

The 12-bit ADC configuration supports all the features listed above, with the exception of the following:

- In the 12-bit configuration, conversion speeds of up to 500 ksps are supported

- There is only one S&H amplifier in the 12-bit configuration; therefore, simultaneous sampling of multiple channels is not supported.

Depending on the particular device pinout, the ADC can have up to 16 analog input pins, designated AN0 through AN15. These analog inputs are shared with op amp inputs and outputs, comparator inputs, and external voltage references. When op amp/comparator functionality is enabled, or an external voltage reference is used, the analog input that shares that pin is no longer available. The actual number of analog input pins, op amps and external voltage reference input configuration depends on the specific device.

A block diagram of the ADC module is shown in Figure 23-1. Figure 23-2 provides a diagram of the ADC conversion clock period.

## 23.2 ADC Helpful Tips

- 1. The SMPIx control bits in the AD1CON2 register:

- a) Determine when the ADC interrupt flag is set and an interrupt is generated, if enabled.

- b) When the CSCNA bit in the AD1CON2 registers is set to '1', this determines when the ADC analog scan channel list, defined in the AD1CSSL/AD1CSSH registers, starts over from the beginning.

- c) When the DMA peripheral is not used (ADDMAEN = 0), this determines when the ADC Result Buffer Pointer to ADC1BUF0-ADC1BUFF gets reset back to the beginning at ADC1BUF0.

- d) When the DMA peripheral is used (ADDMAEN = 1), this determines when the DMA Address Pointer is incremented after a sample/conversion operation. ADC1BUF0 is the only ADC buffer used in this mode. The ADC Result Buffer Pointer to ADC1BUF0-ADC1BUFF gets reset back to the beginning at ADC1BUF0. The DMA address is incremented after completion of every 32nd sample/conversion operation. Conversion results are stored in the ADC1BUF0 register for transfer to RAM using DMA.

- 2. When the DMA module is disabled (ADDMAEN = 0), the ADC has 16 result buffers. ADC conversion results are stored sequentially in ADC1BUF0-ADC1BUFF, regardless of which analog inputs are being used subject to the SMPIx bits and the condition described in 1c) above. There is no relationship between the ANx input being measured and which ADC buffer (ADC1BUF0-ADC1BUFF) that the conversion results will be placed in.

- 3. When the DMA module is enabled (ADDMAEN = 1), the ADC module has only 1 ADC result buffer (i.e., ADC1BUF0) per ADC peripheral and the ADC conversion result must be read, either by the CPU or DMA Controller, before the next ADC conversion is complete to avoid overwriting the previous value.

- 4. The DONE bit (AD1CON1<0>) is only cleared at the start of each conversion and is set at the completion of the conversion, but remains set indefinitely, even through the next sample phase until the next conversion begins. If application code is monitoring the DONE bit in any kind of software loop, the user must consider this behavior because the CPU code execution is faster than the ADC. As a result, in Manual Sample mode, particularly where the user's code is setting the SAMP bit (AD1CON1<1>), the DONE bit should also be cleared by the user application just before setting the SAMP bit.

5. Enabling op amps, comparator inputs and external voltage references can limit the availability of analog inputs (ANx pins). For example, when Op Amp 2 is enabled, the pins for ANO, AN1 and AN2 are used by the op amp's inputs and output. This negates the usefulness of Alternate Input mode since the MUXA selections use AN0-AN2. Carefully study the ADC block diagram to determine the configuration that will best suit your application. Configuration examples are available in the "Analog-to-Digital Converter (ADC)" (DS70621) section in the "dsPIC33/ PIC24 Family Reference Manual".

#### 23.3 ADC Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser:<br>http://www.microchip.com/wwwproducts/ |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | Devices.aspx?dDocName=en555464                                                                                                                          |

#### 23.3.1 KEY RESOURCES

- "Analog-to-Digital Converter (ADC)" (DS70621) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

#### REGISTER 23-1: AD1CON1: ADC1 CONTROL REGISTER 1 (CONTINUED)

| bit 7-5 | SSRC<2:0>: Sample Trigger Source Select bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | If SSRCG = 1:<br>111 = Reserved<br>110 = PTGO15 primary trigger compare ends sampling and starts conversion <sup>(1)</sup><br>101 = PTGO14 primary trigger compare ends sampling and starts conversion <sup>(1)</sup><br>100 = PTGO13 primary trigger compare ends sampling and starts conversion <sup>(1)</sup><br>011 = PTGO12 primary trigger compare ends sampling and starts conversion <sup>(1)</sup><br>010 = PWM Generator 3 primary trigger compare ends sampling and starts conversion <sup>(2)</sup><br>001 = PWM Generator 2 primary trigger compare ends sampling and starts conversion <sup>(2)</sup><br>000 = PWM Generator 1 primary trigger compare ends sampling and starts conversion <sup>(2)</sup> |

|         | If SSRCG = 0:<br>111 = Internal counter ends sampling and starts conversion (auto-convert)<br>110 = CTMU ends sampling and starts conversion<br>101 = Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         | <ul> <li>101 - Reserved</li> <li>100 = Timer5 compare ends sampling and starts conversion</li> <li>011 = PWM primary Special Event Trigger ends sampling and starts conversion</li> <li>010 = Timer3 compare ends sampling and starts conversion</li> <li>001 = Active transition on the INT0 pin ends sampling and starts conversion</li> <li>000 = Clearing the Sample bit (SAMP) ends sampling and starts conversion (Manual mode)</li> </ul>                                                                                                                                                                                                                                                                        |

| bit 4   | SSRCG: Sample Trigger Source Group bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|         | See SSRC<2:0> for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| bit 3   | <ul> <li>SIMSAM: Simultaneous Sample Select bit (only applicable when CHPS&lt;1:0&gt; = 01 or 1x)</li> <li><u>In 12-bit mode (AD21B = 1), SIMSAM is Unimplemented and is Read as '0':</u></li> <li>1 = Samples CH0, CH1, CH2, CH3 simultaneously (when CHPS&lt;1:0&gt; = 1x); or samples CH0 and CH1 simultaneously (when CHPS&lt;1:0&gt; = 01)</li> <li>0 = Samples multiple channels individually in sequence</li> </ul>                                                                                                                                                                                                                                                                                              |

| bit 2   | ASAM: ADC1 Sample Auto-Start bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|         | <ul> <li>1 = Sampling begins immediately after the last conversion; SAMP bit is auto-set</li> <li>0 = Sampling begins when the SAMP bit is set</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| bit 1   | SAMP: ADC1 Sample Enable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|         | <ul> <li>1 = ADC Sample-and-Hold amplifiers are sampling</li> <li>0 = ADC Sample-and-Hold amplifiers are holding</li> <li>If ASAM = 0, software can write '1' to begin sampling. Automatically set by hardware if ASAM = 1. If SSRC&lt;2:0&gt; = 000, software can write '0' to end sampling and start conversion. If SSRC&lt;2:0&gt; ≠ 000, automatically cleared by hardware to end sampling and start conversion.</li> </ul>                                                                                                                                                                                                                                                                                         |

| bit 0   | DONE: ADC1 Conversion Status bit <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|         | <ul> <li>1 = ADC conversion cycle has completed</li> <li>0 = ADC conversion has not started or is in progress</li> <li>Automatically set by hardware when the ADC conversion is complete. Software can write '0' to clear the DONE status bit (software is not allowed to write '1'). Clearing this bit does NOT affect any operation in progress. Automatically cleared by hardware at the start of a new conversion.</li> </ul>                                                                                                                                                                                                                                                                                       |

| Note 1: | See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for information on this selection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

- 2: This setting is available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

- **3:** Do not clear the DONE bit in software if Auto-Sample is enabled (ASAM = 1).

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

## REGISTER 24-4: PTGT0LIM: PTG TIMER0 LIMIT REGISTER<sup>(1)</sup>

| R/W-0                             | R/W-0 | R/W-0            | R/W-0                              | R/W-0                                  | R/W-0    | R/W-0 | R/W-0 |

|-----------------------------------|-------|------------------|------------------------------------|----------------------------------------|----------|-------|-------|

|                                   |       |                  | PTGT0                              | _IM<15:8>                              |          |       |       |

| bit 15                            |       |                  |                                    |                                        |          |       | bit 8 |

|                                   |       |                  |                                    |                                        |          |       |       |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0                              | R/W-0                                  | R/W-0    | R/W-0 | R/W-0 |

|                                   |       |                  | PTGT0                              | LIM<7:0>                               |          |       |       |

| bit 7                             |       |                  |                                    |                                        |          |       | bit 0 |

|                                   |       |                  |                                    |                                        |          |       |       |

| Legend:                           |       |                  |                                    |                                        |          |       |       |

| R = Readable bit W = Writable bit |       | bit              | U = Unimplemented bit, read as '0' |                                        | d as '0' |       |       |

| -n = Value at P                   | POR   | '1' = Bit is set |                                    | '0' = Bit is cleared x = Bit is unknow |          | nown  |       |

#### bit 15-0 **PTGT0LIM<15:0>:** PTG Timer0 Limit Register bits General Purpose Timer0 Limit register (effective only with a PTGT0 Step command).

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

## REGISTER 24-5: PTGT1LIM: PTG TIMER1 LIMIT REGISTER<sup>(1)</sup>

| R/W-0          | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|----------------|-------|-------|-------|-------|-------|-------|-------|--|--|--|

| PTGT1LIM<15:8> |       |       |       |       |       |       |       |  |  |  |

| bit 15         |       |       |       |       |       |       | bit 8 |  |  |  |

|                |       |       |       |       |       |       |       |  |  |  |

| R/W-0 | R/W-0         | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |  |  |

|-------|---------------|-------|-------|-------|-------|-------|-------|--|--|--|--|--|

|       | PTGT1LIM<7:0> |       |       |       |       |       |       |  |  |  |  |  |

| bit 7 |               |       |       |       |       |       | bit 0 |  |  |  |  |  |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-0 **PTGT1LIM<15:0>:** PTG Timer1 Limit Register bits

General Purpose Timer1 Limit register (effective only with a PTGT1 Step command).

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

| R/W-0         | R/W-0                             | R/W-0                                                      | U-0                 | U-0              | R/W-0            | R/W-0               | R/W-0               |  |  |  |  |

|---------------|-----------------------------------|------------------------------------------------------------|---------------------|------------------|------------------|---------------------|---------------------|--|--|--|--|

| CON           | COE <sup>(2)</sup>                | CPOL                                                       | _                   | —                | OPMODE           | CEVT                | COUT                |  |  |  |  |

| bit 15        |                                   |                                                            |                     |                  |                  |                     | bit 8               |  |  |  |  |

|               |                                   |                                                            |                     |                  |                  |                     |                     |  |  |  |  |

| R/W-0         | R/W-0                             | U-0                                                        | R/W-0               | U-0              | U-0              | R/W-0               | R/W-0               |  |  |  |  |

| EVPOL1        | EVPOL0                            | —                                                          | CREF <sup>(1)</sup> | _                | —                | CCH1 <sup>(1)</sup> | CCH0 <sup>(1)</sup> |  |  |  |  |

| bit 7         |                                   |                                                            |                     |                  |                  |                     | bit (               |  |  |  |  |

| Legend:       |                                   |                                                            |                     |                  |                  |                     |                     |  |  |  |  |

| R = Readabl   | e bit                             | W = Writable                                               | bit                 | U = Unimple      | mented bit, read | as '0'              |                     |  |  |  |  |

| -n = Value at | POR                               | '1' = Bit is set                                           |                     | '0' = Bit is cle | eared            | x = Bit is unkr     | nown                |  |  |  |  |

|               |                                   |                                                            |                     |                  |                  |                     |                     |  |  |  |  |

| bit 15        | CON: Op Am                        | p/Comparator                                               | Enable bit          |                  |                  |                     |                     |  |  |  |  |

|               |                                   | comparator is e                                            |                     |                  |                  |                     |                     |  |  |  |  |

|               |                                   | comparator is d                                            |                     |                  |                  |                     |                     |  |  |  |  |

| bit 14        |                                   | arator Output Ei                                           |                     |                  |                  |                     |                     |  |  |  |  |

|               |                                   | tor output is pre                                          |                     | CxOUT pin        |                  |                     |                     |  |  |  |  |

|               | -                                 | tor output is int                                          | -                   |                  |                  |                     |                     |  |  |  |  |

| bit 13        | •                                 | CPOL: Comparator Output Polarity Select bit                |                     |                  |                  |                     |                     |  |  |  |  |

|               | 1 = Comparator output is inverted |                                                            |                     |                  |                  |                     |                     |  |  |  |  |

|               | -                                 | tor output is no                                           |                     |                  |                  |                     |                     |  |  |  |  |

| bit 12-11     | •                                 | ted: Read as '                                             |                     |                  |                  |                     |                     |  |  |  |  |

| bit 10        |                                   | <b>DPMODE:</b> Op Amp/Comparator Operation Mode Select bit |                     |                  |                  |                     |                     |  |  |  |  |

|               |                                   | perates as an o<br>perates as a co                         |                     |                  |                  |                     |                     |  |  |  |  |

| bit 9         | •                                 | arator Event bi                                            | •                   |                  |                  |                     |                     |  |  |  |  |

|               | 1 = Compara                       |                                                            | rding to the E      | VPOL<1:0> s      | ettings occurred | ; disables futur    | e triggers and      |  |  |  |  |

|               |                                   | ator event did n                                           |                     |                  |                  |                     |                     |  |  |  |  |

| bit 8         | COUT: Comp                        | parator Output b                                           | oit                 |                  |                  |                     |                     |  |  |  |  |

|               |                                   | = 0 (non-invert                                            |                     |                  |                  |                     |                     |  |  |  |  |

|               | 1 = VIN+ > VI                     | N-                                                         | • • • • •           |                  |                  |                     |                     |  |  |  |  |

|               | 0 = VIN + < VI                    |                                                            |                     |                  |                  |                     |                     |  |  |  |  |

|               |                                   | = 1 (inverted p                                            | olarity):           |                  |                  |                     |                     |  |  |  |  |

|               | 1 = VIN + < VI                    |                                                            |                     |                  |                  |                     |                     |  |  |  |  |

|               | 0 = VIN + > VI                    | N-                                                         |                     |                  |                  |                     |                     |  |  |  |  |

#### **REGISTER 25-2:** CMxCON: COMPARATOR x CONTROL REGISTER (x = 1, 2 OR 3)

- Note 1: Inputs that are selected and not available will be tied to Vss. See the "Pin Diagrams" section for available inputs for each package.

- 2: This output is not available when OPMODE (CMxCON<10>) = 1.

| AC CHARACTERISTICS |           |                                                                | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                     |      |       |                                                                                                             |

|--------------------|-----------|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|-------------------------------------------------------------------------------------------------------------|

| Param<br>No.       | Symbol    | Characteristic <sup>(1)</sup>                                  | Min.                                                                                                                                                                                                                                                                                    | Тур. <sup>(2)</sup> | Max. | Units | Conditions                                                                                                  |

| SY00               | Τρυ       | Power-up Period                                                | _                                                                                                                                                                                                                                                                                       | 400                 | 600  | μS    |                                                                                                             |

| SY10               | Tost      | Oscillator Start-up Time                                       |                                                                                                                                                                                                                                                                                         | 1024 Tosc           |      |       | Tosc = OSC1 period                                                                                          |

| SY12               | Twdt      | Watchdog Timer<br>Time-out Period                              | 0.81                                                                                                                                                                                                                                                                                    | 0.98                | 1.22 | ms    | WDTPRE = 0,<br>WDTPOST<3:0> = 0000, using<br>LPRC tolerances indicated in F21<br>(see Table 30-20) at +85°C |

|                    |           |                                                                | 3.26                                                                                                                                                                                                                                                                                    | 3.91                | 4.88 | ms    | WDTPRE = 1,<br>WDTPOST<3:0> = 0000, using<br>LPRC tolerances indicated in F21<br>(see Table 30-20) at +85°C |

| SY13               | Tioz      | I/O High-Impedance<br>from MCLR Low or<br>Watchdog Timer Reset | 0.68                                                                                                                                                                                                                                                                                    | 0.72                | 1.2  | μS    |                                                                                                             |

| SY20               | TMCLR     | MCLR Pulse Width (low)                                         | 2                                                                                                                                                                                                                                                                                       | _                   |      | μS    |                                                                                                             |

| SY30               | TBOR      | BOR Pulse Width (low)                                          | 1                                                                                                                                                                                                                                                                                       | _                   |      | μS    |                                                                                                             |

| SY35               | TFSCM     | Fail-Safe Clock Monitor<br>Delay                               | _                                                                                                                                                                                                                                                                                       | 500                 | 900  | μS    | -40°C to +85°C                                                                                              |

| SY36               | TVREG     | Voltage Regulator<br>Standby-to-Active mode<br>Transition Time | _                                                                                                                                                                                                                                                                                       | —                   | 30   | μS    |                                                                                                             |

| SY37               | Toscdfrc  | FRC Oscillator Start-up<br>Delay                               | 46                                                                                                                                                                                                                                                                                      | 48                  | 54   | μS    |                                                                                                             |

| SY38               | Toscdlprc | LPRC Oscillator Start-up<br>Delay                              |                                                                                                                                                                                                                                                                                         | —                   | 70   | μS    |                                                                                                             |

# TABLE 30-22:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMERTIMING REQUIREMENTS

**Note 1:** These parameters are characterized but not tested in manufacturing.

**2:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

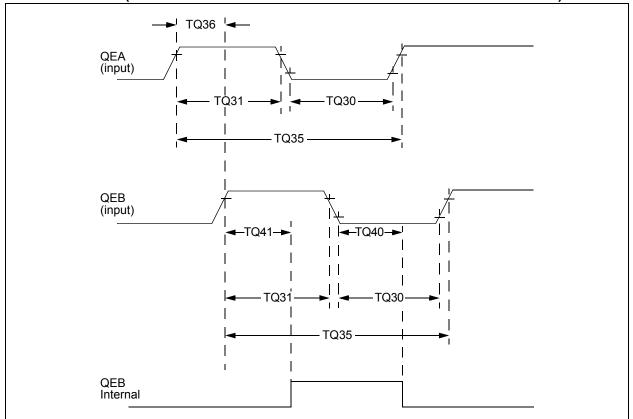

#### FIGURE 30-12: QEA/QEB INPUT CHARACTERISTICS (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

#### TABLE 30-31: QUADRATURE DECODER TIMING REQUIREMENTS (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

| AC CHARACTERISTICS |        |                                                    | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |       |                                                         |

|--------------------|--------|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|---------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>                      | Тур. <sup>(2)</sup>                                                                                                                                                                                                                                                                     | Max. | Units | Conditions                                              |

| TQ30               | TQUL   | Quadrature Input Low Time                          | 6 Tcy                                                                                                                                                                                                                                                                                   |      | ns    |                                                         |

| TQ31               | TQUH   | Quadrature Input High Time                         | 6 Tcy                                                                                                                                                                                                                                                                                   | —    | ns    |                                                         |

| TQ35               | TQUIN  | Quadrature Input Period                            | 12 TCY                                                                                                                                                                                                                                                                                  | _    | ns    |                                                         |

| TQ36               | TQUP   | Quadrature Phase Period                            | 3 TCY                                                                                                                                                                                                                                                                                   | —    | ns    |                                                         |

| TQ40               | TQUFL  | Filter Time to Recognize Low, with Digital Filter  | 3 * N * Tcy                                                                                                                                                                                                                                                                             | —    | ns    | N = 1, 2, 4, 16, 32, 64, 128<br>and 256 <b>(Note 3)</b> |

| TQ41               | TQUFH  | Filter Time to Recognize High, with Digital Filter | 3 * N * Tcy                                                                                                                                                                                                                                                                             | —    | ns    | N = 1, 2, 4, 16, 32, 64, 128<br>and 256 <b>(Note 3)</b> |

**Note 1:** These parameters are characterized but not tested in manufacturing.

**2:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

3: N = Index Channel Digital Filter Clock Divide Select bits. Refer to "Quadrature Encoder Interface (QEI)" (DS70601) in the "*dsPIC33/PIC24 Family Reference Manual*". Please see the Microchip web site for the latest family reference manual sections.

# 44-Terminal Very Thin Leadless Array Package (TL) – 6x6x0.9 mm Body With Exposed Pad [VTLA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

DETAIL A

|                         | MILLIMETERS |          |      |       |  |

|-------------------------|-------------|----------|------|-------|--|

| Dimension               | Limits      | MIN      | NOM  | MAX   |  |

| Number of Pins          | Ν           |          | 44   |       |  |

| Number of Pins per Side | ND          | 12       |      |       |  |

| Number of Pins per Side | NE          | 10       |      |       |  |

| Pitch                   | е           | 0.50 BSC |      |       |  |

| Overall Height          | Α           | 0.80     | 0.90 | 1.00  |  |

| Standoff                | A1          | 0.025    | -    | 0.075 |  |

| Overall Width           | Е           | 6.00 BSC |      |       |  |

| Exposed Pad Width       | E2          | 4.40     | 4.55 | 4.70  |  |

| Overall Length          | D           | 6.00 BSC |      |       |  |

| Exposed Pad Length      | D2          | 4.40     | 4.55 | 4.70  |  |

| Contact Width           | b           | 0.20     | 0.25 | 0.30  |  |

| Contact Length          | L           | 0.20     | 0.25 | 0.30  |  |

| Contact-to-Exposed Pad  | К           | 0.20     | -    | -     |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.