Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

⊡XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 60 MIPs                                                                       |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                    |

| Number of I/O              | 21                                                                            |

| Program Memory Size        | 32KB (10.7K x 24)                                                             |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 2K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 6x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-VQFN Exposed Pad                                                           |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep32gp202-e-mm |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| Pin Name <sup>(4)</sup>                        | Pin<br>Type         | Buffer<br>Type          | PPS              | Description                                                                                                                                                                        |

|------------------------------------------------|---------------------|-------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AN0-AN15                                       | Ι                   | Analog                  | No               | Analog input channels.                                                                                                                                                             |

| CLKI                                           | I                   | ST/<br>CMOS             | No               | External clock source input. Always associated with OSC1 pin function                                                                                                              |

| CLKO                                           | 0                   | —                       | No               | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes. Always associated with OSC2 pin function. |

| OSC1                                           | Ι                   | ST/                     | No               | Oscillator crystal input. ST buffer when configured in RC mode; CMOS                                                                                                               |

| OSC2                                           | I/O                 | CMOS<br>—               | No               | otherwise.<br>Oscillator crystal output. Connects to crystal or resonator in Crystal<br>Oscillator mode. Optionally functions as CLKO in RC and EC modes.                          |

| REFCLKO                                        | 0                   |                         | Yes              | Reference clock output.                                                                                                                                                            |

| IC1-IC4                                        | Ι                   | ST                      | Yes              | Capture Inputs 1 through 4.                                                                                                                                                        |

| OCFA<br>OCFB<br>OC1-OC4                        | <br> <br> <br>0     | ST<br>ST                | Yes<br>No<br>Yes | Compare Fault A input (for Compare channels).<br>Compare Fault B input (for Compare channels).<br>Compare Outputs 1 through 4.                                                     |

| INT0                                           | I                   | ST                      | No               | External Interrupt 0.                                                                                                                                                              |

| INT1<br>INT2                                   |                     | ST<br>ST                | Yes<br>Yes       | External Interrupt 1.<br>External Interrupt 2.                                                                                                                                     |

| RA0-RA4, RA7-RA12                              | I/O                 | ST                      | No               | PORTA is a bidirectional I/O port.                                                                                                                                                 |

| RB0-RB15                                       | I/O                 | ST                      | No               | PORTB is a bidirectional I/O port.                                                                                                                                                 |

| RC0-RC13, RC15                                 | I/O                 | ST                      | No               | PORTC is a bidirectional I/O port.                                                                                                                                                 |

| RD5, RD6, RD8                                  | I/O                 | ST                      | No               | PORTD is a bidirectional I/O port.                                                                                                                                                 |

| RE12-RE15                                      | I/O                 | ST                      | No               | PORTE is a bidirectional I/O port.                                                                                                                                                 |

| RF0, RF1                                       | I/O                 | ST                      | No               | PORTF is a bidirectional I/O port.                                                                                                                                                 |

| RG6-RG9                                        | I/O                 | ST                      | No               | PORTG is a bidirectional I/O port.                                                                                                                                                 |

| T1CK                                           | Ι                   | ST                      | No               | Timer1 external clock input.                                                                                                                                                       |

| T2CK<br>T3CK                                   |                     | ST<br>ST                | Yes              | Timer2 external clock input.                                                                                                                                                       |

| T4CK                                           |                     | ST                      | No<br>No         | Timer3 external clock input.<br>Timer4 external clock input.                                                                                                                       |

| T5CK                                           | i                   | ST                      | No               | Timer5 external clock input.                                                                                                                                                       |

| CTPLS                                          | 0                   | ST                      | No               | CTMU pulse output.                                                                                                                                                                 |

| CTED1                                          | Ι                   | ST                      | No               | CTMU External Edge Input 1.                                                                                                                                                        |

| CTED2                                          | Ι                   | ST                      | No               | CTMU External Edge Input 2.                                                                                                                                                        |

| U1CTS                                          | Ι                   | ST                      | No               | UART1 Clear-To-Send.                                                                                                                                                               |

| U1RTS                                          | 0                   |                         | No               | UART1 Ready-To-Send.                                                                                                                                                               |

| U1RX                                           |                     | ST                      | Yes              | UART1 receive.<br>UART1 transmit.                                                                                                                                                  |

| U1TX<br>BCLK1                                  | 0                   | ST                      | Yes<br>No        | UART1 Iransmit.<br>UART1 IrDA <sup>®</sup> baud clock output.                                                                                                                      |

| Legend: CMOS = CM<br>ST = Schmi<br>PPS = Perip | MOS co<br>itt Trigg | ompatible<br>er input v | input<br>with CN | or output Analog = Analog input P = Power                                                                                                                                          |

## TABLE 1-1:PINOUT I/O DESCRIPTIONS

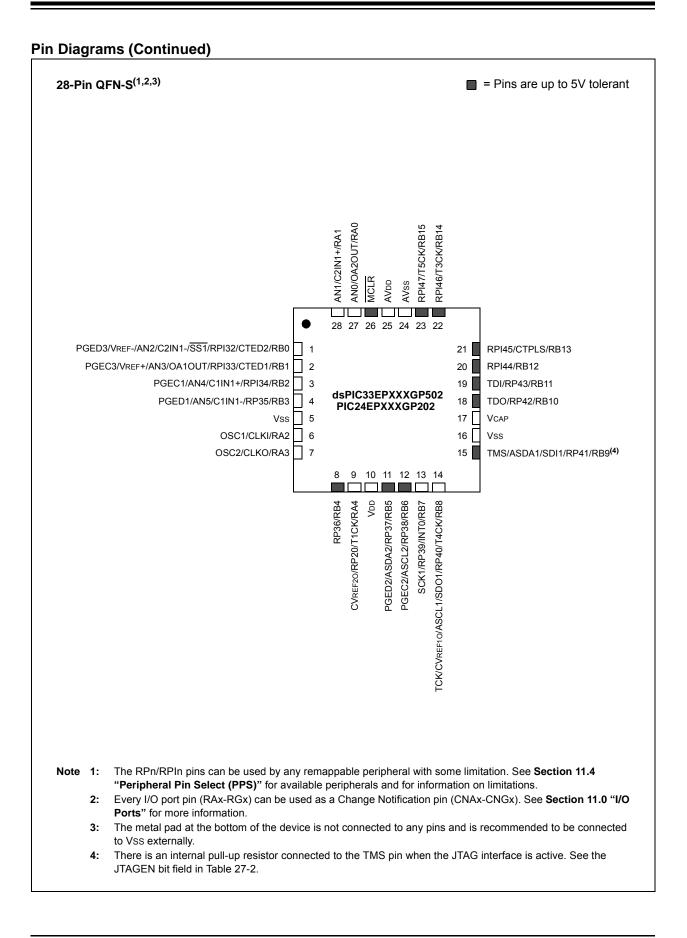

Note 1: This pin is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This pin is available on dsPIC33EPXXXGP/MC50X devices only.

3: This is the default Fault on Reset for dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices. See Section 16.0 "High-Speed PWM Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)" for more information.

4: Not all pins are available in all packages variants. See the "Pin Diagrams" section for pin availability.

**5:** There is an internal pull-up resistor connected to the TMS pin when the JTAG interface is active. See the JTAGEN bit field in Table 27-2.

## 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to 3 MHz <  $F_{IN}$  < 5.5 MHz to comply with device PLL start-up conditions. This means that if the external oscillator frequency is outside this range, the application must start-up in the FRC mode first. The default PLL settings after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV and PLLFBD, to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source. Note that clock switching must be enabled in the device Configuration Word.

## 2.8 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state.

Alternatively, connect a 1k to 10k resistor between Vss and unused pins, and drive the output to logic low.

## 2.9 Application Examples

- · Induction heating

- Uninterruptable Power Supplies (UPS)

- DC/AC inverters

- · Compressor motor control

- · Washing machine 3-phase motor control

- BLDC motor control

- · Automotive HVAC, cooling fans, fuel pumps

- Stepper motor control

- · Audio and fluid sensor monitoring

- · Camera lens focus and stability control

- Speech (playback, hands-free kits, answering machines, VoIP)

- Consumer audio

- Industrial and building control (security systems and access control)

- · Barcode reading

- Networking: LAN switches, gateways

- Data storage device management

- · Smart cards and smart card readers

Examples of typical application connections are shown in Figure 2-4 through Figure 2-8.

#### FIGURE 2-4: BOOST CONVERTER IMPLEMENTATION

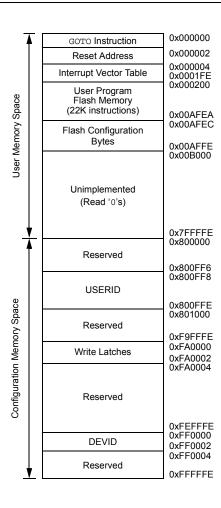

#### FIGURE 4-2: PROGRAM MEMORY MAP FOR dsPIC33EP64GP50X, dsPIC33EP64MC20X/50X AND PIC24EP64GP/MC20X DEVICES

Note: Memory areas are not shown to scale.

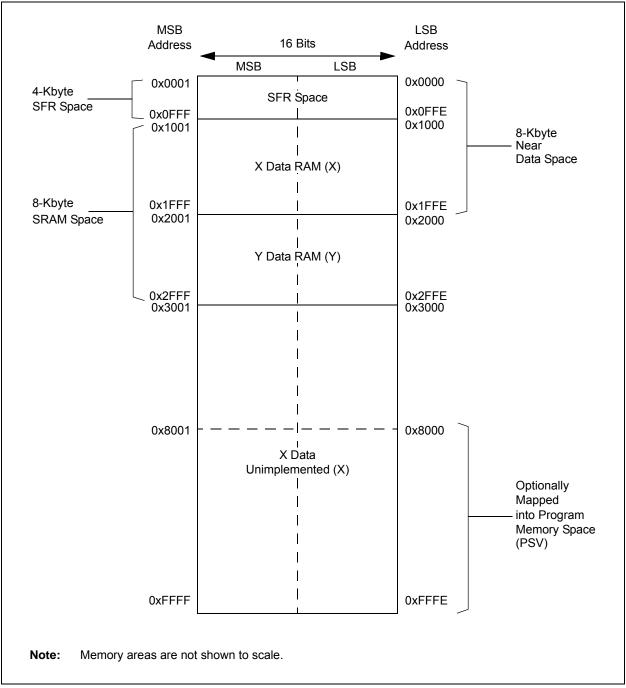

# FIGURE 4-8: DATA MEMORY MAP FOR dsPIC33EP64MC20X/50X AND dsPIC33EP64GP50X DEVICES

| IABLE        | TABLE 4-29: PERIPHERAL PIN SELECT INPUT REGISTER MAP FOR PIC24EPXXXMC20X DEVICES ONLY |        |        |              |        |            |        |       |       |       |              |       |       |            |       |       |       |               |

|--------------|---------------------------------------------------------------------------------------|--------|--------|--------------|--------|------------|--------|-------|-------|-------|--------------|-------|-------|------------|-------|-------|-------|---------------|

| File<br>Name | Addr.                                                                                 | Bit 15 | Bit 14 | Bit 13       | Bit 12 | Bit 11     | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6        | Bit 5 | Bit 4 | Bit 3      | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| RPINR0       | 06A0                                                                                  | _      |        |              |        | INT1R<6:0> |        |       |       | —     | —            | _     | _     | —          | —     | —     | _     | 0000          |

| RPINR1       | 06A2                                                                                  | _      | _      | _            | _      | _          | _      | _     | _     | _     |              |       |       | INT2R<6:0> | >     |       |       | 0000          |

| RPINR3       | 06A6                                                                                  | _      | _      | _            | _      | _          | _      | _     | _     | _     |              |       |       | T2CKR<6:0  | >     |       |       | 0000          |

| RPINR7       | 06AE                                                                                  | _      |        |              |        | IC2R<6:0>  |        | •     |       | _     |              |       |       | IC1R<6:0>  |       |       |       | 0000          |

| RPINR8       | 06B0                                                                                  | _      |        |              |        | IC4R<6:0>  |        |       |       | _     |              |       |       | IC3R<6:0>  |       |       |       | 0000          |

| RPINR11      | 06B6                                                                                  | _      |        | _            | _      | _          | _      | _     | _     | _     | – OCFAR<6:0> |       |       |            |       | 0000  |       |               |

| RPINR12      | 06B8                                                                                  | _      |        | FLT2R<6:0>   |        |            |        |       |       | _     | FLT1R<6:0>   |       |       |            | 0000  |       |       |               |

| RPINR14      | 06BC                                                                                  | _      |        |              | (      | QEB1R<6:0  | >      |       |       | _     | QEA1R<6:0>   |       |       |            |       | 0000  |       |               |

| RPINR15      | 06BE                                                                                  | _      |        |              | Н      | OME1R<6:0  | )>     |       |       | _     | INDX1R<6:0>  |       |       |            |       | 0000  |       |               |

| RPINR18      | 06C4                                                                                  | _      | _      | _            | _      | _          | _      | _     | _     | _     | U1RXR<6:0>   |       |       |            |       | 0000  |       |               |

| RPINR19      | 06C6                                                                                  | _      | _      | _            | _      | _          | _      | _     | _     | _     | U2RXR<6:0>   |       |       |            |       | 0000  |       |               |

| RPINR22      | 06CC                                                                                  |        |        |              | S      | CK2INR<6:( | )>     |       |       | _     |              |       |       | SDI2R<6:0> | >     |       |       | 0000          |

| RPINR23      | 06CE                                                                                  |        | _      | _            | _      | _          | _      | _     | _     | _     |              |       |       | SS2R<6:0>  |       |       |       | 0000          |

| RPINR26      | 06D4                                                                                  |        | _      | _            | _      | _          | _      | _     | _     | _     | _            | _     | _     | _          | _     | _     | _     | 0000          |

| RPINR37      | 06EA                                                                                  | _      |        |              | S      | YNCI1R<6:0 | )>     |       |       | _     | _            | —     | —     | —          | _     | _     | —     | 0000          |

| RPINR38      | 06EC                                                                                  | _      |        | DTCMP1R<6:0> |        |            |        |       |       | _     | _            | —     | —     | —          | _     | _     | —     | 0000          |

| RPINR39      | 06EE                                                                                  | _      |        |              | D      | FCMP3R<6:  | 0>     |       |       | -     |              |       | D     | TCMP2R<6:  | :0>   |       |       | 0000          |

#### TABLE 4-29: PERIPHERAL PIN SELECT INPUT REGISTER MAP FOR PIC24EPXXXMC20X DEVICES ONLY

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-30: PERIPHERAL PIN SELECT INPUT REGISTER MAP FOR PIC24EPXXXGP20X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14       | Bit 13     | Bit 12 | Bit 11    | Bit 10 | Bit 9 | Bit 8      | Bit 7 | Bit 6        | Bit 5 | Bit 4 | Bit 3     | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------------|------------|--------|-----------|--------|-------|------------|-------|--------------|-------|-------|-----------|-------|-------|-------|---------------|

| RPINR0       | 06A0  | —      |              | INT1R<6:0> |        |           |        |       |            | _     | —            | —     | —     | —         | _     | —     | _     | 0000          |

| RPINR1       | 06A2  | _      | _            | _          | _      | _         | _      | _     | _          | _     | – INT2R<6:0> |       |       |           |       |       | 0000  |               |

| RPINR3       | 06A6  | _      | _            | _          | _      | _         | _      | _     | _          | _     | T2CKR<6:0>   |       |       |           | 0000  |       |       |               |

| RPINR7       | 06AE  | _      |              | IC2R<6:0>  |        |           |        |       |            | _     | IC1R<6:0>    |       |       |           |       | 0000  |       |               |

| RPINR8       | 06B0  | _      |              |            |        | IC4R<6:0> |        |       |            | _     | IC3R<6:0>    |       |       |           |       |       | 0000  |               |

| RPINR11      | 06B6  | _      | _            | _          | _      | _         | _      | _     | _          | _     |              |       | (     | DCFAR<6:0 | >     |       |       | 0000          |

| RPINR18      | 06C4  | _      | _            | _          | _      | _         | _      | _     | _          | _     |              |       | ι     | J1RXR<6:0 | >     |       |       | 0000          |

| RPINR19      | 06C6  | _      | _            | _          | _      | _         | _      | _     | _          | _     | U2RXR<6:0>   |       |       |           | 0000  |       |       |               |

| RPINR22      | 06CC  | —      | SCK2INR<6:0> |            |        |           |        | _     | SDI2R<6:0> |       |              |       |       | 0000      |       |       |       |               |

| RPINR23      | 06CE  | _      | _            | —          | —      | —         | —      | —     | —          | _     |              |       |       | SS2R<6:0> |       |       |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### 4.5 Instruction Addressing Modes

The addressing modes shown in Table 4-63 form the basis of the addressing modes optimized to support the specific features of individual instructions. The addressing modes provided in the MAC class of instructions differ from those in the other instruction types.

## 4.5.1 FILE REGISTER INSTRUCTIONS

Most file register instructions use a 13-bit address field (f) to directly address data present in the first 8192 bytes of data memory (Near Data Space). Most file register instructions employ a working register, W0, which is denoted as WREG in these instructions. The destination is typically either the same file register or WREG (with the exception of the MUL instruction), which writes the result to a register or register pair. The MOV instruction allows additional flexibility and can access the entire Data Space.

#### 4.5.2 MCU INSTRUCTIONS

The three-operand MCU instructions are of the form:

Operand 3 = Operand 1 <function> Operand 2

where Operand 1 is always a working register (that is, the addressing mode can only be Register Direct), which is referred to as Wb. Operand 2 can be a W register fetched from data memory or a 5-bit literal. The result location can either be a W register or a data memory location. The following addressing modes are supported by MCU instructions:

- Register Direct

- · Register Indirect

- · Register Indirect Post-Modified

- Register Indirect Pre-Modified

- 5-Bit or 10-Bit Literal

- Note: Not all instructions support all the addressing modes given above. Individual instructions can support different subsets of these addressing modes.

#### TABLE 4-63: FUNDAMENTAL ADDRESSING MODES SUPPORTED

| Addressing Mode                                           | Description                                                                                           |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| File Register Direct                                      | The address of the file register is specified explicitly.                                             |

| Register Direct                                           | The contents of a register are accessed directly.                                                     |

| Register Indirect                                         | The contents of Wn form the Effective Address (EA).                                                   |

| Register Indirect Post-Modified                           | The contents of Wn form the EA. Wn is post-modified (incremented or decremented) by a constant value. |

| Register Indirect Pre-Modified                            | Wn is pre-modified (incremented or decremented) by a signed constant value to form the EA.            |

| Register Indirect with Register Offset (Register Indexed) | The sum of Wn and Wb forms the EA.                                                                    |

| Register Indirect with Literal Offset                     | The sum of Wn and a literal forms the EA.                                                             |

| R/W-0         | R/W-0                                                                                                | R/W-0                                                 | R/W-0   | R/W-0             | R/W-0                 | R/W-0                | U-0   |

|---------------|------------------------------------------------------------------------------------------------------|-------------------------------------------------------|---------|-------------------|-----------------------|----------------------|-------|

| T5MD          | T4MD                                                                                                 | T3MD                                                  | T2MD    | T1MD              | QEI1MD <sup>(1)</sup> | PWMMD <sup>(1)</sup> | _     |

| bit 15        |                                                                                                      |                                                       |         |                   |                       |                      | bit   |

|               |                                                                                                      |                                                       |         |                   |                       |                      |       |

| R/W-0         | R/W-0                                                                                                | R/W-0                                                 | R/W-0   | R/W-0             | U-0                   | R/W-0                | R/W-0 |

| I2C1MD        | U2MD                                                                                                 | U1MD                                                  | SPI2MD  | SPI1MD            | —                     | C1MD <sup>(2)</sup>  | AD1MD |

| bit 7         |                                                                                                      |                                                       |         |                   |                       |                      | bit   |

| Legend:       |                                                                                                      |                                                       |         |                   |                       |                      |       |

| R = Readabl   | e bit                                                                                                | W = Writable                                          | bit     | U = Unimplen      | nented bit, read      | d as '0'             |       |

| -n = Value at | POR                                                                                                  | '1' = Bit is set                                      |         | '0' = Bit is clea | ared                  | x = Bit is unkno     | own   |

| bit 15        | 1 = Timer5 m                                                                                         | 5 Module Disal<br>odule is disable<br>odule is enable | ed      |                   |                       |                      |       |

| bit 14        | 1 = Timer4 m                                                                                         | 4 Module Disal<br>odule is disable<br>odule is enable | ed      |                   |                       |                      |       |

| bit 13        | 1 = Timer3 m                                                                                         | 3 Module Disal<br>odule is disable<br>odule is enable | ed      |                   |                       |                      |       |

| bit 12        | 1 = Timer2 m                                                                                         | 2 Module Disal<br>odule is disable<br>odule is enable | ed      |                   |                       |                      |       |

| bit 11        | 1 = Timer1 m                                                                                         | 1 Module Disal<br>odule is disable<br>odule is enable | ed      |                   |                       |                      |       |

| bit 10        | 1 = QEI1 mod                                                                                         | 11 Module Disa<br>Iule is disablec<br>Iule is enabled |         |                   |                       |                      |       |

| bit 9         | 1 = PWM mod                                                                                          | /M Module Dis<br>dule is disabled<br>dule is enabled  | 1       |                   |                       |                      |       |

| bit 8         | Unimplemen                                                                                           | ted: Read as '                                        | כי      |                   |                       |                      |       |

| bit 7         | 1 = I2C1 mod                                                                                         | 1 Module Disal<br>ule is disabled<br>ule is enabled   | ble bit |                   |                       |                      |       |

| bit 6         | <b>U2MD:</b> UART2 Module Disable bit<br>1 = UART2 module is disabled<br>0 = UART2 module is enabled |                                                       |         |                   |                       |                      |       |

| bit 5         | 1 = UART1 m                                                                                          | 1 Module Disa<br>odule is disabl<br>odule is enable   | ed      |                   |                       |                      |       |

| bit 4         | 1 = SPI2 mod                                                                                         | 2 Module Disa<br>lule is disabled<br>lule is enabled  | ole bit |                   |                       |                      |       |

## REGISTER 10-1: PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1

Note 1: This bit is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This bit is available on dsPIC33EPXXXGP50X and dsPIC33EPXXXMC50X devices only.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0      | U-0   | U-0   | U-0   | U-0       | U-0   | U-0   | U-0   |

|----------|-------|-------|-------|-----------|-------|-------|-------|

| —        | —     | —     | —     | —         | —     | —     | —     |

| bit 15   |       |       |       |           |       |       | bit 8 |

|          |       |       |       |           |       |       |       |

| U-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 | R/W-0 |

| —        |       |       |       | SS2R<6:0> |       |       |       |

| bit 7    |       |       |       |           |       |       | bit 0 |

|          |       |       |       |           |       |       |       |

| l egend: |       |       |       |           |       |       |       |

## REGISTER 11-13: RPINR23: PERIPHERAL PIN SELECT INPUT REGISTER 23

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-7 | Unimplemented: Read as '0'                                                                                                                |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-0  | <b>SS2R&lt;6:0&gt;:</b> Assign SPI2 Slave Select (SS2) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) |

|          | 1111001 = Input tied to RPI121                                                                                                            |

|          |                                                                                                                                           |

|          | •                                                                                                                                         |

|          | 0000001 = Input tied to CMP1<br>0000000 = Input tied to Vss                                                                               |

#### REGISTER 11-14: RPINR26: PERIPHERAL PIN SELECT INPUT REGISTER 26 (dsPIC33EPXXXGP/MC50X DEVICES ONLY)

| U-0    | U-0   | U-0   | U-0   | U-0        | U-0   | U-0   | U-0   |

|--------|-------|-------|-------|------------|-------|-------|-------|

| _      | —     | —     | _     | _          | _     | —     | —     |

| bit 15 |       |       |       |            |       |       | bit 8 |

|        |       |       |       |            |       |       |       |

| U-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

|        |       |       |       | C1RXR<6:0> | >     |       |       |

| bit 7  |       |       |       |            |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-7 | Unimplemented: Read as '0'                                                                                                              |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-0  | <b>C1RXR&lt;6:0&gt;:</b> Assign CAN1 RX Input (CRX1) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) |

|          | 1111001 = Input tied to RPI121                                                                                                          |

|          | •                                                                                                                                       |

|          |                                                                                                                                         |

|          | 0000001 = Input tied to CMP1<br>0000000 = Input tied to Vss                                                                             |

#### 16.1.2 WRITE-PROTECTED REGISTERS

On dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices, write protection is implemented for the IOCONx and FCLCONx registers. The write protection feature prevents any inadvertent writes to these registers. This protection feature can be controlled by the PWMLOCK Configuration bit (FOSCSEL<6>). The default state of the write protection feature is enabled (PWMLOCK = 1). The write protection feature can be disabled by configuring, PWMLOCK = 0. To gain write access to these locked registers, the user application must write two consecutive values of (0xABCD and 0x4321) to the PWMKEY register to perform the unlock operation. The write access to the IOCONx or FCLCONx registers must be the next SFR access following the unlock process. There can be no other SFR accesses during the unlock process and subsequent write access. To write to both the IOCONx and FCLCONx registers requires two unlock operations.

The correct unlocking sequence is described in Example 16-1.

#### EXAMPLE 16-1: PWMx WRITE-PROTECTED REGISTER UNLOCK SEQUENCE

|                                                                                                          | lled low externally in order to clear and disable the fault<br>egister requires unlock sequence                                                                                                                                                                                                   |

|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>mov #0xabcd,w10 mov #0x4321,w11 mov #0x0000,w0 mov w10, PWMKEY mov w11, PWMKEY mov w0,FCLCON1</pre> | <pre>; Load first unlock key to w10 register<br/>; Load second unlock key to w11 register<br/>; Load desired value of FCLCON1 register in w0<br/>; Write first unlock key to PWMKEY register<br/>; Write second unlock key to PWMKEY register<br/>; Write desired value to FCLCON1 register</pre> |

| -                                                                                                        | d polarity using the IOCON1 register<br>gister requires unlock sequence                                                                                                                                                                                                                           |

| <pre>mov #0xabcd,w10 mov #0x4321,w11 mov #0xF000,w0 mov w10, PWMKEY mov w11, PWMKEY mov w0,IOCON1</pre>  | <pre>; Load first unlock key to w10 register<br/>; Load second unlock key to w11 register<br/>; Load desired value of IOCON1 register in w0<br/>; Write first unlock key to PWMKEY register<br/>; Write second unlock key to PWMKEY register<br/>; Write desired value to IOCON1 register</pre>   |

NOTES:

| REGISTER 24-6: | PTGSDLIM: PTG STEP DELAY LIMIT REGISTER <sup>(1,2)</sup> |

|----------------|----------------------------------------------------------|

|                |                                                          |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|------------------|-----------------|-------|

|                 |       |                  | PTGSD | LIM<15:8>         |                  |                 |       |

| bit 15          |       |                  |       |                   |                  |                 | bit 8 |

|                 |       |                  |       |                   |                  |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|                 |       |                  | PTGSE | )LIM<7:0>         |                  |                 |       |

| bit 7           |       |                  |       |                   |                  |                 | bit 0 |

|                 |       |                  |       |                   |                  |                 |       |

| Legend:         |       |                  |       |                   |                  |                 |       |

| R = Readable    | bit   | W = Writable b   | it    | U = Unimplen      | nented bit, read | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

bit 15-0 **PTGSDLIM<15:0>:** PTG Step Delay Limit Register bits Holds a PTG Step delay value representing the number of additional PTG clocks between the start of a Step command and the completion of a Step command.

**Note 1:** A base Step delay of one PTG clock is added to any value written to the PTGSDLIM register (Step Delay = (PTGSDLIM) + 1).

2: This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

## REGISTER 24-7: PTGC0LIM: PTG COUNTER 0 LIMIT REGISTER<sup>(1)</sup>

| R/W-0                  | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|------------------------|-------|------------------|-------|-------------------|-----------------|-----------------|-------|

|                        |       |                  | PTGC0 | LIM<15:8>         |                 |                 |       |

| bit 15                 |       |                  |       |                   |                 |                 | bit 8 |

|                        |       |                  |       |                   |                 |                 |       |

| R/W-0                  | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|                        |       |                  | PTGC  | )LIM<7:0>         |                 |                 |       |

| bit 7                  |       |                  |       |                   |                 |                 | bit 0 |

|                        |       |                  |       |                   |                 |                 |       |

| Legend:                |       |                  |       |                   |                 |                 |       |

| R = Readable bit W = V |       | W = Writable bi  | it    | U = Unimplem      | nented bit, rea | ad as '0'       |       |

| -n = Value at P        | POR   | '1' = Bit is set |       | '0' = Bit is clea | ared            | x = Bit is unki | nown  |

bit 15-0 **PTGC0LIM<15:0>:** PTG Counter 0 Limit Register bits May be used to specify the loop count for the PTGJMPC0 Step command or as a limit register for the General Purpose Counter 0.

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

## REGISTER 24-12: PTGQPTR: PTG STEP QUEUE POINTER REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0 | U-0   | U-0   | U-0         | U-0   | U-0   |

|--------|-----|-----|-------|-------|-------------|-------|-------|

| —      | —   | —   | —     | —     |             | _     | —     |

| bit 15 |     |     |       |       |             |       | bit 8 |

|        |     |     |       |       |             |       |       |

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0       | R/W-0 | R/W-0 |

| _      |     |     |       |       | PTGQPTR<4:0 | >     |       |

| bit 7  |     |     |       |       |             |       | bit 0 |

| Legend:           |                                                           |                      |                    |  |

|-------------------|-----------------------------------------------------------|----------------------|--------------------|--|

| R = Readable bit  | e bit W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |

| -n = Value at POR | '1' = Bit is set                                          | '0' = Bit is cleared | x = Bit is unknown |  |

bit 15-5 Unimplemented: Read as '0'

bit 4-0 **PTGQPTR<4:0>:** PTG Step Queue Pointer Register bits This register points to the currently active Step command in the Step queue.

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

## **REGISTER 24-13: PTGQUEX: PTG STEP QUEUE REGISTER x (x = 0-7)**<sup>(1,3)</sup>

| R/W-0  | R/W-0                            | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |  |

|--------|----------------------------------|-------|-------|-------|-------|-------|-------|--|--|--|--|

|        | STEP(2x + 1)<7:0> <sup>(2)</sup> |       |       |       |       |       |       |  |  |  |  |

| bit 15 |                                  |       |       |       |       |       | bit 8 |  |  |  |  |

|        |                                  |       |       |       |       |       |       |  |  |  |  |

| R/W-0  | R/W-0                            | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |  |

| R/W-0                        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|------------------------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| STEP(2x)<7:0> <sup>(2)</sup> |       |       |       |       |       |       |       |  |  |

| bit 7                        |       |       |       |       |       |       |       |  |  |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 15-8 | STEP(2x + 1)<7:0>: PTG Step Queue Pointer Register bits <sup>(2)</sup> |

|----------|------------------------------------------------------------------------|

|          | A queue location for storage of the STEP(2x + 1) command byte.         |

| bit 7-0  | STEP(2x)<7:0>: PTG Step Queue Pointer Register bits <sup>(2)</sup>     |

|          | A queue location for storage of the STEP(2x) command byte.             |

- **Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

- 2: Refer to Table 24-1 for the Step command encoding.

**3:** The Step registers maintain their values on any type of Reset.

| bit 3-0 | Step<br>Command        | OPTION<3:0> | Option Description                                          |

|---------|------------------------|-------------|-------------------------------------------------------------|

|         | PTGWHI(1)              | 0000        | PWM Special Event Trigger. <sup>(3)</sup>                   |

|         | or (1)                 | 0001        | PWM master time base synchronization output. <sup>(3)</sup> |

|         | PTGWLO(1)              | 0010        | PWM1 interrupt. <sup>(3)</sup>                              |

|         |                        | 0011        | PWM2 interrupt. <sup>(3)</sup>                              |

|         |                        | 0100        | PWM3 interrupt. <sup>(3)</sup>                              |

|         |                        | 0101        | Reserved.                                                   |

|         |                        | 0110        | Reserved.                                                   |

|         |                        | 0111        | OC1 Trigger event.                                          |

|         |                        | 1000        | OC2 Trigger event.                                          |

|         |                        | 1001        | IC1 Trigger event.                                          |

|         |                        | 1010        | CMP1 Trigger event.                                         |

|         |                        | 1011        | CMP2 Trigger event.                                         |

|         |                        | 1100        | CMP3 Trigger event.                                         |

|         |                        | 1101        | CMP4 Trigger event.                                         |

|         |                        | 1110        | ADC conversion done interrupt.                              |

|         |                        | 1111        | INT2 external interrupt.                                    |

|         | PTGIRQ(1)              | 0000        | Generate PTG Interrupt 0.                                   |

|         |                        | 0001        | Generate PTG Interrupt 1.                                   |

|         |                        | 0010        | Generate PTG Interrupt 2.                                   |

|         |                        | 0011        | Generate PTG Interrupt 3.                                   |

|         |                        | 0100        | Reserved.                                                   |

|         |                        | •           | •                                                           |

|         |                        | •           | •                                                           |

|         |                        | •           | •                                                           |

|         | (2)                    | 1111        | Reserved.                                                   |

|         | PTGTRIG <sup>(2)</sup> | 00000       | PTGO0.                                                      |

|         |                        | 00001       | PTGO1.                                                      |

|         |                        | •           | •                                                           |

|         |                        | •           | •                                                           |

|         |                        | •           | •                                                           |

|         |                        | 11110       | PTGO30.                                                     |

|         |                        | 11111       | PTGO31.                                                     |

TABLE 24-1: PTG STEP COMMAND FORMAT (CONTINUED)

Note 1: All reserved commands or options will execute but have no effect (i.e., execute as a NOP instruction).

2: Refer to Table 24-2 for the trigger output descriptions.

3: This feature is only available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

## 25.0 OP AMP/COMPARATOR MODULE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Op Amp/Comparator" (DS70357) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

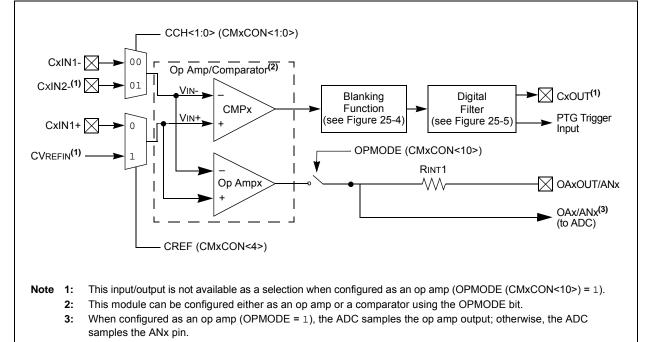

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices contain up to four comparators, which can be configured in various ways. Comparators, CMP1, CMP2 and CMP3, also have the option to be configured as op amps, with the output being brought to an external pin for gain/filtering connections. As shown in Figure 25-1, individual comparator options are specified by the comparator module's Special Function Register (SFR) control bits.

Note: Op Amp/Comparator 3 is not available on the dsPIC33EPXXXGP502/MC502/MC202 and PIC24EP256GP/MC202 (28-pin) devices.

These options allow users to:

- · Select the edge for trigger and interrupt generation

- · Configure the comparator voltage reference

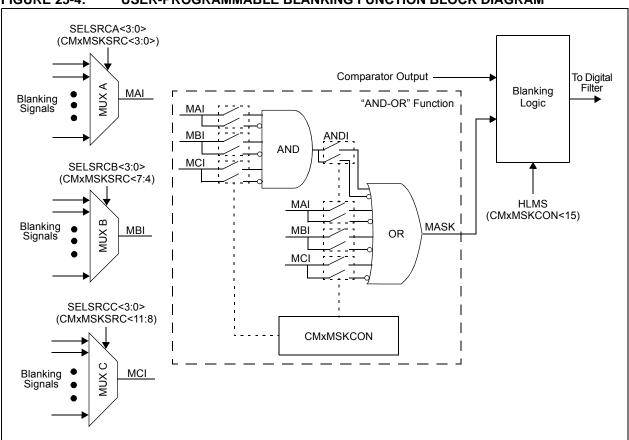

- · Configure output blanking and masking

- Configure as a comparator or op amp (CMP1, CMP2 and CMP3 only)

Note: Not all op amp/comparator input/output connections are available on all devices. See the "Pin Diagrams" section for available connections.

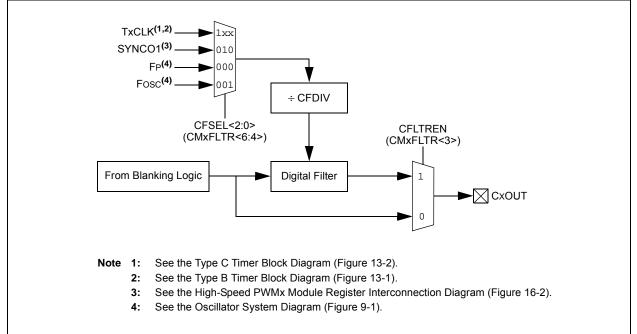

## FIGURE 25-1: OP AMP/COMPARATOR x MODULE BLOCK DIAGRAM (MODULES 1, 2 AND 3)

## DIGITAL FILTER INTERCONNECT BLOCK DIAGRAM

# REGISTER 25-5: CMxMSKCON: COMPARATOR x MASK GATING CONTROL REGISTER (CONTINUED)

bit 3 ABEN: AND Gate B Input Enable bit 1 = MBI is connected to AND gate 0 = MBI is not connected to AND gate bit 2 ABNEN: AND Gate B Input Inverted Enable bit 1 = Inverted MBI is connected to AND gate 0 = Inverted MBI is not connected to AND gate bit 1 AAEN: AND Gate A Input Enable bit 1 = MAI is connected to AND gate 0 = MAI is not connected to AND gate bit 0 AANEN: AND Gate A Input Inverted Enable bit 1 = Inverted MAI is connected to AND gate 0 = Inverted MAI is not connected to AND gate

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| DC CH/                    | ARACTERIS            | TICS                                                                   | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)}^{(1)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                     |                              |        |                                            |  |  |  |  |

|---------------------------|----------------------|------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------------------------|--------|--------------------------------------------|--|--|--|--|

| Param<br>No. Symbo        |                      | Characteristic                                                         | Min.                                                                                                                                                                                                                                                                                          | Тур. <sup>(2)</sup> | Max.                         | Units  | Conditions                                 |  |  |  |  |

| Op Amp DC Characteristics |                      |                                                                        |                                                                                                                                                                                                                                                                                               |                     |                              |        |                                            |  |  |  |  |

| CM40                      | VCMR                 | Common-Mode Input<br>Voltage Range                                     | AVss                                                                                                                                                                                                                                                                                          | _                   | AVDD                         | V      |                                            |  |  |  |  |

| CM41                      | CMRR                 | Common-Mode<br>Rejection Ratio <sup>(3)</sup>                          | —                                                                                                                                                                                                                                                                                             | 40                  | —                            | db     | VCM = AVDD/2                               |  |  |  |  |

| CM42                      | VOFFSET              | Op Amp Offset<br>Voltage <sup>(3)</sup>                                | —                                                                                                                                                                                                                                                                                             | ±5                  | —                            | mV     |                                            |  |  |  |  |

| CM43                      | Vgain                | Open-Loop Voltage<br>Gain <sup>(3)</sup>                               | _                                                                                                                                                                                                                                                                                             | 90                  | _                            | db     |                                            |  |  |  |  |

| CM44                      | los                  | Input Offset Current                                                   | _                                                                                                                                                                                                                                                                                             | -                   | _                            | _      | See pad leakage currents in Table 30-11    |  |  |  |  |

| CM45                      | lв                   | Input Bias Current                                                     | _                                                                                                                                                                                                                                                                                             | _                   | _                            | _      | See pad leakage currents in Table 30-11    |  |  |  |  |

| CM46                      | Ιουτ                 | Output Current                                                         | _                                                                                                                                                                                                                                                                                             |                     | 420                          | μA     | With minimum value of RFEEDBACK (CM48)     |  |  |  |  |

| CM48                      | RFEEDBACK            | Feedback Resistance<br>Value                                           | 8                                                                                                                                                                                                                                                                                             | -                   | _                            | kΩ     |                                            |  |  |  |  |

| CM49a                     | VOADC                | Output Voltage                                                         | AVss + 0.077                                                                                                                                                                                                                                                                                  |                     | AVDD - 0.077                 | V      | Ιουτ = 420 μΑ                              |  |  |  |  |

|                           |                      | Measured at OAx Using ADC <sup>(3,4)</sup>                             | AVss + 0.037<br>AVss + 0.018                                                                                                                                                                                                                                                                  |                     | AVDD – 0.037<br>AVDD – 0.018 | V<br>V | Ιουτ = 200 μΑ<br>Ιουτ = 100 μΑ             |  |  |  |  |

| CM49b                     | Vout                 | Output Voltage                                                         | AVss + 0.210                                                                                                                                                                                                                                                                                  | _                   | AVDD - 0.210                 | V      | Ιουτ = 420 μΑ                              |  |  |  |  |

|                           |                      | Measured at OAxOUT<br>Pin <sup>(3,4,5)</sup>                           | AVss + 0.100<br>AVss + 0.050                                                                                                                                                                                                                                                                  | _                   | AVDD – 0.100<br>AVDD – 0.050 | V<br>V | Ιουτ = 200 μΑ<br>Ιουτ = 100 μΑ             |  |  |  |  |

| CM51                      | RINT1 <sup>(6)</sup> | Internal Resistance 1<br>(Configuration A<br>and B) <sup>(3,4,5)</sup> | 198                                                                                                                                                                                                                                                                                           | 264                 | 317                          | Ω      | Min = -40°C<br>Typ = +25°C<br>Max = +125°C |  |  |  |  |

#### TABLE 30-53: OP AMP/COMPARATOR SPECIFICATIONS (CONTINUED)

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

- 2: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

- **3:** Parameter is characterized but not tested in manufacturing.

- 4: See Figure 25-6 for configuration information.

- 5: See Figure 25-7 for configuration information.

- 6: Resistances can vary by ±10% between op amps.

## 31.1 High-Temperature DC Characteristics

#### TABLE 31-1: OPERATING MIPS VS. VOLTAGE

|                |                            |                              | Max MIPS                                                              |  |  |

|----------------|----------------------------|------------------------------|-----------------------------------------------------------------------|--|--|

| Characteristic | VDD Range<br>(in Volts)    | Temperature Range<br>(in °C) | dsPIC33EPXXXGP50X,<br>dsPIC33EPXXXMC20X/50X and<br>PIC24EPXXXGP/MC20X |  |  |

| HDC5           | 3.0 to 3.6V <sup>(1)</sup> | -40°C to +150°C              | 40                                                                    |  |  |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN. Analog modules, such as the ADC, may have degraded performance. Device functionality is tested but not characterized.

#### TABLE 31-2: THERMAL OPERATING CONDITIONS

| Rating                                                                                                                                                                                 | Symbol | Min           | Тур | Max  | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------|-----|------|------|

| High-Temperature Devices                                                                                                                                                               |        |               |     |      |      |

| Operating Junction Temperature Range                                                                                                                                                   |        | -40           | —   | +155 | °C   |

| Operating Ambient Temperature Range                                                                                                                                                    | TA     | -40           | _   | +150 | °C   |

| Power Dissipation:<br>Internal Chip Power Dissipation:<br>$PINT = VDD x (IDD - \Sigma IOH)$<br>I/O Pin Power Dissipation:<br>$I/O = \Sigma (\{VDD - VOH\} x IOH) + \Sigma (VOL x IOL)$ | PD     | Pint + Pi/o   |     |      | W    |

| Maximum Allowed Power Dissipation                                                                                                                                                      |        | (TJ – TA)/θJA |     |      | W    |

#### TABLE 31-3: DC TEMPERATURE AND VOLTAGE SPECIFICATIONS

| DC CHARACTERISTICS |                | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |     |     |     |       |                 |  |

|--------------------|----------------|-------------------------------------------------------|-----|-----|-----|-------|-----------------|--|

| Parameter<br>No.   | Symbol         | Characteristic                                        | Min | Тур | Max | Units | Conditions      |  |

| Operating Voltage  |                |                                                       |     |     |     |       |                 |  |

| HDC10              | Supply Voltage |                                                       |     |     |     |       |                 |  |

|                    | Vdd            | _                                                     | 3.0 | 3.3 | 3.6 | V     | -40°C to +150°C |  |

#### 64-Lead Plastic Thin Quad Flatpack (PT) – 10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |           |      |      |  |  |

|--------------------------|-------------|-----------|------|------|--|--|

| D                        | MIN         | NOM       | MAX  |      |  |  |

| Number of Leads          | N           | 64        |      |      |  |  |

| Lead Pitch               | е           | 0.50 BSC  |      |      |  |  |

| Overall Height           | А           | -         |      |      |  |  |

| Molded Package Thickness |             | 0.95      | 1.00 | 1.05 |  |  |

| Standoff                 | A1          | 0.05      | -    | 0.15 |  |  |

| Foot Length              | L           | 0.45      | 0.60 | 0.75 |  |  |

| Footprint                | L1          | 1.00 REF  |      |      |  |  |

| Foot Angle               | φ           | 0°        | 3.5° | 7°   |  |  |

| Overall Width            | E           | 12.00 BSC |      |      |  |  |

| Overall Length           | D           | 12.00 BSC |      |      |  |  |

| Molded Package Width     | E1          | 10.00 BSC |      |      |  |  |

| Molded Package Length    | D1          | 10.00 BSC |      |      |  |  |

| Lead Thickness           | С           | 0.09      | -    | 0.20 |  |  |

| Lead Width               | b           | 0.17      | 0.22 | 0.27 |  |  |

| Mold Draft Angle Top     | α           | 11°       | 12°  | 13°  |  |  |

| Mold Draft Angle Bottom  | β           | 11°       | 12°  | 13°  |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-085B