#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 60 MIPs                                                                       |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                    |

| Number of I/O              | 21                                                                            |

| Program Memory Size        | 32KB (10.7K x 24)                                                             |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 2K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 6x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

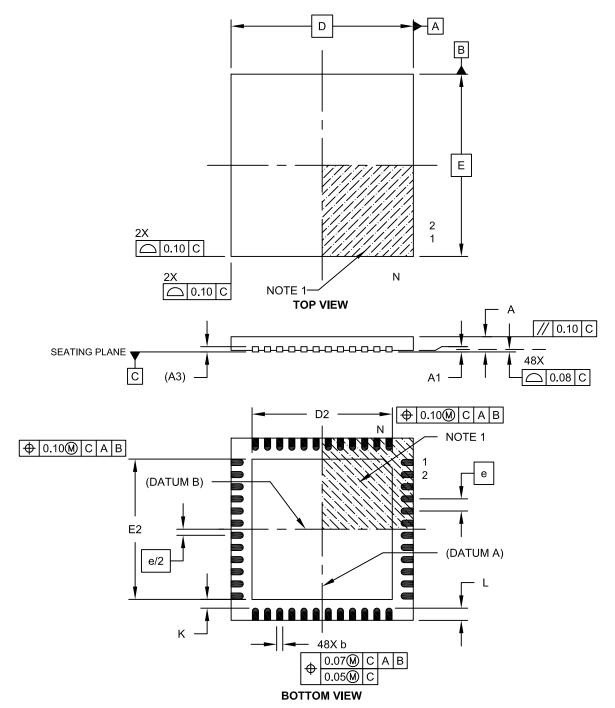

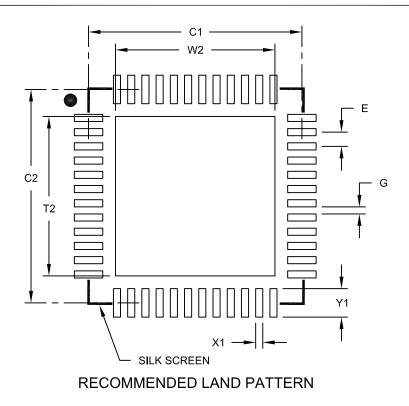

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                |

| Supplier Device Package    | 28-SSOP                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep32gp202-e-ss |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8  | Bit 7 | Bit 6  | Bit 5       | Bit 4  | Bit 3         | Bit 2    | Bit 1        | Bit 0         | All<br>Resets |

|--------------|-------|--------|--------|------------|--------|--------|--------|------------|--------|-------|--------|-------------|--------|---------------|----------|--------------|---------------|---------------|

| IFS0         | 0800  | _      | DMA1IF | AD1IF      | U1TXIF | U1RXIF | SPI1IF | SPI1EIF    | T3IF   | T2IF  | OC2IF  | IC2IF       | DMA0IF | T1IF          | OC1IF    | IC1IF        | <b>INT0IF</b> | 0000          |

| IFS1         | 0802  | U2TXIF | U2RXIF | INT2IF     | T5IF   | T4IF   | OC4IF  | OC3IF      | DMA2IF | _     | _      | _           | INT1IF | CNIF          | CMIF     | MI2C1IF      | SI2C1IF       | 0000          |

| IFS2         | 0804  | _      |        | _          | _      | _      |        | _          | _      |       | IC4IF  | IC3IF       | DMA3IF | _             | —        | SPI2IF       | SPI2EIF       | 0000          |

| IFS3         | 0806  | _      | _      | _          | _      | _      | QEI1IF | PSEMIF     | _      | _     | _      | _           | _      | _             | MI2C2IF  | SI2C2IF      | —             | 0000          |

| IFS4         | 0808  | -      | _      | CTMUIF     | _      | _      |        | —          | _      | _     |        | _           | _      | CRCIF         | U2EIF    | U1EIF        |               | 0000          |

| IFS5         | 080A  | PWM2IF | PWM1IF | _          | _      | _      |        | —          | _      | _     |        | _           | _      | _             | _        | _            |               | 0000          |

| IFS6         | 080C  | _      | _      | _          | _      | _      |        | —          | _      | _     |        | _           | _      | _             | _        | _            | PWM3IF        | 0000          |

| IFS8         | 0810  | JTAGIF | ICDIF  | _          | _      | _      |        | —          | _      | _     |        | _           | _      | _             | _        | _            | _             | 0000          |

| IFS9         | 0812  | _      | _      | _          |        | _      |        | _          | _      | _     | PTG3IF | PTG2IF      | PTG1IF | PTG0IF        | PTGWDTIF | PTGSTEPIF    |               | 0000          |

| IEC0         | 0820  | _      | DMA1IE | AD1IE      | U1TXIE | U1RXIE | SPI1IE | SPI1EIE    | T3IE   | T2IE  | OC2IE  | IC2IE       | DMA0IE | T1IE          | OC1IE    | IC1IE        | INTOIE        | 0000          |

| IEC1         | 0822  | U2TXIE | U2RXIE | INT2IE     | T5IE   | T4IE   | OC4IE  | OC3IE      | DMA2IE | —     | _      | —           | INT1IE | CNIE          | CMIE     | MI2C1IE      | SI2C1IE       | 0000          |

| IEC2         | 0824  | _      | _      | —          | -      | _      |        | —          | —      | _     | IC4IE  | IC3IE       | DMA3IE |               | _        | SPI2IE       | SPI2EIE       | 0000          |

| IEC3         | 0826  | _      | _      | _          |        | _      | QEI1IE | PSEMIE     | —      | _     | _      | —           | —      | -             | MI2C2IE  | SI2C2IE      | —             | 0000          |

| IEC4         | 0828  | _      | _      | CTMUIE     |        | _      |        | —          | —      | _     | _      | —           | _      | CRCIE         | U2EIE    | U1EIE        |               | 0000          |

| IEC5         | 082A  | PWM2IE | PWM1IE | —          |        | _      |        | _          | —      | _     | _      | —           | _      |               | _        | —            |               | 0000          |

| IEC6         | 082C  | _      | _      | _          |        | _      |        | _          | _      | _     | _      | —           | _      | -             | _        | _            | PWM3IE        | 0000          |

| IEC8         | 0830  | JTAGIE | ICDIE  | _          |        | _      |        | _          | _      | _     | _      | —           | _      | -             | _        | _            | —             | 0000          |

| IEC9         | 0832  | _      | _      | _          |        | _      |        | _          | _      | _     | PTG3IE | PTG2IE      | PTG1IE | PTG0IE        | PTGWDTIE | PTGSTEPIE    |               | 0000          |

| IPC0         | 0840  | _      |        | T1IP<2:0>  |        | _      |        | OC1IP<2:0  | )>     | _     |        | IC1IP<2:0>  |        |               |          | INT0IP<2:0>  |               | 4444          |

| IPC1         | 0842  | _      |        | T2IP<2:0>  |        | _      |        | OC2IP<2:0  | )>     | _     |        | IC2IP<2:0>  |        | — DMA0IP<2:0> |          |              | 4444          |               |

| IPC2         | 0844  | _      | -      | U1RXIP<2:0 | >      | _      | :      | SPI1IP<2:0 | )>     | _     |        | SPI1EIP<2:0 | >      | — T3IP<2:0>   |          |              | 4444          |               |

| IPC3         | 0846  | _      | _      | —          | —      | _      | C      | MA1IP<2:   | 0>     | _     |        | AD1IP<2:0>  |        | -             |          | U1TXIP<2:0>  |               | 0444          |

| IPC4         | 0848  | _      |        | CNIP<2:0>  |        | _      |        | CMIP<2:0   | >      | _     |        | MI2C1IP<2:0 | >      | -             | 5        | SI2C1IP<2:0> |               | 4444          |

| IPC5         | 084A  | _      | _      | —          | —      | _      |        | —          | —      | _     | _      | —           | —      | -             |          | INT1IP<2:0>  |               | 0004          |

| IPC6         | 084C  | _      |        | T4IP<2:0>  |        | _      |        | OC4IP<2:0  | )>     |       |        | OC3IP<2:0>  |        |               | [        | DMA2IP<2:0>  |               | 4444          |

| IPC7         | 084E  | _      |        | U2TXIP<2:0 | >      | _      | ι      | J2RXIP<2:  | 0>     |       |        | INT2IP<2:0> | •      |               |          | T5IP<2:0>    |               | 4444          |

| IPC8         | 0850  | _      | _      | —          | —      | _      |        | —          | —      | _     |        | SPI2IP<2:0> | •      | -             | 5        | SPI2EIP<2:0> |               | 0044          |

| IPC9         | 0852  | _      | _      | _          |        | _      |        | IC4IP<2:0  | >      | _     |        | IC3IP<2:0>  |        | -             | [        | DMA3IP<2:0>  |               | 0444          |

| IPC12        | 0858  | _      | _      | _          |        | _      | N      | 112C2IP<2: | 0>     | _     |        | SI2C2IP<2:0 | >      | -             | _        | —            |               | 0440          |

| IPC14        | 085C  | _      | _      | _          | _      | _      | (      | QEI1IP<2:0 | )>     | _     |        | PSEMIP<2:0  | >      | _             | _        | _            | _             | 0440          |

| IPC16        | 0860  | _      |        | CRCIP<2:0  | >      | _      |        | U2EIP<2:0  | >      | _     |        | U1EIP<2:0>  |        | _             | _        | _            | _             | 4440          |

| IPC19        | 0866  | _      | _      | —          | —      | _      | —      | —          | _      | _     |        | CTMUIP<2:0  | >      | _             | _        | _            | _             | 0040          |

| IPC23        | 086E  | _      | F      | PWM2IP<2:0 | )>     | _      | P      | WM1IP<2:   | 0>     | _     | _      | _           | —      | _             | _        | _            | _             | 4400          |

| IPC24        | 0870  | _      | _      |            |        | _      |        | _          |        |       | _      | _           | _      | _             | F        | PWM3IP<2:0>  |               | 4004          |

### TABLE 4-4: INTERRUPT CONTROLLER REGISTER MAP FOR PIC24EPXXXMC20X DEVICES ONLY

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-4: INTERRUPT CONTROLLER REGISTER MAP FOR PIC24EPXXXMC20X DEVICES ONLY (CONTINUED)

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8 | Bit 7       | Bit 6   | Bit 5       | Bit 4   | Bit 3   | Bit 2  | Bit 1       | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|------------|--------|--------|--------|------------|-------|-------------|---------|-------------|---------|---------|--------|-------------|--------|---------------|

| IPC35        | 0886  | _      |        | JTAGIP<2:0 | >      | _      |        | ICDIP<2:0  | >     |             | —       | _           | _       | —       | _      | —           |        | 4400          |

| IPC36        | 0888  | _      | F      | PTG0IP<2:0 | >      | _      | PT     | GWDTIP<    | 2:0>  |             | PT      | GSTEPIP<2   | :0>     | —       | —      | _           | -      | 4440          |

| IPC37        | 088A  | _      | —      | —          | _      | _      | F      | PTG3IP<2:0 | )>    |             |         | PTG2IP<2:0> | >       | _       |        | PTG1IP<2:0> |        | 0444          |

| INTCON1      | 08C0  | NSTDIS | OVAERR | OVBERR     |        |        |        | _          | _     | _           | DIV0ERR | DMACERR     | MATHERR | ADDRERR | STKERR | OSCFAIL     | _      | 0000          |

| INTCON2      | 08C2  | GIE    | DISI   | SWTRAP     | _      | _      |        |            | —     |             | _       | —           | —       | _       | INT2EP | INT1EP      | INT0EP | 8000          |

| INTCON3      | 08C4  | _      | —      | —          | _      | _      |        |            | —     |             | _       | DAE         | DOOVR   | _       | —      | —           |        | 0000          |

| INTCON4      | 08C6  | _      | _      | _          | _      | _      | -      | _          | —     | _           | _       | _           | _       | —       | —      | _           | SGHT   | 0000          |

| INTTREG      | 08C8  | Ι      | _      | _          | _      |        | ILR<   | 3:0>       |       | VECNUM<7:0> |         |             |         | 0000    |        |             |        |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-7: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33EPXXXMC50X DEVICES ONLY (CONTINUED)

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12  | Bit 11  | Bit 10 | Bit 9      | Bit 8 | Bit 7    | Bit 6   | Bit 5       | Bit 4   | Bit 3   | Bit 2  | Bit 1       | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|------------|---------|---------|--------|------------|-------|----------|---------|-------------|---------|---------|--------|-------------|--------|---------------|

| IPC23        | 086E  |        | F      | PWM2IP<2:0 | )>      |         | Р      | WM1IP<2:   | 0>    |          |         | _           |         | —       | _      | -           |        | 4400          |

| IPC24        | 0870  |        | _      | _          | _       | -       | _      | _          | _     | _        | _       | _           | _       | _       | F      | WM3IP<2:0>  |        | 0004          |

| IPC35        | 0886  |        |        | JTAGIP<2:0 | >       | -       |        | ICDIP<2:0  | >     | _        | _       | _           | _       | _       | _      | _           | _      | 4400          |

| IPC36        | 0888  |        | I      | PTG0IP<2:0 | )>      | -       | PT     | GWDTIP<    | 2:0>  | _        | P       | GSTEPIP<2:  | :0>     | _       | _      | _           | _      | 4440          |

| IPC37        | 088A  | _      | _      |            | —       | _       | F      | PTG3IP<2:0 | )>    | _        |         | PTG2IP<2:0> | •       | —       | F      | PTG1IP<2:0> |        | 0444          |

| INTCON1      | 08C0  | NSTDIS | OVAERR | OVBERR     | COVAERR | COVBERR | OVATE  | OVBTE      | COVTE | SFTACERR | DIV0ERR | DMACERR     | MATHERR | ADDRERR | STKERR | OSCFAIL     |        | 0000          |

| INTCON2      | 08C2  | GIE    | DISI   | SWTRAP     | —       | _       | _      | _          |       |          |         | _           |         | _       | INT2EP | INT1EP      | INT0EP | 8000          |

| INTCON3      | 08C4  | _      | —      |            | —       | _       | _      | _          |       |          |         | DAE         | DOOVR   | _       | —      | _           |        | 0000          |

| INTCON4      | 08C6  | _      | _      |            | —       | _       | _      | _          | _     | _        |         | _           | _       | —       | —      | _           | SGHT   | 0000          |

| INTTREG      | 08C8  | _      | —      | -          | —       |         | ILR<   | 3:0>       |       |          |         |             | VECNU   | JM<7:0> |        |             |        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### 5.2 RTSP Operation

RTSP allows the user application to erase a single page of memory and to program two instruction words at a time. See the General Purpose and Motor Control Family tables (Table 1 and Table 2, respectively) for the page sizes of each device.

For more information on erasing and programming Flash memory, refer to "Flash Programming" (DS70609) in the "dsPIC33/PIC24 Family Reference Manual".

### 5.3 **Programming Operations**

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. The processor stalls (waits) until the programming operation is finished.

For erase and program times, refer to Parameters D137a and D137b (Page Erase Time), and D138a and D138b (Word Write Cycle Time) in Table 30-14 in **Section 30.0 "Electrical Characteristics"**.

Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

### 5.3.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

Programmers can program two adjacent words (24 bits x 2) of program Flash memory at a time on every other word address boundary (0x000002, 0x000006, 0x00000A, etc.). To do this, it is necessary to erase the page that contains the desired address of the location the user wants to change.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user application must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS.

Refer to **Flash Programming**" (DS70609) in the "*dsPIC33/PIC24 Family Reference Manual*" for details and codes examples on programming using RTSP.

### 5.4 Flash Memory Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter |

|-------|--------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                            |

|       | http://www.microchip.com/wwwproducts/                                                |

|       | Devices.aspx?dDocName=en555464                                                       |

### 5.4.1 KEY RESOURCES

- "Flash Programming" (DS70609) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

### 5.5 Control Registers

Four SFRs are used to erase and write the program Flash memory: NVMCON, NVMKEY, NVMADRH and NVMADRL.

The NVMCON register (Register 5-1) enables and initiates Flash memory erase and write operations.

NVMKEY (Register 5-4) is a write-only register that is used for write protection. To start a programming or erase sequence, the user application must consecutively write 0x55 and 0xAA to the NVMKEY register.

There are two NVM Address registers: NVMADRH and NVMADRL. These two registers, when concatenated, form the 24-bit Effective Address (EA) of the selected word for programming operations or the selected page for erase operations.

The NVMADRH register is used to hold the upper 8 bits of the EA, while the NVMADRL register is used to hold the lower 16 bits of the EA.

# **REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)**

| bit 3 | <b>SLEEP:</b> Wake-up from Sleep Flag bit<br>1 = Device has been in Sleep mode<br>0 = Device has not been in Sleep mode |

|-------|-------------------------------------------------------------------------------------------------------------------------|

| bit 2 | IDLE: Wake-up from Idle Flag bit                                                                                        |

|       | <ol> <li>1 = Device was in Idle mode</li> <li>0 = Device was not in Idle mode</li> </ol>                                |

| bit 1 | <b>BOR:</b> Brown-out Reset Flag bit<br>1 = A Brown-out Reset has occurred<br>0 = A Brown-out Reset has not occurred    |

| bit 0 | <b>POR:</b> Power-on Reset Flag bit<br>1 = A Power-on Reset has occurred<br>0 = A Power-on Reset has not occurred       |

- **Note 1:** All of the Reset status bits can be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

- 2: If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

|                 | 12. 2007.00                                               |                                       |              |                   |                  |                 |        |  |  |  |  |

|-----------------|-----------------------------------------------------------|---------------------------------------|--------------|-------------------|------------------|-----------------|--------|--|--|--|--|

| U-0             | U-0                                                       | U-0                                   | U-0          | U-0               | U-0              | U-0             | U-0    |  |  |  |  |

| —               | —                                                         | —                                     | —            | —                 | —                | —               | —      |  |  |  |  |

| bit 15          |                                                           |                                       |              |                   |                  |                 | bit 8  |  |  |  |  |

|                 |                                                           |                                       |              |                   |                  |                 |        |  |  |  |  |

| U-0             | U-0                                                       | U-0                                   | U-0          | R-0               | R-0              | R-0             | R-0    |  |  |  |  |

| —               |                                                           | —                                     | —            | RQCOL3            | RQCOL2           | RQCOL1          | RQCOL0 |  |  |  |  |

| bit 7           |                                                           |                                       |              |                   |                  |                 | bit 0  |  |  |  |  |

|                 |                                                           |                                       |              |                   |                  |                 |        |  |  |  |  |

| Legend:         |                                                           |                                       |              |                   |                  |                 |        |  |  |  |  |

| R = Readable    | bit                                                       | W = Writable                          | bit          | U = Unimpler      | mented bit, read | l as '0'        |        |  |  |  |  |

| -n = Value at F | POR                                                       | '1' = Bit is set                      |              | '0' = Bit is cle  | ared             | x = Bit is unkr | nown   |  |  |  |  |

|                 |                                                           |                                       |              |                   |                  |                 |        |  |  |  |  |

| bit 15-4        | Unimplemen                                                | ted: Read as '                        | כ'           |                   |                  |                 |        |  |  |  |  |

| bit 3           | RQCOL3: DN                                                | /IA Channel 3 T                       | ransfer Requ | est Collision F   | ag bit           |                 |        |  |  |  |  |

|                 |                                                           | e and interrupt<br>est collision is d |              | st collision is d | etected          |                 |        |  |  |  |  |

| <b>h</b> # 0    | •                                                         |                                       |              | est Callisian Fl  | aa hit           |                 |        |  |  |  |  |

| bit 2           |                                                           | /IA Channel 2 T<br>ce and interrupt   | •            |                   | 0                |                 |        |  |  |  |  |

|                 |                                                           | e and interrupt<br>est collision is d |              |                   | elecieu          |                 |        |  |  |  |  |

| bit 1           | RQCOL1: DN                                                | /IA Channel 1 T                       | ransfer Requ | est Collision F   | ag bit           |                 |        |  |  |  |  |

|                 | 1 = User for                                              | e and interrupt                       | -based reque | st collision is d | etected          |                 |        |  |  |  |  |

|                 | 0 = No reque                                              | est collision is d                    | etected      |                   |                  |                 |        |  |  |  |  |

| bit 0           | RQCOL0: DMA Channel 0 Transfer Request Collision Flag bit |                                       |              |                   |                  |                 |        |  |  |  |  |

|                 | 1 = User force                                            | e and interrupt                       | -based reque | st collision is d | etected          |                 |        |  |  |  |  |

### REGISTER 8-12: DMARQC: DMA REQUEST COLLISION STATUS REGISTER

0 = No request collision is detected

### REGISTER 10-1: PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1 (CONTINUED)

- bit 3 SPI1MD: SPI1 Module Disable bit 1 = SPI1 module is disabled

- 0 = SPI1 module is enabled

- bit 2 Unimplemented: Read as '0'

- bit 1 C1MD: ECAN1 Module Disable bit<sup>(2)</sup> 1 = ECAN1 module is disabled 0 = ECAN1 module is enabled

- bit 0 AD1MD: ADC1 Module Disable bit 1 = ADC1 module is disabled 0 = ADC1 module is enabled

- Note 1: This bit is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

- 2: This bit is available on dsPIC33EPXXXGP50X and dsPIC33EPXXXMC50X devices only.

### 13.2 Timer Control Registers

| R/W-0         | U-0                                                                                                                                     | R/W-0                                                                    | U-0            | U-0              | U-0             | U-0             | U-0   |  |  |  |  |  |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|----------------|------------------|-----------------|-----------------|-------|--|--|--|--|--|--|

| TON           |                                                                                                                                         | TSIDL                                                                    | —              | _                |                 |                 | _     |  |  |  |  |  |  |

| bit 15        |                                                                                                                                         |                                                                          |                |                  |                 |                 | bit 8 |  |  |  |  |  |  |

|               |                                                                                                                                         |                                                                          |                |                  |                 |                 |       |  |  |  |  |  |  |

| U-0           | R/W-0                                                                                                                                   | R/W-0                                                                    | R/W-0          | R/W-0            | U-0             | R/W-0           | U-0   |  |  |  |  |  |  |

| _             | TGATE                                                                                                                                   | TCKPS1                                                                   | TCKPS0         | T32              | _               | TCS             | _     |  |  |  |  |  |  |

| bit 7         |                                                                                                                                         |                                                                          |                |                  |                 |                 | bit ( |  |  |  |  |  |  |

| <u> </u>      |                                                                                                                                         |                                                                          |                |                  |                 |                 |       |  |  |  |  |  |  |

| Legend:       | - 1-:4                                                                                                                                  |                                                                          |                | II II.           |                 |                 |       |  |  |  |  |  |  |

| R = Readable  |                                                                                                                                         | W = Writable                                                             |                | -                | nented bit, rea |                 |       |  |  |  |  |  |  |

| -n = Value at | PUR                                                                                                                                     | '1' = Bit is set                                                         |                | '0' = Bit is cle | areo            | x = Bit is unkn | own   |  |  |  |  |  |  |

| bit 15        | TON: Timerx                                                                                                                             | On hit                                                                   |                |                  |                 |                 |       |  |  |  |  |  |  |

|               | When T32 = 2                                                                                                                            |                                                                          |                |                  |                 |                 |       |  |  |  |  |  |  |

|               | 1 = Starts 32-                                                                                                                          | bit Timerx/y                                                             |                |                  |                 |                 |       |  |  |  |  |  |  |

|               | 0 = Stops 32-                                                                                                                           |                                                                          |                |                  |                 |                 |       |  |  |  |  |  |  |

|               | <u>When T32 = 0</u><br>1 = Starts 16-                                                                                                   |                                                                          |                |                  |                 |                 |       |  |  |  |  |  |  |

|               | 0 = Stops 16-                                                                                                                           |                                                                          |                |                  |                 |                 |       |  |  |  |  |  |  |

| bit 14        | Unimplemen                                                                                                                              | Unimplemented: Read as '0'                                               |                |                  |                 |                 |       |  |  |  |  |  |  |

| bit 13        | TSIDL: Timerx Stop in Idle Mode bit                                                                                                     |                                                                          |                |                  |                 |                 |       |  |  |  |  |  |  |

|               | <ul> <li>1 = Discontinues module operation when device enters Idle mode</li> <li>0 = Continues module operation in Idle mode</li> </ul> |                                                                          |                |                  |                 |                 |       |  |  |  |  |  |  |

|               |                                                                                                                                         | -                                                                        |                | ode              |                 |                 |       |  |  |  |  |  |  |

| bit 12-7      | -                                                                                                                                       | ted: Read as '                                                           |                |                  |                 |                 |       |  |  |  |  |  |  |

| bit 6         |                                                                                                                                         | <b>TGATE:</b> Timerx Gated Time Accumulation Enable bit<br>When TCS = 1: |                |                  |                 |                 |       |  |  |  |  |  |  |

|               | This bit is igno                                                                                                                        |                                                                          |                |                  |                 |                 |       |  |  |  |  |  |  |

|               | When TCS =                                                                                                                              |                                                                          |                |                  |                 |                 |       |  |  |  |  |  |  |

|               | 1 = Gated tim                                                                                                                           | e accumulatior                                                           |                |                  |                 |                 |       |  |  |  |  |  |  |

|               |                                                                                                                                         | e accumulation                                                           |                |                  |                 |                 |       |  |  |  |  |  |  |

| bit 5-4       |                                                                                                                                         | : Timerx Input                                                           | Clock Prescal  | e Select bits    |                 |                 |       |  |  |  |  |  |  |

|               | 11 = 1:256<br>10 = 1:64                                                                                                                 |                                                                          |                |                  |                 |                 |       |  |  |  |  |  |  |

|               | 01 = 1:8                                                                                                                                |                                                                          |                |                  |                 |                 |       |  |  |  |  |  |  |

|               | 00 = 1:1                                                                                                                                |                                                                          |                |                  |                 |                 |       |  |  |  |  |  |  |

| bit 3         | T32: 32-Bit Ti                                                                                                                          | mer Mode Sele                                                            | ect bit        |                  |                 |                 |       |  |  |  |  |  |  |

|               |                                                                                                                                         | nd Timery form<br>nd Timery act as                                       |                |                  |                 |                 |       |  |  |  |  |  |  |

| bit 2         | Unimplemen                                                                                                                              | ted: Read as '                                                           | )'             |                  |                 |                 |       |  |  |  |  |  |  |

| bit 1         | TCS: Timerx                                                                                                                             | Clock Source S                                                           | elect bit      |                  |                 |                 |       |  |  |  |  |  |  |

|               | 1 = External c<br>0 = Internal cl                                                                                                       | clock is from pir<br>lock (FP)                                           | n, TxCK (on th | ne rising edge)  |                 |                 |       |  |  |  |  |  |  |

| bit 0         | Unimplomon                                                                                                                              | ted: Read as '                                                           | ı'             |                  |                 |                 |       |  |  |  |  |  |  |

## REGISTER 13-1: TxCON: (TIMER2 AND TIMER4) CONTROL REGISTER

NOTES:

#### 18.3 SPIx Control Registers

#### R/W-0 U-0 R/W-0 U-0 R/W-0 R/W-0 R/W-0 U-0 SPIEN SPISIDL SPIBEC<2:0> \_\_\_\_\_ bit 15 R/W-0 R/W-0 R/W-0 R/C-0, HS R/W-0 R/W-0 R-0, HS, HC R-0, HS, HC SRMPT SPIROV SRXMPT SISEL2 SISEL1 SISEL0 SPITBF SPIRBF bit 7 Legend: C = Clearable bit HS = Hardware Settable bit HC = Hardware Clearable bit R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15 SPIEN: SPIx Enable bit 1 = Enables the module and configures SCKx, SDOx, SDIx and $\overline{SSx}$ as serial port pins 0 = Disables the module bit 14 Unimplemented: Read as '0' bit 13 SPISIDL: SPIx Stop in Idle Mode bit 1 = Discontinues the module operation when device enters Idle mode 0 = Continues the module operation in Idle mode bit 12-11 Unimplemented: Read as '0' bit 10-8 SPIBEC<2:0>: SPIx Buffer Element Count bits (valid in Enhanced Buffer mode) Master mode: Number of SPIx transfers that are pending. Slave mode: Number of SPIx transfers that are unread. SRMPT: SPIx Shift Register (SPIxSR) Empty bit (valid in Enhanced Buffer mode) bit 7 1 = SPIx Shift register is empty and Ready-To-Send or receive the data 0 = SPIx Shift register is not empty bit 6 SPIROV: SPIx Receive Overflow Flag bit

#### REGISTER 18-1: SPIxSTAT: SPIx STATUS AND CONTROL REGISTER

1 = A new byte/word is completely received and discarded; the user application has not read the previous data in the SPIxBUF register 0 = No overflow has occurred SRXMPT: SPIx Receive FIFO Empty bit (valid in Enhanced Buffer mode)

- 1 = RX FIFO is empty

- 0 = RX FIFO is not empty

#### bit 4-2 SISEL<2:0>: SPIx Buffer Interrupt Mode bits (valid in Enhanced Buffer mode)

- 111 = Interrupt when the SPIx transmit buffer is full (SPITBF bit is set)

- 110 = Interrupt when last bit is shifted into SPIxSR and as a result, the TX FIFO is empty

- 101 = Interrupt when the last bit is shifted out of SPIxSR and the transmit is complete

- 100 = Interrupt when one data is shifted into the SPIxSR and as a result, the TX FIFO has one open memory location

- 011 = Interrupt when the SPIx receive buffer is full (SPIRBF bit is set)

- 010 = Interrupt when the SPIx receive buffer is 3/4 or more full

- 001 = Interrupt when data is available in the receive buffer (SRMPT bit is set)

- 000 = Interrupt when the last data in the receive buffer is read and as a result, the buffer is empty (SRXMPT bit is set)

bit 5

bit 8

bit 0

# **19.2** I<sup>2</sup>C Control Registers

### REGISTER 19-1: I2CxCON: I2Cx CONTROL REGISTER

| R/W-0            | U-0                                                                      | R/W-0                                    | R/W-1, HC            | R/W-0                        | R/W-0             | R/W-0           | R/W-0          |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------|------------------------------------------|----------------------|------------------------------|-------------------|-----------------|----------------|--|--|--|--|--|

| I2CEN            | —                                                                        | I2CSIDL                                  | SCLREL               | IPMIEN <sup>(1)</sup>        | A10M              | DISSLW          | SMEN           |  |  |  |  |  |

| bit 15           |                                                                          |                                          |                      |                              |                   |                 | bit 8          |  |  |  |  |  |

|                  |                                                                          |                                          |                      |                              |                   |                 |                |  |  |  |  |  |

| R/W-0            | R/W-0                                                                    | R/W-0                                    | R/W-0, HC            | R/W-0, HC                    | R/W-0, HC         | R/W-0, HC       | R/W-0, HC      |  |  |  |  |  |

| GCEN             | STREN                                                                    | ACKDT                                    | ACKEN                | RCEN                         | PEN               | RSEN            | SEN            |  |  |  |  |  |

| bit 7            |                                                                          |                                          |                      |                              |                   |                 | bit 0          |  |  |  |  |  |

| Legend:          |                                                                          | HC = Hardware                            | Clearable bit        |                              |                   |                 |                |  |  |  |  |  |

| R = Readab       | le bit                                                                   | W = Writable bi                          |                      | U = Unimpler                 | mented bit, rea   | d as '0'        |                |  |  |  |  |  |

| -n = Value a     | It POR                                                                   | '1' = Bit is set                         |                      | '0' = Bit is cle             |                   | x = Bit is unk  | nown           |  |  |  |  |  |

|                  |                                                                          |                                          |                      |                              |                   |                 |                |  |  |  |  |  |

| bit 15           | I2CEN: I2Cx                                                              | Enable bit                               |                      |                              |                   |                 |                |  |  |  |  |  |

|                  |                                                                          | the I2Cx module                          |                      |                              |                   |                 | ;              |  |  |  |  |  |

| L:1 4 4          |                                                                          | the I2Cx module                          | ; all I-C ™ pins a   | are controlled               | by port function  | IS              |                |  |  |  |  |  |

| bit 14<br>bit 13 | -                                                                        | ited: Read as '0'                        | do hit               |                              |                   |                 |                |  |  |  |  |  |

| DIC 13           |                                                                          | Stop in Idle Mo<br>ues module oper       |                      | rice enters an l             | dle mode          |                 |                |  |  |  |  |  |

|                  |                                                                          | s module operati                         |                      |                              |                   |                 |                |  |  |  |  |  |

| bit 12           | SCLREL: SC                                                               | Lx Release Con                           | rol bit (when op     | perating as I <sup>2</sup> C | slave)            |                 |                |  |  |  |  |  |

|                  |                                                                          | 1 = Releases SCLx clock                  |                      |                              |                   |                 |                |  |  |  |  |  |

|                  |                                                                          | 0 = Holds SCLx clock low (clock stretch) |                      |                              |                   |                 |                |  |  |  |  |  |

|                  | If STREN = 1<br>Bit is R/W (i e                                          | <u>.:</u><br>e., software can w          | rite '0' to initiate | e stretch and w              | rite '1' to relea | se clock) Harr  | lware is clear |  |  |  |  |  |

|                  | at the beginn                                                            | ing of every slav<br>reception. Hardv    | ve data byte tra     | ansmission. Ha               | ardware is clea   | r at the end o  |                |  |  |  |  |  |

|                  | If STREN = 0                                                             |                                          |                      |                              |                   |                 |                |  |  |  |  |  |

|                  |                                                                          | ., software can or                       |                      |                              |                   |                 |                |  |  |  |  |  |

| hit 11           | -                                                                        | te transmission.<br>Iligent Peripheral   |                      |                              | -                 | address byte re | eception.      |  |  |  |  |  |

| bit 11           |                                                                          | le is enabled; all                       |                      |                              |                   |                 |                |  |  |  |  |  |

|                  | $0 = IPMI \mod$                                                          |                                          |                      | , lon no me agea             |                   |                 |                |  |  |  |  |  |

| bit 10           | A10M: 10-Bit                                                             | Slave Address b                          | oit                  |                              |                   |                 |                |  |  |  |  |  |

|                  |                                                                          | is a 10-bit slave                        |                      |                              |                   |                 |                |  |  |  |  |  |

|                  |                                                                          | is a 7-bit slave a                       |                      |                              |                   |                 |                |  |  |  |  |  |

| bit 9            |                                                                          | able Slew Rate (                         |                      |                              |                   |                 |                |  |  |  |  |  |

|                  |                                                                          | control is disable<br>control is enable  |                      |                              |                   |                 |                |  |  |  |  |  |

| bit 8            |                                                                          | us Input Levels b                        |                      |                              |                   |                 |                |  |  |  |  |  |

|                  |                                                                          | /O pin thresholds                        |                      | SMBus speci                  | fication          |                 |                |  |  |  |  |  |

|                  |                                                                          | SMBus input thre                         |                      | ,                            |                   |                 |                |  |  |  |  |  |

| bit 7            | GCEN: General Call Enable bit (when operating as I <sup>2</sup> C slave) |                                          |                      |                              |                   |                 |                |  |  |  |  |  |

|                  |                                                                          | nterrupt when a ge<br>call address disal |                      | ss is received ir            | n I2CxRSR (mo     | dule is enabled | for reception) |  |  |  |  |  |

|                  |                                                                          |                                          |                      |                              |                   |                 |                |  |  |  |  |  |

Note 1: When performing master operations, ensure that the IPMIEN bit is set to '0'.

### 21.5 ECAN Message Buffers

ECAN Message Buffers are part of RAM memory. They are not ECAN Special Function Registers. The user application must directly write into the RAM area that is configured for ECAN Message Buffers. The location and size of the buffer area is defined by the user application.

### BUFFER 21-1: ECAN™ MESSAGE BUFFER WORD 0

| U-0           | U-0                       | U-0               | R/W-x         | R/W-x            | R/W-x | R/W-x           | R/W-x |

|---------------|---------------------------|-------------------|---------------|------------------|-------|-----------------|-------|

|               | —                         | _                 | SID10         | SID9             | SID8  | SID7            | SID6  |

| bit 15        |                           |                   |               |                  |       |                 | bit 8 |

| R/W-x         | R/W-x                     | R/W-x             | R/W-x         | R/W-x            | R/W-x | R/W-x           | R/W-x |

| SID5          | SID4                      | SID3              | SID2          | SID1             | SID0  | SRR             | IDE   |

| bit 7         |                           |                   |               |                  |       |                 | bit 0 |

| Legend:       |                           |                   |               |                  |       |                 |       |

| R = Readabl   | e bit                     | W = Writable      | bit           | U = Unimpler     |       |                 |       |

| -n = Value at | POR                       | '1' = Bit is set  |               | '0' = Bit is cle | ared  | x = Bit is unkr | nown  |

|               |                           |                   |               |                  |       |                 |       |

| bit 15-13     | Unimplemen                | ted: Read as '    | כי            |                  |       |                 |       |

| bit 12-2      | <b>SID&lt;10:0&gt;:</b> S | Standard Identifi | ier bits      |                  |       |                 |       |

| bit 1         | SRR: Substitu             | ute Remote Re     | quest bit     |                  |       |                 |       |

|               | When IDE =                | 0:                |               |                  |       |                 |       |

|               | 1 = Message               | will request rer  | note transmis | ssion            |       |                 |       |

|               | 0 = Normal m              | nessage           |               |                  |       |                 |       |

|               | When IDE = 1              | <u>1:</u>         |               |                  |       |                 |       |

|               | The SRR bit r             | must be set to '  | 1'.           |                  |       |                 |       |

| bit 0         | IDE: Extende              | d Identifier bit  |               |                  |       |                 |       |

|               | 1 = Message               | will transmit Ex  | tended Ident  | ifier            |       |                 |       |

|               | 0 = Message               | will transmit St  | andard Identi | fier             |       |                 |       |

|               |                           |                   |               |                  |       |                 |       |

### BUFFER 21-2: ECAN™ MESSAGE BUFFER WORD 1

| U-0                                | U-0                               | U-0   | U-0   | R/W-x                                   | R/W-x | R/W-x | R/W-x |  |

|------------------------------------|-----------------------------------|-------|-------|-----------------------------------------|-------|-------|-------|--|

| —                                  | —                                 | —     |       | EID17                                   | EID16 | EID15 | EID14 |  |

| bit 15                             |                                   |       |       |                                         |       |       | bit 8 |  |

|                                    |                                   |       |       |                                         |       |       |       |  |

| R/W-x                              | R/W-x                             | R/W-x | R/W-x | R/W-x                                   | R/W-x | R/W-x | R/W-x |  |

| EID13                              | EID12                             | EID11 | EID10 | EID9                                    | EID8  | EID7  | EID6  |  |

| bit 7                              |                                   |       |       |                                         |       |       | bit 0 |  |

|                                    |                                   |       |       |                                         |       |       |       |  |

| Legend:                            |                                   |       |       |                                         |       |       |       |  |

| R = Readable                       | R = Readable bit W = Writable bit |       |       | U = Unimplemented bit, read as '0'      |       |       |       |  |

| -n = Value at POR '1' = Bit is set |                                   |       |       | '0' = Bit is cleared x = Bit is unknown |       |       |       |  |

| L                                  |                                   |       |       |                                         |       |       |       |  |

bit 15-12 Unimplemented: Read as '0'

bit 11-0 EID<17:6>: Extended Identifier bits

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-x                               | R/W-x                                | R/W-x                              | R/W-x         | R/W-x                              | R/W-x | R/W-x           | R/W-x |  |  |  |  |  |  |

|-------------------------------------|--------------------------------------|------------------------------------|---------------|------------------------------------|-------|-----------------|-------|--|--|--|--|--|--|

| EID5                                | EID4                                 | EID3                               | EID2          | EID1                               | EID0  | RTR             | RB1   |  |  |  |  |  |  |

| bit 15                              |                                      |                                    |               |                                    |       |                 | bit 8 |  |  |  |  |  |  |

|                                     |                                      |                                    |               |                                    |       |                 |       |  |  |  |  |  |  |

| U-x                                 | U-x                                  | U-x                                | R/W-x         | R/W-x                              | R/W-x | R/W-x           | R/W-x |  |  |  |  |  |  |

| —                                   | —                                    | —                                  | RB0           | DLC3                               | DLC2  | DLC1            | DLC0  |  |  |  |  |  |  |

| bit 7                               |                                      |                                    |               |                                    |       |                 | bit 0 |  |  |  |  |  |  |

| Lonondi                             |                                      |                                    |               |                                    |       |                 |       |  |  |  |  |  |  |

| Legend:                             | l. h.:.                              |                                    | L.11          | U = Unimplemented bit, read as '0' |       |                 |       |  |  |  |  |  |  |

| R = Readable bit   W = Writable bit |                                      |                                    |               | •                                  | ,     |                 |       |  |  |  |  |  |  |

| -n = Value a                        | t POR                                | '1' = Bit is set                   |               | '0' = Bit is cle                   | ared  | x = Bit is unkr | iown  |  |  |  |  |  |  |

|                                     |                                      |                                    |               |                                    |       |                 |       |  |  |  |  |  |  |

| bit 15-10                           | EID<5:0>: E                          | EID<5:0>: Extended Identifier bits |               |                                    |       |                 |       |  |  |  |  |  |  |

| bit 9                               | RTR: Remote Transmission Request bit |                                    |               |                                    |       |                 |       |  |  |  |  |  |  |

|                                     | When IDE =                           | When IDE = 1:                      |               |                                    |       |                 |       |  |  |  |  |  |  |

|                                     | •                                    | e will request re                  | mote transmis | ssion                              |       |                 |       |  |  |  |  |  |  |

|                                     | 0 = Normal n                         | 0                                  |               |                                    |       |                 |       |  |  |  |  |  |  |

|                                     | When IDE =<br>The RTR bit            |                                    |               |                                    |       |                 |       |  |  |  |  |  |  |

| <b>h</b> :+ 0                       | RB1: Reserv                          |                                    |               |                                    |       |                 |       |  |  |  |  |  |  |

| bit 8                               |                                      |                                    | or CAN proto  |                                    |       |                 |       |  |  |  |  |  |  |

|                                     |                                      | et this bit to '0' p               | -             | 0001.                              |       |                 |       |  |  |  |  |  |  |

| bit 7-5                             | •                                    | nted: Read as '                    | 0             |                                    |       |                 |       |  |  |  |  |  |  |

| bit 4                               | RB0: Reserv                          |                                    | <b></b>       |                                    |       |                 |       |  |  |  |  |  |  |

|                                     | User must se                         | et this bit to '0' p               | per CAN proto | ocol.                              |       |                 |       |  |  |  |  |  |  |

| hit 2 0                             |                                      | Jota Longth Co.                    | da hita       |                                    |       |                 |       |  |  |  |  |  |  |

### BUFFER 21-3: ECAN™ MESSAGE BUFFER WORD 2

bit 3-0 DLC<3:0>: Data Length Code bits

### BUFFER 21-4: ECAN<sup>™</sup> MESSAGE BUFFER WORD 3

| R/W-x             | R/W-x | R/W-x            | R/W-x | R/W-x                              | R/W-x | R/W-x              | R/W-x |  |

|-------------------|-------|------------------|-------|------------------------------------|-------|--------------------|-------|--|

|                   |       |                  | Ву    | /te 1                              |       |                    |       |  |

| bit 15            |       |                  |       |                                    |       |                    | bit 8 |  |

| R/W-x             | R/W-x | R/W-x            | R/W-x | R/W-x                              | R/W-x | R/W-x              | R/W-x |  |

|                   |       |                  | Ву    | rte 0                              |       |                    |       |  |

| bit 7             |       |                  |       |                                    |       |                    | bit 0 |  |

| Legend:           |       |                  |       |                                    |       |                    |       |  |

| R = Readable bit  |       | W = Writable bit |       | U = Unimplemented bit, read as '0' |       |                    |       |  |

| -n = Value at POR |       | '1' = Bit is set |       | '0' = Bit is cle                   | ared  | x = Bit is unknown |       |  |

bit 15-8 Byte 1<15:8>: ECAN Message Byte 1 bits

bit 7-0 Byte 0<7:0>: ECAN Message Byte 0 bits

| Base<br>Instr<br># | Assembly<br>Mnemonic |        |                               | Description                                                | # of<br>Words | # of<br>Cycles <sup>(2)</sup> | Status Flags<br>Affected            |

|--------------------|----------------------|--------|-------------------------------|------------------------------------------------------------|---------------|-------------------------------|-------------------------------------|

| 53                 | NEG                  | NEG    | <sub>Acc</sub> (1)            | Negate Accumulator                                         | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB             |

|                    |                      | NEG    | f                             | $f = \overline{f} + 1$                                     | 1             | 1                             | C,DC,N,OV,Z                         |

|                    |                      | NEG    | f,WREG                        | WREG = $\overline{f}$ + 1                                  | 1             | 1                             | C,DC,N,OV,Z                         |

|                    |                      | NEG    | Ws,Wd                         | $Wd = \overline{Ws} + 1$                                   | 1             | 1                             | C,DC,N,OV,Z                         |

| 54                 | NOP                  | NOP    |                               | No Operation                                               | 1             | 1                             | None                                |

|                    |                      | NOPR   |                               | No Operation                                               | 1             | 1                             | None                                |

| 55                 | POP                  | POP    | f                             | Pop f from Top-of-Stack (TOS)                              | 1             | 1                             | None                                |

|                    |                      | POP    | Wdo                           | Pop from Top-of-Stack (TOS) to Wdo                         | 1             | 1                             | None                                |

|                    |                      | POP.D  | Wnd                           | Pop from Top-of-Stack (TOS) to<br>W(nd):W(nd + 1)          | 1             | 2                             | None                                |

|                    |                      | POP.S  |                               | Pop Shadow Registers                                       | 1             | 1                             | All                                 |

| 56                 | PUSH                 | PUSH   | f                             | Push f to Top-of-Stack (TOS)                               | 1             | 1                             | None                                |

|                    |                      | PUSH   | Wso                           | Push Wso to Top-of-Stack (TOS)                             | 1             | 1                             | None                                |

|                    |                      | PUSH.D | Wns                           | Push W(ns):W(ns + 1) to Top-of-Stack<br>(TOS)              | 1             | 2                             | None                                |

|                    |                      | PUSH.S |                               | Push Shadow Registers                                      | 1             | 1                             | None                                |

| 57                 | PWRSAV               | PWRSAV | #lit1                         | Go into Sleep or Idle mode                                 | 1             | 1                             | WDTO,Sleep                          |

| 58                 | RCALL                | RCALL  | Expr                          | Relative Call                                              | 1             | 4                             | SFA                                 |

|                    |                      | RCALL  | Wn                            | Computed Call                                              | 1             | 4                             | SFA                                 |

| 59                 | REPEAT               | REPEAT | #lit15                        | Repeat Next Instruction lit15 + 1 times                    | 1             | 1                             | None                                |

|                    |                      | REPEAT | Wn                            | Repeat Next Instruction (Wn) + 1 times                     | 1             | 1                             | None                                |

| 60                 | RESET                | RESET  |                               | Software device Reset                                      | 1             | 1                             | None                                |

| 61                 | RETFIE               | RETFIE |                               | Return from interrupt                                      | 1             | 6 (5)                         | SFA                                 |

| 62                 | RETLW                | RETLW  | #lit10,Wn                     | Return with literal in Wn                                  | 1             | 6 (5)                         | SFA                                 |

| 63                 | RETURN               | RETURN |                               | Return from Subroutine                                     | 1             | 6 (5)                         | SFA                                 |

| 64                 | RLC                  | RLC    | f                             | f = Rotate Left through Carry f                            | 1             | 1                             | C,N,Z                               |

|                    |                      | RLC    | f,WREG                        | WREG = Rotate Left through Carry f                         | 1             | 1                             | C,N,Z                               |

|                    |                      | RLC    | Ws,Wd                         | Wd = Rotate Left through Carry Ws                          | 1             | 1                             | C,N,Z                               |

| 65                 | RLNC                 | RLNC   | f                             | f = Rotate Left (No Carry) f                               | 1             | 1                             | N,Z                                 |

|                    |                      | RLNC   | f,WREG                        | WREG = Rotate Left (No Carry) f                            | 1             | 1                             | N,Z                                 |

|                    |                      | RLNC   | Ws,Wd                         | Wd = Rotate Left (No Carry) Ws                             | 1             | 1                             | N,Z                                 |

| 66                 | RRC                  | RRC    | f                             | f = Rotate Right through Carry f                           | 1             | 1                             | C,N,Z                               |

|                    |                      | RRC    | f,WREG                        | WREG = Rotate Right through Carry f                        | 1             | 1                             | C,N,Z                               |

|                    |                      | RRC    | Ws,Wd                         | Wd = Rotate Right through Carry Ws                         | 1             | 1                             | C,N,Z                               |

| 67                 | RRNC                 | RRNC   | f                             | f = Rotate Right (No Carry) f                              | 1             | 1                             | N,Z                                 |

|                    |                      | RRNC   | f,WREG                        | WREG = Rotate Right (No Carry) f                           | 1             | 1                             | N,Z                                 |

| ~~                 |                      | RRNC   | Ws,Wd                         | Wd = Rotate Right (No Carry) Ws                            | 1             | 1                             | N,Z                                 |

| 68                 | SAC                  | SAC    | Acc,#Slit4,Wdo <sup>(1)</sup> | Store Accumulator                                          | 1             | 1                             | None                                |

| <u></u>            |                      | SAC.R  | Acc,#Slit4,Wdo <sup>(1)</sup> | Store Rounded Accumulator                                  | 1             | 1                             | None                                |

| 69                 | SE                   | SE     | Ws,Wnd                        | Wnd = sign-extended Ws                                     | 1             | 1                             | C,N,Z                               |

| 70                 | SETM                 | SETM   | f                             | f = 0xFFFF                                                 | 1             | 1                             | None                                |

|                    |                      | SETM   | WREG                          | WREG = 0xFFFF                                              | 1             | 1                             | None                                |

| 71                 | SFTAC                | SETM   | Ws<br>Acc, Wn <sup>(1)</sup>  | Ws = 0xFFFF           Arithmetic Shift Accumulator by (Wn) | 1             | 1<br>1                        | None<br>OA,OB,OAB                   |

|                    |                      | SFTAC  | Acc,#Slit6 <sup>(1)</sup>     | Arithmetic Shift Accumulator by Slit6                      | 1             | 1                             | SA,SB,SAB<br>OA,OB,OAB<br>SA,SB,SAB |

### TABLE 28-2: INSTRUCTION SET OVERVIEW (CONTINUED)

Note 1: These instructions are available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

# 29.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

- Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- · Simulators

- MPLAB X SIM Software Simulator

- · Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

### 29.1 MPLAB X Integrated Development Environment Software