Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 70 MIPs                                                                       |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                    |

| Number of I/O              | 21                                                                            |

| Program Memory Size        | 32KB (10.7K × 24)                                                             |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 2K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 6x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                |

| Supplier Device Package    | 28-SOIC                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep32gp202-i-so |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

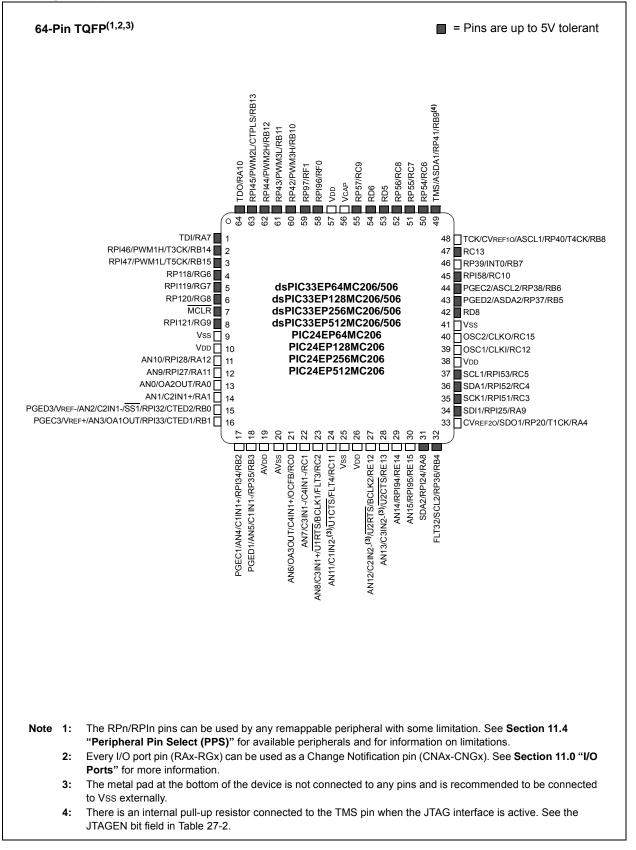

## Pin Diagrams (Continued)

#### **REGISTER 3-1:** SR: CPU STATUS REGISTER (CONTINUED)

| bit 7-5       | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2,3)</sup><br>111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled<br>110 = CPU Interrupt Priority Level is 6 (14)<br>101 = CPU Interrupt Priority Level is 5 (13)<br>100 = CPU Interrupt Priority Level is 4 (12)<br>011 = CPU Interrupt Priority Level is 3 (11)<br>010 = CPU Interrupt Priority Level is 2 (10)<br>001 = CPU Interrupt Priority Level is 1 (9)<br>000 = CPU Interrupt Priority Level is 0 (8) |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4         | RA: REPEAT Loop Active bit<br>1 = REPEAT loop in progress<br>0 = REPEAT loop not in progress                                                                                                                                                                                                                                                                                                                                                                                                    |

| bit 3         | N: MCU ALU Negative bit<br>1 = Result was negative<br>0 = Result was non-negative (zero or positive)                                                                                                                                                                                                                                                                                                                                                                                            |

| bit 2         | <ul> <li>OV: MCU ALU Overflow bit</li> <li>This bit is used for signed arithmetic (2's complement). It indicates an overflow of the magnitude that causes the sign bit to change state.</li> <li>1 = Overflow occurred for signed arithmetic (in this arithmetic operation)</li> <li>0 = No overflow occurred</li> </ul>                                                                                                                                                                        |

| bit 1         | <ul> <li><b>Z:</b> MCU ALU Zero bit</li> <li>1 = An operation that affects the Z bit has set it at some time in the past</li> <li>0 = The most recent operation that affects the Z bit has cleared it (i.e., a non-zero result)</li> </ul>                                                                                                                                                                                                                                                      |

| bit 0         | <b>C:</b> MCU ALU Carry/Borrow bit<br>1 = A carry-out from the Most Significant bit of the result occurred<br>0 = No carry-out from the Most Significant bit of the result occurred                                                                                                                                                                                                                                                                                                             |

| Note 1:<br>2: | This bit is available on dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices only.<br>The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority                                                                                                                                                                                                                                                                                                     |

- Level. The value in parentheses indicates the IPL, if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

3: The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

- 4: A data write to the SR register can modify the SA and SB bits by either a data write to SA and SB or by clearing the SAB bit. To avoid a possible SA or SB bit write race condition, the SA and SB bits should not be modified using bit operations.

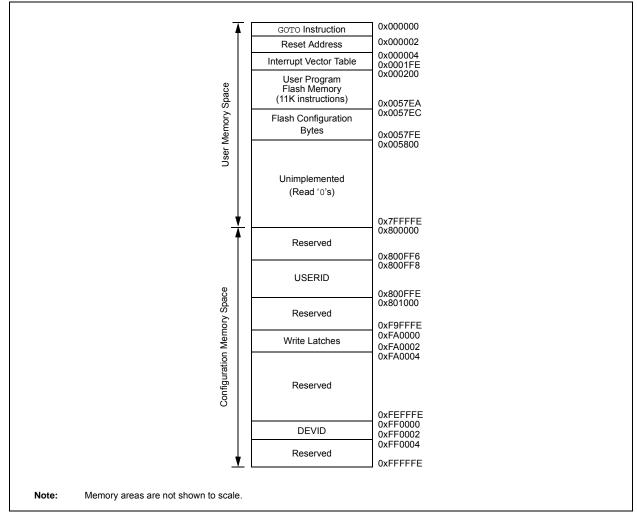

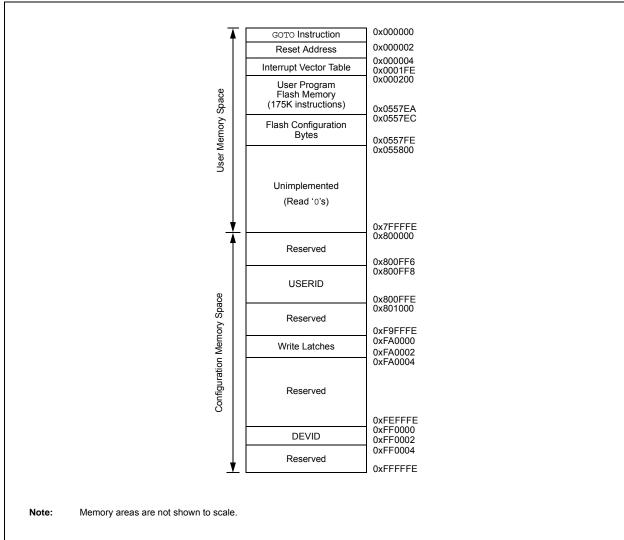

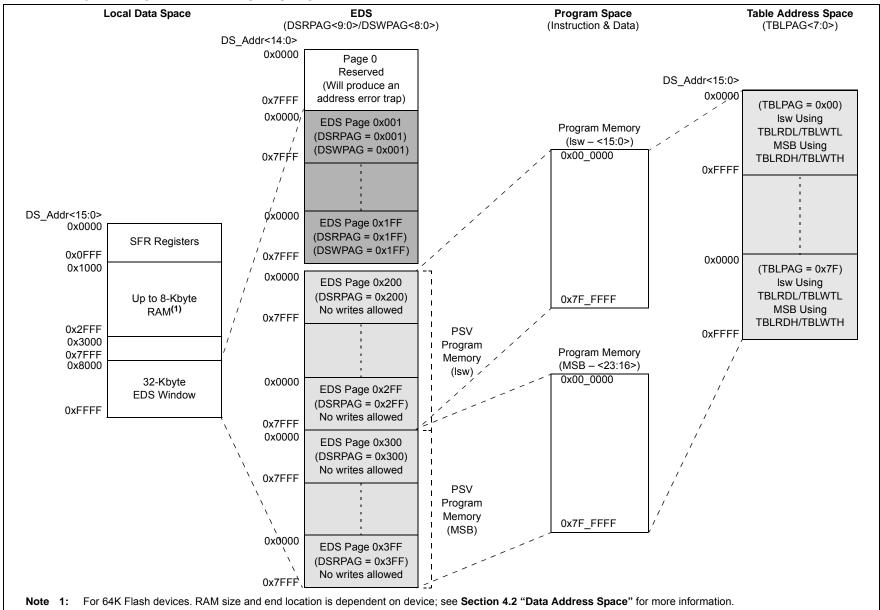

## 4.0 MEMORY ORGANIZATION

Note: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXGP/MC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Program Memory" (DS70613) in the "dsPIC33/PIC24 Family Reference Manual', which is available from the Microchip web site (www.microchip.com).

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X architecture features separate program and data memory spaces, and buses. This architecture also allows the direct access of program memory from the Data Space (DS) during code execution.

## 4.1 Program Address Space

The program address memory space of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices is 4M instructions. The space is addressable by a 24-bit value derived either from the 23-bit PC during program execution, or from table operation or Data Space remapping, as described in Section 4.8 "Interfacing Program and Data Memory Spaces".

User application access to the program memory space is restricted to the lower half of the address range (0x000000 to 0x7FFFF). The exception is the use of TBLRD operations, which use TBLPAG<7> to read Device ID sections of the configuration memory space.

The program memory maps, which are presented by device family and memory size, are shown in Figure 4-1 through Figure 4-5.

# FIGURE 4-1: PROGRAM MEMORY MAP FOR dsPIC33EP32GP50X, dsPIC33EP32MC20X/50X AND PIC24EP32GP/MC20X DEVICES

#### FIGURE 4-5: PROGRAM MEMORY MAP FOR dsPIC33EP512GP50X, dsPIC33EP512MC20X/50X AND PIC24EP512GP/MC20X DEVICES

#### EXAMPLE 4-3: PAGED DATA MEMORY SPACE

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

|                                               | Vector          | IRQ        | IVT Address       | Inte     | errupt Bit L | ocation     |

|-----------------------------------------------|-----------------|------------|-------------------|----------|--------------|-------------|

| Interrupt Source                              | # # IVI Address |            | Flag              | Enable   | Priority     |             |

|                                               | High            | est Natura | I Order Priority  |          |              |             |

| INT0 – External Interrupt 0                   | 8               | 0          | 0x000014          | IFS0<0>  | IEC0<0>      | IPC0<2:0>   |

| IC1 – Input Capture 1                         | 9               | 1          | 0x000016          | IFS0<1>  | IEC0<1>      | IPC0<6:4>   |

| OC1 – Output Compare 1                        | 10              | 2          | 0x000018          | IFS0<2>  | IEC0<2>      | IPC0<10:8>  |

| T1 – Timer1                                   | 11              | 3          | 0x00001A          | IFS0<3>  | IEC0<3>      | IPC0<14:12> |

| DMA0 – DMA Channel 0                          | 12              | 4          | 0x00001C          | IFS0<4>  | IEC0<4>      | IPC1<2:0>   |

| IC2 – Input Capture 2                         | 13              | 5          | 0x00001E          | IFS0<5>  | IEC0<5>      | IPC1<6:4>   |

| OC2 – Output Compare 2                        | 14              | 6          | 0x000020          | IFS0<6>  | IEC0<6>      | IPC1<10:8>  |

| T2 – Timer2                                   | 15              | 7          | 0x000022          | IFS0<7>  | IEC0<7>      | IPC1<14:12> |

| T3 – Timer3                                   | 16              | 8          | 0x000024          | IFS0<8>  | IEC0<8>      | IPC2<2:0>   |

| SPI1E – SPI1 Error                            | 17              | 9          | 0x000026          | IFS0<9>  | IEC0<9>      | IPC2<6:4>   |

| SPI1 – SPI1 Transfer Done                     | 18              | 10         | 0x000028          | IFS0<10> | IEC0<10>     | IPC2<10:8>  |

| U1RX – UART1 Receiver                         | 19              | 11         | 0x00002A          | IFS0<11> | IEC0<11>     | IPC2<14:12> |

| U1TX – UART1 Transmitter                      | 20              | 12         | 0x00002C          | IFS0<12> | IEC0<12>     | IPC3<2:0>   |

| AD1 – ADC1 Convert Done                       | 21              | 13         | 0x00002E          | IFS0<13> | IEC0<13>     | IPC3<6:4>   |

| DMA1 – DMA Channel 1                          | 22              | 14         | 0x000030          | IFS0<14> | IEC0<14>     | IPC3<10:8>  |

| Reserved                                      | 23              | 15         | 0x000032          |          |              | _           |

| SI2C1 – I2C1 Slave Event                      | 24              | 16         | 0x000034          | IFS1<0>  | IEC1<0>      | IPC4<2:0>   |

| MI2C1 – I2C1 Master Event                     | 25              | 17         | 0x000036          | IFS1<1>  | IEC1<1>      | IPC4<6:4>   |

| CM – Comparator Combined Event                | 26              | 18         | 0x000038          | IFS1<2>  | IEC1<2>      | IPC4<10:8>  |

| CN – Input Change Interrupt                   | 27              | 19         | 0x00003A          | IFS1<3>  | IEC1<3>      | IPC4<14:12> |

| INT1 – External Interrupt 1                   | 28              | 20         | 0x00003C          | IFS1<4>  | IEC1<4>      | IPC5<2:0>   |

| Reserved                                      | 29-31           | 21-23      | 0x00003E-0x000042 |          |              | _           |

| DMA2 – DMA Channel 2                          | 32              | 24         | 0x000044          | IFS1<8>  | IEC1<8>      | IPC6<2:0>   |

| OC3 – Output Compare 3                        | 33              | 25         | 0x000046          | IFS1<9>  | IEC1<9>      | IPC6<6:4>   |

| OC4 – Output Compare 4                        | 34              | 26         | 0x000048          | IFS1<10> | IEC1<10>     | IPC6<10:8>  |

| T4 – Timer4                                   | 35              | 27         | 0x00004A          | IFS1<11> | IEC1<11>     | IPC6<14:12> |

| T5 – Timer5                                   | 36              | 28         | 0x00004C          | IFS1<12> | IEC1<12>     | IPC7<2:0>   |

| INT2 – External Interrupt 2                   | 37              | 29         | 0x00004E          | IFS1<13> | IEC1<13>     | IPC7<6:4>   |

| U2RX – UART2 Receiver                         | 38              | 30         | 0x000050          | IFS1<14> | IEC1<14>     | IPC7<10:8>  |

| U2TX – UART2 Transmitter                      | 39              | 31         | 0x000052          | IFS1<15> | IEC1<15>     | IPC7<14:12> |

| SPI2E – SPI2 Error                            | 40              | 32         | 0x000054          | IFS2<0>  | IEC2<0>      | IPC8<2:0>   |

| SPI2 – SPI2 Transfer Done                     | 41              | 33         | 0x000056          | IFS2<1>  | IEC2<1>      | IPC8<6:4>   |

| C1RX – CAN1 RX Data Ready <sup>(1)</sup>      | 42              | 34         | 0x000058          | IFS2<2>  | IEC2<2>      | IPC8<10:8>  |

| C1 – CAN1 Event <sup>(1)</sup>                | 43              | 35         | 0x00005A          | IFS2<3>  | IEC2<3>      | IPC8<14:12> |

| DMA3 – DMA Channel 3                          | 44              | 36         | 0x00005C          | IFS2<4>  | IEC2<4>      | IPC9<2:0>   |

| IC3 – Input Capture 3                         | 45              | 37         | 0x00005E          | IFS2<5>  | IEC2<5>      | IPC9<6:4>   |

| IC4 – Input Capture 4                         | 46              | 38         | 0x000060          | IFS2<6>  | IEC2<6>      | IPC9<10:8>  |

| Reserved                                      | 47-56           | 39-48      | 0x000062-0x000074 | —        | —            | —           |

| SI2C2 – I2C2 Slave Event                      | 57              | 49         | 0x000076          | IFS3<1>  | IEC3<1>      | IPC12<6:4>  |

| MI2C2 – I2C2 Master Event                     | 58              | 50         | 0x000078          | IFS3<2>  | IEC3<2>      | IPC12<10:8> |

| Reserved                                      | 59-64           | 51-56      | 0x00007A-0x000084 |          | _            |             |

| PSEM – PWM Special Event Match <sup>(2)</sup> | 65              | 57         | 0x000086          | IFS3<9>  | IEC3<9>      | IPC14<6:4>  |

#### TABLE 7-1: INTERRUPT VECTOR DETAILS

Note 1: This interrupt source is available on dsPIC33EPXXXGP50X and dsPIC33EPXXXMC50X devices only.

2: This interrupt source is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

| R/W-1        | R/W-0         | R/W-0                                             | U-0          | U-0              | U-0              | U-0             | U-0    |  |  |  |  |  |

|--------------|---------------|---------------------------------------------------|--------------|------------------|------------------|-----------------|--------|--|--|--|--|--|

| GIE          | DISI          | SWTRAP                                            |              |                  |                  | _               |        |  |  |  |  |  |

| bit 15       |               |                                                   |              |                  |                  |                 | bit 8  |  |  |  |  |  |

|              |               |                                                   |              |                  |                  |                 |        |  |  |  |  |  |

| U-0          | U-0           | U-0                                               | U-0          | U-0              | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |  |

|              | —             |                                                   |              |                  | INT2EP           | INT1EP          | INT0EP |  |  |  |  |  |

| bit 7        |               |                                                   |              |                  |                  |                 | bit C  |  |  |  |  |  |

| Legend:      |               |                                                   |              |                  |                  |                 |        |  |  |  |  |  |

| R = Readab   | le bit        | W = Writable                                      | bit          | U = Unimpler     | mented bit, read | l as '0'        |        |  |  |  |  |  |

| -n = Value a |               | '1' = Bit is set                                  |              | '0' = Bit is cle |                  | x = Bit is unki | nown   |  |  |  |  |  |

|              |               |                                                   |              |                  |                  |                 |        |  |  |  |  |  |

| bit 15       | GIE: Global   | Interrupt Enable                                  | e bit        |                  |                  |                 |        |  |  |  |  |  |

|              | 1 = Interrupt | 1 = Interrupts and associated IE bits are enabled |              |                  |                  |                 |        |  |  |  |  |  |

|              |               | s are disabled, I                                 | •            | still enabled    |                  |                 |        |  |  |  |  |  |

| bit 14       | DISI: DISI    | nstruction Statu                                  | s bit        |                  |                  |                 |        |  |  |  |  |  |

|              |               | struction is active<br>struction is not a         | -            |                  |                  |                 |        |  |  |  |  |  |

| bit 13       | SWTRAP: S     | Software Trap St                                  | atus bit     |                  |                  |                 |        |  |  |  |  |  |

|              |               | e trap is enabled<br>e trap is disabled           |              |                  |                  |                 |        |  |  |  |  |  |

| bit 12-3     | Unimpleme     | nted: Read as '                                   | 0'           |                  |                  |                 |        |  |  |  |  |  |

| bit 2        | INT2EP: Ext   | ternal Interrupt 2                                | 2 Edge Detec | t Polarity Selec | t bit            |                 |        |  |  |  |  |  |

|              |               | on negative edg                                   |              |                  |                  |                 |        |  |  |  |  |  |

| bit 1        | INT1EP: Ext   | ternal Interrupt 1                                | Edge Detec   | t Polarity Selec | t bit            |                 |        |  |  |  |  |  |

|              |               | on negative edg                                   |              |                  |                  |                 |        |  |  |  |  |  |

| bit 0        | INTOEP: Ext   | ternal Interrupt C                                | Edge Detec   | t Polarity Selec | t bit            |                 |        |  |  |  |  |  |

|              |               | on negative edg                                   |              |                  |                  |                 |        |  |  |  |  |  |

#### REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

#### REGISTER 8-9: DSADRH: DMA MOST RECENT RAM HIGH ADDRESS REGISTER

| U-0            | U-0 | U-0             | U-0   | U-0          | U-0              | U-0    | U-0   |

|----------------|-----|-----------------|-------|--------------|------------------|--------|-------|

| —              | —   | —               | —     | —            | —                | -      | —     |

| bit 15         |     |                 |       |              |                  |        | bit 8 |

|                |     |                 |       |              |                  |        |       |

| R-0            | R-0 | R-0             | R-0   | R-0          | R-0              | R-0    | R-0   |

|                |     |                 | DSADR | <23:16>      |                  |        |       |

| bit 7          |     |                 |       |              |                  |        | bit 0 |

|                |     |                 |       |              |                  |        |       |

| Legend:        |     |                 |       |              |                  |        |       |

| R = Readable b | it  | W = Writable bi | t     | U = Unimpler | nented bit, read | as '0' |       |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |  |

|-------------------|------------------|------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |  |

#### bit 15-8 Unimplemented: Read as '0'

bit 7-0 DSADR<23:16>: Most Recent DMA Address Accessed by DMA bits

#### REGISTER 8-10: DSADRL: DMA MOST RECENT RAM LOW ADDRESS REGISTER

| R-0                                                                        | R-0 | R-0              | R-0  | R-0            | R-0         | R-0       | R-0   |

|----------------------------------------------------------------------------|-----|------------------|------|----------------|-------------|-----------|-------|

|                                                                            |     |                  | DSAD | DR<15:8>       |             |           |       |

| bit 15                                                                     |     |                  |      |                |             |           | bit 8 |

|                                                                            |     |                  |      |                |             |           |       |

| R-0                                                                        | R-0 | R-0              | R-0  | R-0            | R-0         | R-0       | R-0   |

|                                                                            |     |                  | DSA  | DR<7:0>        |             |           |       |

| bit 7                                                                      |     |                  |      |                |             |           | bit 0 |

|                                                                            |     |                  |      |                |             |           |       |

| Legend:                                                                    |     |                  |      |                |             |           |       |

| R = Readable b                                                             | it  | W = Writable bit |      | U = Unimplemen | ted bit, re | ad as '0' |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |     |                  |      |                |             | own       |       |

bit 15-0 DSADR<15:0>: Most Recent DMA Address Accessed by DMA bits

#### 10.2.1 SLEEP MODE

The following occurs in Sleep mode:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption is reduced to a minimum, provided that no I/O pin is sourcing current.

- The Fail-Safe Clock Monitor does not operate, since the system clock source is disabled.

- The LPRC clock continues to run in Sleep mode if the WDT is enabled.

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode.

- Some device features or peripherals can continue to operate. This includes items such as the Input Change Notification (ICN) on the I/O ports or peripherals that use an external clock input.

- Any peripheral that requires the system clock source for its operation is disabled.

The device wakes up from Sleep mode on any of these events:

- Any interrupt source that is individually enabled

- · Any form of device Reset

- A WDT time-out

On wake-up from Sleep mode, the processor restarts with the same clock source that was active when Sleep mode was entered.

For optimal power savings, the internal regulator and the Flash regulator can be configured to go into Standby when Sleep mode is entered by clearing the VREGS (RCON<8>) and VREGSF (RCON<11>) bits (default configuration).

If the application requires a faster wake-up time, and can accept higher current requirements, the VREGS (RCON<8>) and VREGSF (RCON<11>) bits can be set to keep the internal regulator and the Flash regulator active during Sleep mode.

#### 10.2.2 IDLE MODE

The following occurs in Idle mode:

- The CPU stops executing instructions.

- · The WDT is automatically cleared.

- The system clock source remains active. By default, all peripheral modules continue to operate normally from the system clock source, but can also be selectively disabled (see Section 10.4 "Peripheral Module Disable").

- If the WDT or FSCM is enabled, the LPRC also remains active.

The device wakes from Idle mode on any of these events:

- · Any interrupt that is individually enabled

- Any device Reset

- · A WDT time-out

On wake-up from Idle mode, the clock is reapplied to the CPU and instruction execution will begin (2-4 clock cycles later), starting with the instruction following the PWRSAV instruction or the first instruction in the Interrupt Service Routine (ISR).

All peripherals also have the option to discontinue operation when Idle mode is entered to allow for increased power savings. This option is selectable in the control register of each peripheral; for example, the TSIDL bit in the Timer1 Control register (T1CON<13>).

#### 10.2.3 INTERRUPTS COINCIDENT WITH POWER SAVE INSTRUCTIONS

Any interrupt that coincides with the execution of a PWRSAV instruction is held off until entry into Sleep or Idle mode has completed. The device then wakes up from Sleep or Idle mode.

#### REGISTER 15-2: OCxCON2: OUTPUT COMPARE x CONTROL REGISTER 2 (CONTINUED)

| bit 4-0 | SYNCSEL<4:0>: Trigger/Synchronization Source Selection bits  |

|---------|--------------------------------------------------------------|

|         | 11111 = OCxRS compare event is used for synchronization      |

|         | 11110 = INT2 pin synchronizes or triggers OCx                |

|         | 11101 = INT1 pin synchronizes or triggers OCx                |

|         | 11100 = CTMU module synchronizes or triggers OCx             |

|         | 11011 = ADC1 module synchronizes or triggers OCx             |

|         | 11010 = CMP3 module synchronizes or triggers OCx             |

|         | 11001 = CMP2 module synchronizes or triggers OCx             |

|         | 11000 = CMP1 module synchronizes or triggers OCx             |

|         | 10111 = Reserved                                             |

|         | 10110 = Reserved                                             |

|         | 10101 = Reserved                                             |

|         | 10100 = Reserved                                             |

|         | 10011 = IC4 input capture event synchronizes or triggers OCx |

|         | 10010 = IC3 input capture event synchronizes or triggers OCx |

|         | 10001 = IC2 input capture event synchronizes or triggers OCx |

|         | 10000 = IC1 input capture event synchronizes or triggers OCx |

|         | 01111 = Timer5 synchronizes or triggers OCx                  |

|         | 01110 = Timer4 synchronizes or triggers OCx                  |

|         | 01101 = Timer3 synchronizes or triggers OCx                  |

|         | 01100 = Timer2 synchronizes or triggers OCx (default)        |

|         | 01011 = Timer1 synchronizes or triggers OCx $(2)$            |

|         | 01010 = PTGOx synchronizes or triggers $OCx^{(3)}$           |

|         | 01001 = Reserved                                             |

|         | 01000 = Reserved                                             |

|         | 00111 = Reserved                                             |

|         | 00110 = Reserved                                             |

|         | 00101 = Reserved                                             |

|         | 00100 = OC4 module synchronizes or triggers $OCx^{(1,2)}$    |

|         | 00011 = OC3 module synchronizes or triggers $OCx^{(1,2)}$    |

|         | 00010 = OC2 module synchronizes or triggers $OCx^{(1,2)}$    |

|         | 00001 = OC1 module synchronizes or triggers $OCx^{(1,2)}$    |

|         | 00000 = No Sync or Trigger source for OCx                    |

- **Note 1:** Do not use the OCx module as its own Synchronization or Trigger source.

- 2: When the OCy module is turned OFF, it sends a trigger out signal. If the OCx module uses the OCy module as a Trigger source, the OCy module must be unselected as a Trigger source prior to disabling it.

- Each Output Compare x module (OCx) has one PTG Trigger/Synchronization source. See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for more information. PTGO0 = OC1

PTGO0 = OC1 PTGO1 = OC2 PTGO2 = OC3PTGO3 = OC4

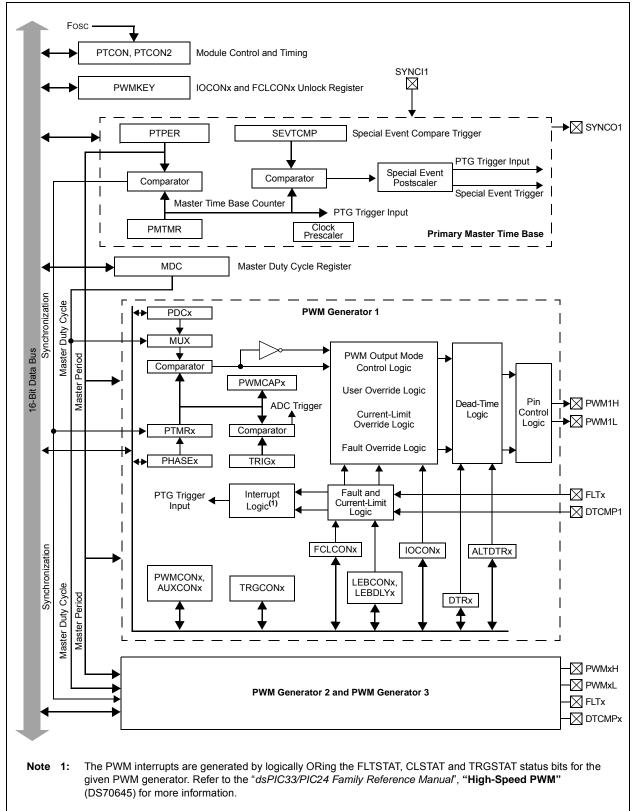

#### FIGURE 16-2: HIGH-SPEED PWMx MODULE REGISTER INTERCONNECTION DIAGRAM

| R/W-0         | R/W-0                                  | R/W-0                                 | R/W-0            | R/W-0              | R/W-0           | R/W-0           | R/W-0    |  |  |  |

|---------------|----------------------------------------|---------------------------------------|------------------|--------------------|-----------------|-----------------|----------|--|--|--|

| EDG1MOD       | EDG1POL                                | EDG1SEL3                              | EDG1SEL2         | EDG1SEL1           | EDG1SEL0        | EDG2STAT        | EDG1STAT |  |  |  |

| bit 15        |                                        | 1                                     |                  | 11                 |                 |                 | bit 8    |  |  |  |

|               |                                        |                                       |                  |                    |                 |                 |          |  |  |  |

| R/W-0         | R/W-0                                  | R/W-0                                 | R/W-0            | R/W-0              | R/W-0           | U-0             | U-0      |  |  |  |

| EDG2MOD       | EDG2POL                                | EDG2SEL3                              | EDG2SEL2         | EDG2SEL1           | EDG2SEL0        | —               | _        |  |  |  |

| bit 7         |                                        |                                       |                  | 1 1                |                 | 1               | bit (    |  |  |  |

|               |                                        |                                       |                  |                    |                 |                 |          |  |  |  |

| Legend:       |                                        |                                       |                  |                    |                 |                 |          |  |  |  |

| R = Readabl   | le bit                                 | W = Writable                          | oit              | U = Unimplem       | ented bit, read | l as '0'        |          |  |  |  |

| -n = Value at | POR                                    | '1' = Bit is set                      |                  | '0' = Bit is clea  | red             | x = Bit is unkr | nown     |  |  |  |

|               |                                        |                                       |                  |                    |                 |                 |          |  |  |  |

| bit 15        | EDG1MOD: E                             | Edge 1 Edge Sa                        | ampling Mode     | Selection bit      |                 |                 |          |  |  |  |

|               | 1 = Edge 1 is                          | s edge-sensitive                      | 9                |                    |                 |                 |          |  |  |  |

|               | •                                      | s level-sensitive                     |                  |                    |                 |                 |          |  |  |  |

| bit 14        |                                        | dge 1 Polarity                        |                  |                    |                 |                 |          |  |  |  |

|               |                                        | s programmed f                        |                  |                    |                 |                 |          |  |  |  |

| L:1 40 40     | •                                      | s programmed f                        | •                | •                  |                 |                 |          |  |  |  |

| bit 13-10     |                                        | :0>: Edge 1 So                        | urce Select bits | 5                  |                 |                 |          |  |  |  |

|               | 1xxx = Reserved<br>01xx = Reserved     |                                       |                  |                    |                 |                 |          |  |  |  |

|               |                                        | 0011 = CTED1 pin                      |                  |                    |                 |                 |          |  |  |  |

|               | 0010 = CTED2 pin                       |                                       |                  |                    |                 |                 |          |  |  |  |

|               | 0001 = OC1                             |                                       |                  |                    |                 |                 |          |  |  |  |

| hit O         | 0000 = Timer                           |                                       | :+               |                    |                 |                 |          |  |  |  |

| bit 9         |                                        | Edge 2 Status b                       |                  | vritten to control | the odge cou    | reo             |          |  |  |  |

|               | 1 = Edge 2 h                           |                                       |                  |                    | the edge sou    | ice.            |          |  |  |  |

|               |                                        | as not occurred                       | 1                |                    |                 |                 |          |  |  |  |

| bit 8         | EDG1STAT: E                            | Edge 1 Status b                       | it               |                    |                 |                 |          |  |  |  |

|               |                                        |                                       | 1 and can be v   | vritten to control | the edge sou    | rce.            |          |  |  |  |

|               | 1 = Edge 1 h                           |                                       |                  |                    |                 |                 |          |  |  |  |

|               | -                                      | as not occurred                       |                  |                    |                 |                 |          |  |  |  |

| bit 7         |                                        | Edge 2 Edge Sa                        |                  | Selection bit      |                 |                 |          |  |  |  |

|               |                                        | s edge-sensitive<br>s level-sensitive |                  |                    |                 |                 |          |  |  |  |

| bit 6         | •                                      | dge 2 Polarity                        |                  |                    |                 |                 |          |  |  |  |

| Sit 0         |                                        | s programmed f                        |                  | dae response       |                 |                 |          |  |  |  |

|               |                                        | s programmed f                        |                  |                    |                 |                 |          |  |  |  |

| bit 5-2       | EDG2SEL<3                              | :0>: Edge 2 So                        | urce Select bits | 3                  |                 |                 |          |  |  |  |

|               | 1111 <b>= Rese</b>                     | rved                                  |                  |                    |                 |                 |          |  |  |  |

|               | 01xx = Rese                            |                                       |                  |                    |                 |                 |          |  |  |  |

|               | 0100 = CMP <sup>2</sup><br>0011 = CTEE |                                       |                  |                    |                 |                 |          |  |  |  |

|               | 0010 = CTEE                            |                                       |                  |                    |                 |                 |          |  |  |  |

|               |                                        | Ji pili                               |                  |                    |                 |                 |          |  |  |  |

|               | 0001 = OC1                             | module                                |                  |                    |                 |                 |          |  |  |  |

|               |                                        | module                                |                  |                    |                 |                 |          |  |  |  |

#### REGISTER 22-2: CTMUCON2: CTMU CONTROL REGISTER 2

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

## REGISTER 24-4: PTGT0LIM: PTG TIMER0 LIMIT REGISTER<sup>(1)</sup>

| R/W-0           | R/W-0                                                                      | R/W-0          | R/W-0 | R/W-0        | R/W-0           | R/W-0    | R/W-0 |

|-----------------|----------------------------------------------------------------------------|----------------|-------|--------------|-----------------|----------|-------|

|                 |                                                                            |                | PTGT0 | _IM<15:8>    |                 |          |       |

| bit 15          |                                                                            |                |       |              |                 |          | bit 8 |

|                 |                                                                            |                |       |              |                 |          |       |

| R/W-0           | R/W-0                                                                      | R/W-0          | R/W-0 | R/W-0        | R/W-0           | R/W-0    | R/W-0 |

|                 |                                                                            |                | PTGT0 | LIM<7:0>     |                 |          |       |

| bit 7           |                                                                            |                |       |              |                 |          | bit 0 |

|                 |                                                                            |                |       |              |                 |          |       |

| Legend:         |                                                                            |                |       |              |                 |          |       |

| R = Readable    | bit                                                                        | W = Writable b | bit   | U = Unimplem | nented bit, rea | d as '0' |       |

| -n = Value at P | -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |                |       |              |                 | nown     |       |

#### bit 15-0 **PTGT0LIM<15:0>:** PTG Timer0 Limit Register bits General Purpose Timer0 Limit register (effective only with a PTGT0 Step command).

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

## REGISTER 24-5: PTGT1LIM: PTG TIMER1 LIMIT REGISTER<sup>(1)</sup>

| R/W-0  | R/W-0 | R/W-0 | R/W-0   | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|---------|----------|-------|-------|-------|

|        |       |       | PTGT1LI | IM<15:8> |       |       |       |

| bit 15 |       |       |         |          |       |       | bit 8 |

|        |       |       |         |          |       |       |       |

| R/W-0 | R/W-0         | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |  |

|-------|---------------|-------|-------|-------|-------|-------|-------|--|--|--|--|

|       | PTGT1LIM<7:0> |       |       |       |       |       |       |  |  |  |  |

| bit 7 |               |       |       |       |       |       | bit 0 |  |  |  |  |

| Legend:           |                  |                                    |                    |

|-------------------|------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

bit 15-0 **PTGT1LIM<15:0>:** PTG Timer1 Limit Register bits

General Purpose Timer1 Limit register (effective only with a PTGT1 Step command).

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

NOTES:

#### REGISTER 25-4: CMxMSKSRC: COMPARATOR x MASK SOURCE SELECT CONTROL REGISTER (CONTINUED)

- bit 3-0 SELSRCA<3:0>: Mask A Input Select bits

- 1111 = FLT4 1110 = FLT2 1101 = PTGO19 1100 = PTGO18 1011 = Reserved 1010 = Reserved 1001 = Reserved 1000 = Reserved 0111 = Reserved 0110 = Reserved 0101 = PWM3H 0100 = PWM3L 0011 = PWM2H 0010 = PWM2L 0001 = PWM1H 0000 = PWM1L

NOTES:

NOTES:

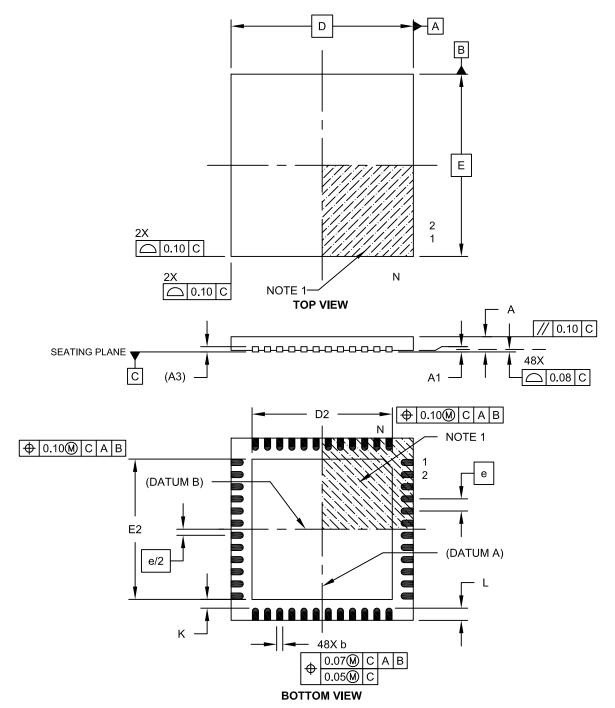

#### 48-Lead Plastic Ultra Thin Quad Flat, No Lead Package (MV) – 6x6x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-153A Sheet 1 of 2

## TABLE A-1:MAJOR SECTION UPDATES (CONTINUED)

| Section Name                                 | Update Description                                                                                                                                                       |  |  |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Section 30.0 "Electrical<br>Characteristics" | Removed Voltage on VCAP with respect to Vss and added Note 5 in Absolute Maximum Ratings <sup>(1)</sup> .                                                                |  |  |

|                                              | Removed Parameter DC18 (VCORE) and Note 3 from the DC Temperature and Voltage Specifications (see Table 30-4).                                                           |  |  |

|                                              | Updated Note 1 in the DC Characteristics: Operating Current (IDD) (see Table 30-6).                                                                                      |  |  |

|                                              | Updated Note 1 in the DC Characteristics: Idle Current (IIDLE) (see Table 30-7).                                                                                         |  |  |

|                                              | Changed the Typical values for Parameters DC60a-DC60d and updated Note 1 in the DC Characteristics: Power-down Current (IPD) (see Table 30-8).                           |  |  |

|                                              | Updated Note 1 in the DC Characteristics: Doze Current (IDOZE) (see Table 30-9).                                                                                         |  |  |

|                                              | Updated Note 2 in the Electrical Characteristics: BOR (see Table 30-12).                                                                                                 |  |  |

|                                              | Updated Parameters CM20 and CM31, and added Parameters CM44 and CM45 in the AC/DC Characteristics: Op amp/Comparator (see Table 30-14).                                  |  |  |

|                                              | Added the Op amp/Comparator Reference Voltage Settling Time Specifications (see Table 30-15).                                                                            |  |  |

|                                              | Added Op amp/Comparator Voltage Reference DC Specifications (see Table 30-16).                                                                                           |  |  |

|                                              | Updated Internal FRC Accuracy Parameter F20a (see Table 30-21).                                                                                                          |  |  |

|                                              | Updated the Typical value and Units for Parameter CTMUI1, and added Parameters CTMUI4, CTMUFV1, and CTMUFV2 to the CTMU Current Source Specifications (see Table 30-55). |  |  |

| Section 31.0 "Packaging<br>Information"      | Updated packages by replacing references of VLAP with TLA.                                                                                                               |  |  |

| "Product Identification<br>System"           | Changed VLAP to TLA.                                                                                                                                                     |  |  |

NOTES: