#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 70 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 32KB (10.7K x 24)                                                              |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 2K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 6x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                 |

| Supplier Device Package    | 28-SOIC                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep32gp202t-i-so |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name <sup>(4)</sup>                        | Pin<br>Type         | Buffer<br>Type          | PPS              | Description                                                                                                                                                                        |

|------------------------------------------------|---------------------|-------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AN0-AN15                                       | I                   | Analog                  | No               | Analog input channels.                                                                                                                                                             |

| CLKI                                           | I                   | ST/<br>CMOS             | No               | External clock source input. Always associated with OSC1 pin function                                                                                                              |

| CLKO                                           | 0                   | —                       | No               | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes. Always associated with OSC2 pin function. |

| OSC1                                           | I                   | ST/                     | No               | Oscillator crystal input. ST buffer when configured in RC mode; CMOS                                                                                                               |

| OSC2                                           | I/O                 | CMOS<br>—               | No               | otherwise.<br>Oscillator crystal output. Connects to crystal or resonator in Crystal<br>Oscillator mode. Optionally functions as CLKO in RC and EC modes.                          |

| REFCLKO                                        | 0                   |                         | Yes              | Reference clock output.                                                                                                                                                            |

| IC1-IC4                                        | Ι                   | ST                      | Yes              | Capture Inputs 1 through 4.                                                                                                                                                        |

| OCFA<br>OCFB<br>OC1-OC4                        | <br> <br> <br>0     | ST<br>ST                | Yes<br>No<br>Yes | Compare Fault A input (for Compare channels).<br>Compare Fault B input (for Compare channels).<br>Compare Outputs 1 through 4.                                                     |

| INT0                                           |                     | ST                      | No               | External Interrupt 0.                                                                                                                                                              |

| INT1<br>INT2                                   |                     | ST<br>ST                | Yes<br>Yes       | External Interrupt 1.<br>External Interrupt 2.                                                                                                                                     |

| RA0-RA4, RA7-RA12                              | I/O                 | ST                      | No               | PORTA is a bidirectional I/O port.                                                                                                                                                 |

| RB0-RB15                                       | I/O                 | ST                      | No               | PORTB is a bidirectional I/O port.                                                                                                                                                 |

| RC0-RC13, RC15                                 | I/O                 | ST                      | No               | PORTC is a bidirectional I/O port.                                                                                                                                                 |

| RD5, RD6, RD8                                  | I/O                 | ST                      | No               | PORTD is a bidirectional I/O port.                                                                                                                                                 |

| RE12-RE15                                      | I/O                 | ST                      | No               | PORTE is a bidirectional I/O port.                                                                                                                                                 |

| RF0, RF1                                       | I/O                 | ST                      | No               | PORTF is a bidirectional I/O port.                                                                                                                                                 |

| RG6-RG9                                        | I/O                 | ST                      | No               | PORTG is a bidirectional I/O port.                                                                                                                                                 |

| T1CK                                           | Ι                   | ST                      | No               | Timer1 external clock input.                                                                                                                                                       |

| T2CK<br>T3CK                                   |                     | ST<br>ST                | Yes              | Timer2 external clock input.                                                                                                                                                       |

| T4CK                                           |                     | ST                      | No<br>No         | Timer3 external clock input.<br>Timer4 external clock input.                                                                                                                       |

| T5CK                                           | i                   | ST                      | No               | Timer5 external clock input.                                                                                                                                                       |

| CTPLS                                          | 0                   | ST                      | No               | CTMU pulse output.                                                                                                                                                                 |

| CTED1                                          | Ι                   | ST                      | No               | CTMU External Edge Input 1.                                                                                                                                                        |

| CTED2                                          | Ι                   | ST                      | No               | CTMU External Edge Input 2.                                                                                                                                                        |

| U1CTS                                          | Ι                   | ST                      | No               | UART1 Clear-To-Send.                                                                                                                                                               |

| U1RTS                                          | 0                   |                         | No               | UART1 Ready-To-Send.                                                                                                                                                               |

| U1RX                                           |                     | ST                      | Yes              | UART1 receive.<br>UART1 transmit.                                                                                                                                                  |

| U1TX<br>BCLK1                                  | 0                   | ST                      | Yes<br>No        | UART1 Iransmit.<br>UART1 IrDA <sup>®</sup> baud clock output.                                                                                                                      |

| Legend: CMOS = CM<br>ST = Schmi<br>PPS = Perip | MOS co<br>itt Trigg | ompatible<br>er input v | input<br>with CN | or output Analog = Analog input P = Power                                                                                                                                          |

### TABLE 1-1:PINOUT I/O DESCRIPTIONS

Note 1: This pin is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This pin is available on dsPIC33EPXXXGP/MC50X devices only.

3: This is the default Fault on Reset for dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices. See Section 16.0 "High-Speed PWM Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)" for more information.

4: Not all pins are available in all packages variants. See the "Pin Diagrams" section for pin availability.

**5:** There is an internal pull-up resistor connected to the TMS pin when the JTAG interface is active. See the JTAGEN bit field in Table 27-2.

### TABLE 4-4: INTERRUPT CONTROLLER REGISTER MAP FOR PIC24EPXXXMC20X DEVICES ONLY (CONTINUED)

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8 | Bit 7 | Bit 6   | Bit 5       | Bit 4   | Bit 3   | Bit 2  | Bit 1       | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|------------|--------|--------|--------|------------|-------|-------|---------|-------------|---------|---------|--------|-------------|--------|---------------|

| IPC35        | 0886  | _      |        | JTAGIP<2:0 | >      | _      |        | ICDIP<2:0  | >     |       | —       | _           | _       | —       | _      | —           |        | 4400          |

| IPC36        | 0888  | _      | F      | PTG0IP<2:0 | >      | _      | PT     | GWDTIP<    | 2:0>  |       | PT      | GSTEPIP<2   | :0>     | —       | —      | —           | -      | 4440          |

| IPC37        | 088A  | _      | —      | —          | _      | _      | F      | PTG3IP<2:0 | )>    |       |         | PTG2IP<2:0> | >       | _       |        | PTG1IP<2:0> |        | 0444          |

| INTCON1      | 08C0  | NSTDIS | OVAERR | OVBERR     |        |        |        | _          | _     | _     | DIV0ERR | DMACERR     | MATHERR | ADDRERR | STKERR | OSCFAIL     | _      | 0000          |

| INTCON2      | 08C2  | GIE    | DISI   | SWTRAP     | _      | _      |        |            | —     |       | _       | —           | —       | _       | INT2EP | INT1EP      | INT0EP | 8000          |

| INTCON3      | 08C4  | _      | —      | —          | _      | _      |        |            | —     |       | _       | DAE         | DOOVR   | _       | —      | —           |        | 0000          |

| INTCON4      | 08C6  | _      | _      | _          | _      | _      | -      | _          | —     | _     | _       | _           | _       | —       | —      | —           | SGHT   | 0000          |

| INTTREG      | 08C8  | Ι      | _      | _          | _      |        | ILR<   | 3:0>       |       |       |         |             | VECN    | UM<7:0> |        |             |        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Allocating different Page registers for read and write access allows the architecture to support data movement between different pages in data memory. This is accomplished by setting the DSRPAG register value to the page from which you want to read, and configuring the DSWPAG register to the page to which it needs to be written. Data can also be moved from different PSV to EDS pages, by configuring the DSRPAG and DSWPAG registers to address PSV and EDS space, respectively. The data can be moved between pages by a single instruction.

When an EDS or PSV page overflow or underflow occurs, EA<15> is cleared as a result of the register indirect EA calculation. An overflow or underflow of the EA in the EDS or PSV pages can occur at the page boundaries when:

- The initial address prior to modification addresses an EDS or PSV page

- The EA calculation uses Pre-Modified or Post-Modified Register Indirect Addressing; however, this does not include Register Offset Addressing

In general, when an overflow is detected, the DSxPAG register is incremented and the EA<15> bit is set to keep the base address within the EDS or PSV window. When an underflow is detected, the DSxPAG register is decremented and the EA<15> bit is set to keep the base address within the EDS or PSV window. This creates a linear EDS and PSV address space, but only when using Register Indirect Addressing modes.

Exceptions to the operation described above arise when entering and exiting the boundaries of Page 0, EDS and PSV spaces. Table 4-61 lists the effects of overflow and underflow scenarios at different boundaries.

In the following cases, when overflow or underflow occurs, the EA<15> bit is set and the DSxPAG is not modified; therefore, the EA will wrap to the beginning of the current page:

- · Register Indirect with Register Offset Addressing

- Modulo Addressing

- · Bit-Reversed Addressing

|             | -                   | SV SI ACE BOON |              |                        |                |              |                        |  |

|-------------|---------------------|----------------|--------------|------------------------|----------------|--------------|------------------------|--|

| 0/11        |                     |                | Before       |                        | After          |              |                        |  |

| O/U,<br>R/W | Operation           | DSxPAG         | DS<br>EA<15> | Page<br>Description    | DSxPAG         | DS<br>EA<15> | Page<br>Description    |  |

| O,<br>Read  |                     | DSRPAG = 0x1FF | 1            | EDS: Last page         | DSRPAG = 0x1FF | 0            | See Note 1             |  |

| O,<br>Read  | [++Wn]              | DSRPAG = 0x2FF | 1            | PSV: Last lsw<br>page  | DSRPAG = 0x300 | 1            | PSV: First MSB<br>page |  |

| O,<br>Read  | <b>Or</b><br>[Wn++] | DSRPAG = 0x3FF | 1            | PSV: Last MSB<br>page  | DSRPAG = 0x3FF | 0            | See Note 1             |  |

| O,<br>Write |                     | DSWPAG = 0x1FF | 1            | EDS: Last page         | DSWPAG = 0x1FF | 0            | See Note 1             |  |

| U,<br>Read  |                     | DSRPAG = 0x001 | 1            | PSV page               | DSRPAG = 0x001 | 0            | See Note 1             |  |

| U,<br>Read  | [Wn]<br>Or<br>[Wn]  | DSRPAG = 0x200 | 1            | PSV: First Isw<br>page | DSRPAG = 0x200 | 0            | See Note 1             |  |

| U,<br>Read  | [ //11 - ]          | DSRPAG = 0x300 | 1            | PSV: First MSB<br>page | DSRPAG = 0x2FF | 1            | PSV: Last Isw<br>page  |  |

# TABLE 4-61: OVERFLOW AND UNDERFLOW SCENARIOS AT PAGE 0, EDS and PSV SPACE BOUNDARIES<sup>(2,3,4)</sup>

Legend: O = Overflow, U = Underflow, R = Read, W = Write

Note 1: The Register Indirect Addressing now addresses a location in the base Data Space (0x0000-0x8000).

2: An EDS access with DSxPAG = 0x000 will generate an address error trap.

- **3:** Only reads from PS are supported using DSRPAG. An attempt to write to PS using DSWPAG will generate an address error trap.

- 4: Pseudo-Linear Addressing is not supported for large offsets.

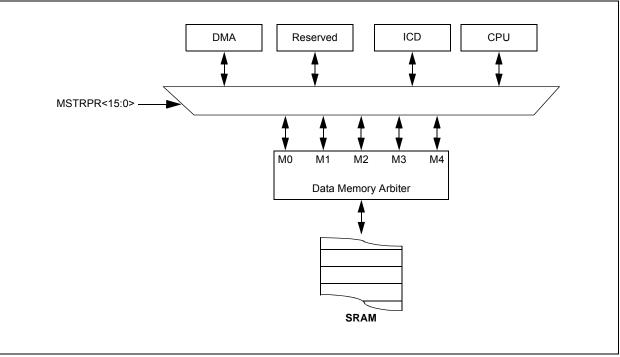

# 4.4.3 DATA MEMORY ARBITRATION AND BUS MASTER PRIORITY

EDS accesses from bus masters in the system are arbitrated.

The arbiter for data memory (including EDS) arbitrates between the CPU, the DMA and the ICD module. In the event of coincidental access to a bus by the bus masters, the arbiter determines which bus master access has the highest priority. The other bus masters are suspended and processed after the access of the bus by the bus master with the highest priority.

By default, the CPU is Bus Master 0 (M0) with the highest priority and the ICD is Bus Master 4 (M4) with the lowest priority. The remaining bus master (DMA Controller) is allocated to M3 (M1 and M2 are reserved and cannot be used). The user application may raise or lower the priority of the DMA Controller to be above that of the CPU by setting the appropriate bits in the EDS Bus Master Priority Control (MSTRPR) register. All bus masters with raised priorities will maintain the same priority relationship relative to each other (i.e., M1 being highest and M3 being lowest, with M2 in between). Also, all the bus masters with priorities below

### FIGURE 4-18: ARBITER ARCHITECTURE

that of the CPU maintain the same priority relationship relative to each other. The priority schemes for bus masters with different MSTRPR values are tabulated in Table 4-62.

This bus master priority control allows the user application to manipulate the real-time response of the system, either statically during initialization or dynamically in response to real-time events.

| TABLE 4-62: | DATA MEMORY BUS  |

|-------------|------------------|

|             | ARBITER PRIORITY |

| Drierity     | MSTRPR<15:0> Bit Setting <sup>(1)</sup> |          |  |  |  |  |

|--------------|-----------------------------------------|----------|--|--|--|--|

| Priority     | 0x0000                                  | 0x0020   |  |  |  |  |

| M0 (highest) | CPU                                     | DMA      |  |  |  |  |

| M1           | Reserved                                | CPU      |  |  |  |  |

| M2           | Reserved                                | Reserved |  |  |  |  |

| M3           | DMA                                     | Reserved |  |  |  |  |

| M4 (lowest)  | ICD                                     | ICD      |  |  |  |  |

**Note 1:** All other values of MSTRPR<15:0> are reserved.

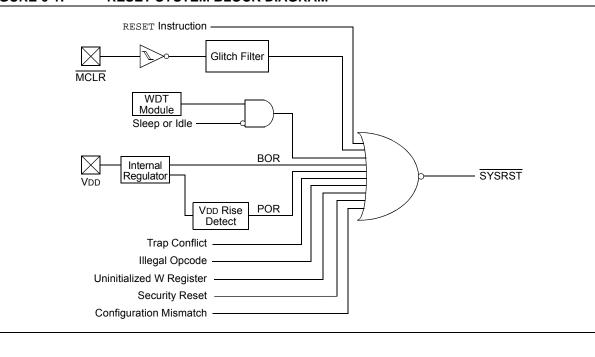

### 6.0 RESETS

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Reset" (DS70602) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- · POR: Power-on Reset

- · BOR: Brown-out Reset

- MCLR: Master Clear Pin Reset

- SWR: RESET Instruction

- WDTO: Watchdog Timer Time-out Reset

- CM: Configuration Mismatch Reset

- TRAPR: Trap Conflict Reset

- IOPUWR: Illegal Condition Device Reset

- Illegal Opcode Reset

- Uninitialized W Register Reset

- Security Reset

FIGURE 6-1: RESET SYSTEM BLOCK DIAGRAM

A simplified block diagram of the Reset module is shown in Figure 6-1.

Any active source of Reset will make the SYSRST signal active. On system Reset, some of the registers associated with the CPU and peripherals are forced to a known Reset state and some are unaffected.

Note: Refer to the specific peripheral section or Section 4.0 "Memory Organization" of this manual for register Reset states.

All types of device Reset set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 6-1).

A POR clears all the bits, except for the POR and BOR bits (RCON<1:0>), that are set. The user application can set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software does not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer and device power-saving states. The function of these bits is discussed in other sections of this manual.

**Note:** The status bits in the RCON register should be cleared after they are read so that the next RCON register value after a device Reset is meaningful.

For all Resets, the default clock source is determined by the FNOSC<2:0> bits in the FOSCSEL Configuration register. The value of the FNOSC<2:0> bits is loaded into NOSC<2:0> (OSCCON<10:8>) on Reset, which in turn, initializes the system clock.

|                 | 12. 2007.00    |                                       |              |                   |                  |                 |        |

|-----------------|----------------|---------------------------------------|--------------|-------------------|------------------|-----------------|--------|

| U-0             | U-0            | U-0                                   | U-0          | U-0               | U-0              | U-0             | U-0    |

| —               | —              | —                                     | —            | —                 | —                | —               | —      |

| bit 15          |                |                                       |              |                   |                  |                 | bit 8  |

|                 |                |                                       |              |                   |                  |                 |        |

| U-0             | U-0            | U-0                                   | U-0          | R-0               | R-0              | R-0             | R-0    |

| —               |                | —                                     | —            | RQCOL3            | RQCOL2           | RQCOL1          | RQCOL0 |

| bit 7           |                |                                       |              |                   |                  |                 | bit 0  |

|                 |                |                                       |              |                   |                  |                 |        |

| Legend:         |                |                                       |              |                   |                  |                 |        |

| R = Readable    | bit            | W = Writable                          | bit          | U = Unimpler      | mented bit, read | l as '0'        |        |

| -n = Value at F | POR            | '1' = Bit is set                      |              | '0' = Bit is cle  | ared             | x = Bit is unkr | nown   |

|                 |                |                                       |              |                   |                  |                 |        |

| bit 15-4        | Unimplemen     | ted: Read as '                        | כ'           |                   |                  |                 |        |

| bit 3           | RQCOL3: DN     | /IA Channel 3 T                       | ransfer Requ | est Collision F   | ag bit           |                 |        |

|                 |                | e and interrupt<br>est collision is d |              | st collision is d | etected          |                 |        |

| <b>h</b> # 0    | •              |                                       |              | est Callisian Fl  | aa hit           |                 |        |

| bit 2           |                | /IA Channel 2 T<br>ce and interrupt   | •            |                   | 0                |                 |        |

|                 |                | e and interrupt<br>est collision is d |              |                   | elecieu          |                 |        |

| bit 1           | RQCOL1: DN     | /IA Channel 1 T                       | ransfer Requ | est Collision F   | ag bit           |                 |        |

|                 | 1 = User for   | e and interrupt                       | -based reque | st collision is d | etected          |                 |        |

|                 | 0 = No reque   | est collision is d                    | etected      |                   |                  |                 |        |

| bit 0           | RQCOLO: DN     | /IA Channel 0 T                       | ransfer Requ | est Collision F   | lag bit          |                 |        |

|                 | 1 = User force | e and interrupt                       | -based reque | st collision is d | etected          |                 |        |

### REGISTER 8-12: DMARQC: DMA REQUEST COLLISION STATUS REGISTER

0 = No request collision is detected

| U-0     | U-0 | U-0   | U-0   | U-0   | U-0   | U-0   | U-0   |

|---------|-----|-------|-------|-------|-------|-------|-------|

| —       | —   | —     | —     | —     | —     | —     | —     |

| bit 15  |     |       |       |       |       |       | bit 8 |

|         |     |       |       |       |       |       |       |

| U-0     | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| —       | —   | TUN5  | TUN4  | TUN3  | TUN2  | TUN1  | TUN0  |

| bit 7   |     |       |       |       |       |       | bit 0 |

|         |     |       |       |       |       |       |       |

| Logondi |     |       |       |       |       |       |       |

### REGISTER 9-4: OSCTUN: FRC OSCILLATOR TUNING REGISTER

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-6 Unimplemented: Read as '0'

bit 5-0 **TUN<5:0>:** FRC Oscillator Tuning bits 011111 = Maximum frequency deviation of 1.453% (7.477 MHz) 011110 = Center frequency + 1.406% (7.474 MHz) •••• 000001 = Center frequency + 0.047% (7.373 MHz) 000000 = Center frequency (7.37 MHz nominal) 111111 = Center frequency - 0.047% (7.367 MHz) ••• 100001 = Center frequency - 1.453% (7.263 MHz) 100000 = Minimum frequency deviation of -1.5% (7.259 MHz)

### 11.5 I/O Helpful Tips

- 1. In some cases, certain pins, as defined in Table 30-11, under "Injection Current", have internal protection diodes to VDD and Vss. The term, "Injection Current", is also referred to as "Clamp Current". On designated pins, with sufficient external current-limiting precautions by the user, I/O pin input voltages are allowed to be greater or less than the data sheet absolute maximum ratings, with respect to the Vss and VDD supplies. Note that when the user application forward biases either of the high or low side internal input clamp diodes, that the resulting current being injected into the device, that is clamped internally by the VDD and Vss power rails, may affect the ADC accuracy by four to six counts.

- 2. I/O pins that are shared with any analog input pin (i.e., ANx) are always analog pins by default after any Reset. Consequently, configuring a pin as an analog input pin automatically disables the digital input pin buffer and any attempt to read the digital input level by reading PORTx or LATx will always return a '0', regardless of the digital logic level on the pin. To use a pin as a digital I/O pin on a shared ANx pin, the user application needs to configure the Analog Pin Configuration registers in the I/O ports module (i.e., ANSELx) by setting the appropriate bit that corresponds to that I/O port pin to a '0'.

- **Note:** Although it is not possible to use a digital input pin when its analog function is enabled, it is possible to use the digital I/O output function, TRISx = 0x0, while the analog function is also enabled. However, this is not recommended, particularly if the analog input is connected to an external analog voltage source, which would create signal contention between the analog signal and the output pin driver.

- 3. Most I/O pins have multiple functions. Referring to the device pin diagrams in this data sheet, the priorities of the functions allocated to any pins are indicated by reading the pin name from left-to-right. The left most function name takes precedence over any function to its right in the naming convention. For example: AN16/T2CK/T7CK/RC1. This indicates that AN16 is the highest priority in this example and will supersede all other functions to its right in the list. Those other functions to its right, even if enabled, would not work as long as any other function to its left was enabled. This rule applies to all of the functions listed for a given pin.

- 4. Each pin has an internal weak pull-up resistor and pull-down resistor that can be configured using the CNPUx and CNPDx registers, respectively. These resistors eliminate the need for external resistors in certain applications. The internal pull-up is up to ~(VDD - 0.8), not VDD. This value is still above the minimum VIH of CMOS and TTL devices.

5. When driving LEDs directly, the I/O pin can source or sink more current than what is specified in the VOH/IOH and VOL/IOL DC characteristic specification. The respective IOH and IOL current rating only applies to maintaining the corresponding output at or above the VOH, and at or below the VOL levels. However, for LEDs, unlike digital inputs of an externally connected device, they are not governed by the same minimum VIH/VIL levels. An I/O pin output can safely sink or source any current less than that listed in the absolute maximum rating section of this data sheet. For example:

VOH = 2.4V @ IOH = -8 mA and VDD = 3.3VThe maximum output current sourced by any 8 mA I/O pin = 12 mA.

LED source current < 12 mA is technically permitted. Refer to the VOH/IOH graphs in Section 30.0 "Electrical Characteristics" for additional information.

- 6. The Peripheral Pin Select (PPS) pin mapping rules are as follows:

- a) Only one "output" function can be active on a given pin at any time, regardless if it is a dedicated or remappable function (one pin, one output).

- b) It is possible to assign a "remappable output" function to multiple pins and externally short or tie them together for increased current drive.

- c) If any "dedicated output" function is enabled on a pin, it will take precedence over any remappable "output" function.

- d) If any "dedicated digital" (input or output) function is enabled on a pin, any number of "input" remappable functions can be mapped to the same pin.

- e) If any "dedicated analog" function(s) are enabled on a given pin, "digital input(s)" of any kind will all be disabled, although a single "digital output", at the user's cautionary discretion, can be enabled and active as long as there is no signal contention with an external analog input signal. For example, it is possible for the ADC to convert the digital output logic level, or to toggle a digital output on a comparator or ADC input provided there is no external analog input, such as for a built-in self-test.

- f) Any number of "input" remappable functions can be mapped to the same pin(s) at the same time, including to any pin with a single output from either a dedicated or remappable "output".

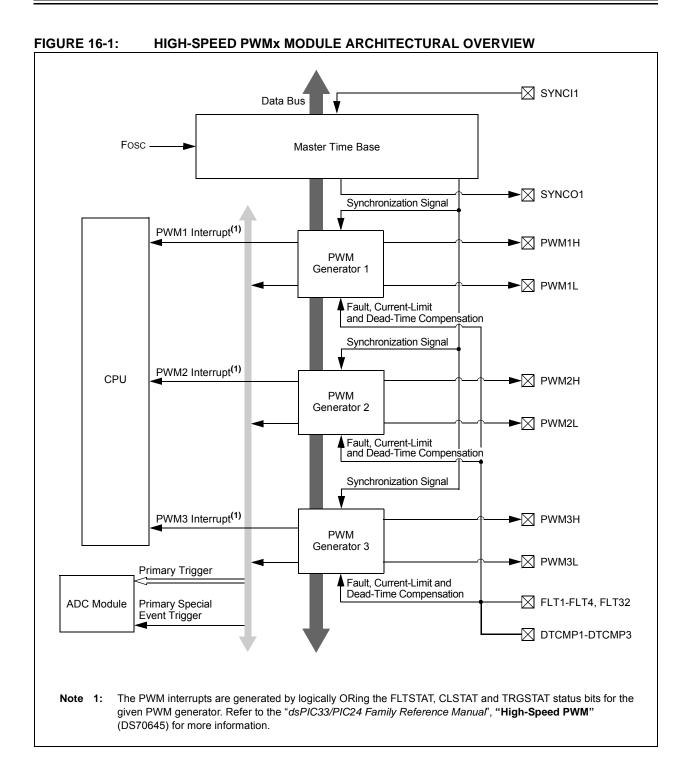

| REGISTER 16-2: | PTCON2: PWMx PRIMARY MASTER CLOCK DIVIDER SELECT REGISTER 2 |

|----------------|-------------------------------------------------------------|

|----------------|-------------------------------------------------------------|

| U-0                                                                        | U-0        | U-0            | U-0 | U-0          | U-0                     | U-0                     | U-0         |

|----------------------------------------------------------------------------|------------|----------------|-----|--------------|-------------------------|-------------------------|-------------|

| —                                                                          | —          | —              | _   | —            | —                       | —                       | _           |

| bit 15                                                                     |            |                |     |              |                         |                         | bit 8       |

|                                                                            |            |                |     |              |                         |                         |             |

| U-0                                                                        | U-0        | U-0            | U-0 | U-0          | R/W-0                   | R/W-0                   | R/W-0       |

| —                                                                          | —          | —              | _   | —            | PCLKDIV2 <sup>(1)</sup> | PCLKDIV1 <sup>(1)</sup> | PCLKDIV0(1) |

| bit 7                                                                      |            |                |     |              |                         |                         | bit 0       |

|                                                                            |            |                |     |              |                         |                         |             |

| Legend:                                                                    |            |                |     |              |                         |                         |             |

| R = Readable                                                               | bit        | W = Writable   | bit | U = Unimpler | mented bit, read        | as '0'                  |             |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |            |                |     |              |                         |                         | own         |

|                                                                            |            |                |     |              |                         |                         |             |

| bit 15-3                                                                   | Unimplemen | ted: Read as ' | י'  |              |                         |                         |             |

#### bit 15-3 Unimplemented: Read as '0'

bit 2-0 PCLKDIV<2:0>: PWMx Input Clock Prescaler (Divider) Select bits<sup>(1)</sup>

- 111 = Reserved 110 = Divide-by-64 101 = Divide-by-32

- 100 = Divide-by-32100 = Divide-by-16

- 011 = Divide-by-8

- 010 = Divide-by-4

- 001 = Divide-by-2

- 000 = Divide-by-1, maximum PWMx timing resolution (power-on default)

- **Note 1:** These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

### REGISTER 16-8: PDCx: PWMx GENERATOR DUTY CYCLE REGISTER

| R/W-0                                                                      | R/W-0                                                                | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|----------------------------------------------------------------------------|----------------------------------------------------------------------|-------|-------|--------|-------|-------|-------|--|--|--|

|                                                                            |                                                                      |       | PDC   | <15:8> |       |       |       |  |  |  |

| bit 15 bit 8                                                               |                                                                      |       |       |        |       |       |       |  |  |  |

|                                                                            |                                                                      |       |       |        |       |       |       |  |  |  |

| R/W-0                                                                      | R/W-0                                                                | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|                                                                            |                                                                      |       | PDC   | x<7:0> |       |       |       |  |  |  |

| bit 7                                                                      |                                                                      |       |       |        |       |       | bit 0 |  |  |  |

|                                                                            |                                                                      |       |       |        |       |       |       |  |  |  |

| Legend:                                                                    |                                                                      |       |       |        |       |       |       |  |  |  |

| R = Readable                                                               | R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |       |       |        |       |       |       |  |  |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |                                                                      |       |       |        |       |       | nown  |  |  |  |

bit 15-0 **PDCx<15:0>:** PWMx Generator # Duty Cycle Value bits

### REGISTER 16-9: PHASEx: PWMx PRIMARY PHASE-SHIFT REGISTER

| R/W-0                                                              | R/W-0 | R/W-0           | R/W-0                              | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|--------------------------------------------------------------------|-------|-----------------|------------------------------------|----------|-------|-------|-------|

|                                                                    |       |                 | PHAS                               | Ex<15:8> |       |       |       |

| bit 15                                                             |       |                 |                                    |          |       |       | bit 8 |

|                                                                    |       |                 |                                    |          |       |       |       |

| R/W-0                                                              | R/W-0 | R/W-0           | R/W-0                              | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|                                                                    |       |                 | PHAS                               | SEx<7:0> |       |       |       |

| bit 7                                                              |       |                 |                                    |          |       |       | bit 0 |

|                                                                    |       |                 |                                    |          |       |       |       |

| Legend:                                                            |       |                 |                                    |          |       |       |       |

| R = Readable bit W = Writable bit U                                |       |                 | U = Unimplemented bit, read as '0' |          |       |       |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is |       | x = Bit is unkr | nown                               |          |       |       |       |

bit 15-0 PHASEx<15:0>: PWMx Phase-Shift Value or Independent Time Base Period for the PWM Generator bits

Note 1: If ITB (PWMCONx<9>) = 0, the following applies based on the mode of operation: Complementary, Redundant and Push-Pull Output mode (PMOD<1:0> (IOCON<11:10>) = 00, 01 or 10), PHASEx<15:0> = Phase-shift value for PWMxH and PWMxL outputs

If ITB (PWMCONx<9>) = 1, the following applies based on the mode of operation: Complementary, Redundant and Push-Pull Output mode (PMOD<1:0> (IOCONx<11:10>) = 00, 01 or 10), PHASEx<15:0> = Independent time base period value for PWMxH and PWMxL

### REGISTER 19-1: I2CxCON: I2Cx CONTROL REGISTER (CONTINUED)

| bit 6         | <b>STREN:</b> SCLx Clock Stretch Enable bit (when operating as I <sup>2</sup> C slave)<br>Used in conjunction with the SCLREL bit.<br>1 = Enables software or receives clock stretching<br>0 = Disables software or receives clock stretching |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5         | ACKDT: Acknowledge Data bit (when operating as I <sup>2</sup> C master, applicable during master receive)                                                                                                                                     |

|               | Value that is transmitted when the software initiates an Acknowledge sequence.<br>1 = Sends NACK during Acknowledge<br>0 = Sends ACK during Acknowledge                                                                                       |

| bit 4         | <b>ACKEN:</b> Acknowledge Sequence Enable bit (when operating as I <sup>2</sup> C master, applicable during master receive)                                                                                                                   |

|               | <ul> <li>1 = Initiates Acknowledge sequence on SDAx and SCLx pins and transmits ACKDT data bit. Hardware is clear at the end of the master Acknowledge sequence.</li> <li>0 = Acknowledge sequence is not in progress</li> </ul>              |

| bit 3         | <b>RCEN:</b> Receive Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                                   |

|               | <ul> <li>1 = Enables Receive mode for I<sup>2</sup>C. Hardware is clear at the end of the eighth bit of the master receive data byte.</li> <li>0 = Receive sequence is not in progress</li> </ul>                                             |

| bit 2         | <b>PEN:</b> Stop Condition Enable bit (when operating as $I^2C$ master)                                                                                                                                                                       |

| 511 2         | 1 = Initiates Stop condition on SDAx and SCLx pins. Hardware is clear at the end of the master Stop sequence.                                                                                                                                 |

| <b>h</b> :+ 4 | 0 = Stop condition is not in progress                                                                                                                                                                                                         |

| bit 1         | <b>RSEN:</b> Repeated Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                  |

|               | <ul> <li>1 = Initiates Repeated Start condition on SDAx and SCLx pins. Hardware is clear at the end of the<br/>master Repeated Start sequence.</li> <li>0 = Repeated Start condition is not in progress</li> </ul>                            |

| bit 0         | <b>SEN:</b> Start Condition Enable bit (when operating as $l^2C$ master)                                                                                                                                                                      |

|               | <ul> <li>1 = Initiates Start condition on SDAx and SCLx pins. Hardware is clear at the end of the master Start sequence.</li> <li>0 = Start condition is not in progress</li> </ul>                                                           |

**Note 1:** When performing master operations, ensure that the IPMIEN bit is set to '0'.

### BUFFER 21-5: ECAN™ MESSAGE BUFFER WORD 4

| R/W-x                                              | R/W-x | R/W-x | R/W-x             | R/W-x                              | R/W-x           | R/W-x | R/W-x |

|----------------------------------------------------|-------|-------|-------------------|------------------------------------|-----------------|-------|-------|

|                                                    |       |       | Ву                | /te 3                              |                 |       |       |

| bit 15                                             |       |       |                   |                                    |                 |       | bit 8 |

|                                                    |       |       |                   |                                    |                 |       |       |

| R/W-x                                              | R/W-x | R/W-x | R/W-x             | R/W-x                              | R/W-x           | R/W-x | R/W-x |

|                                                    |       |       | Ву                | /te 2                              |                 |       |       |

| bit 7                                              |       |       |                   |                                    |                 |       | bit 0 |

| Legend:                                            |       |       |                   |                                    |                 |       |       |

| R = Readable bit W = Writable bit                  |       |       | bit               | U = Unimplemented bit, read as '0' |                 |       |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cl |       |       | '0' = Bit is clea | ared                               | x = Bit is unkr | nown  |       |

bit 15-8 Byte 3<15:8>: ECAN Message Byte 3 bits

bit 7-0 Byte 2<7:0>: ECAN Message Byte 2 bits

#### BUFFER 21-6: ECAN™ MESSAGE BUFFER WORD 5

| R/W-x                                                     | R/W-x | R/W-x | R/W-x           | R/W-x                              | R/W-x | R/W-x | R/W-x |

|-----------------------------------------------------------|-------|-------|-----------------|------------------------------------|-------|-------|-------|

|                                                           |       |       | В               | yte 5                              |       |       |       |

| bit 15                                                    |       |       |                 |                                    |       |       | bit 8 |

| R/W-x                                                     | R/W-x | R/W-x | R/W-x           | R/W-x                              | R/W-x | R/W-x | R/W-x |

|                                                           |       |       |                 | yte 4                              |       |       |       |

| bit 7                                                     |       |       |                 | -                                  |       |       | bit 0 |

|                                                           |       |       |                 |                                    |       |       |       |

| Legend:                                                   |       |       |                 |                                    |       |       |       |

| R = Readable bit W = Writable bit                         |       |       | bit             | U = Unimplemented bit, read as '0' |       |       |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x |       |       | x = Bit is unki | nown                               |       |       |       |

bit 15-8 Byte 5<15:8>: ECAN Message Byte 5 bits

bit 7-0 Byte 4<7:0>: ECAN Message Byte 4 bits

### 22.0 CHARGE TIME MEASUREMENT UNIT (CTMU)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Charge Time Measurement Unit (CTMU)" (DS70661) in the "dsPIC33/PIC24 Family Reference Manual", which is available on the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Charge Time Measurement Unit is a flexible analog module that provides accurate differential time measurement between pulse sources, as well as asynchronous pulse generation. Its key features include:

- Four Edge Input Trigger Sources

- Polarity Control for Each Edge Source

- Control of Edge Sequence

- Control of Response to Edges

- · Precise Time Measurement Resolution of 1 ns

- Accurate Current Source Suitable for Capacitive Measurement

- On-Chip Temperature Measurement using a Built-in Diode

Together with other on-chip analog modules, the CTMU can be used to precisely measure time, measure capacitance, measure relative changes in capacitance or generate output pulses that are independent of the system clock.

The CTMU module is ideal for interfacing with capacitive-based sensors. The CTMU is controlled through three registers: CTMUCON1, CTMUCON2 and CTMUICON. CTMUCON1 and CTMUCON2 enable the module and control edge source selection, edge source polarity selection and edge sequencing. The CTMUICON register controls the selection and trim of the current source.

### 24.3 PTG Control Registers

#### REGISTER 24-1: PTGCST: PTG CONTROL/STATUS REGISTER

| R/W-0        | U-0     | R/W-0   | R/W-0   | U-0 | R/W-0                 | R/W-0                  | R/W-0                  |  |

|--------------|---------|---------|---------|-----|-----------------------|------------------------|------------------------|--|

| PTGEN        | —       | PTGSIDL | PTGTOGL | —   | PTGSWT <sup>(2)</sup> | PTGSSEN <sup>(3)</sup> | PTGIVIS                |  |

| bit 15 bit 8 |         |         |         |     |                       |                        |                        |  |

|              |         |         |         |     |                       |                        |                        |  |

| R/W-0        | HS-0    | U-0     | U-0     | U-0 | U-0                   | R/W-0                  |                        |  |

| PTGSTRT      | PTGWDTO | _       | _       | _   | _                     | PTGITM1 <sup>(1)</sup> | PTGITM0 <sup>(1)</sup> |  |

| bit 7 |

|-------|

|-------|

| Legend:           | HS = Hardware Settable bit |                                    |                    |  |  |  |

|-------------------|----------------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

| bit 15  |       | PTGEN: Module Enable bit                                                                                                                                                                                                      |

|---------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |       | 1 = PTG module is enabled                                                                                                                                                                                                     |

|         |       | 0 = PTG module is disabled                                                                                                                                                                                                    |

| bit 14  |       | Unimplemented: Read as '0'                                                                                                                                                                                                    |

| bit 13  |       | PTGSIDL: PTG Stop in Idle Mode bit                                                                                                                                                                                            |

|         |       | <ul> <li>1 = Discontinues module operation when device enters Idle mode</li> <li>0 = Continues module operation in Idle mode</li> </ul>                                                                                       |

| bit 12  |       | PTGTOGL: PTG TRIG Output Toggle Mode bit                                                                                                                                                                                      |

|         |       | <ul> <li>1 = Toggle state of the PTGOx for each execution of the PTGTRIG command</li> <li>0 = Each execution of the PTGTRIG command will generate a single PTGOx pulse determined by the value in the PTGPWDx bits</li> </ul> |

| bit 11  |       | Unimplemented: Read as '0'                                                                                                                                                                                                    |

| bit 10  |       | PTGSWT: PTG Software Trigger bit <sup>(2)</sup>                                                                                                                                                                               |

|         |       | 1 = Triggers the PTG module                                                                                                                                                                                                   |

|         |       | 0 = No action (clearing this bit will have no effect)                                                                                                                                                                         |

| bit 9   |       | PTGSSEN: PTG Enable Single-Step bit <sup>(3)</sup>                                                                                                                                                                            |

|         |       | 1 = Enables Single-Step mode                                                                                                                                                                                                  |

|         |       | 0 = Disables Single-Step mode                                                                                                                                                                                                 |

| bit 8   |       | PTGIVIS: PTG Counter/Timer Visibility Control bit                                                                                                                                                                             |

|         |       | 1 = Reads of the PTGSDLIM, PTGCxLIM or PTGTxLIM registers return the current values of their<br>corresponding counter/timer registers (PTGSD, PTGCx, PTGTx)                                                                   |

|         |       | <ul> <li>Reads of the PTGSDLIM, PTGCxLIM or PTGTxLIM registers return the value previously written<br/>to those limit registers</li> </ul>                                                                                    |

| bit 7   |       | PTGSTRT: PTG Start Sequencer bit                                                                                                                                                                                              |

|         |       | <ul><li>1 = Starts to sequentially execute commands (Continuous mode)</li><li>0 = Stops executing commands</li></ul>                                                                                                          |

| bit 6   |       | PTGWDTO: PTG Watchdog Timer Time-out Status bit                                                                                                                                                                               |

|         |       | 1 = PTG Watchdog Timer has timed out                                                                                                                                                                                          |

|         |       | 0 = PTG Watchdog Timer has not timed out.                                                                                                                                                                                     |

| bit 5-2 |       | Unimplemented: Read as '0'                                                                                                                                                                                                    |

| Note    | 1: Th | nese bits apply to the PTGWHI and PTGWLO commands only.                                                                                                                                                                       |

|         | 2: Th | is bit is only used with the PTGCTRL step command software trigger option.                                                                                                                                                    |

3: Use of the PTG Single-Step mode is reserved for debugging tools only.

bit 0

### REGISTER 24-8: PTGC1LIM: PTG COUNTER 1 LIMIT REGISTER<sup>(1)</sup>

| R/W-0  | R/W-0 | R/W-0 | R/W-0  | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|--------|----------|-------|-------|-------|

|        |       |       | PTGC1L | IM<15:8> |       |       |       |

| bit 15 |       |       |        |          |       |       | bit 8 |

|        |       |       |        |          |       |       |       |

| R/W-0  | R/W-0 | R/W-0 | R/W-0  | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|        |       |       | PTGC1L | IM<7:0>  |       |       |       |

| bit 7  |       |       |        |          |       |       | bit C |

| Legena.           |                  |                                                |                    |  |  |

|-------------------|------------------|------------------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | ritable bit U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                           | x = Bit is unknown |  |  |

bit 15-0 **PTGC1LIM<15:0>:** PTG Counter 1 Limit Register bits May be used to specify the loop count for the PTGJMPC1 Step command or as a limit register for the General Purpose Counter 1.

### REGISTER 24-9: PTGHOLD: PTG HOLD REGISTER<sup>(1)</sup>

| R/W-0         | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|---------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| PTGHOLD<15:8> |       |       |       |       |       |       |       |  |  |

| bit 15        |       |       |       |       |       |       | bit 8 |  |  |

| R/W-0        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|--------------|-------|-------|-------|-------|-------|-------|-------|--|--|--|

| PTGHOLD<7:0> |       |       |       |       |       |       |       |  |  |  |

| bit 7        |       |       |       |       |       |       | bit 0 |  |  |  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 **PTGHOLD<15:0>:** PTG General Purpose Hold Register bits Holds user-supplied data to be copied to the PTGTxLIM, PTGCxLIM, PTGSDLIM or PTGL0 registers with the PTGCOPY command.

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

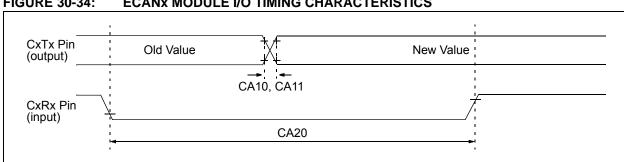

#### FIGURE 30-34: ECANx MODULE I/O TIMING CHARACTERISTICS

#### TABLE 30-51: ECANx MODULE I/O TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                              | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                     |      |       | $\leq$ +85°C for Industrial |

|--------------------|--------|----------------------------------------------|-------------------------------------------------------|---------------------|------|-------|-----------------------------|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>                | Min.                                                  | Тур. <sup>(2)</sup> | Max. | Units | Conditions                  |

| CA10               | TIOF   | Port Output Fall Time                        | —                                                     | _                   |      | ns    | See Parameter DO32          |

| CA11               | TioR   | Port Output Rise Time                        | _                                                     | —                   | _    | ns    | See Parameter DO31          |

| CA20               | TCWF   | Pulse Width to Trigger<br>CAN Wake-up Filter | 120                                                   |                     | _    | ns    |                             |

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

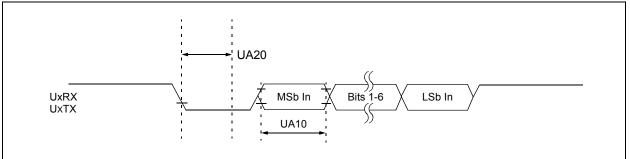

#### **FIGURE 30-35: UARTX MODULE I/O TIMING CHARACTERISTICS**

### TABLE 30-52: UARTX MODULE I/O TIMING REQUIREMENTS

| AC CHARACTERISTICS |         | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |       |                     |      |       |            |

|--------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------|-------|---------------------|------|-------|------------|

| Param<br>No.       | Symbol  | Characteristic <sup>(1)</sup>                                                                                                          | Min.  | Тур. <sup>(2)</sup> | Max. | Units | Conditions |

| UA10               | TUABAUD | UARTx Baud Time                                                                                                                        | 66.67 |                     | _    | ns    |            |

| UA11               | FBAUD   | UARTx Baud Frequency                                                                                                                   | —     |                     | 15   | Mbps  |            |

| UA20               | TCWF    | Start Bit Pulse Width to Trigger<br>UARTx Wake-up                                                                                      | 500   | _                   |      | ns    |            |

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

| Remappable Input for U1RX               |     |

|-----------------------------------------|-----|

| Reset System                            | 123 |

| Shared Port Structure                   |     |

| Single-Phase Synchronous Buck Converter |     |

| SPIx Module                             |     |

| Suggested Oscillator Circuit Placement  | 31  |

| Type B Timer (Timer2 and Timer4)        |     |

| Type B/Type C Timer Pair (32-Bit Timer) |     |

| Type C Timer (Timer3 and Timer5)        |     |

| UARTx Module                            |     |

| User-Programmable Blanking Function     |     |

| Watchdog Timer (WDT)                    |     |

| Brown-out Reset (BOR)                   |     |

### С

| C Compilers                              |          |

|------------------------------------------|----------|

| MPLAB XC Compilers                       |          |

| Charge Time Measurement Unit. See CTMU.  |          |

| Code Examples                            |          |

| IC1 Connection to QEI1 Input on          |          |

| Pin 43 of dsPIC33EPXXXMC206              |          |

| Port Write/Read                          |          |

| PWMx Write-Protected Register            |          |

| Unlock Sequence                          |          |

| PWRSAV Instruction Syntax                |          |

| Code Protection                          |          |

| CodeGuard Security                       | 379, 386 |

| Configuration Bits                       |          |

| Description                              |          |

| Configuration Byte Register Map          |          |

| Configuring Analog and Digital Port Pins |          |

| CPU                                      |          |

| Addressing Modes                         |          |

| Clocking System Options                  |          |

| Fast RC (FRC) Oscillator                 |          |

| FRC Oscillator with PLL                  |          |

| FRC Oscillator with Postscaler           |          |

| Low-Power RC (LPRC) Oscillator           |          |

| Primary (XT, HS, EC) Oscillator          |          |

| Primary Oscillator with PLL              |          |

| Control Registers                        | 40       |

| Data Space Addressing                    |          |

| Instruction Set                          |          |

| Resources                                |          |

| CTMU                                     |          |

| Control Registers                        |          |

| Resources                                |          |

| Customer Change Notification Service     |          |

| Customer Notification Service            |          |

| Customer Support                         |          |

|                                          |          |

## D

| Data Address Space                    | 51 |

|---------------------------------------|----|

| Memory Map for dsPIC33EP128MC20X/50X, |    |

| dsPIC33EP128GP50X Devices             | 54 |

| Memory Map for dsPIC33EP256MC20X/50X, |    |

| dsPIC33EP256GP50X Devices             | 55 |

| Memory Map for dsPIC33EP32MC20X/50X,  |    |

| dsPIC33EP32GP50X Devices              | 52 |

| Memory Map for dsPIC33EP512MC20X/50X, |    |

| dsPIC33EP512GP50X Devices             | 56 |

| Memory Map for dsPIC33EP64MC20X/50X,  |    |

| dsPIC33EP64GP50X Devices              | 53 |

| Memory Map for PIC24EP128GP/MC20X/50X |    |

| Devices                               | 59 |

|                                       |    |

| Memory Map for PIC24EP256GP/MC20X/50X   |       |     |

|-----------------------------------------|-------|-----|

| Devices                                 |       | 60  |

| Memory Map for PIC24EP32GP/MC20X/50X    |       |     |

| Devices                                 |       | 57  |

| Memory Map for PIC24EP512GP/MC20X/50X   | ••••• | 57  |

|                                         |       | ~ ~ |

| Devices                                 |       | 61  |

| Memory Map for PIC24EP64GP/MC20X/50X    |       |     |

| Devices                                 |       | 58  |

| Near Data Space                         |       | 51  |

| Organization, Alignment                 |       | 51  |

| SFR Space                               |       |     |

| Width                                   |       |     |

| Data Memory                             | ••••• | 51  |

|                                         |       | 440 |

| Arbitration and Bus Master Priority     | ••••• | 110 |

| Data Space                              |       |     |

| Extended X                              |       | 109 |

| Paged Memory Scheme                     |       | 105 |

| DC and AC Characteristics               |       |     |

| Graphs                                  |       | 475 |

| DC Characteristics                      |       |     |

| BOR                                     |       | 111 |

|                                         |       |     |

| CTMU Current Source Requirements        |       |     |

| Doze Current (IDOZE) 4                  |       |     |

| High Temperature                        |       |     |

| I/O Pin Input Specifications            |       | 408 |

| I/O Pin Output Specifications4          | 11,   | 470 |

| Idle Current (IIDLE) 4                  |       |     |

| Op Amp/Comparator Requirements          |       |     |

| Op Amp/Comparator Voltage Reference     |       |     |

|                                         |       | 457 |

| Requirements                            |       |     |

| Operating Current (IDD)                 |       |     |

| Operating MIPS vs. Voltage 4            |       |     |

| Power-Down Current (IPD) 4              |       |     |

| Program Memory                          |       | 412 |

| Temperature and Voltage                 |       | 468 |

| Temperature and Voltage Specifications  |       |     |

| Thermal Operating Conditions            |       |     |

| Watchdog Timer Delta Current            |       |     |

| Demo/Development Boards, Evaluation and |       | 407 |

|                                         |       | 400 |

| Starter Kits                            |       |     |

| Development Support                     |       |     |

| Third-Party Tools                       |       | 400 |

| DMA Controller                          |       |     |

| Channel to Peripheral Associations      |       | 140 |

| Control Registers                       |       | 141 |

| DMAXCNT                                 |       |     |

| DMAxCON                                 |       |     |

| DMAXPAD                                 |       |     |

|                                         |       |     |

| DMAxREQ                                 |       |     |

| DMAxSTA                                 |       |     |

| DMAxSTB                                 |       |     |

| Resources                               |       |     |

| Supported Peripherals                   |       | 139 |

| Doze Mode                               |       |     |

| DSP Engine                              |       | 44  |

| •                                       |       |     |

| E                                       |       |     |

## Ε

| 310 |

|-----|

| 311 |

| 311 |

| 312 |

| 312 |

| 313 |

| 313 |

|     |

#### Ρ

| Packaging                                  |     |

|--------------------------------------------|-----|

| Details                                    |     |

| Marking                                    |     |

| Peripheral Module Disable (PMD)            |     |

| Peripheral Pin Select (PPS)                |     |

| Available Peripherals                      | 175 |

| Available Pins                             | 175 |

| Control                                    |     |

| Control Registers                          |     |

| Input Mapping                              |     |

| Output Selection for Remappable Pins       |     |

| Pin Selection for Selectable Input Sources |     |

| Selectable Input Sources                   |     |

| Peripheral Trigger Generator (PTG) Module  |     |

| PICkit 3 In-Circuit Debugger/Programmer    |     |

| Pinout I/O Descriptions (table)            |     |

| Power-Saving Features                      |     |

| Clock Frequency                            |     |

| Clock Switching                            |     |

| Instruction-Based Modes                    |     |

| Idle                                       |     |

| Interrupts Coincident with Power           |     |

| Save Instructions                          |     |

| Sleep                                      |     |

| Resources                                  |     |

| Program Address Space                      | 45  |

| Construction                               | 117 |

| Data Access from Program Memory Using      |     |

| Table Instructions                         | 118 |

| Memory Map (dsPIC33EP128GP50X,             |     |

| dsPIC33EP128MC20X/50X,                     |     |