Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 60 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 25                                                                             |

| Program Memory Size        | 32KB (10.7K x 24)                                                              |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 2K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 8x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 36-VFTLA Exposed Pad                                                           |

| Supplier Device Package    | 36-VTLA (5x5)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep32gp203t-e-tl |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

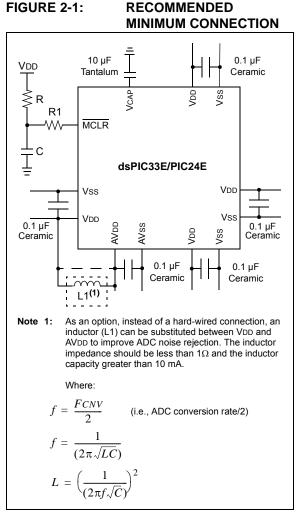

#### 2.2.1 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits including DSCs to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

## 2.3 CPU Logic Filter Capacitor Connection (VCAP)

A low-ESR (< 1 Ohm) capacitor is required on the VCAP pin, which is used to stabilize the voltage regulator output voltage. The VCAP pin must not be connected to VDD and must have a capacitor greater than 4.7  $\mu$ F (10  $\mu$ F is recommended), 16V connected to ground. The type can be ceramic or tantalum. See **Section 30.0** "**Electrical Characteristics**" for additional information.

The placement of this capacitor should be close to the VCAP pin. It is recommended that the trace length not exceeds one-quarter inch (6 mm). See **Section 27.3 "On-Chip Voltage Regulator"** for details.

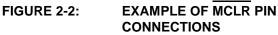

# 2.4 Master Clear (MCLR) Pin

The MCLR pin provides two specific device functions:

- Device Reset

- Device Programming and Debugging.

During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as shown in Figure 2-2, it is recommended that the capacitor, C, be isolated from the  $\overline{\text{MCLR}}$  pin during programming and debugging operations.

Place the components as shown in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

# 3.6 CPU Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter |

|-------|--------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                            |

|       | http://www.microchip.com/wwwproducts/                                                |

|       | Devices.aspx?dDocName=en555464                                                       |

## 3.6.1 KEY RESOURCES

- "CPU" (DS70359) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

#### **REGISTER 3-1:** SR: CPU STATUS REGISTER (CONTINUED)

| bit 7-5       | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2,3)</sup><br>111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled<br>110 = CPU Interrupt Priority Level is 6 (14)<br>101 = CPU Interrupt Priority Level is 5 (13)<br>100 = CPU Interrupt Priority Level is 4 (12)<br>011 = CPU Interrupt Priority Level is 3 (11)<br>010 = CPU Interrupt Priority Level is 2 (10)<br>001 = CPU Interrupt Priority Level is 1 (9)<br>000 = CPU Interrupt Priority Level is 0 (8) |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4         | RA: REPEAT Loop Active bit<br>1 = REPEAT loop in progress<br>0 = REPEAT loop not in progress                                                                                                                                                                                                                                                                                                                                                                                                    |

| bit 3         | N: MCU ALU Negative bit<br>1 = Result was negative<br>0 = Result was non-negative (zero or positive)                                                                                                                                                                                                                                                                                                                                                                                            |

| bit 2         | <ul> <li>OV: MCU ALU Overflow bit</li> <li>This bit is used for signed arithmetic (2's complement). It indicates an overflow of the magnitude that causes the sign bit to change state.</li> <li>1 = Overflow occurred for signed arithmetic (in this arithmetic operation)</li> <li>0 = No overflow occurred</li> </ul>                                                                                                                                                                        |

| bit 1         | <ul> <li><b>Z:</b> MCU ALU Zero bit</li> <li>1 = An operation that affects the Z bit has set it at some time in the past</li> <li>0 = The most recent operation that affects the Z bit has cleared it (i.e., a non-zero result)</li> </ul>                                                                                                                                                                                                                                                      |

| bit 0         | <b>C:</b> MCU ALU Carry/Borrow bit<br>1 = A carry-out from the Most Significant bit of the result occurred<br>0 = No carry-out from the Most Significant bit of the result occurred                                                                                                                                                                                                                                                                                                             |

| Note 1:<br>2: | This bit is available on dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices only.<br>The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority                                                                                                                                                                                                                                                                                                     |

- Level. The value in parentheses indicates the IPL, if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

3: The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

- 4: A data write to the SR register can modify the SA and SB bits by either a data write to SA and SB or by clearing the SAB bit. To avoid a possible SA or SB bit write race condition, the SA and SB bits should not be modified using bit operations.

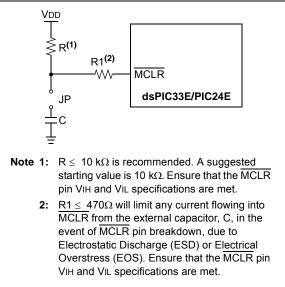

## 4.0 MEMORY ORGANIZATION

Note: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXGP/MC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Program Memory" (DS70613) in the "dsPIC33/PIC24 Family Reference Manual', which is available from the Microchip web site (www.microchip.com).

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X architecture features separate program and data memory spaces, and buses. This architecture also allows the direct access of program memory from the Data Space (DS) during code execution.

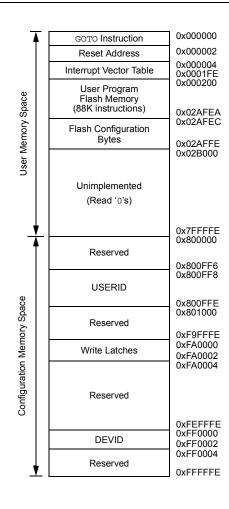

## 4.1 Program Address Space

The program address memory space of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices is 4M instructions. The space is addressable by a 24-bit value derived either from the 23-bit PC during program execution, or from table operation or Data Space remapping, as described in Section 4.8 "Interfacing Program and Data Memory Spaces".

User application access to the program memory space is restricted to the lower half of the address range (0x000000 to 0x7FFFF). The exception is the use of TBLRD operations, which use TBLPAG<7> to read Device ID sections of the configuration memory space.

The program memory maps, which are presented by device family and memory size, are shown in Figure 4-1 through Figure 4-5.

# FIGURE 4-1: PROGRAM MEMORY MAP FOR dsPIC33EP32GP50X, dsPIC33EP32MC20X/50X AND PIC24EP32GP/MC20X DEVICES

#### FIGURE 4-4: PROGRAM MEMORY MAP FOR dsPIC33EP256GP50X, dsPIC33EP256MC20X/50X AND PIC24EP256GP/MC20X DEVICES

Note: Memory areas are not shown to scale.

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12 | Bit 11 | Bit 10 | Bit 9          | Bit 8  | Bit 7 | Bit 6  | Bit 5           | Bit 4         | Bit 3  | Bit 2    | Bit 1        | Bit 0   | All<br>Reset |

|--------------|-------|--------|--------|------------|--------|--------|--------|----------------|--------|-------|--------|-----------------|---------------|--------|----------|--------------|---------|--------------|

| IFS0         | 0800  | _      | DMA1IF | AD1IF      | U1TXIF | U1RXIF | SPI1IF | SPI1EIF        | T3IF   | T2IF  | OC2IF  | IC2IF           | DMA0IF        | T1IF   | OC1IF    | IC1IF        | INTOIF  | 0000         |

| IFS1         | 0802  | U2TXIF | U2RXIF | INT2IF     | T5IF   | T4IF   | OC4IF  | OC3IF          | DMA2IF | _     | _      | _               | INT1IF        | CNIF   | CMIF     | MI2C1IF      | SI2C1IF | 0000         |

| IFS2         | 0804  | _      | _      | _          | _      |        |        |                | _      | _     | IC4IF  | IC3IF           | DMA3IF        | C1IF   | C1RXIF   | SPI2IF       | SPI2EIF | 0000         |

| IFS3         | 0806  | _      | _      | _          | _      |        | QEI1IF | PSEMIF         | _      | _     | _      | _               | _             | _      | MI2C2IF  | SI2C2IF      | _       | 0000         |

| IFS4         | 0808  | _      | _      | CTMUIF     |        |        |        |                | _      | _     | C1TXIF | _               | _             | CRCIF  | U2EIF    | U1EIF        |         | 0000         |

| IFS5         | 080A  | PWM2IF | PWM1IF | _          |        |        |        |                | _      | _     | _      | _               | _             | _      | _        | _            |         | 0000         |

| IFS6         | 080C  | _      | _      | _          |        |        |        |                | _      | _     | _      | _               | _             | _      | _        | _            | PWM3IF  | 0000         |

| IFS8         | 0810  | JTAGIF | ICDIF  | _          |        |        |        |                | _      | _     | _      | _               | _             | _      | _        | _            |         | 0000         |

| IFS9         | 0812  | _      | —      | _          | _      | _      |        |                | _      | _     | PTG3IF | PTG2IF          | PTG1IF        | PTG0IF | PTGWDTIF | PTGSTEPIF    |         | 0000         |

| IEC0         | 0820  | _      | DMA1IE | AD1IE      | U1TXIE | U1RXIE | SPI1IE | SPI1EIE        | T3IE   | T2IE  | OC2IE  | IC2IE           | DMA0IE        | T1IE   | OC1IE    | IC1IE        | INTOIE  | 0000         |

| IEC1         | 0822  | U2TXIE | U2RXIE | INT2IE     | T5IE   | T4IE   | OC4IE  | OC3IE          | DMA2IE | —     | _      | —               | INT1IE        | CNIE   | CMIE     | MI2C1IE      | SI2C1IE | 0000         |

| IEC2         | 0824  | _      | _      | _          | _      | _      |        | _              | _      | _     | IC4IE  | IC3IE           | <b>DMA3IE</b> | C1IE   | C1RXIE   | SPI2IE       | SPI2EIE | 0000         |

| IEC3         | 0826  | _      | _      | _          | _      | _      | QEI1IE | PSEMIE         | _      | _     | _      | _               | _             | _      | MI2C2IE  | SI2C2IE      | _       | 0000         |

| IEC4         | 0828  | _      | _      | CTMUIE     | _      |        |        | _              | _      | _     | C1TXIE | _               | _             | CRCIE  | U2EIE    | U1EIE        | _       | 0000         |

| IEC5         | 082A  | PWM2IE | PWM1IE | _          | _      | _      |        | _              | _      | _     | _      | _               | _             | _      | _        | _            | _       | 0000         |

| IEC6         | 082C  | _      | _      | _          | _      | _      |        | _              | _      | _     | _      | _               | _             | _      | _        | _            | PWM3IE  | 0000         |

| IEC7         | 082E  | _      | _      | _          | _      | _      |        | _              | _      | _     | _      | _               | _             | _      | _        | _            | _       | 0000         |

| IEC8         | 0830  | JTAGIE | ICDIE  | _          | _      | _      |        | _              | _      | _     | _      | _               | _             | _      | _        | _            | _       | 0000         |

| IEC9         | 0832  | _      | _      | _          | _      | _      |        | _              | _      | _     | PTG3IE | PTG2IE          | PTG1IE        | PTG0IE | PTGWDTIE | PTGSTEPIE    | _       | 0000         |

| IPC0         | 0840  | _      |        | T1IP<2:0>  |        | _      |        | OC1IP<2:0      | >      | _     |        | IC1IP<2:0>      |               | _      |          | INT0IP<2:0>  |         | 4444         |

| IPC1         | 0842  | _      |        | T2IP<2:0>  |        | _      |        | OC2IP<2:0      | >      | _     |        | IC2IP<2:0>      |               | _      | [        | DMA0IP<2:0>  |         | 4444         |

| IPC2         | 0844  | _      | l      | J1RXIP<2:0 | >      | _      |        | SPI1IP<2:0     | )>     | _     |        | SPI1EIP<2:0     | >             |        |          | T3IP<2:0>    |         | 4444         |

| IPC3         | 0846  | _      | _      | _          | _      | _      | C      | MA1IP<2:       | 0>     | _     |        | AD1IP<2:0>      |               |        |          | U1TXIP<2:0>  |         | 0444         |

| IPC4         | 0848  | _      |        | CNIP<2:0>  |        | _      |        | CMIP<2:0       | >      | _     |        | MI2C1IP<2:0     | >             |        | 5        | SI2C1IP<2:0> |         | 4444         |

| IPC5         | 084A  | _      | _      | _          | _      | _      |        | _              | _      | _     | _      | _               | _             |        |          | INT1IP<2:0>  |         | 0004         |

| IPC6         | 084C  | _      |        | T4IP<2:0>  |        | _      |        | OC4IP<2:0      | >      | _     |        | OC3IP<2:0>      |               |        | [        | DMA2IP<2:0>  |         | 4444         |

| IPC7         | 084E  | _      | 1      | U2TXIP<2:0 | >      | _      | ι      | J2RXIP<2:      | 0>     | _     |        | INT2IP<2:0>     |               |        |          | T5IP<2:0>    |         | 4444         |

| IPC8         | 0850  | _      |        | C1IP<2:0>  |        | _      | C      | 2:<br>2:<br>2: | 0>     | _     |        | SPI2IP<2:0>     |               |        | 5        | SPI2EIP<2:0> |         | 4444         |

| IPC9         | 0852  | _      | _      | _          | _      | _      |        | IC4IP<2:0      | >      | _     |        | IC3IP<2:0>      |               |        | [        | DMA3IP<2:0>  |         | 0444         |

| IPC12        | 0858  | _      | _      | _          | _      | _      | N      | 112C2IP<2:     | 0>     | _     |        | SI2C2IP<2:0     | >             | _      | _        | _            | _       | 0440         |

| IPC14        | 085C  | _      | _      | _          | _      | _      | (      | QEI1IP<2:(     | )>     | _     |        | PSEMIP<2:0      | >             | _      | _        | _            | _       | 0440         |

| IPC16        | 0860  | _      |        | CRCIP<2:0  | >      | _      |        | U2EIP<2:0      |        | _     |        | U1EIP<2:0>      |               | _      | <u> </u> | _            | _       | 4440         |

| IPC17        | 0862  | _      | _      | _          | _      | _      |        | C1TXIP<2:      |        | _     | _      | _               | —             | _      | _        | _            | _       | 0400         |

| IPC19        | 0866  | _      | _      |            | _      | _      |        |                |        |       |        | L<br>CTMUIP<2:0 | >             |        | <u> </u> | _            | _       | 0040         |

#### TABLE 4-7: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33EPXXXMC50X DEVICES ONLY

DS70000657H-page 73

# TABLE 4-27: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EPXXXGP/MC204/504 AND PIC24EPXXXGP/MC204 DEVICES ONLY DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12     | Bit 11 | Bit 10 | Bit 9 | Bit 8      | Bit 7 | Bit 6 | Bit 5         | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|------------|------------|--------|--------|-------|------------|-------|-------|---------------|--------|-------|-------|-------|-------|---------------|

| RPOR0        | 0680  |        |        |            | RP35R<5:0> |        |        |       |            | _     | —     | RP20R<5:0> 00 |        |       |       |       |       | 0000          |

| RPOR1        | 0682  | _      | _      |            | RP37R<5:0> |        |        |       |            |       | —     |               |        | RP36F | <5:0> |       |       | 0000          |

| RPOR2        | 0684  | _      | _      |            | RP39R<5:0> |        |        |       |            |       | —     | RP38R<5:0>    |        |       |       |       |       | 0000          |

| RPOR3        | 0686  | _      | _      |            |            | RP41   | R<5:0> |       |            |       | —     |               |        | RP40F | <5:0> |       |       | 0000          |

| RPOR4        | 0688  | _      | _      |            |            | RP43   | R<5:0> |       |            |       | —     |               |        | RP42F | <5:0> |       |       | 0000          |

| RPOR5        | 068A  | _      | —      | RP55R<5:0> |            |        | _      | —     | RP54R<5:0> |       |       |               |        | 0000  |       |       |       |               |

| RPOR6        | 068C  | _      | —      |            | RP57R<5:0> |        |        | _     | —          |       |       | RP56F         | R<5:0> |       |       | 0000  |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-28: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EPXXXGP/MC206/506 AND PIC24EPXXXGP/MC206 DEVICES ONLY DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13      | Bit 12     | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3 | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|-------------|------------|--------|--------|-------|-------|-------|-------|-------|--------|-------|--------|-------|-------|---------------|

| RPOR0        | 0680  | _      | _      |             |            | RP35F  | R<5:0> |       |       | _     | _     |       | •      | RP20F | R<5:0> |       |       | 0000          |

| RPOR1        | 0682  | _      |        |             |            | RP37F  | R<5:0> |       |       | _     | _     |       |        | RP36  | R<5:0> |       |       | 0000          |

| RPOR2        | 0684  | _      | —      |             |            | RP39F  | २<5:0> |       |       | _     | _     |       |        | RP38  | R<5:0> |       |       | 0000          |

| RPOR3        | 0686  | _      | —      |             | RP41R<5:0> |        |        |       |       | _     | _     |       |        | RP40  | R<5:0> |       |       | 0000          |

| RPOR4        | 0688  | _      | _      |             |            | RP43F  | २<5:0> |       |       | —     | _     |       |        | RP42  | R<5:0> |       |       | 0000          |

| RPOR5        | 068A  | _      | _      |             |            | RP55F  | २<5:0> |       |       | —     | _     |       |        | RP54  | R<5:0> |       |       | 0000          |

| RPOR6        | 068C  | _      | _      |             | RP57R<5:0> |        |        |       |       | —     | _     |       |        | RP56  | R<5:0> |       |       | 0000          |

| RPOR7        | 068E  | _      | _      |             |            | RP97F  | २<5:0> |       |       | —     | _     | _     | _      | _     | _      | _     | _     | 0000          |

| RPOR8        | 0690  |        | _      | RP118R<5:0> |            |        |        | _     | _     | —     | _     | —     | _      | —     | _      | 0000  |       |               |

| RPOR9        | 0692  | —      | _      |             |            |        |        | _     | _     |       |       | RP120 | R<5:0> |       |        | 0000  |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

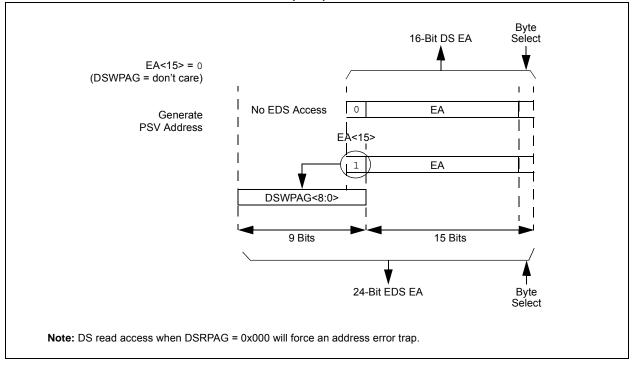

#### EXAMPLE 4-2: EXTENDED DATA SPACE (EDS) WRITE ADDRESS GENERATION

The paged memory scheme provides access to multiple 32-Kbyte windows in the EDS and PSV memory. The Data Space Page registers, DSxPAG, in combination with the upper half of the Data Space address, can provide up to 16 Mbytes of additional address space in the EDS and 8 Mbytes (DSRPAG only) of PSV address space. The paged data memory space is shown in Example 4-3.

The Program Space (PS) can be accessed with a DSRPAG of 0x200 or greater. Only reads from PS are supported using the DSRPAG. Writes to PS are not supported, so DSWPAG is dedicated to DS, including EDS only. The Data Space and EDS can be read from, and written to, using DSRPAG and DSWPAG, respectively.

# **REGISTER 8-7:** DMAXPAD: DMA CHANNEL X PERIPHERAL ADDRESS REGISTER<sup>(1)</sup>

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|------------------|-----------------|-------|

|                 |       |                  | PAD   | <15:8>            |                  |                 |       |

| bit 15          |       |                  |       |                   |                  |                 | bit 8 |

|                 |       |                  |       |                   |                  |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|                 |       |                  | PAE   | )<7:0>            |                  |                 |       |

| bit 7           |       |                  |       |                   |                  |                 | bit 0 |

|                 |       |                  |       |                   |                  |                 |       |

| Legend:         |       |                  |       |                   |                  |                 |       |

| R = Readable    | bit   | W = Writable     | bit   | U = Unimplen      | nented bit, read | d as '0'        |       |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

#### bit 15-0 PAD<15:0>: Peripheral Address Register bits

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

#### REGISTER 8-8: DMAXCNT: DMA CHANNEL X TRANSFER COUNT REGISTER<sup>(1)</sup>

| U-0             | U-0   | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|------------------|-----------------|-------|

| —               |       |                  |       | CNT<              | 13:8> <b>(2)</b> |                 |       |

| bit 15          |       |                  |       |                   |                  |                 | bit 8 |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|                 |       |                  | CNT<  | <7:0> <b>(2)</b>  |                  |                 |       |

| bit 7           |       |                  |       |                   |                  |                 | bit 0 |

| Legend:         |       |                  |       |                   |                  |                 |       |

| R = Readable b  | oit   | W = Writable b   | bit   | U = Unimplen      | nented bit, rea  | id as '0'       |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

bit 15-14 Unimplemented: Read as '0'

bit 13-0 CNT<13:0>: DMA Transfer Count Register bits<sup>(2)</sup>

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

**2:** The number of DMA transfers = CNT<13:0> + 1.

# 9.0 OSCILLATOR CONFIGURATION

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Oscillator" (DS70580) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

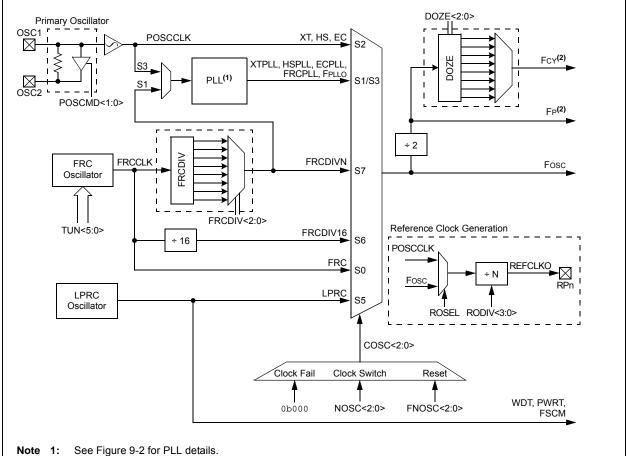

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X oscillator system provides:

- On-chip Phase-Locked Loop (PLL) to boost internal operating frequency on select internal and external oscillator sources

- On-the-fly clock switching between various clock sources

- · Doze mode for system power savings

- Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown

- Configuration bits for clock source selection

- A simplified diagram of the oscillator system is shown in Figure 9-1.

### FIGURE 9-1: OSCILLATOR SYSTEM DIAGRAM

2: The term, FP, refers to the clock source for all peripherals, while FCY refers to the clock source for the CPU. Throughout this document, FCY and FP are used interchangeably, except in the case of Doze mode. FP and FCY will be different when Doze mode is used with a doze ratio of 1:2 or lower.

| R/W-0         | U-0                                                                                                                                                                                                                                          | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |  |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|-----------------------|-----------------------|--|--|

| ROON          |                                                                                                                                                                                                                                              | ROSSLP                                                                                                                                                                                                                                                                                                                                                                                                   | ROSEL                                                                                                                                                                                                                 | RODIV3 <sup>(1)</sup> | RODIV2 <sup>(1)</sup> | RODIV1 <sup>(1)</sup> | RODIV0 <sup>(1)</sup> |  |  |

| bit 15        |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                       |                       |                       | •                     | bit                   |  |  |

| U-0           | U-0                                                                                                                                                                                                                                          | U-0                                                                                                                                                                                                                                                                                                                                                                                                      | U-0                                                                                                                                                                                                                   | U-0                   | U-0                   | U-0                   | U-0                   |  |  |

|               | _                                                                                                                                                                                                                                            | _                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                       | _                     |                       | _                     |                       |  |  |

| bit 7         |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                       |                       |                       |                       | bit                   |  |  |

| Legend:       |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                       |                       |                       |                       |                       |  |  |

| R = Readable  | e bit                                                                                                                                                                                                                                        | W = Writable                                                                                                                                                                                                                                                                                                                                                                                             | bit                                                                                                                                                                                                                   | U = Unimpler          | nented bit, read      | l as '0'              |                       |  |  |

| -n = Value at |                                                                                                                                                                                                                                              | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                       | '0' = Bit is cle      |                       | x = Bit is unkr       | iown                  |  |  |

| bit 14        | 0 = Reference                                                                                                                                                                                                                                | e oscillator outp<br>e oscillator outp<br>i <b>ted:</b> Read as '                                                                                                                                                                                                                                                                                                                                        | out is disabled                                                                                                                                                                                                       |                       | .K pin <sup>(2)</sup> |                       |                       |  |  |

| bit 13        | <b>ROSSLP:</b> Reference Oscillator Run in Sleep bit                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                       |                       |                       |                       |                       |  |  |

|               | 1 = Reference oscillator output continues to run in Sleep<br>0 = Reference oscillator output is disabled in Sleep                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                       |                       |                       |                       |                       |  |  |

| bit 12        | 1 = Oscillator                                                                                                                                                                                                                               | erence Oscillato<br>crystal is used<br>lock is used as                                                                                                                                                                                                                                                                                                                                                   | as the refere                                                                                                                                                                                                         | nce clock             |                       |                       |                       |  |  |

| bit 11-8      | 1111 = Refer<br>1110 = Refer<br>1101 = Refer<br>1000 = Refer<br>1011 = Refer<br>1001 = Refer<br>1000 = Refer<br>0111 = Refer<br>0111 = Refer<br>0101 = Refer<br>0100 = Refer<br>0101 = Refer<br>0011 = Refer<br>0011 = Refer<br>0011 = Refer | Reference Os<br>rence clock divi<br>rence clock divi | ded by 32,763<br>ded by 16,384<br>ded by 8,192<br>ded by 4,096<br>ded by 2,048<br>ded by 1,024<br>ded by 512<br>ded by 512<br>ded by 256<br>ded by 128<br>ded by 64<br>ded by 32<br>ded by 16<br>ded by 8<br>ded by 4 | 8                     |                       |                       |                       |  |  |

|               | 0000 = Refer                                                                                                                                                                                                                                 | ence clock                                                                                                                                                                                                                                                                                                                                                                                               | -                                                                                                                                                                                                                     |                       |                       |                       |                       |  |  |

#### REGISTER 9-5: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

- **Note 1:** The reference oscillator output must be disabled (ROON = 0) before writing to these bits.

- 2: This pin is remappable. See Section 11.4 "Peripheral Pin Select (PPS)" for more information.

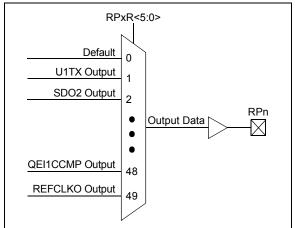

#### 11.4.4.2 Output Mapping

In contrast to inputs, the outputs of the Peripheral Pin Select options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPORx registers are used to control output mapping. Like the RPINRx registers, each register contains sets of 6-bit fields, with each set associated with one RPn pin (see Register 11-18 through Register 11-27). The value of the bit field corresponds to one of the peripherals and that peripheral's output is mapped to the pin (see Table 11-3 and Figure 11-3).

A null output is associated with the output register Reset value of '0'. This is done to ensure that remappable outputs remain disconnected from all output pins by default.

#### FIGURE 11-3: MULTIPLEXING REMAPPABLE OUTPUT FOR RPn

#### 11.4.4.3 Mapping Limitations

The control schema of the peripheral select pins is not limited to a small range of fixed peripheral configurations. There are no mutual or hardware-enforced lockouts between any of the peripheral mapping SFRs. Literally any combination of peripheral mappings across any or all of the RPn pins is possible. This includes both many-toone and one-to-many mappings of peripheral inputs and outputs to pins. While such mappings may be technically possible from a configuration point of view, they may not be supportable from an electrical point of view.

#### TABLE 11-3: OUTPUT SELECTION FOR REMAPPABLE PINS (RPn)

| Function                | RPxR<5:0> | Output Name                                   |

|-------------------------|-----------|-----------------------------------------------|

| Default PORT            | 000000    | RPn tied to Default Pin                       |

| U1TX                    | 000001    | RPn tied to UART1 Transmit                    |

| U2TX                    | 000011    | RPn tied to UART2 Transmit                    |

| SDO2                    | 001000    | RPn tied to SPI2 Data Output                  |

| SCK2                    | 001001    | RPn tied to SPI2 Clock Output                 |

| SS2                     | 001010    | RPn tied to SPI2 Slave Select                 |

| C1TX <sup>(2)</sup>     | 001110    | RPn tied to CAN1 Transmit                     |

| OC1                     | 010000    | RPn tied to Output Compare 1 Output           |

| OC2                     | 010001    | RPn tied to Output Compare 2 Output           |

| OC3                     | 010010    | RPn tied to Output Compare 3 Output           |

| OC4                     | 010011    | RPn tied to Output Compare 4 Output           |

| C1OUT                   | 011000    | RPn tied to Comparator Output 1               |

| C2OUT                   | 011001    | RPn tied to Comparator Output 2               |

| C3OUT                   | 011010    | RPn tied to Comparator Output 3               |

| SYNCO1 <sup>(1)</sup>   | 101101    | RPn tied to PWM Primary Time Base Sync Output |

| QEI1CCMP <sup>(1)</sup> | 101111    | RPn tied to QEI 1 Counter Comparator Output   |

| REFCLKO                 | 110001    | RPn tied to Reference Clock Output            |

| C4OUT                   | 110010    | RPn tied to Comparator Output 4               |

Note 1: This function is available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This function is available in dsPIC33EPXXXGP/MC50X devices only.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0     | U-0   | U-0   | U-0   | U-0        | U-0   | U-0   | U-0   |

|---------|-------|-------|-------|------------|-------|-------|-------|

| —       | —     | —     | —     | —          | —     | —     | —     |

| bit 15  | •     |       |       |            | •     |       | bit 8 |

|         |       |       |       |            |       |       |       |

| U-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

| _       |       |       |       | OCFAR<6:0> | >     |       |       |

| bit 7   | •     |       |       |            |       |       | bit 0 |

|         |       |       |       |            |       |       |       |

| Leaend: |       |       |       |            |       |       |       |

### REGISTER 11-6: RPINR11: PERIPHERAL PIN SELECT INPUT REGISTER 11

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-7 Unimplemented: Read as '0'

bit 6-0 OCFAR<6:0>: Assign Output Compare Fault A (OCFA) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) 1111001 = Input tied to RPI121

> . 0000001 = Input tied to CMP1 0000000 = Input tied to Vss

### REGISTER 11-7: RPINR12: PERIPHERAL PIN SELECT INPUT REGISTER 12 (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

|                   | R/W-0                                                      | R/W-0                                                                      | R/W-0                                        | R/W-0                      | R/W-0           | R/W-0              | R/W-0           |

|-------------------|------------------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------|----------------------------|-----------------|--------------------|-----------------|

| —                 |                                                            |                                                                            |                                              | FLT2R<6:0>                 |                 |                    |                 |

| bit 15            |                                                            |                                                                            |                                              |                            |                 |                    | bit 8           |

|                   | <b>D</b> 444 0                                             |                                                                            | <b>D</b> 444 A                               | Date                       | <b>D</b> 444 0  | DAVA               | <b>D</b> # 44 0 |

| U-0               | R/W-0                                                      | R/W-0                                                                      | R/W-0                                        | R/W-0                      | R/W-0           | R/W-0              | R/W-0           |

|                   |                                                            |                                                                            |                                              | FLT1R<6:0>                 |                 |                    |                 |

| bit 7             |                                                            |                                                                            |                                              |                            |                 |                    | bit C           |

| Legend:           |                                                            |                                                                            |                                              |                            |                 |                    |                 |

| R = Readabl       | le bit                                                     | W = Writable                                                               | bit                                          | U = Unimplen               | nented bit, rea | ad as '0'          |                 |

| -n = Value at POR |                                                            | '1' = Bit is set                                                           |                                              | '0' = Bit is cleared       |                 | x = Bit is unknown |                 |

| bit 14-8          | (see Table 11                                              | -2 for input pin                                                           | Fault 2 (FLT2)                               | ) to the Corresp<br>nbers) | onding RPn F    | Pin bits           |                 |

| bit 14-8          | (see Table 11<br>1111001 = In                              | : Assign PWM F                                                             | Fault 2 (FLT2)<br>selection nur<br>121       |                            | onding RPn F    | Pin bits           |                 |

| bit 14-8          | (see Table 11<br>1111001 = h<br>0000001 = h                | : Assign PWM F<br>-2 for input pin<br>nput tied to RPI                     | Fault 2 (FLT2)<br>selection nur<br>121<br>P1 |                            | onding RPn F    | Pin bits           |                 |

| bit 14-8<br>bit 7 | (see Table 11<br>1111001 = H<br>0000001 = H<br>0000000 = H | : Assign PWM F<br>-2 for input pin<br>nput tied to RPI<br>nput tied to CMI | Fault 2 (FLT2<br>selection nur<br>121<br>P1  |                            | onding RPn F    | Pin bits           |                 |

#### BUFFER 21-5: ECAN™ MESSAGE BUFFER WORD 4

| R/W-x            | R/W-x | R/W-x            | R/W-x | R/W-x                              | R/W-x | R/W-x           | R/W-x |

|------------------|-------|------------------|-------|------------------------------------|-------|-----------------|-------|

|                  |       |                  | Ву    | /te 3                              |       |                 |       |

| bit 15           |       |                  |       |                                    |       |                 | bit 8 |

|                  |       |                  |       |                                    |       |                 |       |

| R/W-x            | R/W-x | R/W-x            | R/W-x | R/W-x                              | R/W-x | R/W-x           | R/W-x |

|                  |       |                  | Ву    | /te 2                              |       |                 |       |

| bit 7            |       |                  |       |                                    |       |                 | bit 0 |

| Legend:          |       |                  |       |                                    |       |                 |       |

| R = Readable bit |       | W = Writable bit |       | U = Unimplemented bit, read as '0' |       |                 |       |

| -n = Value at P  | OR    | '1' = Bit is set |       | '0' = Bit is clea                  | ared  | x = Bit is unkr | nown  |

bit 15-8 Byte 3<15:8>: ECAN Message Byte 3 bits

bit 7-0 Byte 2<7:0>: ECAN Message Byte 2 bits

#### BUFFER 21-6: ECAN™ MESSAGE BUFFER WORD 5

| R/W-x                              | R/W-x | R/W-x            | R/W-x             | R/W-x                              | R/W-x           | R/W-x | R/W-x |

|------------------------------------|-------|------------------|-------------------|------------------------------------|-----------------|-------|-------|

|                                    |       |                  | B                 | yte 5                              |                 |       |       |

| bit 15                             |       |                  |                   |                                    |                 |       | bit 8 |

| R/W-x                              | R/W-x | R/W-x            | R/W-x             | R/W-x                              | R/W-x           | R/W-x | R/W-x |

|                                    |       |                  |                   | yte 4                              |                 |       |       |

| bit 7                              |       |                  |                   |                                    |                 |       | bit 0 |

|                                    |       |                  |                   |                                    |                 |       |       |

| Legend:                            |       |                  |                   |                                    |                 |       |       |

| R = Readable bit                   |       | W = Writable bit |                   | U = Unimplemented bit, read as '0' |                 |       |       |

| -n = Value at POR '1' = Bit is set |       |                  | '0' = Bit is clea | ared                               | x = Bit is unkr | nown  |       |

bit 15-8 Byte 5<15:8>: ECAN Message Byte 5 bits

bit 7-0 Byte 4<7:0>: ECAN Message Byte 4 bits

## 23.2 ADC Helpful Tips

- 1. The SMPIx control bits in the AD1CON2 register:

- a) Determine when the ADC interrupt flag is set and an interrupt is generated, if enabled.

- b) When the CSCNA bit in the AD1CON2 registers is set to '1', this determines when the ADC analog scan channel list, defined in the AD1CSSL/AD1CSSH registers, starts over from the beginning.

- c) When the DMA peripheral is not used (ADDMAEN = 0), this determines when the ADC Result Buffer Pointer to ADC1BUF0-ADC1BUFF gets reset back to the beginning at ADC1BUF0.

- d) When the DMA peripheral is used (ADDMAEN = 1), this determines when the DMA Address Pointer is incremented after a sample/conversion operation. ADC1BUF0 is the only ADC buffer used in this mode. The ADC Result Buffer Pointer to ADC1BUF0-ADC1BUFF gets reset back to the beginning at ADC1BUF0. The DMA address is incremented after completion of every 32nd sample/conversion operation. Conversion results are stored in the ADC1BUF0 register for transfer to RAM using DMA.

- 2. When the DMA module is disabled (ADDMAEN = 0), the ADC has 16 result buffers. ADC conversion results are stored sequentially in ADC1BUF0-ADC1BUFF, regardless of which analog inputs are being used subject to the SMPIx bits and the condition described in 1c) above. There is no relationship between the ANx input being measured and which ADC buffer (ADC1BUF0-ADC1BUFF) that the conversion results will be placed in.

- 3. When the DMA module is enabled (ADDMAEN = 1), the ADC module has only 1 ADC result buffer (i.e., ADC1BUF0) per ADC peripheral and the ADC conversion result must be read, either by the CPU or DMA Controller, before the next ADC conversion is complete to avoid overwriting the previous value.

- 4. The DONE bit (AD1CON1<0>) is only cleared at the start of each conversion and is set at the completion of the conversion, but remains set indefinitely, even through the next sample phase until the next conversion begins. If application code is monitoring the DONE bit in any kind of software loop, the user must consider this behavior because the CPU code execution is faster than the ADC. As a result, in Manual Sample mode, particularly where the user's code is setting the SAMP bit (AD1CON1<1>), the DONE bit should also be cleared by the user application just before setting the SAMP bit.

5. Enabling op amps, comparator inputs and external voltage references can limit the availability of analog inputs (ANx pins). For example, when Op Amp 2 is enabled, the pins for ANO, AN1 and AN2 are used by the op amp's inputs and output. This negates the usefulness of Alternate Input mode since the MUXA selections use AN0-AN2. Carefully study the ADC block diagram to determine the configuration that will best suit your application. Configuration examples are available in the "Analog-to-Digital Converter (ADC)" (DS70621) section in the "dsPIC33/ PIC24 Family Reference Manual".

### 23.3 ADC Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser:<br>http://www.microchip.com/wwwproducts/ |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | Devices.aspx?dDocName=en555464                                                                                                                          |

### 23.3.1 KEY RESOURCES

- "Analog-to-Digital Converter (ADC)" (DS70621) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

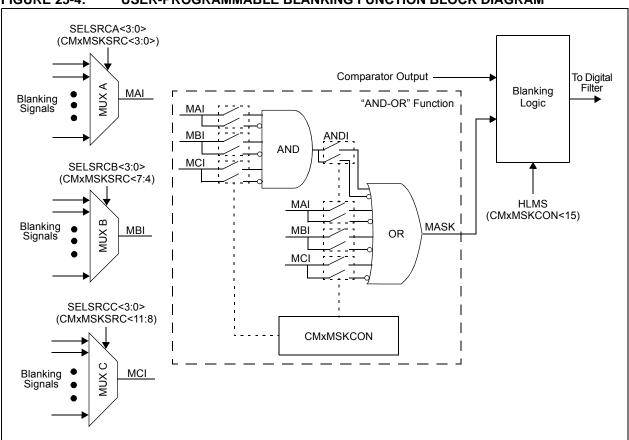

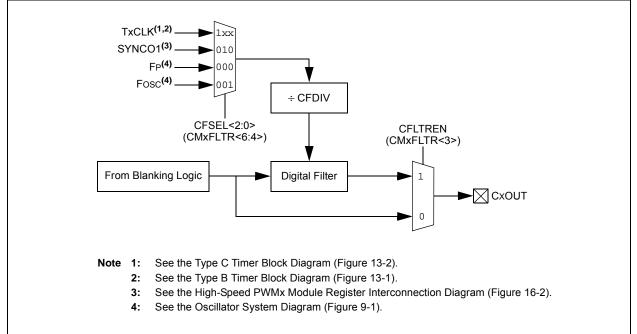

## DIGITAL FILTER INTERCONNECT BLOCK DIAGRAM

# 29.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

- Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- · Simulators

- MPLAB X SIM Software Simulator

- · Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

#### 29.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac  $OS^{®}$  X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

Feature-Rich Editor:

- Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- · Call graph window

- Project-Based Workspaces:

- · Multiple projects

- Multiple tools

- · Multiple configurations

- · Simultaneous debugging sessions

File History and Bug Tracking:

- · Local file history feature

- Built-in support for Bugzilla issue tracker

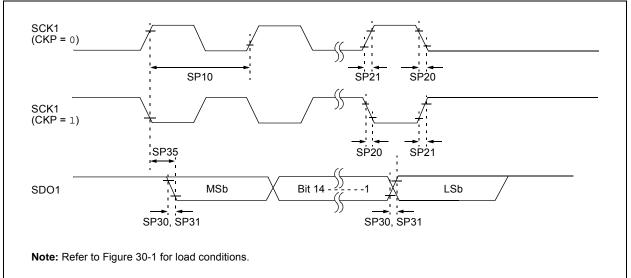

| AC CHARA             | CTERISTICS                               |                                             | $\begin{tabular}{ l l l l l l l l l l l l l l l l l l l$ |     |     |     |

|----------------------|------------------------------------------|---------------------------------------------|----------------------------------------------------------|-----|-----|-----|

| Maximum<br>Data Rate | Master<br>Transmit Only<br>(Half-Duplex) | Master<br>Transmit/Receive<br>(Full-Duplex) | Slave<br>Transmit/Receive<br>(Full-Duplex)               | CKE | СКР | SMP |

| 15 MHz               | Table 30-42                              | _                                           | _                                                        | 0,1 | 0,1 | 0,1 |

| 10 MHz               | _                                        | Table 30-43                                 | —                                                        | 1   | 0,1 | 1   |

| 10 MHz               | —                                        | Table 30-44                                 | —                                                        | 0   | 0,1 | 1   |

| 15 MHz               | —                                        | —                                           | Table 30-45                                              | 1   | 0   | 0   |

| 11 MHz               | —                                        | —                                           | Table 30-46                                              | 1   | 1   | 0   |

| 15 MHz               | _                                        | —                                           | Table 30-47                                              | 0   | 1   | 0   |

| 11 MHz               | _                                        | _                                           | Table 30-48                                              | 0   | 0   | 0   |

#### TABLE 30-41: SPI1 MAXIMUM DATA/CLOCK RATE SUMMARY

### FIGURE 30-22: SPI1 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 0) TIMING CHARACTERISTICS

# 33.0 PACKAGING INFORMATION

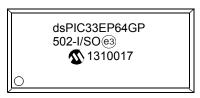

## 33.1 Package Marking Information

## 28-Lead SPDIP

#### 28-Lead SOIC (.300")

28-Lead SSOP

Example dsPIC33EP64GP 502-I/SP@3 1310017

## Example

#### Example

28-Lead QFN-S (6x6x0.9 mm)

Example

| Legend | : XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>*                                                                                                                                                                      | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator ((e3))<br>can be found on the outer packaging for this package. |  |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|        | In the event the full Microchip part number cannot be marked on one line, it will<br>be carried over to the next line, thus limiting the number of available<br>characters for customer-specific information. |                                                                                                                                                                                                                                                                                                                                                                                |  |