Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 70 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 25                                                                             |

| Program Memory Size        | 32KB (10.7K x 24)                                                              |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 2K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 8x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

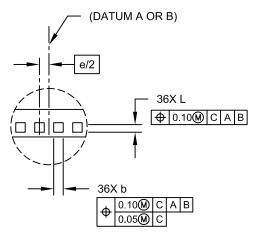

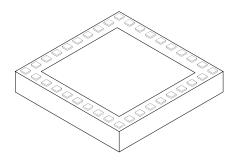

| Package / Case             | 36-VFTLA Exposed Pad                                                           |

| Supplier Device Package    | 36-VTLA (5x5)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep32gp203t-i-tl |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

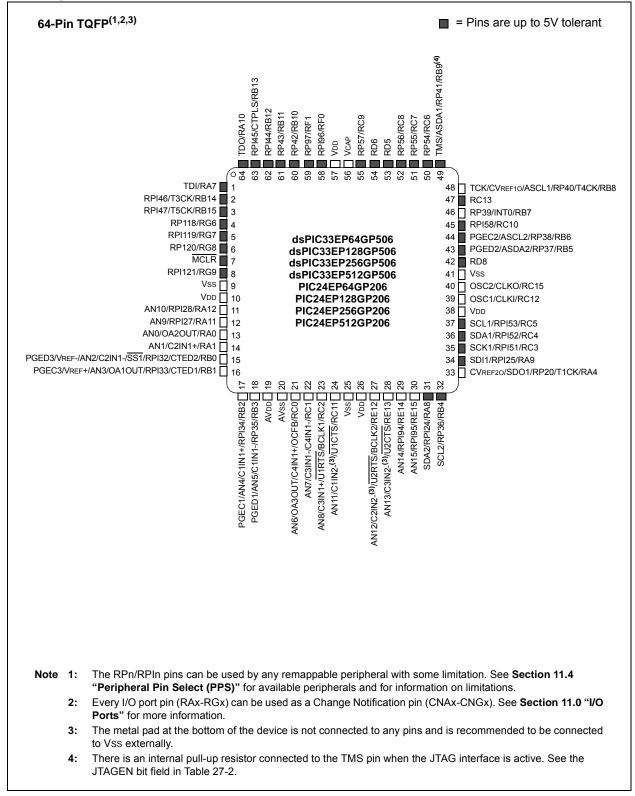

## **Pin Diagrams (Continued)**

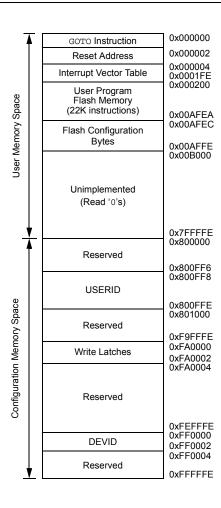

### FIGURE 4-2: PROGRAM MEMORY MAP FOR dsPIC33EP64GP50X, dsPIC33EP64MC20X/50X AND PIC24EP64GP/MC20X DEVICES

Note: Memory areas are not shown to scale.

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8  | Bit 7 | Bit 6  | Bit 5       | Bit 4  | Bit 3  | Bit 2    | Bit 1       | Bit 0         | All<br>Resets |

|--------------|-------|--------|--------|------------|--------|--------|--------|------------|--------|-------|--------|-------------|--------|--------|----------|-------------|---------------|---------------|

| IFS0         | 0800  | _      | DMA1IF | AD1IF      | U1TXIF | U1RXIF | SPI1IF | SPI1EIF    | T3IF   | T2IF  | OC2IF  | IC2IF       | DMA0IF | T1IF   | OC1IF    | IC1IF       | <b>INTOIF</b> | 0000          |

| IFS1         | 0802  | U2TXIF | U2RXIF | INT2IF     | T5IF   | T4IF   | OC4IF  | OC3IF      | DMA2IF | _     | _      | _           | INT1IF | CNIF   | CMIF     | MI2C1IF     | SI2C1IF       | 0000          |

| IFS2         | 0804  | _      | _      | _          | _      | —      |        | _          | —      | _     | IC4IF  | IC3IF       | DMA3IF | C1IF   | C1RXIF   | SPI2IF      | SPI2EIF       | 0000          |

| IFS3         | 0806  | _      | _      | _          | _      | —      |        | _          | —      | _     | _      | _           | —      | _      | MI2C2IF  | SI2C2IF     | —             | 0000          |

| IFS4         | 0808  | _      | _      | CTMUIF     | _      | —      |        | _          | —      | _     | C1TXIF | _           | —      | CRCIF  | U2EIF    | U1EIF       | —             | 0000          |

| IFS6         | 080C  | _      | _      | _          | _      | —      |        | _          | —      | _     | _      | _           | —      | _      | —        | _           | PWM3IF        | 0000          |

| IFS8         | 0810  | JTAGIF | ICDIF  | —          | _      | —      |        | _          | —      | _     | _      | _           | —      | _      | —        | _           | —             | 0000          |

| IFS9         | 0812  |        |        | _          | _      | _      | _      | _          | _      | _     | PTG3IF | PTG2IF      | PTG1IF | PTG0IF | PTGWDTIF | PTGSTEPIF   | _             | 0000          |

| IEC0         | 0820  |        | DMA1IE | AD1IE      | U1TXIE | U1RXIE | SPI1IE | SPI1EIE    | T3IE   | T2IE  | OC2IE  | IC2IE       | DMA0IE | T1IE   | OC1IE    | IC1IE       | INT0IE        | 0000          |

| IEC1         | 0822  | U2TXIE | U2RXIE | INT2IE     | T5IE   | T4IE   | OC4IE  | OC3IE      | DMA2IE | _     | _      | _           | INT1IE | CNIE   | CMIE     | MI2C1IE     | SI2C1IE       | 0000          |

| IEC2         | 0824  |        |        | _          | _      | _      | _      | _          | _      | _     | IC4IE  | IC3IE       | DMA3IE | C1IE   | C1RXIE   | SPI2IE      | SPI2EIE       | 0000          |

| IEC3         | 0826  | _      | _      | —          | —      |        | _      |            | _      | _     | _      |             |        | —      | MI2C2IE  | SI2C2IE     | _             | 0000          |

| IEC4         | 0828  | _      | _      | CTMUIE     | —      |        |        |            | _      | —     | C1TXIE |             |        | CRCIE  | U2EIE    | U1EIE       |               | 0000          |

| IEC8         | 0830  | JTAGIE | ICDIE  | —          | —      |        | _      |            | _      | _     | _      |             |        | —      | _        | _           | _             | 0000          |

| IEC9         | 0832  | _      | _      | —          | —      |        | _      |            | _      | _     | PTG3IE | PTG2IE      | PTG1IE | PTG0IE | PTGWDTIE | PTGSTEPIE   | _             | 0000          |

| IPC0         | 0840  |        |        | T1IP<2:0>  | >      | _      | (      | OC1IP<2:0  | >      | _     |        | IC1IP<2:0>  |        | _      |          | NT0IP<2:0>  |               | 4444          |

| IPC1         | 0842  |        |        | T2IP<2:0>  | >      | _      | (      | C2IP<2:0   | >      | _     |        | IC2IP<2:0>  |        | _      | D        | MA0IP<2:0>  |               | 4444          |

| IPC2         | 0844  |        | ι      | J1RXIP<2:0 | 0>     | _      | Ş      | SPI1IP<2:0 | )>     | _     |        | SPI1EIP<2:0 | >      | _      |          | T3IP<2:0>   |               | 4444          |

| IPC3         | 0846  |        |        | _          | _      | _      | C      | MA1IP<2:   | 0>     | _     |        | AD1IP<2:0>  |        | _      | U        | J1TXIP<2:0> |               | 0444          |

| IPC4         | 0848  |        |        | CNIP<2:0   | >      | _      |        | CMIP<2:0   | >      | _     | I      | WI2C1IP<2:0 | >      | _      | S        | I2C1IP<2:0> |               | 4444          |

| IPC5         | 084A  |        |        | _          | _      | _      | _      | _          | _      | _     | _      | _           | _      | _      |          | NT1IP<2:0>  |               | 0004          |

| IPC6         | 084C  |        |        | T4IP<2:0>  | >      | _      | (      | C4IP<2:0   | >      | _     |        | OC3IP<2:0>  |        | _      | D        | MA2IP<2:0>  |               | 4444          |

| IPC7         | 084E  |        | ι      | U2TXIP<2:0 | )>     | _      | L      | I2RXIP<2:  | 0>     | _     |        | INT2IP<2:0> | •      | _      |          | T5IP<2:0>   |               | 4444          |

| IPC8         | 0850  |        |        | C1IP<2:0>  | >      | _      | C      | 1RXIP<2:   | 0>     | _     |        | SPI2IP<2:0> | •      | _      | S        | PI2EIP<2:0> |               | 4444          |

| IPC9         | 0852  | _      | _      | _          | _      | _      |        | IC4IP<2:0  | >      | _     |        | IC3IP<2:0>  |        | _      | D        | MA3IP<2:0>  |               | 0444          |

| IPC11        | 0856  | _      | _      | _          | _      | _      |        | _          | —      | _     | _      | _           | —      | _      | _        | _           | _             | 0000          |

| IPC12        | 0858  | _      | _      | _          | _      | _      | N      | II2C2IP<2: | 0>     | _     |        | SI2C2IP<2:0 | >      | _      | _        | _           | _             | 0440          |

| IPC16        | 0860  | _      |        | CRCIP<2:0  | )>     | _      |        | U2EIP<2:0  | >      | _     |        | U1EIP<2:0>  |        | _      | _        | _           | _             | 4440          |

| IPC17        | 0862  | _      | _      | _          | _      | _      | C      | 1TXIP<2:   | )>     | _     | _      | _           | —      | _      | _        | _           | _             | 0400          |

| IPC19        | 0866  | _      | _      | —          | _      | _      |        | _          | —      | _     |        | CTMUIP<2:0  | >      | _      | —        |             |               | 0040          |

| IPC35        | 0886  | _      |        | JTAGIP<2:0 | )>     | _      |        | ICDIP<2:0  | >      | _     | _      | —           | _      | _      | —        | _           | _             | 4400          |

| IPC36        | 0888  | _      | F      | PTG0IP<2:  | 0>     | _      | PT     | GWDTIP<    | 2:0>   | _     | PT     | GSTEPIP<2   | :0>    | _      | _        | _           | _             | 4440          |

| IPC37        | 088A  | _      | _      | _          | _      | _      | F      | TG3IP<2:   | )>     | _     |        | PTG2IP<2:0  | >      | _      | Р        | TG1IP<2:0>  |               | 0444          |

## TABLE 4-5: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33EPXXXGP50X DEVICES ONLY

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Allocating different Page registers for read and write access allows the architecture to support data movement between different pages in data memory. This is accomplished by setting the DSRPAG register value to the page from which you want to read, and configuring the DSWPAG register to the page to which it needs to be written. Data can also be moved from different PSV to EDS pages, by configuring the DSRPAG and DSWPAG registers to address PSV and EDS space, respectively. The data can be moved between pages by a single instruction.

When an EDS or PSV page overflow or underflow occurs, EA<15> is cleared as a result of the register indirect EA calculation. An overflow or underflow of the EA in the EDS or PSV pages can occur at the page boundaries when:

- The initial address prior to modification addresses an EDS or PSV page

- The EA calculation uses Pre-Modified or Post-Modified Register Indirect Addressing; however, this does not include Register Offset Addressing

In general, when an overflow is detected, the DSxPAG register is incremented and the EA<15> bit is set to keep the base address within the EDS or PSV window. When an underflow is detected, the DSxPAG register is decremented and the EA<15> bit is set to keep the base address within the EDS or PSV window. This creates a linear EDS and PSV address space, but only when using Register Indirect Addressing modes.

Exceptions to the operation described above arise when entering and exiting the boundaries of Page 0, EDS and PSV spaces. Table 4-61 lists the effects of overflow and underflow scenarios at different boundaries.

In the following cases, when overflow or underflow occurs, the EA<15> bit is set and the DSxPAG is not modified; therefore, the EA will wrap to the beginning of the current page:

- · Register Indirect with Register Offset Addressing

- Modulo Addressing

- · Bit-Reversed Addressing

| 0/11        |                     |                | Before       |                        | After          |              |                        |  |  |  |

|-------------|---------------------|----------------|--------------|------------------------|----------------|--------------|------------------------|--|--|--|

| O/U,<br>R/W | Operation           | DSxPAG         | DS<br>EA<15> | Page<br>Description    | DSxPAG         | DS<br>EA<15> | Page<br>Description    |  |  |  |

| O,<br>Read  |                     | DSRPAG = 0x1FF | 1            | EDS: Last page         | DSRPAG = 0x1FF | 0            | See Note 1             |  |  |  |

| O,<br>Read  | [++Wn]              | DSRPAG = 0x2FF | 1            | PSV: Last lsw<br>page  | DSRPAG = 0x300 | 1            | PSV: First MSB<br>page |  |  |  |

| O,<br>Read  | <b>Or</b><br>[Wn++] | DSRPAG = 0x3FF | 1            | PSV: Last MSB<br>page  | DSRPAG = 0x3FF | 0            | See Note 1             |  |  |  |

| O,<br>Write |                     | DSWPAG = 0x1FF | 1            | EDS: Last page         | DSWPAG = 0x1FF | 0            | See Note 1             |  |  |  |

| U,<br>Read  |                     | DSRPAG = 0x001 | 1            | PSV page               | DSRPAG = 0x001 | 0            | See Note 1             |  |  |  |

| U,<br>Read  | [Wn]<br>Or<br>[Wn]  | DSRPAG = 0x200 | 1            | PSV: First Isw<br>page | DSRPAG = 0x200 | 0            | See Note 1             |  |  |  |

| U,<br>Read  | [ //11 - ]          | DSRPAG = 0x300 | 1            | PSV: First MSB<br>page | DSRPAG = 0x2FF | 1            | PSV: Last Isw<br>page  |  |  |  |

# TABLE 4-61: OVERFLOW AND UNDERFLOW SCENARIOS AT PAGE 0, EDS and PSV SPACE BOUNDARIES<sup>(2,3,4)</sup>

Legend: O = Overflow, U = Underflow, R = Read, W = Write

Note 1: The Register Indirect Addressing now addresses a location in the base Data Space (0x0000-0x8000).

2: An EDS access with DSxPAG = 0x000 will generate an address error trap.

- **3:** Only reads from PS are supported using DSRPAG. An attempt to write to PS using DSWPAG will generate an address error trap.

- 4: Pseudo-Linear Addressing is not supported for large offsets.

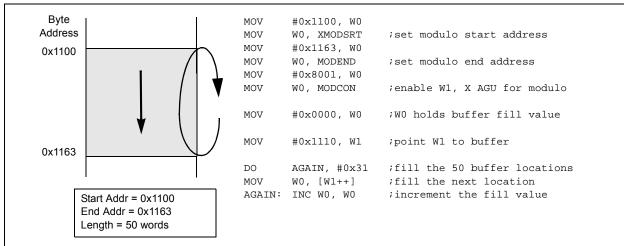

## 4.6 Modulo Addressing (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X Devices Only)

Modulo Addressing mode is a method of providing an automated means to support circular data buffers using hardware. The objective is to remove the need for software to perform data address boundary checks when executing tightly looped code, as is typical in many DSP algorithms.

Modulo Addressing can operate in either Data or Program Space (since the Data Pointer mechanism is essentially the same for both). One circular buffer can be supported in each of the X (which also provides the pointers into Program Space) and Y Data Spaces. Modulo Addressing can operate on any W Register Pointer. However, it is not advisable to use W14 or W15 for Modulo Addressing since these two registers are used as the Stack Frame Pointer and Stack Pointer, respectively.

In general, any particular circular buffer can be configured to operate in only one direction, as there are certain restrictions on the buffer start address (for incrementing buffers) or end address (for decrementing buffers), based upon the direction of the buffer.

The only exception to the usage restrictions is for buffers that have a power-of-two length. As these buffers satisfy the start and end address criteria, they can operate in a bidirectional mode (that is, address boundary checks are performed on both the lower and upper address boundaries).

## 4.6.1 START AND END ADDRESS

The Modulo Addressing scheme requires that a starting and ending address be specified, and loaded into the 16-bit Modulo Buffer Address registers: XMODSRT, XMODEND, YMODSRT and YMODEND (see Table 4-1).

| Note: | Y space Modulo Addressing EA calcula- |

|-------|---------------------------------------|

|       | tions assume word-sized data (LSb of  |

|       | every EA is always clear).            |

The length of a circular buffer is not directly specified. It is determined by the difference between the corresponding start and end addresses. The maximum possible length of the circular buffer is 32K words (64 Kbytes).

## 4.6.2 W ADDRESS REGISTER SELECTION

The Modulo and Bit-Reversed Addressing Control register, MODCON<15:0>, contains enable flags as well as a W register field to specify the W Address registers. The XWM and YWM fields select the registers that operate with Modulo Addressing:

- If XWM = 1111, X RAGU and X WAGU Modulo Addressing is disabled

- If YWM = 1111, Y AGU Modulo Addressing is disabled

The X Address Space Pointer W register (XWM), to which Modulo Addressing is to be applied, is stored in MODCON<3:0> (see Table 4-1). Modulo Addressing is enabled for X Data Space when XWM is set to any value other than '1111' and the XMODEN bit is set (MODCON<15>).

The Y Address Space Pointer W register (YWM), to which Modulo Addressing is to be applied, is stored in MODCON<7:4>. Modulo Addressing is enabled for Y Data Space when YWM is set to any value other than '1111' and the YMODEN bit is set at MODCON<14>.

## FIGURE 4-20: MODULO ADDRESSING OPERATION EXAMPLE

| U-0    | U-0      | U-0 | U-0   | U-0   | U-0   | U-0   | R/W-0 |

|--------|----------|-----|-------|-------|-------|-------|-------|

| —      | _        | -   | —     | —     | —     | —     | IC32  |

| bit 15 |          |     |       |       |       |       | bit 8 |

|        |          |     |       |       |       |       |       |

| R/W-0  | R/W/HS-0 | U-0 | R/W-0 | R/W-1 | R/W-1 | R/W-0 | R/W-1 |

## REGISTER 14-2: ICxCON2: INPUT CAPTURE x CONTROL REGISTER 2

| bit 7            |                      |                                    | bit 0 |

|------------------|----------------------|------------------------------------|-------|

|                  |                      |                                    |       |

| Legend:          | HS = Hardware Settal | ole bit                            |       |

| R = Readable bit | W = Writable bit     | U = Unimplemented bit, read as '0' |       |

SYNCSEL4<sup>(4)</sup> SYNCSEL3<sup>(4)</sup> SYNCSEL2<sup>(4)</sup> SYNCSEL1<sup>(4)</sup>

SYNCSEL0(4)

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

|-------------------|------------------|----------------------|--------------------|

bit 15-9 Unimplemented: Read as '0'

TRIGSTAT<sup>(3)</sup>

ICTRIG<sup>(2)</sup>

bit 8

- IC32: Input Capture 32-Bit Timer Mode Select bit (Cascade mode)

- 1 = Odd IC and Even IC form a single 32-bit input capture module<sup>(1)</sup>

- 0 = Cascade module operation is disabled

## bit 7 ICTRIG: Input Capture Trigger Operation Select bit<sup>(2)</sup>

- 1 = Input source used to trigger the input capture timer (Trigger mode)

- 0 = Input source used to synchronize the input capture timer to a timer of another module (Synchronization mode)

## bit 6 **TRIGSTAT:** Timer Trigger Status bit<sup>(3)</sup>

- 1 = ICxTMR has been triggered and is running

- 0 = ICxTMR has not been triggered and is being held clear

## bit 5 Unimplemented: Read as '0'

- **Note 1:** The IC32 bit in both the Odd and Even IC must be set to enable Cascade mode.

- 2: The input source is selected by the SYNCSEL<4:0> bits of the ICxCON2 register.

- **3:** This bit is set by the selected input source (selected by SYNCSEL<4:0> bits). It can be read, set and cleared in software.

- 4: Do not use the ICx module as its own Sync or Trigger source.

- 5: This option should only be selected as a trigger source and not as a synchronization source.

- 6: Each Input Capture x (ICx) module has one PTG input source. See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for more information.

PTGO8 = IC1 PTGO9 = IC2 PTGO10 = IC3 PTGO11 = IC4

DS70000657H-page 216

## 16.3 PWMx Control Registers

#### REGISTER 16-1: PTCON: PWMx TIME BASE CONTROL REGISTER

| R/W-0  | U-0 | R/W-0  | HS/HC-0 | R/W-0 | R/W-0               | R/W-0                  | R/W-0                  |

|--------|-----|--------|---------|-------|---------------------|------------------------|------------------------|

| PTEN   | —   | PTSIDL | SESTAT  | SEIEN | EIPU <sup>(1)</sup> | SYNCPOL <sup>(1)</sup> | SYNCOEN <sup>(1)</sup> |

| bit 15 |     |        |         |       |                     |                        | bit 8                  |

| R/W-0                 | R/W-0                   | R/W-0                   | R/W-0                   | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  |

|-----------------------|-------------------------|-------------------------|-------------------------|------------------------|------------------------|------------------------|------------------------|

| SYNCEN <sup>(1)</sup> | SYNCSRC2 <sup>(1)</sup> | SYNCSRC1 <sup>(1)</sup> | SYNCSRC0 <sup>(1)</sup> | SEVTPS3 <sup>(1)</sup> | SEVTPS2 <sup>(1)</sup> | SEVTPS1 <sup>(1)</sup> | SEVTPS0 <sup>(1)</sup> |

| bit 7                 | •                       |                         |                         |                        |                        |                        | bit 0                  |

| Legend:           | HC = Hardware Clearable bit | HS = Hardware Settable bit | t                  |

|-------------------|-----------------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, re  | ad as '0'          |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared       | x = Bit is unknown |

| bit 15  | PTEN: PWMx Module Enable bit                                                                                                                            |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = PWMx module is enabled</li> <li>0 = PWMx module is disabled</li> </ul>                                                                     |

| bit 14  | Unimplemented: Read as '0'                                                                                                                              |

| bit 13  | PTSIDL: PWMx Time Base Stop in Idle Mode bit                                                                                                            |

|         | <ul> <li>1 = PWMx time base halts in CPU Idle mode</li> <li>0 = PWMx time base runs in CPU Idle mode</li> </ul>                                         |

| bit 12  | SESTAT: Special Event Interrupt Status bit                                                                                                              |

|         | <ul> <li>1 = Special event interrupt is pending</li> <li>0 = Special event interrupt is not pending</li> </ul>                                          |

| bit 11  | SEIEN: Special Event Interrupt Enable bit                                                                                                               |

|         | 1 = Special event interrupt is enabled                                                                                                                  |

|         | 0 = Special event interrupt is disabled                                                                                                                 |

| bit 10  | EIPU: Enable Immediate Period Updates bit <sup>(1)</sup>                                                                                                |

|         | <ul> <li>1 = Active Period register is updated immediately</li> <li>0 = Active Period register updates occur on PWMx cycle boundaries</li> </ul>        |

| bit 9   | SYNCPOL: Synchronize Input and Output Polarity bit <sup>(1)</sup>                                                                                       |

|         | 1 = SYNCI1/SYNCO1 polarity is inverted (active-low)                                                                                                     |

|         | 0 = SYNCI1/SYNCO1 is active-high                                                                                                                        |

| bit 8   | SYNCOEN: Primary Time Base Sync Enable bit <sup>(1)</sup>                                                                                               |

|         | 1 = SYNCO1 output is enabled                                                                                                                            |

| L:1 7   | 0 = SYNCO1 output is disabled                                                                                                                           |

| bit 7   | SYNCEN: External Time Base Synchronization Enable bit <sup>(1)</sup>                                                                                    |

|         | <ul> <li>1 = External synchronization of primary time base is enabled</li> <li>0 = External synchronization of primary time base is disabled</li> </ul> |

|         |                                                                                                                                                         |

| Note 1: | These bits should be changed only when PTEN = 0. In addition, when using the SYNCI1 feature, the user                                                   |

|         | application must program the period register with a value that is slightly larger than the expected period of                                           |

the external synchronization input signal.

2: See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for information on this selection.

## 22.0 CHARGE TIME MEASUREMENT UNIT (CTMU)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Charge Time Measurement Unit (CTMU)" (DS70661) in the "dsPIC33/PIC24 Family Reference Manual", which is available on the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Charge Time Measurement Unit is a flexible analog module that provides accurate differential time measurement between pulse sources, as well as asynchronous pulse generation. Its key features include:

- Four Edge Input Trigger Sources

- Polarity Control for Each Edge Source

- Control of Edge Sequence

- Control of Response to Edges

- · Precise Time Measurement Resolution of 1 ns

- Accurate Current Source Suitable for Capacitive Measurement

- On-Chip Temperature Measurement using a Built-in Diode

Together with other on-chip analog modules, the CTMU can be used to precisely measure time, measure capacitance, measure relative changes in capacitance or generate output pulses that are independent of the system clock.

The CTMU module is ideal for interfacing with capacitive-based sensors. The CTMU is controlled through three registers: CTMUCON1, CTMUCON2 and CTMUICON. CTMUCON1 and CTMUCON2 enable the module and control edge source selection, edge source polarity selection and edge sequencing. The CTMUICON register controls the selection and trim of the current source.

| R/W-0              | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0              | R/W-0 |  |

|--------------------|-------|------------------|-------|------------------|-----------------|--------------------|-------|--|

| CSS15              | CSS14 | CSS13            | CSS12 | CSS11            | CSS10           | CSS9               | CSS8  |  |

| bit 15             |       |                  |       | ·                | •               | ·                  | bit 8 |  |

|                    |       |                  |       |                  |                 |                    |       |  |

| R/W-0              | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0              | R/W-0 |  |

| CSS7               | CSS6  | CSS5             | CSS4  | CSS3             | CSS2            | CSS1               | CSS0  |  |

| bit 7              | -     |                  |       |                  | •               |                    | bit ( |  |

|                    |       |                  |       |                  |                 |                    |       |  |

| Legend:            |       |                  |       |                  |                 |                    |       |  |

| R = Readable bit W |       | W = Writable     | bit   | U = Unimple      | mented bit, rea | d as '0'           |       |  |

| -n = Value at POR  |       | '1' = Bit is set |       | '0' = Bit is cle | eared           | x = Bit is unknown |       |  |

## REGISTER 23-8: AD1CSSL: ADC1 INPUT SCAN SELECT REGISTER LOW<sup>(1,2)</sup>

bit 15-0 CSS<15:0>: ADC1 Input Scan Selection bits

1 = Selects ANx for input scan

0 = Skips ANx for input scan

**Note 1:** On devices with less than 16 analog inputs, all AD1CSSL bits can be selected by the user. However, inputs selected for scan, without a corresponding input on the device, convert VREFL.

**2:** CSSx = ANx, where x = 0-15.

## 24.2 PTG Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

## 24.2.1 KEY RESOURCES

- "Peripheral Trigger Generator" (DS70669) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

## REGISTER 24-4: PTGT0LIM: PTG TIMER0 LIMIT REGISTER<sup>(1)</sup>

| R/W-0                                             | R/W-0          | R/W-0            | R/W-0 | R/W-0             | R/W-0    | R/W-0              | R/W-0 |  |  |  |  |  |

|---------------------------------------------------|----------------|------------------|-------|-------------------|----------|--------------------|-------|--|--|--|--|--|

|                                                   | PTGT0LIM<15:8> |                  |       |                   |          |                    |       |  |  |  |  |  |

| bit 15                                            |                |                  |       |                   |          |                    | bit 8 |  |  |  |  |  |

|                                                   |                |                  |       |                   |          |                    |       |  |  |  |  |  |

| R/W-0                                             | R/W-0          | R/W-0            | R/W-0 | R/W-0             | R/W-0    | R/W-0              | R/W-0 |  |  |  |  |  |

|                                                   |                |                  | PTGT0 | LIM<7:0>          |          |                    |       |  |  |  |  |  |

| bit 7                                             |                |                  |       |                   |          |                    | bit 0 |  |  |  |  |  |

|                                                   |                |                  |       |                   |          |                    |       |  |  |  |  |  |

| Legend:                                           |                |                  |       |                   |          |                    |       |  |  |  |  |  |

| R = Readable bit W = Writable bit U = Unimplement |                |                  |       | nented bit, rea   | d as '0' |                    |       |  |  |  |  |  |

| -n = Value at P                                   | POR            | '1' = Bit is set |       | '0' = Bit is clea | ared     | x = Bit is unknown |       |  |  |  |  |  |

## bit 15-0 **PTGT0LIM<15:0>:** PTG Timer0 Limit Register bits General Purpose Timer0 Limit register (effective only with a PTGT0 Step command).

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

## REGISTER 24-5: PTGT1LIM: PTG TIMER1 LIMIT REGISTER<sup>(1)</sup>

| R/W-0          | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|----------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| PTGT1LIM<15:8> |       |       |       |       |       |       |       |  |  |

| bit 15         |       |       |       |       |       |       |       |  |  |

|                |       |       |       |       |       |       |       |  |  |

| R/W-0         | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|---------------|-------|-------|-------|-------|-------|-------|-------|--|

| PTGT1LIM<7:0> |       |       |       |       |       |       |       |  |

| bit 7         |       |       |       |       |       |       |       |  |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-0 **PTGT1LIM<15:0>:** PTG Timer1 Limit Register bits

General Purpose Timer1 Limit register (effective only with a PTGT1 Step command).

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

| File<br>Name | Address          | Device<br>Memory<br>Size<br>(Kbytes) | Bits 23-8 | Bit 7                   | Bit 6                  | Bit 5    | Bit 4                   | Bit 3                   | Bit 2        | Bit 1     | Bit 0   |

|--------------|------------------|--------------------------------------|-----------|-------------------------|------------------------|----------|-------------------------|-------------------------|--------------|-----------|---------|

| Reserved     | 0057EC           | 32                                   |           |                         |                        |          |                         |                         |              |           |         |

|              | 00AFEC           | 64                                   |           |                         |                        |          |                         |                         |              |           |         |

|              | 0157EC           | 128                                  | _         | _                       | _                      | _        | _                       | _                       | _            | —         | _       |

|              | 02AFEC           | 256                                  |           |                         |                        |          |                         |                         |              |           |         |

|              | 0557EC           | 512                                  |           |                         |                        |          |                         |                         |              |           |         |

| Reserved     | 0057EE           | 32                                   |           |                         |                        |          |                         |                         |              |           |         |

|              | 00AFEE           | 64                                   |           |                         |                        |          |                         |                         |              |           |         |

|              | 0157EE           | 128                                  | _         | _                       | _                      | _        | _                       | _                       | _            | _         | _       |

|              | 02AFEE           | 256                                  |           |                         |                        |          |                         |                         |              |           |         |

|              | 0557EE           | 512                                  |           |                         |                        |          |                         |                         |              |           |         |

| FICD         | 0057F0           | 32                                   |           |                         |                        |          |                         |                         |              |           |         |

|              | 00AFF0           | 64                                   | -         |                         |                        |          |                         |                         |              |           |         |

|              | 0157F0           | 128                                  |           | Reserved <sup>(3)</sup> | _                      | JTAGEN   | Reserved <sup>(2)</sup> | Reserved <sup>(3)</sup> | _            | ICS<      | :1.0>   |

|              | 02AFF0           | 256                                  |           |                         |                        | 01110211 |                         |                         |              |           | 1.0-    |

|              | 0557F0           | 512                                  |           |                         |                        |          |                         |                         |              |           |         |

| FPOR         | 0057F2           | 32                                   |           |                         |                        |          |                         |                         |              |           |         |

|              | 003712<br>00AFF2 | 64                                   |           |                         |                        |          |                         |                         |              |           |         |

|              | 0157F2           | 128                                  |           | WDTV                    | VIN<1:0>               | ALTI2C2  | ALTI2C1                 | Reserved <sup>(3)</sup> | _            |           |         |

|              | 013712<br>02AFF2 | 256                                  |           | VUDIV                   |                        | ALTIZOZ  | ALIIZOI                 | Tteserveu.              |              |           | _       |

|              | 02AFF2<br>0557F2 | 512                                  |           |                         |                        |          |                         |                         |              |           |         |

| FWDT         | 0057F2           | 32                                   |           |                         |                        |          |                         |                         |              |           |         |

|              |                  |                                      |           |                         |                        |          |                         |                         |              |           |         |

|              | 00AFF4           | 64                                   |           |                         |                        |          | WDTDDE                  |                         | WDTPOST<3:0> |           |         |

|              | 0157F4           | 128                                  | —         | FWDTEN                  | WINDIS                 | PLLKEN   | WDTPRE                  |                         |              |           |         |

|              | 02AFF4           | 256                                  |           |                         |                        |          |                         |                         |              |           |         |

| 5000         | 0557F4           | 512                                  |           |                         |                        |          |                         |                         | r            |           |         |

| FOSC         | 0057F6           | 32                                   |           |                         |                        |          |                         |                         |              |           |         |

|              | 00AFF6           | 64                                   | -         |                         |                        |          |                         |                         |              |           |         |

|              | 0157F6           | 128                                  | —         | FCKS                    | SM<1:0>                | IOL1WAY  | -                       | -                       | OSCIOFNC     | POSCN     | ID<1:0> |

|              | 02AFF6           | 256                                  |           |                         |                        |          |                         |                         |              |           |         |

|              | 0557F6           | 512                                  |           |                         |                        |          |                         |                         |              |           |         |

| FOSCSEL      | 0057F8           | 32                                   |           |                         |                        |          |                         |                         |              |           |         |

|              | 00AFF8           | 64                                   |           |                         | (4)                    |          |                         |                         |              |           |         |

|              | 0157F8           | 128                                  | —         | IESO                    | PWMLOCK <sup>(1)</sup> | —        | -                       | -                       | F            | NOSC<2:0> |         |

|              | 02AFF8           | 256                                  |           |                         |                        |          |                         |                         |              |           |         |

|              | 0557F8           | 512                                  |           |                         |                        |          |                         |                         |              |           |         |

| FGS          | 0057FA           | 32                                   |           |                         |                        |          |                         |                         |              |           |         |

|              | 00AFFA           | 64                                   |           |                         |                        |          |                         |                         |              |           |         |

|              | 0157FA           | 128                                  | —         | —                       | —                      | —        | —                       | —                       | —            | GCP       | GWRP    |

|              | 02AFFA           | 256                                  |           |                         |                        |          |                         |                         |              |           |         |

|              | 0557FA           | 512                                  |           |                         |                        |          |                         |                         |              |           |         |

| Reserved     | 0057FC           | 32                                   |           |                         |                        |          |                         |                         |              |           |         |

|              | 00AFFC           | 64                                   |           |                         |                        |          |                         |                         |              |           |         |

|              | 0157FC           | 128                                  | —         | -                       | —                      | —        | —                       | —                       | —            | —         | —       |

|              | 02AFFC           | 256                                  |           |                         |                        |          |                         |                         |              |           |         |

|              | 0557FC           | 512                                  |           |                         |                        |          |                         |                         |              |           |         |

| Reserved     | 057FFE           | 32                                   |           |                         |                        |          |                         |                         |              |           |         |

|              | 00AFFE           | 64                                   |           |                         |                        |          |                         |                         |              |           |         |

|              | 0157FE           | 128                                  | _         | -                       | _                      | _        | —                       | -                       |              |           | _       |

|              | 02AFFE           | 256                                  |           |                         |                        |          |                         |                         |              |           |         |

|              | 0557FE           | 512                                  |           |                         |                        |          |                         |                         |              |           |         |

## TABLE 27-1: CONFIGURATION BYTE REGISTER MAP

Legend: — = unimplemented, read as '1'.

Note 1: This bit is only available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

**2:** This bit is reserved and must be programmed as '0'.

3: These bits are reserved and must be programmed as '1'.

| Base<br>Instr<br># | Assembly<br>Mnemonic |        | Assembly Syntax                                                | Description                                       | # of<br>Words | # of<br>Cycles <sup>(2)</sup> | Status Flags<br>Affected        |

|--------------------|----------------------|--------|----------------------------------------------------------------|---------------------------------------------------|---------------|-------------------------------|---------------------------------|

| 53                 | NEG                  | NEG    | <sub>Acc</sub> (1)                                             | Negate Accumulator                                | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB         |

|                    |                      | NEG    | f                                                              | $f = \overline{f} + 1$                            | 1             | 1                             | C,DC,N,OV,Z                     |

|                    |                      | NEG    | f,WREG                                                         | WREG = $\overline{f}$ + 1                         | 1             | 1                             | C,DC,N,OV,Z                     |

|                    |                      | NEG    | Ws,Wd                                                          | $Wd = \overline{Ws} + 1$                          | 1             | 1                             | C,DC,N,OV,Z                     |

| 54                 | NOP                  | NOP    | · · · · · · · · · · · · · · · · · · ·                          | No Operation                                      | 1             | 1                             | None                            |

|                    |                      | NOPR   |                                                                | No Operation                                      | 1             | 1                             | None                            |

| 55                 | POP                  | POP    | f                                                              | Pop f from Top-of-Stack (TOS)                     | 1             | 1                             | None                            |

|                    |                      | POP    | Wdo                                                            | Pop from Top-of-Stack (TOS) to Wdo                | 1             | 1                             | None                            |

|                    |                      | POP.D  | Wnd                                                            | Pop from Top-of-Stack (TOS) to<br>W(nd):W(nd + 1) | 1             | 2                             | None                            |

|                    |                      | POP.S  |                                                                | Pop Shadow Registers                              | 1             | 1                             | All                             |

| 56                 | PUSH                 | PUSH   | f                                                              | Push f to Top-of-Stack (TOS)                      | 1             | 1                             | None                            |

|                    |                      | PUSH   | Wso                                                            | Push Wso to Top-of-Stack (TOS)                    | 1             | 1                             | None                            |

|                    |                      | PUSH.D | Wns                                                            | Push W(ns):W(ns + 1) to Top-of-Stack<br>(TOS)     | 1             | 2                             | None                            |

|                    |                      | PUSH.S |                                                                | Push Shadow Registers                             | 1             | 1                             | None                            |

| 57                 | PWRSAV               | PWRSAV | #lit1                                                          | Go into Sleep or Idle mode                        | 1             | 1                             | WDTO,Sleep                      |

| 58                 | RCALL                | RCALL  | Expr                                                           | Relative Call                                     | 1             | 4                             | SFA                             |

|                    |                      | RCALL  | Wn                                                             | Computed Call                                     | 1             | 4                             | SFA                             |

| 59                 | REPEAT               | REPEAT | #lit15                                                         | Repeat Next Instruction lit15 + 1 times           | 1             | 1                             | None                            |

|                    |                      | REPEAT | Wn                                                             | Repeat Next Instruction (Wn) + 1 times            | 1             | 1                             | None                            |

| 60                 | RESET                | RESET  |                                                                | Software device Reset                             | 1             | 1                             | None                            |

| 61                 | RETFIE               | RETFIE |                                                                | Return from interrupt                             | 1             | 6 (5)                         | SFA                             |

| 62                 | RETLW                | RETLW  | #lit10,Wn                                                      | Return with literal in Wn                         | 1             | 6 (5)                         | SFA                             |

| 63                 | RETURN               | RETURN |                                                                | Return from Subroutine                            | 1             | 6 (5)                         | SFA                             |

| 64                 | RLC                  | RLC    | f                                                              | f = Rotate Left through Carry f                   | 1             | 1                             | C,N,Z                           |

|                    |                      | RLC    | f,WREG                                                         | WREG = Rotate Left through Carry f                | 1             | 1                             | C,N,Z                           |

|                    |                      | RLC    | Ws,Wd                                                          | Wd = Rotate Left through Carry Ws                 | 1             | 1                             | C,N,Z                           |

| 65                 | RLNC                 | RLNC   | f                                                              | f = Rotate Left (No Carry) f                      | 1             | 1                             | N,Z                             |

|                    |                      | RLNC   | f,WREG                                                         | WREG = Rotate Left (No Carry) f                   | 1             | 1                             | N,Z                             |

|                    |                      | RLNC   | Ws,Wd                                                          | Wd = Rotate Left (No Carry) Ws                    | 1             | 1                             | N,Z                             |

| 66                 | RRC                  | RRC    | f                                                              | f = Rotate Right through Carry f                  | 1             | 1                             | C,N,Z                           |

|                    |                      | RRC    | f,WREG                                                         | WREG = Rotate Right through Carry f               | 1             | 1                             | C,N,Z                           |

| 07                 |                      | RRC    | Ws,Wd                                                          | Wd = Rotate Right through Carry Ws                | 1             | 1                             | C,N,Z                           |

| 67                 | RRNC                 | RRNC   | f                                                              | f = Rotate Right (No Carry) f                     | 1             | 1                             | N,Z                             |

|                    |                      | RRNC   | f,WREG                                                         | WREG = Rotate Right (No Carry) f                  | 1             | 1                             | N,Z                             |

| <u></u>            | ~~~~                 | RRNC   | Ws,Wd                                                          | Wd = Rotate Right (No Carry) Ws                   | 1             | 1                             | N,Z                             |

| 68                 | SAC                  | SAC    | Acc,#Slit4,Wdo <sup>(1)</sup><br>Acc,#Slit4,Wdo <sup>(1)</sup> | Store Accumulator                                 | 1             | 1                             | None                            |

| 60                 | CE                   | SAC.R  |                                                                | Store Rounded Accumulator                         | 1             | 1                             | None                            |

| 69<br>70           | SE                   | SE     | Ws,Wnd                                                         | Wnd = sign-extended Ws<br>f = 0xFFFF              | 1             | 1                             | C,N,Z<br>None                   |

| 10                 | SETM                 | SETM   | f                                                              |                                                   | -             | 1                             |                                 |

|                    |                      | SETM   | WREG                                                           | WREG = 0xFFFF<br>Ws = 0xFFFF                      | 1             | 1                             | None                            |

| 71                 | SFTAC                | SETM   | Ws<br>Acc, Wn <sup>(1)</sup>                                   | Arithmetic Shift Accumulator by (Wn)              | 1             | 1                             | None<br>OA,OB,OAB,<br>SA,SB,SAB |

|                    |                      | SFTAC  | Acc,#Slit6 <sup>(1)</sup>                                      | Arithmetic Shift Accumulator by Slit6             | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB         |

## TABLE 28-2: INSTRUCTION SET OVERVIEW (CONTINUED)

Note 1: These instructions are available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

| DC CHARACTERISTICS |        |                                                                     | $ \begin{array}{ c c c c c } \hline Standard Operating Conditions (see Note 1): 3.0V to 3.6V \\ \hline (unless otherwise stated) \\ \hline Operating temperature & -40^\circ C \leq TA \leq +85^\circ C \text{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \text{ for Extended} \\ \hline \end{array} $ |       |            |      |                 |  |

|--------------------|--------|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------|------|-----------------|--|

| Param<br>No.       | Symbol | ymbol Characteristic Min. Typ. Max. Units                           |                                                                                                                                                                                                                                                                                                                        | Units | Conditions |      |                 |  |

| Operating Voltage  |        |                                                                     |                                                                                                                                                                                                                                                                                                                        |       |            |      |                 |  |

| DC10               | Vdd    | Supply Voltage                                                      | 3.0                                                                                                                                                                                                                                                                                                                    |       | 3.6        | V    |                 |  |

| DC16               | VPOR   | VDD Start Voltage<br>to Ensure Internal<br>Power-on Reset Signal    | -                                                                                                                                                                                                                                                                                                                      | _     | Vss        | V    |                 |  |

| DC17               | Svdd   | <b>VDD Rise Rate</b><br>to Ensure Internal<br>Power-on Reset Signal | 0.03                                                                                                                                                                                                                                                                                                                   | _     | —          | V/ms | 0V-1V in 100 ms |  |

## TABLE 30-4: DC TEMPERATURE AND VOLTAGE SPECIFICATIONS

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Device functionality is tested but not characterized. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

## TABLE 30-5: FILTER CAPACITOR (CEFC) SPECIFICATIONS

|                                                                                                                          | Standard Operating Conditions (unless otherwise stated):Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |  |  |  |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Param<br>No.                                                                                                             | Symbol Characteristics Min Typ Max Units Comments                                                                                                                                        |  |  |  |  |  |  |  |  |  |

| CEFC     External Filter Capacitor     4.7     10     —     μF     Capacitor must have a low series resistance (< 1 Ohm) |                                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |

**Note 1:** Typical VCAP voltage = 1.8 volts when VDD  $\geq$  VDDMIN.

| DC CHARACTI       | ERISTICS            |      | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |        |            |           |  |  |

|-------------------|---------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------|-----------|--|--|

| Parameter<br>No.  | Тур.                | Max. | Units                                                                                                                                                                                                                                                                                   |        | Conditions |           |  |  |

| Idle Current (III | dle) <sup>(1)</sup> |      |                                                                                                                                                                                                                                                                                         |        |            |           |  |  |

| DC40d             | 3                   | 8    | mA                                                                                                                                                                                                                                                                                      | -40°C  |            |           |  |  |

| DC40a             | 3                   | 8    | mA                                                                                                                                                                                                                                                                                      | +25°C  | - 3.3V     | 10 MIPS   |  |  |

| DC40b             | 3                   | 8    | mA                                                                                                                                                                                                                                                                                      | +85°C  | 3.3V       | 10 101195 |  |  |

| DC40c             | 3                   | 8    | mA                                                                                                                                                                                                                                                                                      | +125°C | ]          |           |  |  |

| DC42d             | 6                   | 12   | mA                                                                                                                                                                                                                                                                                      | -40°C  |            |           |  |  |

| DC42a             | 6                   | 12   | mA                                                                                                                                                                                                                                                                                      | +25°C  | - 3.3V     | 20 MIPS   |  |  |

| DC42b             | 6                   | 12   | mA                                                                                                                                                                                                                                                                                      | +85°C  |            | 20 1011-5 |  |  |

| DC42c             | 6                   | 12   | mA                                                                                                                                                                                                                                                                                      | +125°C |            |           |  |  |

| DC44d             | 11                  | 18   | mA                                                                                                                                                                                                                                                                                      | -40°C  |            |           |  |  |

| DC44a             | 11                  | 18   | mA                                                                                                                                                                                                                                                                                      | +25°C  | 3.3V       | 40 MIPS   |  |  |

| DC44b             | 11                  | 18   | mA                                                                                                                                                                                                                                                                                      | +85°C  | 5.50       | 40 1011-3 |  |  |

| DC44c             | 11                  | 18   | mA                                                                                                                                                                                                                                                                                      | +125°C |            |           |  |  |

| DC45d             | 17                  | 27   | mA                                                                                                                                                                                                                                                                                      | -40°C  |            |           |  |  |

| DC45a             | 17                  | 27   | mA                                                                                                                                                                                                                                                                                      | +25°C  | - 3.3V     | 60 MIPS   |  |  |

| DC45b             | 17                  | 27   | mA                                                                                                                                                                                                                                                                                      | +85°C  | 3.3V       |           |  |  |

| DC45c             | 17                  | 27   | mA                                                                                                                                                                                                                                                                                      | +125°C | ]          |           |  |  |

| DC46d             | 20                  | 35   | mA                                                                                                                                                                                                                                                                                      | -40°C  |            |           |  |  |

| DC46a             | 20                  | 35   | mA                                                                                                                                                                                                                                                                                      | +25°C  | 3.3V       | 70 MIPS   |  |  |

| DC46b             | 20                  | 35   | mA                                                                                                                                                                                                                                                                                      | +85°C  | ]          |           |  |  |

## TABLE 30-7: DC CHARACTERISTICS: IDLE CURRENT (lidle)

**Note 1:** Base Idle current (IIDLE) is measured as follows:

• CPU core is off, oscillator is configured in EC mode and external clock is active; OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)

- · CLKO is configured as an I/O input pin in the Configuration Word

- All I/O pins are configured as inputs and pulled to Vss

- $\overline{\text{MCLR}}$  = VDD, WDT and FSCM are disabled

- No peripheral modules are operating; however, every peripheral is being clocked (all PMDx bits are zeroed)

- The NVMSIDL bit (NVMCON<12>) = 1 (i.e., Flash regulator is set to standby while the device is in Idle mode)

- The VREGSF bit (RCON<11>) = 0 (i.e., Flash regulator is set to standby while the device is in Sleep mode)

- JTAG is disabled

# FIGURE 30-11: TIMERQ (QEI MODULE) EXTERNAL CLOCK TIMING CHARACTERISTICS (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

## TABLE 30-30: QEI MODULE EXTERNAL CLOCK TIMING REQUIREMENTS (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

| АС СНА       | ARACTERIST | rics                                                         | $\begin{array}{ll} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                                                |      |      |       |                                  |

|--------------|------------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|------|------|-------|----------------------------------|

| Param<br>No. | Symbol     | ol Characteristic <sup>(1)</sup>                             |                                                                                                                                                                                                                                                                                        | Min.                                           | Тур. | Max. | Units | Conditions                       |

| TQ10         | TtQH       | TQCK High<br>Time                                            | Synchronous, with prescaler                                                                                                                                                                                                                                                            | Greater of 12.5 + 25<br>or<br>(0.5 Tcy/N) + 25 |      |      | ns    | Must also meet<br>Parameter TQ15 |

| TQ11         | TtQL       | TQCK Low<br>Time                                             | Synchronous, with prescaler                                                                                                                                                                                                                                                            | Greater of 12.5 + 25<br>or<br>(0.5 Tcy/N) + 25 | —    | _    | ns    | Must also meet<br>Parameter TQ15 |

| TQ15         | TtQP       | TQCP Input<br>Period                                         | Synchronous, with prescaler                                                                                                                                                                                                                                                            | Greater of 25 + 50<br>or<br>(1 Tcy/N) + 50     | —    | _    | ns    |                                  |