Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 60 MIPs                                                                       |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                    |

| Number of I/O              | 35                                                                            |

| Program Memory Size        | 32KB (10.7K x 24)                                                             |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 2K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 9x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 48-UFQFN Exposed Pad                                                          |

| Supplier Device Package    | 48-UQFN (6x6)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep32gp204-e-mv |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

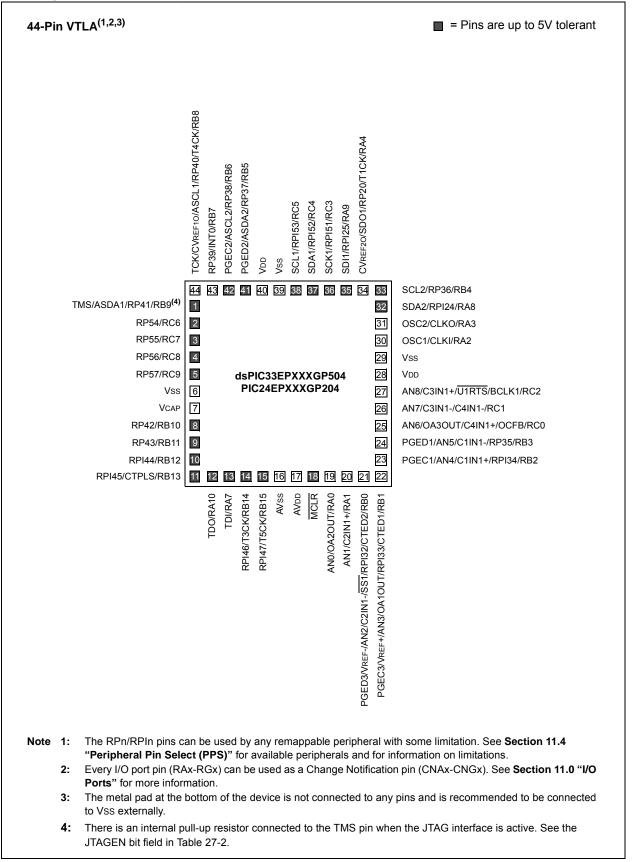

#### **Pin Diagrams (Continued)**

## 2.5 ICSP Pins

The PGECx and PGEDx pins are used for ICSP and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes, and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin Voltage Input High (VIH) and Voltage Input Low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> PICkit<sup>™</sup> 3, MPLAB ICD 3, or MPLAB REAL ICE<sup>™</sup>.

For more information on MPLAB ICD 2, ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site.

- "Using MPLAB<sup>®</sup> ICD 3" (poster) DS51765

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" DS51764

- "MPLAB<sup>®</sup> REAL ICE<sup>™</sup> In-Circuit Emulator User's Guide" DS51616

- "Using MPLAB<sup>®</sup> REAL ICE™ In-Circuit Emulator" (poster) DS51749

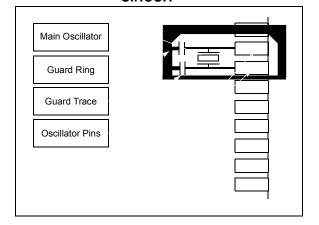

#### 2.6 External Oscillator Pins

Many DSCs have options for at least two oscillators: a high-frequency Primary Oscillator and a low-frequency Secondary Oscillator. For details, see **Section 9.0 "Oscillator Configuration"** for details.

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is shown in Figure 2-3.

#### SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

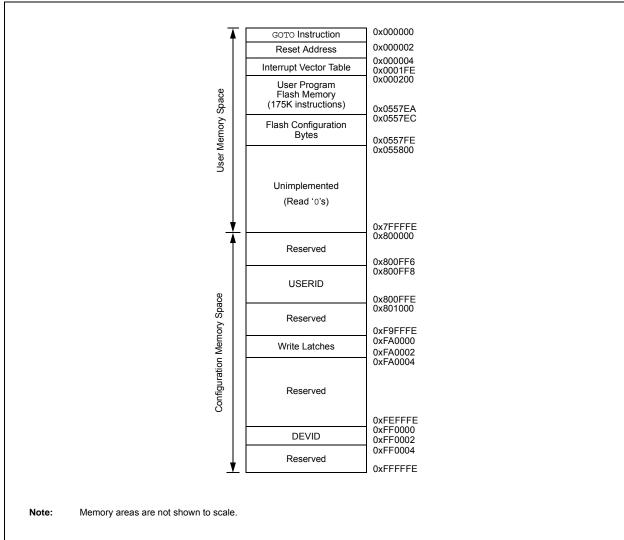

#### FIGURE 4-5: PROGRAM MEMORY MAP FOR dsPIC33EP512GP50X, dsPIC33EP512MC20X/50X AND PIC24EP512GP/MC20X DEVICES

#### **TABLE 4-3**: INTERRUPT CONTROLLER REGISTER MAP FOR PIC24EPXXXGP20X DEVICES ONLY

| TADLL        | τу.   | . INTERROFT CONTROLLER REGISTER MAPT OR FIC24EFXXXGF20X DEVICES ONET |        |            |        |        |        |            |        |       |                          |             |         |         |          |              |         |               |

|--------------|-------|----------------------------------------------------------------------|--------|------------|--------|--------|--------|------------|--------|-------|--------------------------|-------------|---------|---------|----------|--------------|---------|---------------|

| File<br>Name | Addr. | Bit 15                                                               | Bit 14 | Bit 13     | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8  | Bit 7 | Bit 6                    | Bit 5       | Bit 4   | Bit 3   | Bit 2    | Bit 1        | Bit 0   | All<br>Resets |

| IFS0         | 0800  |                                                                      | DMA1IF | AD1IF      | U1TXIF | U1RXIF | SPI1IF | SPI1EIF    | T3IF   | T2IF  | OC2IF                    | IC2IF       | DMA0IF  | T1IF    | OC1IF    | IC1IF        | INTOIF  | 0000          |

| IFS1         | 0802  | U2TXIF                                                               | U2RXIF | INT2IF     | T5IF   | T4IF   | OC4IF  | OC3IF      | DMA2IF | _     | _                        | —           | INT1IF  | CNIF    | CMIF     | MI2C1IF      | SI2C1IF | 0000          |

| IFS2         | 0804  |                                                                      | _      | _          | -      |        | _      | —          | _      | _     | IC4IF                    | IC3IF       | DMA3IF  | _       | —        | SPI2IF       | SPI2EIF | 0000          |

| IFS3         | 0806  | _                                                                    | _      | _          | _      | _      | _      | _          | _      | _     | _                        | _           | _       | _       | MI2C2IF  | SI2C2IF      | _       | 0000          |

| IFS4         | 0808  | _                                                                    | _      | CTMUIF     | _      | _      | _      | _          | _      | _     | _                        | _           | _       | CRCIF   | U2EIF    | U1EIF        | _       | 0000          |

| IFS8         | 0810  | JTAGIF                                                               | ICDIF  |            | _      | _      | _      | —          | —      | _     | _                        | _           | _       | _       | —        | —            | —       | 0000          |

| IFS9         | 0812  | _                                                                    | _      | _          | _      | _      | _      | —          | —      | _     | PTG3IF                   | PTG2IF      | PTG1IF  | PTG0IF  | PTGWDTIF | PTGSTEPIF    | _       | 0000          |

| IEC0         | 0820  | _                                                                    | DMA1IE | AD1IE      | U1TXIE | U1RXIE | SPI1IE | SPI1EIE    | T3IE   | T2IE  | OC2IE                    | IC2IE       | DMA0IE  | T1IE    | OC1IE    | IC1IE        | INT0IE  | 0000          |

| IEC1         | 0822  | U2TXIE                                                               | U2RXIE | INT2IE     | T5IE   | T4IE   | OC4IE  | OC3IE      | DMA2IE | _     | _                        | _           | INT1IE  | CNIE    | CMIE     | MI2C1IE      | SI2C1IE | 0000          |

| IEC2         | 0824  | _                                                                    | _      | _          | _      | _      | _      | _          | _      | _     | IC4IE                    | IC3IE       | DMA3IE  | _       | _        | SPI2IE       | SPI2EIE | 0000          |

| IEC3         | 0826  | _                                                                    | _      | _          | _      | _      | _      | —          | —      | _     | _                        | _           | _       | _       | MI2C2IE  | SI2C2IE      | —       | 0000          |

| IEC4         | 0828  | _                                                                    | _      | CTMUIE     | _      | _      | _      | _          | _      | _     | _                        | _           | _       | CRCIE   | U2EIE    | U1EIE        | _       | 0000          |

| IEC8         | 0830  | JTAGIE                                                               | ICDIE  | _          | _      | _      | _      | _          | _      | _     | _                        | _           | _       | _       | _        | _            | _       | 0000          |

| IEC9         | 0832  | _                                                                    | _      | _          | _      | _      | _      | —          | —      | _     | PTG3IE                   | PTG2IE      | PTG1IE  | PTG0IE  | PTGWDTIE | PTGSTEPIE    | _       | 0000          |

| IPC0         | 0840  | _                                                                    |        | T1IP<2:0>  |        | _      | (      | OC1IP<2:0  | >      | _     | - IC1IP<2:0> INT0IP<2:0> |             |         | 4444    |          |              |         |               |

| IPC1         | 0842  | _                                                                    |        | T2IP<2:0>  |        | _      | (      | OC2IP<2:0  | >      | _     |                          | IC2IP<2:0>  |         | _       | C        | 0MA0IP<2:0>  |         | 4444          |

| IPC2         | 0844  | _                                                                    | U      | J1RXIP<2:0 | >      | _      | ;      | SPI1IP<2:0 | >      | _     |                          | SPI1EIP<2:0 | >       | _       |          | T3IP<2:0>    |         | 4444          |

| IPC3         | 0846  | _                                                                    | _      | _          | _      | _      | D      | )MA1IP<2:  | 0>     | _     |                          | AD1IP<2:0>  |         | _       | ι        | J1TXIP<2:0>  |         | 0444          |

| IPC4         | 0848  |                                                                      |        | CNIP<2:0>  |        |        |        | CMIP<2:0   | >      | _     |                          | MI2C1IP<2:0 | >       | _       | S        | SI2C1IP<2:0> |         | 4444          |

| IPC5         | 084A  | _                                                                    | _      | _          | _      | _      | _      | _          | _      | _     | _                        | —           | _       | _       | I        | INT1IP<2:0>  |         | 0004          |

| IPC6         | 084C  | _                                                                    |        | T4IP<2:0>  |        | _      | (      | OC4IP<2:0  | >      | _     |                          | OC3IP<2:0>  |         | _       | C        | )ma2IP<2:0>  |         | 4444          |

| IPC7         | 084E  |                                                                      | l      | U2TXIP<2:0 | >      |        | L      | J2RXIP<2:  | )>     | _     |                          | INT2IP<2:0> |         | _       |          | T5IP<2:0>    |         | 4444          |

| IPC8         | 0850  |                                                                      | _      | _          | _      |        | _      | —          | —      | _     |                          | SPI2IP<2:0> |         | _       | S        | SPI2EIP<2:0> |         | 0044          |

| IPC9         | 0852  |                                                                      | _      | _          | _      |        |        | IC4IP<2:0  | >      | _     |                          | IC3IP<2:0>  |         | _       | C        | 0MA3IP<2:0>  |         | 0444          |

| IPC12        | 0858  |                                                                      | _      | _          |        |        | N      | 112C2IP<2: | 0>     | _     |                          | SI2C2IP<2:0 | >       | _       | _        | _            | _       | 0440          |

| IPC16        | 0860  |                                                                      |        | CRCIP<2:0> | >      |        |        | U2EIP<2:0  | >      | _     |                          | U1EIP<2:0>  |         | _       | _        | _            | _       | 4440          |

| IPC19        | 0866  |                                                                      | _      | _          | _      | _      | _      | _          | _      | _     |                          | CTMUIP<2:0  | >       | _       | _        | _            | _       | 0040          |

| IPC35        | 0886  |                                                                      |        | JTAGIP<2:0 | >      | _      |        | ICDIP<2:0  | >      | _     | _                        | _           | _       | _       | _        | _            | _       | 4400          |

| IPC36        | 0888  | _                                                                    |        | PTG0IP<2:0 | >      | _      | PT     | GWDTIP<    | 2:0>   | _     | P                        | TGSTEPIP<2  | :0>     | _       | _        | —            | _       | 4440          |

| IPC37        | 088A  | _                                                                    | _      | _          | _      | _      | F      | PTG3IP<2:  | )>     | _     |                          | PTG2IP<2:0  | >       | _       | F        | PTG1IP<2:0>  |         | 0444          |

| INTCON1      | 08C0  | NSTDIS                                                               | OVAERR | OVBERR     | _      |        |        |            | —      | _     | DIV0ERR                  | DMACERR     | MATHERR | ADDRERR | STKERR   | OSCFAIL      |         | 0000          |

| INTCON2      | 08C2  | GIE                                                                  | DISI   | SWTRAP     | _      |        |        |            | _      | _     |                          | —           | —       | _       | INT2EP   | INT1EP       | INT0EP  | 8000          |

| INTCON3      | 08C4  | _                                                                    | _      |            | _      |        |        | _          | _      | _     | _                        | DAE         | DOOVR   | _       | _        | —            |         | 0000          |

| INTCON4      | 08C6  |                                                                      | _      | _          | _      | _      | _      | —          | _      | SGHT  |                          |             | SGHT    | 0000    |          |              |         |               |

| INTTREG      | 08C8  | _                                                                    |        |            | _      |        | ILR<   | 3:0>       |        |       |                          |             | VECN    | UM<7:0> |          |              |         | 0000          |

|              |       |                                                                      |        |            |        |        |        |            |        |       |                          |             |         |         |          |              |         |               |

- = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

| File Name  | Addr          | Bit 15 | Bit 14    | Bit 13 | Bit 12                                | Bit 11 | Bit 10 | Bit 9    | Bit 8      | Bit 7      | Bit 6    | Bit 5    | Bit 4    | Bit 3               | Bit 2 | Bit 1 | Bit 0  | All<br>Resets |

|------------|---------------|--------|-----------|--------|---------------------------------------|--------|--------|----------|------------|------------|----------|----------|----------|---------------------|-------|-------|--------|---------------|

|            | 0400-<br>041E |        |           |        |                                       |        |        |          | See defini | ion when W | 'IN = x  |          |          |                     |       |       |        |               |

| C1BUFPNT1  | 0420          |        | F3BF      | P<3:0> |                                       |        | F2BI   | ><3:0>   |            |            | F1BP     | <3:0>    |          |                     | F0BP  | <3:0> |        | 0000          |

| C1BUFPNT2  | 0422          |        | F7BF      | ><3:0> |                                       |        | F6BI   | ><3:0>   |            |            | F5BP     | <3:0>    |          | F4BP<3:0>           |       |       |        | 0000          |

| C1BUFPNT3  | 0424          |        | F11B      | P<3:0> |                                       |        | F10B   | P<3:0>   |            |            | F9BP     | <3:0>    |          | F8BP<3:0>           |       |       | 0000   |               |

| C1BUFPNT4  | 0426          |        | F15B      | P<3:0> |                                       |        | F14B   | P<3:0>   |            |            | F13B     | D<3:0>   |          | F12BP<3:0>          |       |       | 0000   |               |

| C1RXM0SID  | 0430          |        |           |        | SID<                                  | :10:3> |        |          |            |            | SID<2:0> |          | _        | MIDE                | _     | EID<  | 17:16> | xxxx          |

| C1RXM0EID  | 0432          |        |           |        | EID<                                  | :15:8> |        |          |            |            |          |          | EID<     | :7:0>               |       |       | xxxx   |               |

| C1RXM1SID  | 0434          |        |           |        | SID<                                  | :10:3> |        |          |            |            | SID<2:0> |          | _        | - MIDE - EID<17:16> |       |       |        | xxxx          |

| C1RXM1EID  | 0436          |        |           |        | EID<                                  | :15:8> |        |          |            |            |          |          | EID<7:0> |                     |       |       |        | xxxx          |

| C1RXM2SID  | 0438          |        |           |        | SID<                                  | :10:3> |        |          |            |            | SID<2:0> |          | —        | MIDE                | —     | EID<  | 17:16> | xxxx          |

| C1RXM2EID  | 043A          |        |           |        | EID<                                  | :15:8> |        |          |            |            |          | EID<7:0> |          |                     |       |       | xxxx   |               |

| C1RXF0SID  | 0440          |        |           |        | SID<                                  | :10:3> |        |          |            |            | SID<2:0> |          | —        | EXIDE               | —     | EID<  | 17:16> | xxxx          |

| C1RXF0EID  | 0442          |        | EID<      |        |                                       | :15:8> |        |          |            |            | EID<7:0> |          |          |                     |       | xxxx  |        |               |

| C1RXF1SID  | 0444          |        |           |        | SID<10:3> SID<2:0> — EXIDE — EID<17:1 |        |        |          |            |            | 17:16>   | xxxx     |          |                     |       |       |        |               |

| C1RXF1EID  | 0446          |        | EID<15:8> |        |                                       |        |        |          |            |            |          |          | EID<     | 7:0>                |       |       |        | xxxx          |

| C1RXF2SID  | 0448          |        |           |        | SID<                                  | :10:3> |        |          |            |            | SID<2:0> |          | —        | EXIDE               | —     | EID<  | 17:16> | xxxx          |

| C1RXF2EID  | 044A          |        |           |        | EID<                                  | :15:8> |        |          |            |            |          |          | EID<     | 7:0>                |       |       |        | xxxx          |

| C1RXF3SID  | 044C          |        |           |        | SID<                                  | :10:3> |        |          |            |            | SID<2:0> |          | —        | EXIDE               | —     | EID<  | 17:16> | xxxx          |

| C1RXF3EID  | 044E          |        |           |        | EID<                                  | :15:8> |        |          |            | EID<7:0>   |          |          |          |                     |       |       | xxxx   |               |

| C1RXF4SID  | 0450          |        |           |        | SID<                                  | :10:3> |        |          |            |            | SID<2:0> |          | —        | EXIDE — EID<17:16>  |       |       | 17:16> | xxxx          |

| C1RXF4EID  | 0452          |        |           |        | EID<                                  | :15:8> |        |          |            |            |          |          | EID<     | 7:0>                |       |       |        | xxxx          |

| C1RXF5SID  | 0454          |        |           |        | SID<                                  | :10:3> |        |          |            |            | SID<2:0> |          | —        | EXIDE               | —     | EID<  | 17:16> | xxxx          |

| C1RXF5EID  | 0456          |        |           |        | EID<                                  | :15:8> |        |          |            |            |          |          | EID<     | 7:0>                |       |       |        | xxxx          |

| C1RXF6SID  | 0458          |        |           |        | SID<                                  | :10:3> |        |          |            |            | SID<2:0> |          | —        | EXIDE               | —     | EID<  | 17:16> | xxxx          |

| C1RXF6EID  | 045A          |        |           |        | EID<                                  | :15:8> |        |          |            |            |          |          | EID<     | 7:0>                |       |       |        | xxxx          |

| C1RXF7SID  | 045C          |        |           |        | SID<                                  | :10:3> |        |          |            |            | SID<2:0> |          | —        | EXIDE               | —     | EID<  | 17:16> | xxxx          |

| C1RXF7EID  | 045E          |        |           |        | EID<                                  | :15:8> |        |          |            |            |          |          | EID<     | 7:0>                |       |       |        | xxxx          |

| C1RXF8SID  | 0460          |        |           |        | SID<                                  | :10:3> |        |          |            |            | SID<2:0> |          | —        | EXIDE               | —     | EID<  | 17:16> | xxxx          |

| C1RXF8EID  | 0462          |        | EID<15:8> |        |                                       |        |        | EID<7:0> |            |            |          |          |          | xxxx                |       |       |        |               |

| C1RXF9SID  | 0464          |        |           |        |                                       | :10:3> |        |          |            |            | SID<2:0> |          | —        | EXIDE               | —     | EID<  | 17:16> | xxxx          |

| C1RXF9EID  | 0466          |        |           |        |                                       | :15:8> |        |          |            |            |          | xxxx     |          |                     |       |       |        |               |

| C1RXF10SID | 0468          |        |           |        |                                       | :10:3> |        |          |            |            | SID<2:0> |          | —        | EXIDE               | —     | EID<  | 17:16> | xxxx          |

| C1RXF10EID | 046A          |        |           |        |                                       | :15:8> |        |          |            | EID<7:0>   |          |          |          |                     |       |       | xxxx   |               |

| C1RXF11SID | 046C          |        |           |        | SID<                                  | :10:3> |        |          |            |            | SID<2:0> |          | —        | EXIDE               | -     | EID<  | 17:16> | xxxx          |

#### TABLE 4-23: ECAN1 REGISTER MAP WHEN WIN (C1CTRL1<0>) = 1 FOR dsPIC33EPXXXMC/GP50X DEVICES ONLY

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| <b>TABLE 4-33</b> : | PERIPHERAL PIN SELECT INPUT REGISTER MAP FOR dsPIC33EPXXXMC20X DEVICES ONLY |

|---------------------|-----------------------------------------------------------------------------|

|---------------------|-----------------------------------------------------------------------------|

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12                  | Bit 11     | Bit 10 | Bit 9 | Bit 8 | Bit 7      | Bit 6      | Bit 5 | Bit 4 | Bit 3      | Bit 2     | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|-------------------------|------------|--------|-------|-------|------------|------------|-------|-------|------------|-----------|-------|-------|---------------|

| RPINR0       | 06A0  | _      |        |        |                         | NT1R<6:0>  |        |       |       |            | _          | _     | _     | _          |           | _     | _     | 0000          |

| RPINR1       | 06A2  |        | —      | —      | -                       |            | -      |       |       | -          | INT2R<6:0> |       |       |            |           | 0000  |       |               |

| RPINR3       | 06A6  |        | _      | _      | _                       | _          | _      | _     | _     | _          | T2CKR<6:0> |       |       |            | 0000      |       |       |               |

| RPINR7       | 06AE  | _      |        |        |                         | IC2R<6:0>  |        |       |       | —          | IC1R<6:0>  |       |       |            | 0000      |       |       |               |

| RPINR8       | 06B0  | _      |        |        |                         | IC4R<6:0>  |        |       |       | —          | IC3R<6:0>  |       |       |            | IC3R<6:0> |       |       | 0000          |

| RPINR11      | 06B6  | _      | _      | _      | —                       | _          | _      | _     | _     | —          | OCFAR<6:0> |       |       |            | 0000      |       |       |               |

| RPINR12      | 06B8  | _      |        |        | FLT2R<6:0> — FLT1R<6:0> |            |        |       |       | FLT1R<6:0> |            |       |       |            | 0000      |       |       |               |

| RPINR14      | 06BC  | _      |        |        | (                       | QEB1R<6:0  | >      |       |       | —          |            |       | (     | QEA1R<6:0> | >         |       |       | 0000          |

| RPINR15      | 06BE  | _      |        |        | Н                       | OME1R<6:0  | )>     |       |       | —          |            |       | I     | NDX1R<6:0  | >         |       |       | 0000          |

| RPINR18      | 06C4  | _      | _      | _      | —                       | _          | _      | _     | _     | —          |            |       | ι     | J1RXR<6:0> | >         |       |       | 0000          |

| RPINR19      | 06C6  | _      | _      | _      | _                       | _          | _      | _     | _     | —          |            |       | ι     | J2RXR<6:0> | >         |       |       | 0000          |

| RPINR22      | 06CC  | _      |        | •      | S                       | CK2INR<6:0 | )>     |       |       | _          |            |       |       | SDI2R<6:0> | •         |       |       | 0000          |

| RPINR23      | 06CE  | _      | _      |        | _                       | _          | _      | _     | _     | _          | SS2R<6:0>  |       |       |            | 0000      |       |       |               |

| RPINR37      | 06EA  | _      |        |        | S                       | YNCI1R<6:0 | )>     |       |       | _          |            |       |       |            | 0000      |       |       |               |

| RPINR38      | 06EC  | _      |        |        | DT                      | CMP1R<6:   | 0>     |       |       | _          |            |       |       |            |           | 0000  |       |               |

| RPINR39      | 06EE  | _      |        |        | DT                      | CMP3R<6:   | 0>     |       |       | —          |            |       | D     | CMP2R<6:   | 0>        |       |       | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### 4.4.1 PAGED MEMORY SCHEME

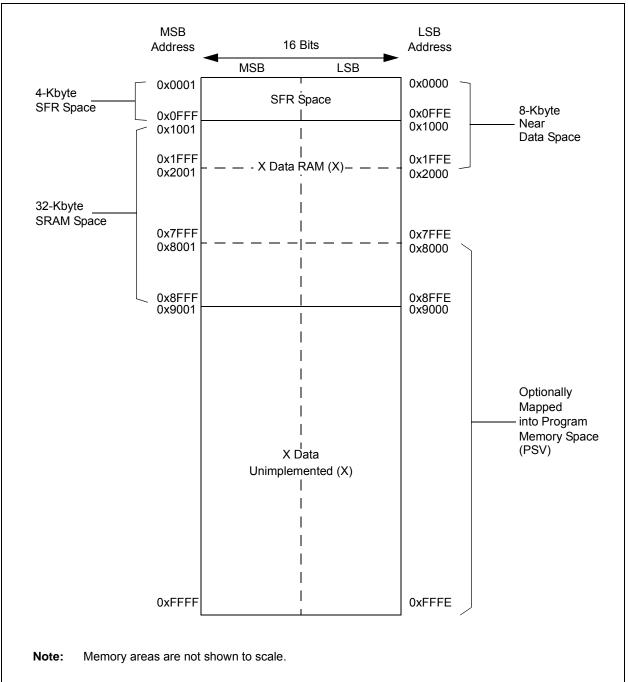

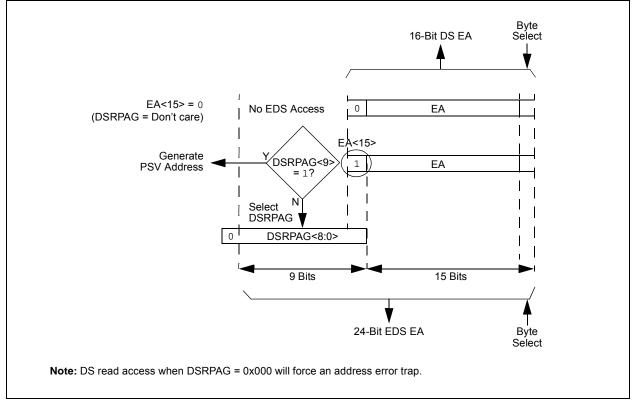

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X architecture extends the available Data Space through a paging scheme, which allows the available Data Space to be accessed using MOV instructions in a linear fashion for pre-modified and post-modified Effective Addresses (EA). The upper half of the base Data Space address is used in conjunction with the Data Space Page registers, the 10-bit Read Page register (DSRPAG) or the 9-bit Write Page register (DSWPAG), to form an Extended Data Space (EDS) address or Program Space Visibility (PSV) address. The Data Space Page registers are located in the SFR space.

Construction of the EDS address is shown in Example 4-1. When DSRPAG<9> = 0 and the base address bit, EA<15> = 1, the DSRPAG<8:0> bits are concatenated onto EA<14:0> to form the 24-bit EDS read address. Similarly, when base address bit, EA<15> = 1, DSWPAG<8:0> are concatenated onto EA<14:0> to form the 24-bit EDS write address.

Allocating different Page registers for read and write access allows the architecture to support data movement between different pages in data memory. This is accomplished by setting the DSRPAG register value to the page from which you want to read, and configuring the DSWPAG register to the page to which it needs to be written. Data can also be moved from different PSV to EDS pages, by configuring the DSRPAG and DSWPAG registers to address PSV and EDS space, respectively. The data can be moved between pages by a single instruction.

When an EDS or PSV page overflow or underflow occurs, EA<15> is cleared as a result of the register indirect EA calculation. An overflow or underflow of the EA in the EDS or PSV pages can occur at the page boundaries when:

- The initial address prior to modification addresses an EDS or PSV page

- The EA calculation uses Pre-Modified or Post-Modified Register Indirect Addressing; however, this does not include Register Offset Addressing

In general, when an overflow is detected, the DSxPAG register is incremented and the EA<15> bit is set to keep the base address within the EDS or PSV window. When an underflow is detected, the DSxPAG register is decremented and the EA<15> bit is set to keep the base address within the EDS or PSV window. This creates a linear EDS and PSV address space, but only when using Register Indirect Addressing modes.

Exceptions to the operation described above arise when entering and exiting the boundaries of Page 0, EDS and PSV spaces. Table 4-61 lists the effects of overflow and underflow scenarios at different boundaries.

In the following cases, when overflow or underflow occurs, the EA<15> bit is set and the DSxPAG is not modified; therefore, the EA will wrap to the beginning of the current page:

- · Register Indirect with Register Offset Addressing

- Modulo Addressing

- · Bit-Reversed Addressing

| 0/11        |                     |                | Before       |                        |                | After        |                        |  |  |  |  |  |  |

|-------------|---------------------|----------------|--------------|------------------------|----------------|--------------|------------------------|--|--|--|--|--|--|

| O/U,<br>R/W | Operation           | DSxPAG         | DS<br>EA<15> | Page<br>Description    | DSxPAG         | DS<br>EA<15> | Page<br>Description    |  |  |  |  |  |  |

| O,<br>Read  |                     | DSRPAG = 0x1FF | 1            | EDS: Last page         | DSRPAG = 0x1FF | 0            | See Note 1             |  |  |  |  |  |  |

| O,<br>Read  | [++Wn]              | DSRPAG = 0x2FF | 1            | PSV: Last lsw<br>page  | DSRPAG = 0x300 | 1            | PSV: First MSB<br>page |  |  |  |  |  |  |

| O,<br>Read  | <b>Or</b><br>[Wn++] | DSRPAG = 0x3FF | 1            | PSV: Last MSB<br>page  | DSRPAG = 0x3FF | 0            | See Note 1             |  |  |  |  |  |  |

| O,<br>Write |                     | DSWPAG = 0x1FF | 1            | EDS: Last page         | DSWPAG = 0x1FF | 0            | See Note 1             |  |  |  |  |  |  |

| U,<br>Read  |                     | DSRPAG = 0x001 | 1            | PSV page               | DSRPAG = 0x001 | 0            | See Note 1             |  |  |  |  |  |  |

| U,<br>Read  | [Wn]<br>Or<br>[Wn]  | DSRPAG = 0x200 | 1            | PSV: First Isw<br>page | DSRPAG = 0x200 | 0            | See Note 1             |  |  |  |  |  |  |

| U,<br>Read  | [ //11 - ]          | DSRPAG = 0x300 | 1            | PSV: First MSB<br>page | DSRPAG = 0x2FF | 1            | PSV: Last Isw<br>page  |  |  |  |  |  |  |

## TABLE 4-61: OVERFLOW AND UNDERFLOW SCENARIOS AT PAGE 0, EDS and PSV SPACE BOUNDARIES<sup>(2,3,4)</sup>

Legend: O = Overflow, U = Underflow, R = Read, W = Write

Note 1: The Register Indirect Addressing now addresses a location in the base Data Space (0x0000-0x8000).

2: An EDS access with DSxPAG = 0x000 will generate an address error trap.

- **3:** Only reads from PS are supported using DSRPAG. An attempt to write to PS using DSWPAG will generate an address error trap.

- 4: Pseudo-Linear Addressing is not supported for large offsets.

| U-0          | U-0                         | U-0                                          | U-0            | U-0              | U-0             | U-0    | U-0   |

|--------------|-----------------------------|----------------------------------------------|----------------|------------------|-----------------|--------|-------|

| -            | —                           | —                                            | —              | —                | —               | —      | —     |

| bit 15       |                             |                                              |                |                  |                 |        | bit 8 |

| U-0          | U-0                         | U-0                                          | U-0            | R-1              | R-1             | R-1    | R-1   |

| _            | _                           | _                                            | _              |                  | LSTC            | H<3:0> |       |

| bit 7        |                             |                                              |                |                  |                 |        | bit 0 |

| Legend:      |                             |                                              |                |                  |                 |        |       |

| R = Readat   | ole bit                     | W = Writable                                 | bit            | U = Unimpler     |                 |        |       |

| -n = Value a | at POR                      | '1' = Bit is set                             |                | '0' = Bit is cle | x = Bit is unkr | nown   |       |

|              |                             |                                              |                |                  |                 |        |       |

| bit 15-4     | Unimplemen                  | ted: Read as '                               | 0'             |                  |                 |        |       |

| bit 3-0      | LSTCH<3:0>                  | : Last DMAC C                                | hannel Active  | e Status bits    |                 |        |       |

|              | 1111 = No DI<br>1110 = Rese | MA transfer has<br>rved                      | s occurred sir | nce system Res   | set             |        |       |

|              | •                           |                                              |                |                  |                 |        |       |

|              | •                           |                                              |                |                  |                 |        |       |

|              | •                           |                                              |                |                  |                 |        |       |

|              |                             | rved<br>data transfer wa<br>data transfer wa |                |                  |                 |        |       |

|              |                             | data transfer wa                             |                |                  |                 |        |       |

## REGISTER 8-13: DMALCA: DMA LAST CHANNEL ACTIVE STATUS REGISTER

0001 = Last data transfer was handled by Channel 0 0000 = Last data transfer was handled by Channel 0

## 9.1 CPU Clocking System

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X family of devices provides six system clock options:

- Fast RC (FRC) Oscillator

- FRC Oscillator with Phase Locked Loop (PLL)

- · FRC Oscillator with Postscaler

- Primary (XT, HS or EC) Oscillator

- Primary Oscillator with PLL

- · Low-Power RC (LPRC) Oscillator

Instruction execution speed or device operating frequency, FCY, is given by Equation 9-1.

# EQUATION 9-1: DEVICE OPERATING FREQUENCY

FCY = Fosc/2

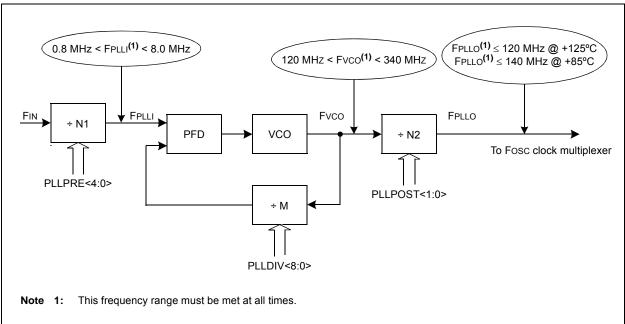

Figure 9-2 is a block diagram of the PLL module.

Equation 9-2 provides the relationship between input frequency (FIN) and output frequency (FPLLO). In clock modes S1 and S3, when the PLL output is selected, FOSC = FPLLO.

Equation 9-3 provides the relationship between input frequency (FIN) and VCO frequency (FVCO).

#### EQUATION 9-2: FPLLO CALCULATION

$$FPLLO = FIN \times \left(\frac{M}{N1 \times N2}\right) = FIN \times \left(\frac{(PLLDIV + 2)}{(PLLPRE + 2) \times 2(PLLPOST + 1)}\right)$$

Where:

N1 = PLLPRE + 2 $N2 = 2 \times (PLLPOST + 1)$

M = PLLDIV + 2

### EQUATION 9-3: Fvco CALCULATION

$$Fvco = FIN \times \left(\frac{M}{N1}\right) = FIN \times \left(\frac{(PLLDIV + 2)}{(PLLPRE + 2)}\right)$$

DS70000657H-page 154

#### © 2011-2013 Microchip Technology Inc.

## FIGURE 9-2: PLL BLOCK DIAGRAM

### REGISTER 11-16: RPINR38: PERIPHERAL PIN SELECT INPUT REGISTER 38 (dsPIC33EPXXXMC20X AND PIC24EPXXXMC20X DEVICES ONLY)

|              | -         |                                      |       |                  |                   | -               |                |

|--------------|-----------|--------------------------------------|-------|------------------|-------------------|-----------------|----------------|

| U-0          | R/W-0     | R/W-0                                | R/W-0 | R/W-0            | R/W-0             | R/W-0           | R/W-0          |

|              |           |                                      |       | DTCMP1R<6:       | 0>                |                 |                |

| bit 15       |           |                                      |       |                  |                   |                 | bit 8          |

|              |           |                                      |       |                  |                   |                 |                |

| U-0          | U-0       | U-0                                  | U-0   | U-0              | U-0               | U-0             | U-0            |

| —            | —         | —                                    | _     |                  | _                 | —               | —              |

| bit 7        |           |                                      |       |                  |                   |                 | bit C          |

|              |           |                                      |       |                  |                   |                 |                |

| Legend:      |           |                                      |       |                  |                   |                 |                |

| R = Readal   | ole bit   | W = Writable                         | bit   | U = Unimpler     | mented bit, read  | d as '0'        |                |

| -n = Value a | at POR    | '1' = Bit is set                     | :     | '0' = Bit is cle | ared              | x = Bit is unkr | nown           |

|              |           |                                      |       |                  |                   |                 |                |

| bit 15       | Unimpleme | nted: Read as '                      | 0'    |                  |                   |                 |                |

| bit 14-8     |           | 6:0>: Assign PV<br>1-2 for input pin |       | •                | on Input 1 to the | e Corresponding | g RPn Pin bits |

|              | 1111001 = | Input tied to RP                     | 1121  |                  |                   |                 |                |

|              | •         |                                      |       |                  |                   |                 |                |

|              | •         |                                      |       |                  |                   |                 |                |

|              |           | Input tied to CM                     | P1    |                  |                   |                 |                |

|              |           | Input tied to Vss                    |       |                  |                   |                 |                |

| bit 7-0      |           | nted: Read as '                      |       |                  |                   |                 |                |

|              |           |                                      | -     |                  |                   |                 |                |

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-0      | R/W-0                                                                    | R/W-0                                                | R/W-0                           | U-0               | U-0              | U-0                    | R/W-0        |

|------------|--------------------------------------------------------------------------|------------------------------------------------------|---------------------------------|-------------------|------------------|------------------------|--------------|

| FLTMD      | FLTOUT                                                                   | FLTTRIEN                                             | OCINV                           | —                 | _                | —                      | OC32         |

| bit 15     | ·                                                                        |                                                      |                                 |                   | ·                |                        | bit          |

|            |                                                                          |                                                      |                                 |                   |                  |                        |              |

| R/W-0      | R/W-0, HS                                                                | R/W-0                                                | R/W-0                           | R/W-1             | R/W-1            | R/W-0                  | R/W-0        |

| OCTRIG     | G TRIGSTAT                                                               | OCTRIS                                               | SYNCSEL4                        | SYNCSEL3          | SYNCSEL2         | SYNCSEL1               | SYNCSEL      |

| bit 7      |                                                                          |                                                      |                                 |                   |                  |                        | bit          |

| Legend:    |                                                                          | HS = Hardwa                                          | re Settable bit                 |                   |                  |                        |              |

| R = Reada  | able bit                                                                 | W = Writable                                         | bit                             | U = Unimplem      | nented bit, read | l as '0'               |              |

| -n = Value | at POR                                                                   | '1' = Bit is set                                     |                                 | '0' = Bit is clea | ared             | x = Bit is unkn        | iown         |

|            |                                                                          |                                                      |                                 |                   |                  |                        |              |

| bit 15     | 1 = Fault mo<br>cleared i                                                | t Mode Select b<br>ode is maintain<br>n software and | ed until the Fa<br>a new PWM pe | eriod starts      |                  |                        |              |

|            |                                                                          | de is maintaine                                      | d until the Faul                | t source is rem   | loved and a ne   | w PWM period           | starts       |

| bit 14     | FLTOUT: Fau                                                              |                                                      | . –                             |                   |                  |                        |              |

|            |                                                                          | tput is driven hi<br>tput is driven lo               |                                 |                   |                  |                        |              |

| bit 13     |                                                                          | ault Output Sta                                      |                                 |                   |                  |                        |              |

|            |                                                                          | is tri-stated on                                     |                                 | 'n                |                  |                        |              |

|            | •                                                                        | I/O state is defi                                    |                                 |                   | ault condition   |                        |              |

| bit 12     | OCINV: Outp                                                              | ut Compare x I                                       | nvert bit                       |                   |                  |                        |              |

|            |                                                                          | out is inverted<br>out is not invert                 | ed                              |                   |                  |                        |              |

| bit 11-9   | Unimplemen                                                               | ted: Read as '                                       | כי                              |                   |                  |                        |              |

| bit 8      | OC32: Casca                                                              | ide Two OCx M                                        | odules Enable                   | bit (32-bit oper  | ration)          |                        |              |

|            |                                                                          | module operate module operate                        |                                 |                   |                  |                        |              |

| bit 7      |                                                                          | tput Compare x                                       |                                 | Select bit        |                  |                        |              |

|            |                                                                          | OCx from the s                                       |                                 |                   | CSELx bits       |                        |              |

|            |                                                                          | nizes OCx with                                       |                                 |                   |                  | S                      |              |

| bit 6      | TRIGSTAT: T                                                              | imer Trigger St                                      | atus bit                        |                   |                  |                        |              |

|            |                                                                          | urce has been <sup>.</sup><br>urce has not be        |                                 |                   | d clear          |                        |              |

| bit 5      |                                                                          | put Compare x                                        |                                 | •                 |                  |                        |              |

|            | 1 = OCx is tr                                                            | • •                                                  | ·                               |                   |                  |                        |              |

|            | 0 = Output C                                                             | ompare x mod                                         | ule drives the C                | OCx pin           |                  |                        |              |

| Note 1:    | Do not use the O                                                         | Cx module as i                                       | ts own Svnchro                  | nization or Tric  | aaer source.     |                        |              |

|            | When the OCy m                                                           |                                                      | -                               |                   |                  | module uses t          | he OCv       |

|            | module as a Trigg                                                        |                                                      |                                 |                   |                  |                        |              |

| 3:         | Each Output Con<br><b>"Peripheral Trig</b><br>PTGO0 = OC1<br>PTGO1 = OC2 |                                                      |                                 |                   |                  | n source. See <b>S</b> | Section 24.0 |

|            | PTGO2 = OC3 $PTGO3 = OC4$                                                |                                                      |                                 |                   |                  |                        |              |

## REGISTER 15-2: OCxCON2: OUTPUT COMPARE x CONTROL REGISTER 2

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0                                                                       | U-0   | R/W-0          | R/W-0 | R/W-0        | R/W-0           | R/W-0    | R/W-0 |  |  |

|---------------------------------------------------------------------------|-------|----------------|-------|--------------|-----------------|----------|-------|--|--|

| —                                                                         | —     |                |       | DTR)         | <13:8>          |          |       |  |  |

| bit 15                                                                    |       |                |       |              |                 |          | bit 8 |  |  |

|                                                                           |       |                |       |              |                 |          |       |  |  |

| R/W-0                                                                     | R/W-0 | R/W-0          | R/W-0 | R/W-0        | R/W-0           | R/W-0    | R/W-0 |  |  |

|                                                                           |       |                | DTR   | x<7:0>       |                 |          |       |  |  |

| bit 7                                                                     |       |                |       |              |                 |          | bit 0 |  |  |

|                                                                           |       |                |       |              |                 |          |       |  |  |

| Legend:                                                                   |       |                |       |              |                 |          |       |  |  |

| R = Readable                                                              | bit   | W = Writable b | bit   | U = Unimpler | nented bit, rea | d as '0' |       |  |  |

| -n = Value at POR (1' = Bit is set 0' = Bit is cleared x = Bit is unknown |       |                |       |              |                 |          |       |  |  |

## REGISTER 16-10: DTRx: PWMx DEAD-TIME REGISTER

bit 15-14 Unimplemented: Read as '0'

bit 13-0 DTRx<13:0>: Unsigned 14-Bit Dead-Time Value for PWMx Dead-Time Unit bits

#### REGISTER 16-11: ALTDTRx: PWMx ALTERNATE DEAD-TIME REGISTER

| U-0                                                                  | U-0   | R/W-0            | R/W-0 | R/W-0             | R/W-0    | R/W-0           | R/W-0 |  |  |

|----------------------------------------------------------------------|-------|------------------|-------|-------------------|----------|-----------------|-------|--|--|

| _                                                                    | _     |                  |       | ALTDTF            | Rx<13:8> |                 |       |  |  |

| bit 15                                                               |       |                  |       |                   |          |                 | bit 8 |  |  |

|                                                                      |       |                  |       |                   |          |                 |       |  |  |

| R/W-0                                                                | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0    | R/W-0           | R/W-0 |  |  |

|                                                                      |       |                  | ALTDT | Rx<7:0>           |          |                 |       |  |  |

| bit 7                                                                |       |                  |       |                   |          |                 | bit 0 |  |  |

|                                                                      |       |                  |       |                   |          |                 |       |  |  |

| Legend:                                                              |       |                  |       |                   |          |                 |       |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |       |                  |       |                   |          |                 |       |  |  |

| -n = Value at F                                                      | POR   | '1' = Bit is set |       | '0' = Bit is clea | ared     | x = Bit is unkr | nown  |  |  |

bit 15-14 Unimplemented: Read as '0'

bit 13-0 ALTDTRx<13:0>: Unsigned 14-Bit Dead-Time Value for PWMx Dead-Time Unit bits

| U-0                   | U-0                                | HS, R/C-0                          | R/W-0            | HS, R/C-0        | R/W-0            | HS, R/C-0             | R/W-0    |

|-----------------------|------------------------------------|------------------------------------|------------------|------------------|------------------|-----------------------|----------|

| _                     | —                                  | PCHEQIRQ                           | PCHEQIEN         | PCLEQIRQ         | PCLEQIEN         | POSOVIRQ              | POSOVIEN |

| bit 15                |                                    |                                    |                  |                  |                  |                       | bit 8    |

|                       |                                    |                                    |                  |                  |                  |                       |          |

| HS, R/C-0             | R/W-0                              | HS, R/C-0                          | R/W-0            | HS, R/C-0        | R/W-0            | HS, R/C-0             | R/W-0    |

| PCIIRQ <sup>(1)</sup> | PCIIEN                             | VELOVIRQ                           | VELOVIEN         | HOMIRQ           | HOMIEN           | IDXIRQ                | IDXIEN   |

| bit 7                 |                                    |                                    |                  |                  |                  |                       | bit 0    |

| r                     |                                    |                                    |                  |                  |                  |                       |          |

| Legend:               |                                    | HS = Hardware                      |                  | C = Clearable    |                  |                       |          |

| R = Readable I        |                                    | W = Writable b                     | bit              | •                | nented bit, rea  |                       |          |

| -n = Value at P       | OR                                 | '1' = Bit is set                   |                  | '0' = Bit is cle | ared             | x = Bit is unkr       | iown     |

|                       |                                    |                                    |                  |                  |                  |                       |          |

| bit 15-14             | -                                  | ted: Read as '0                    |                  |                  |                  | .,                    |          |

| bit 13                |                                    | Position Counte                    | er Greater Tha   | n or Equal Cor   | npare Status b   | it                    |          |

|                       |                                    | T ≥ QEI1GEC<br>T < QEI1GEC         |                  |                  |                  |                       |          |

| bit 12                |                                    | Position Counte                    | r Greater Tha    | n or Equal Con   | npare Interrupt  | Enable bit            |          |

|                       | 1 = Interrupt i                    |                                    |                  |                  |                  |                       |          |

|                       | 0 = Interrupt i                    | s disabled                         |                  |                  |                  |                       |          |

| bit 11                |                                    | Position Counte                    | r Less Than o    | r Equal Compa    | are Status bit   |                       |          |

|                       | 1 = POS1CN                         |                                    |                  |                  |                  |                       |          |

| bit 10                |                                    | Position Counte                    | r Less Than or   | - Equal Compa    | ire Interrunt En | ahla hit              |          |

|                       | 1 = Interrupt i                    |                                    |                  |                  |                  |                       |          |

|                       | 0 = Interrupt i                    |                                    |                  |                  |                  |                       |          |

| bit 9                 | POSOVIRQ:                          | Position Counte                    | er Overflow Sta  | itus bit         |                  |                       |          |

|                       | 1 = Overflow                       |                                    |                  |                  |                  |                       |          |

|                       |                                    | ow has occurred                    |                  |                  |                  |                       |          |

| bit 8                 |                                    | Position Counte                    | r Overflow Inte  | errupt Enable b  | Dit              |                       |          |

|                       | 1 = Interrupt i<br>0 = Interrupt i |                                    |                  |                  |                  |                       |          |

| bit 7                 | •                                  | tion Counter (H                    | oming) Initializ | ation Process    | Complete Stat    | us bit <sup>(1)</sup> |          |

|                       |                                    | T was reinitialize                 | •                |                  | · · · · · · · ·  |                       |          |

|                       | 0 = POS1CN                         | T was not reiniti                  | alized           |                  |                  |                       |          |

| bit 6                 | PCIIEN: Posi                       | tion Counter (He                   | oming) Initializ | ation Process    | Complete inter   | rupt Enable bit       |          |

|                       | 1 = Interrupt i                    |                                    |                  |                  |                  |                       |          |

| bit 5                 | 0 = Interrupt i                    |                                    | r Overflow Sta   | tuo hit          |                  |                       |          |

| DIL 5                 | 1 = Overflow                       | Velocity Counter                   | I Overnow Sta    |                  |                  |                       |          |

|                       |                                    | ow has not occu                    | irred            |                  |                  |                       |          |

| bit 4                 | VELOVIEN:                          | /elocity Counter                   | Overflow Inte    | rrupt Enable bi  | it               |                       |          |

|                       | 1 = Interrupt i                    | s enabled                          |                  |                  |                  |                       |          |

|                       | 0 = Interrupt i                    |                                    |                  |                  |                  |                       |          |

| bit 3                 |                                    | atus Flag for Ho                   |                  | us bit           |                  |                       |          |

|                       |                                    | ent has occurred<br>event has occu |                  |                  |                  |                       |          |

|                       |                                    |                                    |                  |                  |                  |                       |          |

#### REGISTER 17-3: QEI1STAT: QEI1 STATUS REGISTER

**Note 1:** This status bit is only applicable to PIMOD<2:0> modes, '011' and '100'.

## 19.0 INTER-INTEGRATED CIRCUIT<sup>™</sup> (I<sup>2</sup>C<sup>™</sup>)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXGP50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS70330) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

- 3: There are minimum bit rates of approximately FCY/512. As a result, high processor speeds may not support 100 Kbit/second operation. See timing specifications, IM10 and IM11, and the "Baud Rate Generator" in the "dsPIC33/PIC24 Family Reference Manual".

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X family of devices contains two Inter-Integrated Circuit (I<sup>2</sup>C) modules: I2C1 and I2C2.

The  $l^2C$  module provides complete hardware support for both Slave and Multi-Master modes of the  $l^2C$  serial communication standard, with a 16-bit interface.

The I<sup>2</sup>C module has a 2-pin interface:

- · The SCLx pin is clock

- The SDAx pin is data

The I<sup>2</sup>C module offers the following key features:

- I<sup>2</sup>C interface supporting both Master and Slave modes of operation

- I<sup>2</sup>C Slave mode supports 7 and 10-bit addressing

- I<sup>2</sup>C Master mode supports 7 and 10-bit addressing

- I<sup>2</sup>C port allows bidirectional transfers between master and slaves

- Serial clock synchronization for I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control)

- I<sup>2</sup>C supports multi-master operation, detects bus collision and arbitrates accordingly

- Intelligent Platform Management Interface (IPMI)

support

- System Management Bus (SMBus) support

| U-0               | U-0                                                                                                                                                                                                      | U-0                                                                                                              | U-0 | U-0              | U-0              | U-0                | R/W-0  |  |  |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-----|------------------|------------------|--------------------|--------|--|--|--|

| —                 | —                                                                                                                                                                                                        | —                                                                                                                | —   | —                | —                |                    |        |  |  |  |

| bit 15            |                                                                                                                                                                                                          |                                                                                                                  |     |                  |                  |                    | bit 8  |  |  |  |

|                   |                                                                                                                                                                                                          |                                                                                                                  |     |                  |                  |                    |        |  |  |  |

| U-0               | U-0                                                                                                                                                                                                      | U-0                                                                                                              | U-0 | U-0              | R/W-0            | R/W-0              | R/W-0  |  |  |  |

| _                 |                                                                                                                                                                                                          | —                                                                                                                |     |                  | DMABL2           | DMABL1             | DMABL0 |  |  |  |

| bit 7             |                                                                                                                                                                                                          |                                                                                                                  |     |                  |                  |                    | bit 0  |  |  |  |

| Levend            |                                                                                                                                                                                                          |                                                                                                                  |     |                  |                  |                    |        |  |  |  |

| Legend:           | le hit                                                                                                                                                                                                   |                                                                                                                  | .:. |                  | mented bit mee   |                    |        |  |  |  |

|                   |                                                                                                                                                                                                          | W = Writable bit                                                                                                 |     | •                | mented bit, read |                    |        |  |  |  |

| -n = Value at POR |                                                                                                                                                                                                          | '1' = Bit is set                                                                                                 |     | '0' = Bit is cle | eared            | x = Bit is unknown |        |  |  |  |

| bit 15-9          | Unimplemen                                                                                                                                                                                               | tod: Poad as 'n                                                                                                  | ,   |                  |                  |                    |        |  |  |  |

| bit 8             | -                                                                                                                                                                                                        | Unimplemented: Read as '0' ADDMAEN: ADC1 DMA Enable bit                                                          |     |                  |                  |                    |        |  |  |  |

|                   | 1 = Conversion results are stored in the ADC1BUF0 register for transfer to RAM using DMA                                                                                                                 |                                                                                                                  |     |                  |                  |                    |        |  |  |  |

|                   | <ul> <li>Conversion results are stored in ADC1BUF0 register for transfer to RAM using DMA</li> <li>Conversion results are stored in ADC1BUF0 through ADC1BUFF registers; DMA will not be used</li> </ul> |                                                                                                                  |     |                  |                  |                    |        |  |  |  |

| bit 7-3           | Unimplemen                                                                                                                                                                                               | Unimplemented: Read as '0'                                                                                       |     |                  |                  |                    |        |  |  |  |

| bit 2-0           | DMABL<2:0>: Selects Number of DMA Buffer Locations per Analog Input bits                                                                                                                                 |                                                                                                                  |     |                  |                  |                    |        |  |  |  |

|                   | 111 = Allocates 128 words of buffer to each analog input                                                                                                                                                 |                                                                                                                  |     |                  |                  |                    |        |  |  |  |

|                   | 110 = Allocates 64 words of buffer to each analog input                                                                                                                                                  |                                                                                                                  |     |                  |                  |                    |        |  |  |  |