Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                      |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 60 MIPs                                                                       |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

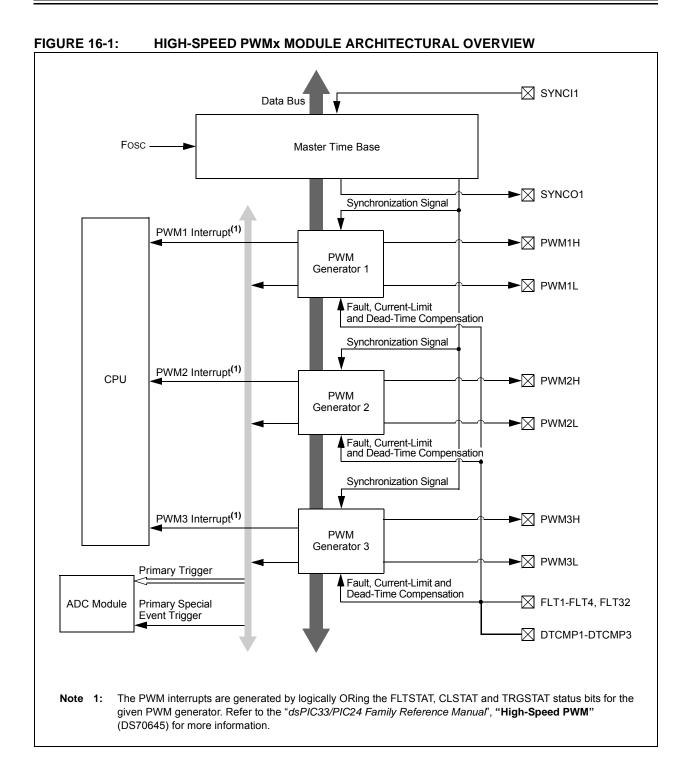

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                    |

| Number of I/O              | 35                                                                            |

| Program Memory Size        | 32KB (10.7K x 24)                                                             |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 2K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 9x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 44-VQFN Exposed Pad                                                           |

| Supplier Device Package    | 44-QFN (8x8)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep32gp204-h-ml |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

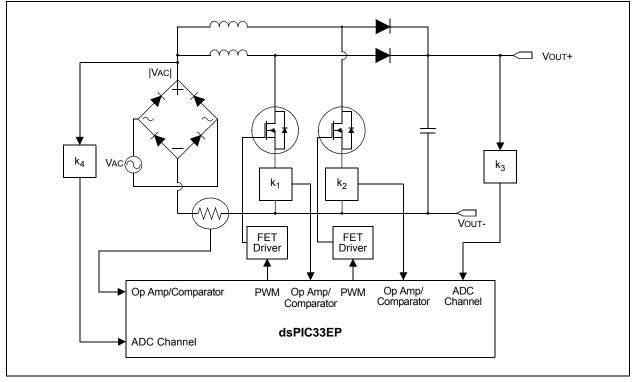

#### FIGURE 2-7: INTERLEAVED PFC

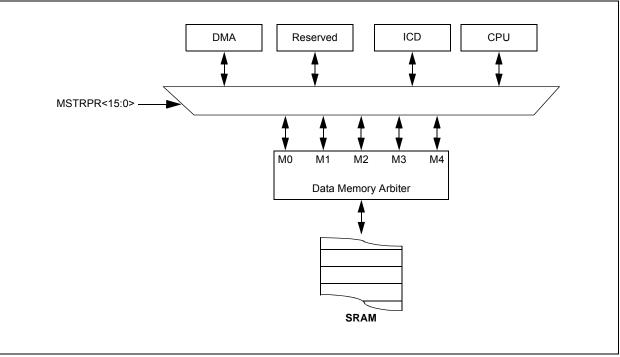

## 4.4.3 DATA MEMORY ARBITRATION AND BUS MASTER PRIORITY

EDS accesses from bus masters in the system are arbitrated.

The arbiter for data memory (including EDS) arbitrates between the CPU, the DMA and the ICD module. In the event of coincidental access to a bus by the bus masters, the arbiter determines which bus master access has the highest priority. The other bus masters are suspended and processed after the access of the bus by the bus master with the highest priority.

By default, the CPU is Bus Master 0 (M0) with the highest priority and the ICD is Bus Master 4 (M4) with the lowest priority. The remaining bus master (DMA Controller) is allocated to M3 (M1 and M2 are reserved and cannot be used). The user application may raise or lower the priority of the DMA Controller to be above that of the CPU by setting the appropriate bits in the EDS Bus Master Priority Control (MSTRPR) register. All bus masters with raised priorities will maintain the same priority relationship relative to each other (i.e., M1 being highest and M3 being lowest, with M2 in between). Also, all the bus masters with priorities below

### FIGURE 4-18: ARBITER ARCHITECTURE

that of the CPU maintain the same priority relationship relative to each other. The priority schemes for bus masters with different MSTRPR values are tabulated in Table 4-62.

This bus master priority control allows the user application to manipulate the real-time response of the system, either statically during initialization or dynamically in response to real-time events.

| TABLE 4-62: | DATA MEMORY BUS  |

|-------------|------------------|

|             | ARBITER PRIORITY |

| Drierity     | MSTRPR<15:0> Bit Setting <sup>(1)</sup> |          |  |  |  |

|--------------|-----------------------------------------|----------|--|--|--|

| Priority     | 0x0000                                  | 0x0020   |  |  |  |

| M0 (highest) | CPU                                     | DMA      |  |  |  |

| M1           | Reserved                                | CPU      |  |  |  |

| M2           | Reserved                                | Reserved |  |  |  |

| M3           | DMA                                     | Reserved |  |  |  |

| M4 (lowest)  | ICD                                     | ICD      |  |  |  |

**Note 1:** All other values of MSTRPR<15:0> are reserved.

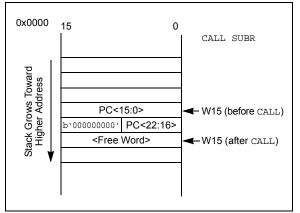

#### 4.4.4 SOFTWARE STACK

The W15 register serves as a dedicated Software Stack Pointer (SSP) and is automatically modified by exception processing, subroutine calls and returns; however, W15 can be referenced by any instruction in the same manner as all other W registers. This simplifies reading, writing and manipulating of the Stack Pointer (for example, creating stack frames).

| Note: | To protect against misaligned stack               |

|-------|---------------------------------------------------|

|       | accesses, W15<0> is fixed to '0' by the hardware. |

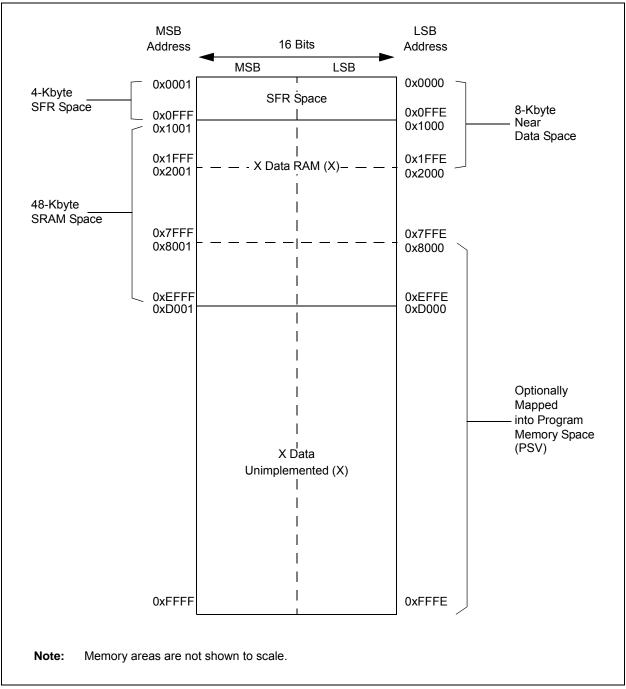

W15 is initialized to 0x1000 during all Resets. This address ensures that the SSP points to valid RAM in all dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices, and permits stack availability for non-maskable trap exceptions. These can occur before the SSP is initialized by the user software. You can reprogram the SSP during initialization to any location within Data Space.

The Software Stack Pointer always points to the first available free word and fills the software stack working from lower toward higher addresses. Figure 4-19 illustrates how it pre-decrements for a stack pop (read) and post-increments for a stack push (writes).

When the PC is pushed onto the stack, PC<15:0> are pushed onto the first available stack word, then PC<22:16> are pushed into the second available stack location. For a PC push during any CALL instruction, the MSB of the PC is zero-extended before the push, as shown in Figure 4-19. During exception processing, the MSB of the PC is concatenated with the lower 8 bits of the CPU STATUS Register, SR. This allows the contents of SRL to be preserved automatically during interrupt processing.

- **Note 1:** To maintain system Stack Pointer (W15) coherency, W15 is never subject to (EDS) paging, and is therefore restricted to an address range of 0x0000 to 0xFFFF. The same applies to the W14 when used as a Stack Frame Pointer (SFA = 1).

- 2: As the stack can be placed in, and can access X and Y spaces, care must be taken regarding its use, particularly with regard to local automatic variables in a C development environment

FIGURE 4-19: CALL STACK FRAME

|                                               | Vector | IRQ        |                   | Interrupt Bit Location |          |             |

|-----------------------------------------------|--------|------------|-------------------|------------------------|----------|-------------|

| Interrupt Source                              | #      | #          | IVT Address       | Flag                   | Enable   | Priority    |

|                                               | High   | est Natura | I Order Priority  |                        |          |             |

| INT0 – External Interrupt 0                   | 8      | 0          | 0x000014          | IFS0<0>                | IEC0<0>  | IPC0<2:0>   |

| IC1 – Input Capture 1                         | 9      | 1          | 0x000016          | IFS0<1>                | IEC0<1>  | IPC0<6:4>   |

| OC1 – Output Compare 1                        | 10     | 2          | 0x000018          | IFS0<2>                | IEC0<2>  | IPC0<10:8>  |

| T1 – Timer1                                   | 11     | 3          | 0x00001A          | IFS0<3>                | IEC0<3>  | IPC0<14:12> |

| DMA0 – DMA Channel 0                          | 12     | 4          | 0x00001C          | IFS0<4>                | IEC0<4>  | IPC1<2:0>   |

| IC2 – Input Capture 2                         | 13     | 5          | 0x00001E          | IFS0<5>                | IEC0<5>  | IPC1<6:4>   |

| OC2 – Output Compare 2                        | 14     | 6          | 0x000020          | IFS0<6>                | IEC0<6>  | IPC1<10:8>  |

| T2 – Timer2                                   | 15     | 7          | 0x000022          | IFS0<7>                | IEC0<7>  | IPC1<14:12> |

| T3 – Timer3                                   | 16     | 8          | 0x000024          | IFS0<8>                | IEC0<8>  | IPC2<2:0>   |

| SPI1E – SPI1 Error                            | 17     | 9          | 0x000026          | IFS0<9>                | IEC0<9>  | IPC2<6:4>   |

| SPI1 – SPI1 Transfer Done                     | 18     | 10         | 0x000028          | IFS0<10>               | IEC0<10> | IPC2<10:8>  |

| U1RX – UART1 Receiver                         | 19     | 11         | 0x00002A          | IFS0<11>               | IEC0<11> | IPC2<14:12> |

| U1TX – UART1 Transmitter                      | 20     | 12         | 0x00002C          | IFS0<12>               | IEC0<12> | IPC3<2:0>   |

| AD1 – ADC1 Convert Done                       | 21     | 13         | 0x00002E          | IFS0<13>               | IEC0<13> | IPC3<6:4>   |

| DMA1 – DMA Channel 1                          | 22     | 14         | 0x000030          | IFS0<14>               | IEC0<14> | IPC3<10:8>  |

| Reserved                                      | 23     | 15         | 0x000032          |                        |          | _           |

| SI2C1 – I2C1 Slave Event                      | 24     | 16         | 0x000034          | IFS1<0>                | IEC1<0>  | IPC4<2:0>   |

| MI2C1 – I2C1 Master Event                     | 25     | 17         | 0x000036          | IFS1<1>                | IEC1<1>  | IPC4<6:4>   |

| CM – Comparator Combined Event                | 26     | 18         | 0x000038          | IFS1<2>                | IEC1<2>  | IPC4<10:8>  |

| CN – Input Change Interrupt                   | 27     | 19         | 0x00003A          | IFS1<3>                | IEC1<3>  | IPC4<14:12> |

| INT1 – External Interrupt 1                   | 28     | 20         | 0x00003C          | IFS1<4>                | IEC1<4>  | IPC5<2:0>   |

| Reserved                                      | 29-31  | 21-23      | 0x00003E-0x000042 |                        |          | _           |

| DMA2 – DMA Channel 2                          | 32     | 24         | 0x000044          | IFS1<8>                | IEC1<8>  | IPC6<2:0>   |

| OC3 – Output Compare 3                        | 33     | 25         | 0x000046          | IFS1<9>                | IEC1<9>  | IPC6<6:4>   |

| OC4 – Output Compare 4                        | 34     | 26         | 0x000048          | IFS1<10>               | IEC1<10> | IPC6<10:8>  |

| T4 – Timer4                                   | 35     | 27         | 0x00004A          | IFS1<11>               | IEC1<11> | IPC6<14:12> |

| T5 – Timer5                                   | 36     | 28         | 0x00004C          | IFS1<12>               | IEC1<12> | IPC7<2:0>   |

| INT2 – External Interrupt 2                   | 37     | 29         | 0x00004E          | IFS1<13>               | IEC1<13> | IPC7<6:4>   |

| U2RX – UART2 Receiver                         | 38     | 30         | 0x000050          | IFS1<14>               | IEC1<14> | IPC7<10:8>  |

| U2TX – UART2 Transmitter                      | 39     | 31         | 0x000052          | IFS1<15>               | IEC1<15> | IPC7<14:12> |

| SPI2E – SPI2 Error                            | 40     | 32         | 0x000054          | IFS2<0>                | IEC2<0>  | IPC8<2:0>   |

| SPI2 – SPI2 Transfer Done                     | 41     | 33         | 0x000056          | IFS2<1>                | IEC2<1>  | IPC8<6:4>   |

| C1RX – CAN1 RX Data Ready <sup>(1)</sup>      | 42     | 34         | 0x000058          | IFS2<2>                | IEC2<2>  | IPC8<10:8>  |

| C1 – CAN1 Event <sup>(1)</sup>                | 43     | 35         | 0x00005A          | IFS2<3>                | IEC2<3>  | IPC8<14:12> |

| DMA3 – DMA Channel 3                          | 44     | 36         | 0x00005C          | IFS2<4>                | IEC2<4>  | IPC9<2:0>   |

| IC3 – Input Capture 3                         | 45     | 37         | 0x00005E          | IFS2<5>                | IEC2<5>  | IPC9<6:4>   |

| IC4 – Input Capture 4                         | 46     | 38         | 0x000060          | IFS2<6>                | IEC2<6>  | IPC9<10:8>  |

| Reserved                                      | 47-56  | 39-48      | 0x000062-0x000074 | —                      | —        | —           |

| SI2C2 – I2C2 Slave Event                      | 57     | 49         | 0x000076          | IFS3<1>                | IEC3<1>  | IPC12<6:4>  |

| MI2C2 – I2C2 Master Event                     | 58     | 50         | 0x000078          | IFS3<2>                | IEC3<2>  | IPC12<10:8> |

| Reserved                                      | 59-64  | 51-56      | 0x00007A-0x000084 |                        | _        |             |

| PSEM – PWM Special Event Match <sup>(2)</sup> | 65     | 57         | 0x000086          | IFS3<9>                | IEC3<9>  | IPC14<6:4>  |

#### TABLE 7-1: INTERRUPT VECTOR DETAILS

Note 1: This interrupt source is available on dsPIC33EPXXXGP50X and dsPIC33EPXXXMC50X devices only.

2: This interrupt source is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

#### REGISTER 8-3: DMAXSTAH: DMA CHANNEL X START ADDRESS REGISTER A (HIGH)

| U-0            | U-0   | U-0            | U-0   | U-0          | U-0              | U-0    | U-0   |

|----------------|-------|----------------|-------|--------------|------------------|--------|-------|

| —              | _     | —              | —     | —            | —                | —      | —     |

| bit 15         |       |                |       |              |                  |        | bit 8 |

|                |       |                |       |              |                  |        |       |

| R/W-0          | R/W-0 | R/W-0          | R/W-0 | R/W-0        | R/W-0            | R/W-0  | R/W-0 |

|                |       |                | STA<  | 23:16>       |                  |        |       |

| bit 7          |       |                |       |              |                  |        | bit 0 |

|                |       |                |       |              |                  |        |       |

| Legend:        |       |                |       |              |                  |        |       |

| R = Readable b | oit   | W = Writable b | it    | U = Unimpler | mented bit, read | as '0' |       |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

|-------------------|------------------|----------------------|--------------------|

|                   |                  |                      |                    |

#### bit 15-8 Unimplemented: Read as '0'

bit 7-0 STA<23:16>: Primary Start Address bits (source or destination)

#### REGISTER 8-4: DMAXSTAL: DMA CHANNEL x START ADDRESS REGISTER A (LOW)

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|-----------------|-------|------------------|-------|-----------------------------------------|-------|-------|-------|

|                 |       |                  | STA   | <15:8>                                  |       |       |       |

| bit 15          |       |                  |       |                                         |       |       | bit 8 |

|                 |       |                  |       |                                         |       |       |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|                 |       |                  | STA   | A<7:0>                                  |       |       |       |

| bit 7           |       |                  |       |                                         |       |       | bit 0 |

|                 |       |                  |       |                                         |       |       |       |

| Legend:         |       |                  |       |                                         |       |       |       |

| R = Readable    | bit   | W = Writable b   | oit   | U = Unimplemented bit, read as '0'      |       |       |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |       |       | nown  |

bit 15-0 STA<15:0>: Primary Start Address bits (source or destination)

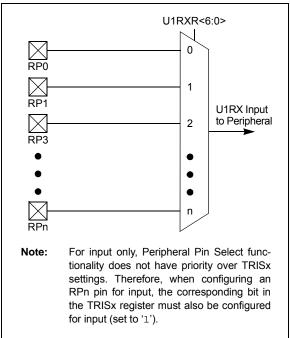

#### 11.4.4 INPUT MAPPING

The inputs of the Peripheral Pin Select options are mapped on the basis of the peripheral. That is, a control register associated with a peripheral dictates the pin it will be mapped to. The RPINRx registers are used to configure peripheral input mapping (see Register 11-1 through Register 11-17). Each register contains sets of 7-bit fields, with each set associated with one of the remappable peripherals. Programming a given peripheral's bit field with an appropriate 7-bit value maps the RPn pin with the corresponding value to that peripheral. For any given device, the valid range of values for any bit field corresponds to the maximum number of Peripheral Pin Selections supported by the device.

For example, Figure 11-2 illustrates remappable pin selection for the U1RX input.

#### FIGURE 11-2: REMAPPABLE INPUT FOR U1RX

#### 11.4.4.1 Virtual Connections

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices support virtual (internal) connections to the output of the op amp/ comparator module (see Figure 25-1 in Section 25.0 "Op Amp/Comparator Module"), and the PTG module (see Section 24.0 "Peripheral Trigger Generator (PTG) Module").

In addition, dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices support virtual connections to the filtered QEI module inputs: FINDX1, FHOME1, FINDX2 and FHOME2 (see Figure 17-1 in Section 17.0 "Quadrature Encoder Interface (QEI) Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)".

Virtual connections provide a simple way of interperipheral connection without utilizing a physical pin. For example, by setting the FLT1R<6:0> bits of the RPINR12 register to the value of `b0000001, the output of the analog comparator, C1OUT, will be connected to the PWM Fault 1 input, which allows the analog comparator to trigger PWM Faults without the use of an actual physical pin on the device.

Virtual connection to the QEI module allows peripherals to be connected to the QEI digital filter input. To utilize this filter, the QEI module must be enabled and its inputs must be connected to a physical RPn pin. Example 11-2 illustrates how the input capture module can be connected to the QEI digital filter.

# EXAMPLE 11-2: CONNECTING IC1 TO THE HOME1 QEI1 DIGITAL FILTER INPUT ON PIN 43 OF THE dsPIC33EPXXXMC206 DEVICE

| RPINR15 = 0x2500; | /* Connect the QEI1 HOME1 input to RP37 (pin 43) */                   |

|-------------------|-----------------------------------------------------------------------|

| RPINR7 = 0x009;   | /* Connect the IC1 input to the digital filter on the FHOME1 input */ |

| QEI1IOC = 0x4000; | /* Enable the QEI digital filter */                                   |

| QEI1CON = 0x8000; | /* Enable the QEI module */                                           |

#### **REGISTER 15-1: OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1 (CONTINUED)**

- bit 3 TRIGMODE: Trigger Status Mode Select bit

- 1 = TRIGSTAT (OCxCON2<6>) is cleared when OCxRS = OCxTMR or in software

- 0 = TRIGSTAT is cleared only by software

- bit 2-0 OCM<2:0>: Output Compare x Mode Select bits

- 111 = Center-Aligned PWM mode: Output set high when OCxTMR = OCxR and set low when OCxTMR = OCxRS<sup>(1)</sup>

- 110 = Edge-Aligned PWM mode: Output set high when OCxTMR = 0 and set low when OCxTMR = OCxR<sup>(1)</sup>

- 101 = Double Compare Continuous Pulse mode: Initializes OCx pin low, toggles OCx state continuously on alternate matches of OCxR and OCxRS

- 100 = Double Compare Single-Shot mode: Initializes OCx pin low, toggles OCx state on matches of OCxR and OCxRS for one cycle

- 011 = Single Compare mode: Compare event with OCxR, continuously toggles OCx pin

- 010 = Single Compare Single-Shot mode: Initializes OCx pin high, compare event with OCxR, forces OCx pin low

- 001 = Single Compare Single-Shot mode: Initializes OCx pin low, compare event with OCxR, forces OCx pin high

- 000 = Output compare channel is disabled

- Note 1: OCxR and OCxRS are double-buffered in PWM mode only.

- 2: Each Output Compare x module (OCx) has one PTG clock source. See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for more information.

- PTGO4 = OC1 PTGO5 = OC2

- PTGO6 = OC3 PTGO7 = OC4

#### REGISTER 17-7: VEL1CNT: VELOCITY COUNTER 1 REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|-----------------|-------|------------------|-------|-----------------------------------------|-------|-------|-------|

|                 |       |                  | VELC  | NT<15:8>                                |       |       |       |

| bit 15          |       |                  |       |                                         |       |       | bit 8 |

|                 |       |                  |       |                                         |       |       |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|                 |       |                  | VELC  | NT<7:0>                                 |       |       |       |

| bit 7           |       |                  |       |                                         |       |       | bit 0 |

|                 |       |                  |       |                                         |       |       |       |

| Legend:         |       |                  |       |                                         |       |       |       |

| R = Readable I  | bit   | W = Writable b   | oit   | U = Unimplemented bit, read as '0'      |       |       |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |       |       | nown  |

bit 15-0 VELCNT<15:0>: Velocity Counter bits

#### REGISTER 17-8: INDX1CNTH: INDEX COUNTER 1 HIGH WORD REGISTER

| R/W-0  | R/W-0 | R/W-0 | R/W-0               | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|---------------------|----------|-------|-------|-------|

|        |       |       | INDXCN <sup>®</sup> | T<31:24> |       |       |       |

| bit 15 |       |       |                     |          |       |       | bit 8 |

|        |       |       |                     |          |       |       |       |

| R/W-0  | R/W-0 | R/W-0 | R/W-0               | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|        |       |       | INDXCN              | T<23:16> |       |       |       |

| bit 7  |       |       |                     |          |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 INDXCNT<31:16>: High Word Used to Form 32-Bit Index Counter Register (INDX1CNT) bits

#### REGISTER 17-9: INDX1CNTL: INDEX COUNTER 1 LOW WORD REGISTER

'1' = Bit is set

| <b>Legend:</b><br>R = Readable b | it    | W = Writable bit |        | U = Unimplen | nented bit, reac | l as '0' |       |

|----------------------------------|-------|------------------|--------|--------------|------------------|----------|-------|

| bit 7                            |       |                  |        |              |                  |          | bit 0 |

|                                  |       |                  | INDXC  | NT<7:0>      |                  |          |       |

| R/W-0                            | R/W-0 | R/W-0            | R/W-0  | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

| bit 15                           |       |                  |        |              |                  |          | bit 8 |

|                                  |       |                  | INDXCN | NT<15:8>     |                  |          |       |

| R/W-0                            | R/W-0 | R/W-0            | R/W-0  | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

'0' = Bit is cleared

bit 15-0 INDXCNT<15:0>: Low Word Used to Form 32-Bit Index Counter Register (INDX1CNT) bits

-n = Value at POR

x = Bit is unknown

#### REGISTER 18-1: SPIx STAT: SPIx STATUS AND CONTROL REGISTER (CONTINUED)

- bit 1 SPITBF: SPIx Transmit Buffer Full Status bit

- 1 = Transmit not yet started, SPIxTXB is full

- 0 = Transmit started, SPIxTXB is empty

#### Standard Buffer mode:

Automatically set in hardware when core writes to the SPIxBUF location, loading SPIxTXB. Automatically cleared in hardware when SPIx module transfers data from SPIxTXB to SPIxSR.

#### Enhanced Buffer mode:

Automatically set in hardware when the CPU writes to the SPIxBUF location, loading the last available buffer location. Automatically cleared in hardware when a buffer location is available for a CPU write operation.

#### bit 0 SPIRBF: SPIx Receive Buffer Full Status bit

1 = Receive is complete, SPIxRXB is full

0 = Receive is incomplete, SPIxRXB is empty

#### Standard Buffer mode:

Automatically set in hardware when SPIx transfers data from SPIxSR to SPIxRXB. Automatically cleared in hardware when the core reads the SPIxBUF location, reading SPIxRXB.

#### Enhanced Buffer mode:

Automatically set in hardware when SPIx transfers data from SPIxSR to the buffer, filling the last unread buffer location. Automatically cleared in hardware when a buffer location is available for a transfer from SPIxSR.

| R/W-0         | R/W-0                                                                  | R/W-0                                    | U-0        | U-0               | U-0                  | U-0               | U-0                |  |

|---------------|------------------------------------------------------------------------|------------------------------------------|------------|-------------------|----------------------|-------------------|--------------------|--|

| FRMEN         | SPIFSD                                                                 | FRMPOL                                   | —          | —                 | _                    | —                 | —                  |  |

| bit 15        |                                                                        |                                          |            |                   |                      |                   | bit 8              |  |

|               |                                                                        |                                          |            |                   |                      |                   |                    |  |

| U-0           | U-0                                                                    | U-0                                      | U-0        | U-0               | U-0                  | R/W-0             | R/W-0              |  |

| —             | —                                                                      | —                                        | —          | —                 | _                    | FRMDLY            | SPIBEN             |  |

| bit 7         |                                                                        |                                          |            |                   |                      |                   | bit 0              |  |

|               |                                                                        |                                          |            |                   |                      |                   |                    |  |

| Legend:       |                                                                        |                                          |            |                   |                      |                   |                    |  |

| R = Readable  | e bit                                                                  | W = Writable b                           | pit        | U = Unimpler      | nented bit, rea      | ad as '0'         |                    |  |

| -n = Value at | POR                                                                    | '1' = Bit is set                         |            | '0' = Bit is cle  | '0' = Bit is cleared |                   | x = Bit is unknown |  |

|               |                                                                        |                                          |            |                   |                      |                   |                    |  |

| bit 15        |                                                                        | med SPIx Suppo                           |            |                   |                      |                   |                    |  |

|               |                                                                        | SPIx support is e<br>SPIx support is d   |            | sx pin is used as | Frame Sync           | pulse input/outpu | ıt)                |  |

| bit 14        |                                                                        | me Sync Pulse I                          |            | ontrol bit        |                      |                   |                    |  |

|               | 1 = Frame S                                                            | ync pulse input (                        | slave)     |                   |                      |                   |                    |  |

|               |                                                                        | ync pulse output                         | . ,        |                   |                      |                   |                    |  |

| bit 13        |                                                                        | ame Sync Pulse                           |            | t                 |                      |                   |                    |  |

|               |                                                                        | ync pulse is activ<br>ync pulse is activ |            |                   |                      |                   |                    |  |

| bit 12-2      | •                                                                      |                                          |            |                   |                      |                   |                    |  |

| bit 1         | Unimplemented: Read as '0'<br>FRMDLY: Frame Sync Pulse Edge Select bit |                                          |            |                   |                      |                   |                    |  |

|               | 1 = Frame Sync pulse coincides with first bit clock                    |                                          |            |                   |                      |                   |                    |  |

|               | 0 = Frame Sync pulse precedes first bit clock                          |                                          |            |                   |                      |                   |                    |  |

| bit 0         | SPIBEN: Enhanced Buffer Enable bit                                     |                                          |            |                   |                      |                   |                    |  |

|               | 1 = Enhance                                                            | d buffer is enabl                        | ed         |                   |                      |                   |                    |  |

|               | 0 = Enhance                                                            | d buffer is disabl                       | ed (Standa | rd mode)          |                      |                   |                    |  |

|               |                                                                        |                                          |            |                   |                      |                   |                    |  |

#### REGISTER 18-3: SPIxCON2: SPIx CONTROL REGISTER 2

| REGISTER 21-26: | CxTRmnCON: ECANx TX/RX BUFFER mn CONTROL REGISTER |

|-----------------|---------------------------------------------------|

|                 | (m = 0,2,4,6; n = 1,3,5,7)                        |

|               | (                                                                                                                                                       | ,_, ., ., ., .,                   | -,-,-,                |                          |                  |                 |                 |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----------------------|--------------------------|------------------|-----------------|-----------------|

| R/W-0         | R-0                                                                                                                                                     | R-0                               | R-0                   | R/W-0                    | R/W-0            | R/W-0           | R/W-0           |

| TXENn         | TXABTn                                                                                                                                                  | TXLARBn                           | TXERRn                | TXREQn                   | RTRENn           | TXnPRI1         | TXnPRI0         |

| bit 15        |                                                                                                                                                         |                                   |                       |                          |                  |                 | bit 8           |

| R/W-0         | R-0                                                                                                                                                     | R-0                               | R-0                   | R/W-0                    | R/W-0            | R/W-0           | R/W-0           |

| TXENm         | TXABTm <sup>(1)</sup>                                                                                                                                   | TXLARBm <sup>(1)</sup>            | TXERRm <sup>(1)</sup> | TXREQm                   | RTRENm           | TXmPRI1         | TXmPRI0         |

| bit 7         |                                                                                                                                                         |                                   |                       |                          |                  |                 | bit C           |

| Legend:       |                                                                                                                                                         |                                   |                       |                          |                  |                 |                 |

| R = Readabl   | le bit                                                                                                                                                  | W = Writable                      | bit                   | U = Unimpler             | mented bit, read | d as '0'        |                 |

| -n = Value at | t POR                                                                                                                                                   | '1' = Bit is set                  |                       | '0' = Bit is cle         | ared             | x = Bit is unki | nown            |

| bit 15-8      | See Definitio                                                                                                                                           | n for bits<7:0>,                  | Controls Buffe        | <u>er n</u>              |                  |                 |                 |

| bit 7         |                                                                                                                                                         | RX Buffer Sele                    |                       |                          |                  |                 |                 |

|               |                                                                                                                                                         | RBn is a transm                   |                       |                          |                  |                 |                 |

|               | 0 = Buffer TR                                                                                                                                           | RBn is a receive                  | buffer                |                          |                  |                 |                 |

| bit 6         | TXABTm: Me                                                                                                                                              | essage Aborted                    | d bit <sup>(1)</sup>  |                          |                  |                 |                 |

|               | 1 = Message                                                                                                                                             |                                   |                       |                          |                  |                 |                 |

|               |                                                                                                                                                         | completed tran                    |                       |                          |                  |                 |                 |

| bit 5         |                                                                                                                                                         | Message Lost A                    |                       |                          |                  |                 |                 |

|               |                                                                                                                                                         | lost arbitration did not lose ar  |                       |                          |                  |                 |                 |

| bit 4         | TXERRm: Er                                                                                                                                              | ror Detected D                    | uring Transmis        | ssion bit <sup>(1)</sup> |                  |                 |                 |

|               |                                                                                                                                                         | or occurred wh<br>or did not occu |                       |                          |                  |                 |                 |

| bit 3         |                                                                                                                                                         | essage Send F                     |                       |                          |                  |                 |                 |

|               |                                                                                                                                                         | 0                                 | •                     | bit automatic            | ally clears wher | n the message   | is successfully |

|               | 0 = Clearing                                                                                                                                            | the bit to '0' wh                 | nile set reques       | ts a message             | abort            |                 |                 |

| bit 2         | RTRENm: Au                                                                                                                                              | uto-Remote Tra                    | Insmit Enable         | bit                      |                  |                 |                 |

|               | <ul> <li>1 = When a remote transmit is received, TXREQ will be set</li> <li>0 = When a remote transmit is received, TXREQ will be unaffected</li> </ul> |                                   |                       |                          |                  |                 |                 |

| bit 1-0       | TXmPRI<1:0>: Message Transmission Priority bits                                                                                                         |                                   |                       |                          |                  |                 |                 |

|               | 11 = Highest                                                                                                                                            | message prior                     | ity                   |                          |                  |                 |                 |

|               | 0                                                                                                                                                       | ermediate mes                     |                       |                          |                  |                 |                 |

|               |                                                                                                                                                         | ermediate mess<br>message priori  |                       |                          |                  |                 |                 |

|               |                                                                                                                                                         |                                   | -                     |                          |                  |                 |                 |

| Note 1: ⊤     | his bit is cleared                                                                                                                                      | when TXREQ                        | s set.                |                          |                  |                 |                 |

Note: The buffers, SID, EID, DLC, Data Field, and Receive Status registers are located in DMA RAM.

### 22.0 CHARGE TIME MEASUREMENT UNIT (CTMU)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Charge Time Measurement Unit (CTMU)" (DS70661) in the "dsPIC33/PIC24 Family Reference Manual", which is available on the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Charge Time Measurement Unit is a flexible analog module that provides accurate differential time measurement between pulse sources, as well as asynchronous pulse generation. Its key features include:

- Four Edge Input Trigger Sources

- Polarity Control for Each Edge Source

- Control of Edge Sequence

- Control of Response to Edges

- · Precise Time Measurement Resolution of 1 ns

- Accurate Current Source Suitable for Capacitive Measurement

- On-Chip Temperature Measurement using a Built-in Diode

Together with other on-chip analog modules, the CTMU can be used to precisely measure time, measure capacitance, measure relative changes in capacitance or generate output pulses that are independent of the system clock.

The CTMU module is ideal for interfacing with capacitive-based sensors. The CTMU is controlled through three registers: CTMUCON1, CTMUCON2 and CTMUICON. CTMUCON1 and CTMUCON2 enable the module and control edge source selection, edge source polarity selection and edge sequencing. The CTMUICON register controls the selection and trim of the current source.

### 24.3 PTG Control Registers

#### REGISTER 24-1: PTGCST: PTG CONTROL/STATUS REGISTER

| R/W-0   | U-0     | R/W-0   | R/W-0   | U-0 | R/W-0                 | R/W-0                  | R/W-0                  |

|---------|---------|---------|---------|-----|-----------------------|------------------------|------------------------|

| PTGEN   | —       | PTGSIDL | PTGTOGL | —   | PTGSWT <sup>(2)</sup> | PTGSSEN <sup>(3)</sup> | PTGIVIS                |

| bit 15  |         |         |         |     |                       |                        | bit 8                  |

|         |         |         |         |     |                       |                        |                        |

| R/W-0   | HS-0    | U-0     | U-0     | U-0 | U-0                   | R/V                    | V-0                    |

| PTGSTRT | PTGWDTO | _       | _       | _   | _                     | PTGITM1 <sup>(1)</sup> | PTGITM0 <sup>(1)</sup> |

| bit 7 |

|-------|

|-------|

| Legend:           | HS = Hardware Settable bi | HS = Hardware Settable bit  |                    |  |  |

|-------------------|---------------------------|-----------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit          | U = Unimplemented bit, read | d as '0'           |  |  |

| -n = Value at POR | '1' = Bit is set          | '0' = Bit is cleared        | x = Bit is unknown |  |  |

| bit 15  |       | PTGEN: Module Enable bit                                                                                                                                                                                                      |

|---------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |       | 1 = PTG module is enabled                                                                                                                                                                                                     |

|         |       | 0 = PTG module is disabled                                                                                                                                                                                                    |

| bit 14  |       | Unimplemented: Read as '0'                                                                                                                                                                                                    |

| bit 13  |       | PTGSIDL: PTG Stop in Idle Mode bit                                                                                                                                                                                            |

|         |       | <ul> <li>1 = Discontinues module operation when device enters Idle mode</li> <li>0 = Continues module operation in Idle mode</li> </ul>                                                                                       |

| bit 12  |       | PTGTOGL: PTG TRIG Output Toggle Mode bit                                                                                                                                                                                      |

|         |       | <ul> <li>1 = Toggle state of the PTGOx for each execution of the PTGTRIG command</li> <li>0 = Each execution of the PTGTRIG command will generate a single PTGOx pulse determined by the value in the PTGPWDx bits</li> </ul> |

| bit 11  |       | Unimplemented: Read as '0'                                                                                                                                                                                                    |

| bit 10  |       | PTGSWT: PTG Software Trigger bit <sup>(2)</sup>                                                                                                                                                                               |

|         |       | 1 = Triggers the PTG module                                                                                                                                                                                                   |

|         |       | 0 = No action (clearing this bit will have no effect)                                                                                                                                                                         |

| bit 9   |       | PTGSSEN: PTG Enable Single-Step bit <sup>(3)</sup>                                                                                                                                                                            |

|         |       | 1 = Enables Single-Step mode                                                                                                                                                                                                  |

|         |       | 0 = Disables Single-Step mode                                                                                                                                                                                                 |

| bit 8   |       | PTGIVIS: PTG Counter/Timer Visibility Control bit                                                                                                                                                                             |

|         |       | 1 = Reads of the PTGSDLIM, PTGCxLIM or PTGTxLIM registers return the current values of their<br>corresponding counter/timer registers (PTGSD, PTGCx, PTGTx)                                                                   |

|         |       | <ul> <li>Reads of the PTGSDLIM, PTGCxLIM or PTGTxLIM registers return the value previously written<br/>to those limit registers</li> </ul>                                                                                    |

| bit 7   |       | PTGSTRT: PTG Start Sequencer bit                                                                                                                                                                                              |

|         |       | <ul><li>1 = Starts to sequentially execute commands (Continuous mode)</li><li>0 = Stops executing commands</li></ul>                                                                                                          |

| bit 6   |       | PTGWDTO: PTG Watchdog Timer Time-out Status bit                                                                                                                                                                               |

|         |       | 1 = PTG Watchdog Timer has timed out                                                                                                                                                                                          |

|         |       | 0 = PTG Watchdog Timer has not timed out.                                                                                                                                                                                     |

| bit 5-2 |       | Unimplemented: Read as '0'                                                                                                                                                                                                    |

| Note    | 1: Th | nese bits apply to the PTGWHI and PTGWLO commands only.                                                                                                                                                                       |

|         | 2: Th | is bit is only used with the PTGCTRL step command software trigger option.                                                                                                                                                    |

3: Use of the PTG Single-Step mode is reserved for debugging tools only.

bit 0

| REGISTER      | 25-3: CM40                                              | CON: COMPA                             | RATOR 4 CO        | ONTROL RE        | GISTER             |                                            |                     |

|---------------|---------------------------------------------------------|----------------------------------------|-------------------|------------------|--------------------|--------------------------------------------|---------------------|

| R/W-0         | R/W-0                                                   | R/W-0                                  | U-0               | U-0              | U-0                | R/W-0                                      | R/W-0               |

| CON           | COE                                                     | CPOL                                   | —                 | —                | _                  | CEVT                                       | COUT                |

| bit 15        |                                                         |                                        |                   |                  |                    |                                            | bit 8               |

| R/W-0         | DAM 0                                                   | U-0                                    |                   | U-0              | U-0                |                                            | R/W-0               |

|               | R/W-0                                                   | 0-0                                    | R/W-0             | 0-0              | 0-0                | R/W-0                                      |                     |

| EVPOL1        | EVPOL0                                                  | —                                      | CREF              | —                | _                  | CCH1 <sup>(1)</sup>                        | CCH0 <sup>(1)</sup> |

| bit 7         |                                                         |                                        |                   |                  |                    |                                            | bit (               |

| Legend:       |                                                         |                                        |                   |                  |                    |                                            |                     |

| R = Readable  | e bit                                                   | W = Writable                           | bit               | U = Unimple      | mented bit, rea    | d as '0'                                   |                     |

| -n = Value at |                                                         | '1' = Bit is se                        |                   | '0' = Bit is cle |                    | x = Bit is unkr                            | iown                |

|               |                                                         |                                        | •                 |                  |                    |                                            |                     |

| bit 15        | CON: Comp                                               | arator Enable b                        | bit               |                  |                    |                                            |                     |

|               |                                                         | ator is enabled                        |                   |                  |                    |                                            |                     |

|               |                                                         | ator is disabled                       |                   |                  |                    |                                            |                     |

| bit 14        | COE: Comp                                               | arator Output E                        | nable bit         |                  |                    |                                            |                     |

|               |                                                         | ator output is pr<br>ator output is in |                   | xOUT pin         |                    |                                            |                     |

| bit 13        | CPOL: Com                                               | parator Output                         | Polarity Select   | bit              |                    |                                            |                     |

|               |                                                         | ator output is in                      |                   |                  |                    |                                            |                     |

|               | 0 = Compara                                             | ator output is no                      | ot inverted       |                  |                    |                                            |                     |

| bit 12-10     | Unimpleme                                               | nted: Read as                          | '0'               |                  |                    |                                            |                     |

| bit 9         | CEVT: Com                                               | CEVT: Comparator Event bit             |                   |                  |                    |                                            |                     |

|               | interrup                                                | ts until the bit is                    | cleared           | POL<1:0> set     | tings occurred;    | disables future                            | triggers and        |

|               | •                                                       | ator event did i                       |                   |                  |                    |                                            |                     |

| bit 8         |                                                         | parator Output                         |                   |                  |                    |                                            |                     |

|               | $\frac{\text{VVnen CPOL}}{1 = \text{VIN} + > \text{V}}$ | <u>. = 0 (non-inver</u><br>/N-         | ted polarity):    |                  |                    |                                            |                     |

|               | 0 = VIN + < V                                           |                                        |                   |                  |                    |                                            |                     |

|               | When CPOL                                               | = 1 (inverted p                        | olarity):         |                  |                    |                                            |                     |

|               | 1 = VIN+ < V                                            |                                        |                   |                  |                    |                                            |                     |

|               | 0 = VIN + > V                                           | 'IN-                                   |                   |                  |                    |                                            |                     |

| bit 7-6       |                                                         | >: Trigger/Ever                        |                   | -                |                    |                                            |                     |

|               | 10 = Trigger                                            |                                        | generated only    |                  |                    | or output (while (<br>ne polarity selected |                     |

|               |                                                         | L = 1 (inverted)<br>-high transition   |                   | ator output.     |                    |                                            |                     |

|               |                                                         | L = 0 (non-inve<br>-low transition     |                   | ator output.     |                    |                                            |                     |

|               |                                                         | /event/interrupt<br>(while CEVT =      |                   | v on low-to-higl | n transition of th | e polarity selecte                         | ed comparato        |

|               |                                                         | L = 1 (inverted                        |                   | ator output.     |                    |                                            |                     |

|               |                                                         | L = 0 (non-inve<br>-high transition    |                   | ator output.     |                    |                                            |                     |

|               | 00 = Trigger                                            | /event/interrupt                       | generation is     | disabled         |                    |                                            |                     |

| Note 1: In    | puts that are se                                        | lected and not a                       | available will be | e tied to Vss. S | See the "Pin Dia   | agrams" sectior                            | n for available     |

Note 1: Inputs that are selected and not available will be tied to Vss. See the "Pin Diagrams" section for available inputs for each package.

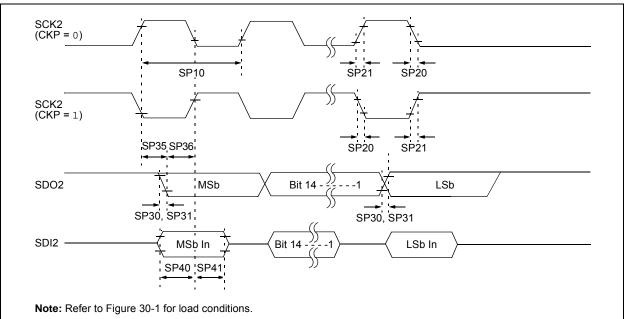

#### FIGURE 30-17: SPI2 MASTER MODE (FULL-DUPLEX, CKE = 0, CKP = x, SMP = 1) TIMING CHARACTERISTICS

## TABLE 30-36:SPI2 MASTER MODE (FULL-DUPLEX, CKE = 0, CKP = x, SMP = 1)TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                               | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                     |      |       |                             |  |

|--------------------|-----------------------|-----------------------------------------------|-------------------------------------------------------|---------------------|------|-------|-----------------------------|--|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>                 | Min.                                                  | Typ. <sup>(2)</sup> | Max. | Units | Conditions                  |  |

| SP10               | FscP                  | Maximum SCK2 Frequency                        |                                                       | —                   | 9    | MHz   | -40°C to +125°C<br>(Note 3) |  |

| SP20               | TscF                  | SCK2 Output Fall Time                         | _                                                     | —                   | _    | ns    | See Parameter DO32 (Note 4) |  |

| SP21               | TscR                  | SCK2 Output Rise Time                         | _                                                     | —                   | _    | ns    | See Parameter DO31 (Note 4) |  |

| SP30               | TdoF                  | SDO2 Data Output Fall Time                    | _                                                     | —                   | _    | ns    | See Parameter DO32 (Note 4) |  |

| SP31               | TdoR                  | SDO2 Data Output Rise Time                    | _                                                     | —                   | _    | ns    | See Parameter DO31 (Note 4) |  |

| SP35               | TscH2doV,<br>TscL2doV | SDO2 Data Output Valid after<br>SCK2 Edge     | _                                                     | 6                   | 20   | ns    |                             |  |

| SP36               | TdoV2scH,<br>TdoV2scL | SDO2 Data Output Setup to<br>First SCK2 Edge  | 30                                                    | —                   | _    | ns    |                             |  |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDI2 Data<br>Input to SCK2 Edge | 30                                                    | —                   | _    | ns    |                             |  |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDI2 Data Input to SCK2 Edge     | 30                                                    | —                   |      | ns    |                             |  |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The minimum clock period for SCK2 is 111 ns. The clock generated in Master mode must not violate this specification.

- 4: Assumes 50 pF load on all SPI2 pins.

| Section Name                    | Update Description                                                                                                                                                   |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Section 30.0 "Electrical        | These SPI2 Timing Requirements were updated:                                                                                                                         |

| Characteristics"<br>(Continued) | <ul> <li>Maximum value for Parameter SP10 and the minimum clock period value for<br/>SCKx in Note 3 (see Table 30-36, Table 30-37, and Table 30-38)</li> </ul>       |

|                                 | <ul> <li>Maximum value for Parameter SP70 and the minimum clock period value for<br/>SCKx in Note 3 (see Table 30-40 and Table 30-42)</li> </ul>                     |

|                                 | The Maximum Data Rate values were updated for the SPI2 Maximum Data/Clock<br>Rate Summary (see Table 30-43)                                                          |

|                                 | These SPI1 Timing Requirements were updated:                                                                                                                         |

|                                 | Maximum value for Parameters SP10 and the minimum clock period value for SCKx in Note 3 (see Table 30-44, Table 30-45, and Table 30-46)                              |

|                                 | Maximum value for Parameters SP70 and the minimum clock period value for SCKx in Note 3 (see Table 30-47 through Table 30-50)                                        |

|                                 | <ul> <li>Minimum value for Parameters SP40 and SP41 see Table 30-44 through<br/>Table 30-50)</li> </ul>                                                              |

|                                 | Updated all Typical values for the CTMU Current Source Specifications (see Table 30-55).                                                                             |

|                                 | Updated Note1, the Maximum value for Parameter AD06, the Minimum value for AD07, and the Typical values for AD09 in the ADC Module Specifications (see Table 30-56). |

|                                 | Added Note 1 to the ADC Module Specifications (12-bit Mode) (see Table 30-57).                                                                                       |

|                                 | Added Note 1 to the ADC Module Specifications (10-bit Mode) (see Table 30-58).                                                                                       |

|                                 | Updated the Minimum and Maximum values for Parameter AD21b in the 10-bit Mode ADC Module Specifications (see Table 30-58).                                           |

|                                 | Updated Note 2 in the ADC Conversion (12-bit Mode) Timing Requirements (see Table 30-59).                                                                            |

|                                 | Updated Note 1 in the ADC Conversion (10-bit Mode) Timing Requirements (see Table 30-60).                                                                            |

#### TABLE A-2: MAJOR SECTION UPDATES (CONTINUED)

#### TABLE A-5: MAJOR SECTION UPDATES (CONTINUED)

NOTES: