Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                  |                                                                                |

|--------------------------|--------------------------------------------------------------------------------|

| roduct Status            | Obsolete                                                                       |

| Core Processor           | PIC                                                                            |

| ore Size                 | 16-Bit                                                                         |

| eed                      | 60 MIPs                                                                        |

| nnectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| eripherals               | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| umber of I/O             | 35                                                                             |

| ogram Memory Size        | 32KB (10.7K x 24)                                                              |

| ogram Memory Type        | FLASH                                                                          |

| PROM Size                | -                                                                              |

| M Size                   | 2K x 16                                                                        |

| ltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| ta Converters            | A/D 9x10b/12b                                                                  |

| cillator Type            | Internal                                                                       |

| erating Temperature      | -40°C ~ 125°C (TA)                                                             |

| unting Type              | Surface Mount                                                                  |

| ckage / Case             | 44-TQFP                                                                        |

| pplier Device Package    | 44-TQFP (10x10)                                                                |

| rchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep32gp204t-e-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

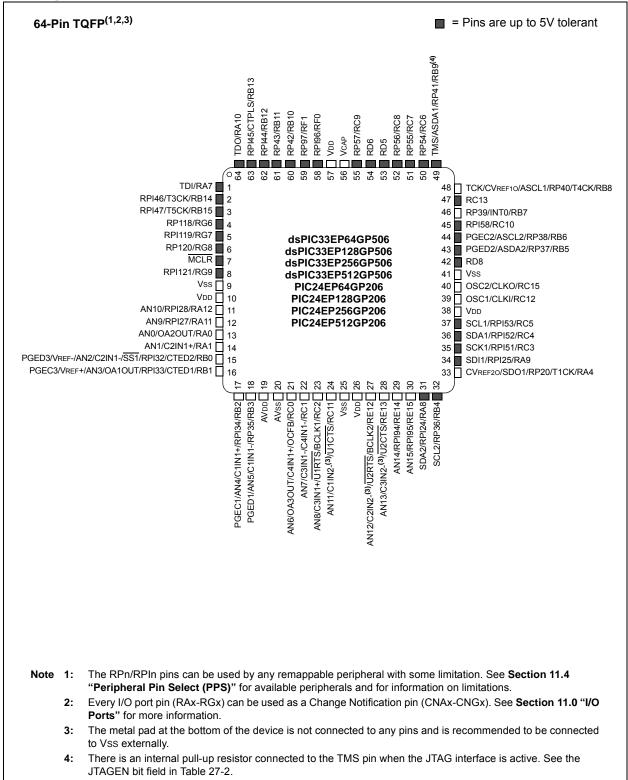

# Pin Diagrams (Continued)

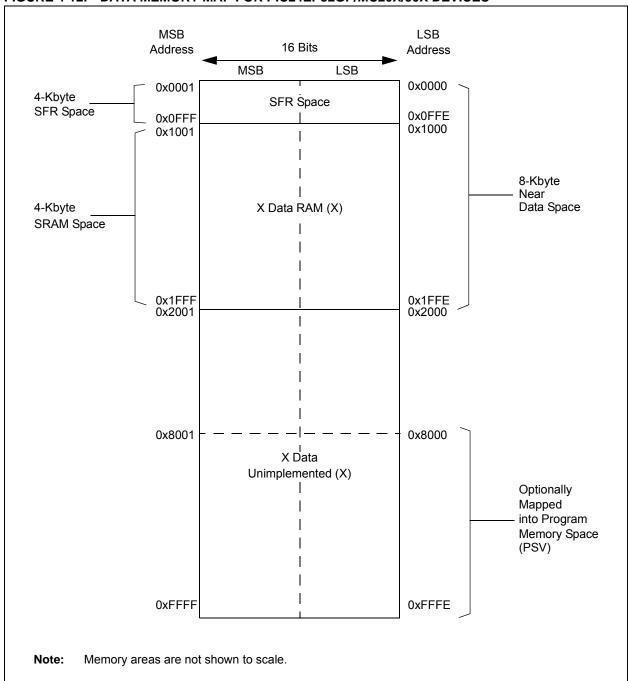

FIGURE 4-12: DATA MEMORY MAP FOR PIC24EP32GP/MC20X/50X DEVICES

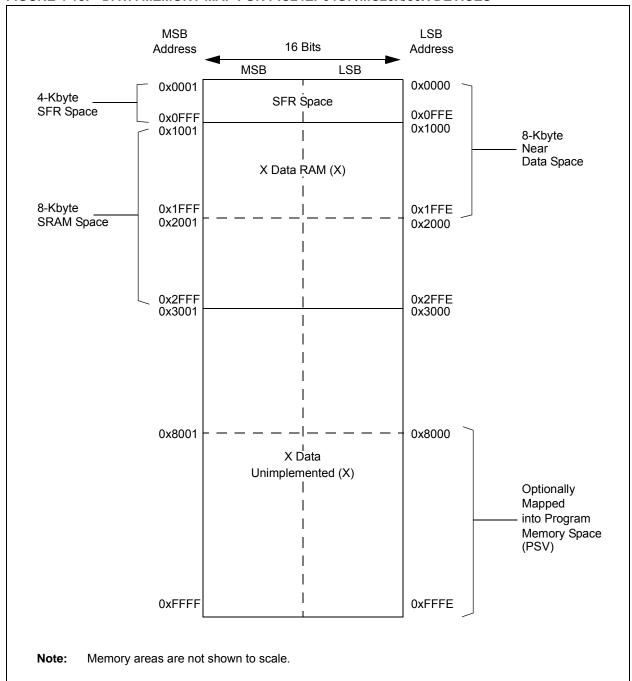

FIGURE 4-13: DATA MEMORY MAP FOR PIC24EP64GP/MC20X/50X DEVICES

TABLE 4-39: PMD REGISTER MAP FOR dsPIC33EPXXXGP50X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | _      | _     | _     | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | _      | C1MD   | AD1MD | 0000          |

| PMD2         | 0762  | -      | _      | -      | -      | IC4MD  | IC3MD  | IC2MD | IC1MD | _      | -     | _     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  | -      | _      | -      | -      | -      | CMPMD  | _     | _     | CRCMD  | -     | _     | _      | _      | _      | I2C2MD | _     | 0000          |

| PMD4         | 0766  | -      | _      | -      | -      | -      | _      | _     | _     | _      | -     | _     | _      | REFOMD | CTMUMD | _      | _     | 0000          |

| PMD6         | 076A  | -      | _      | -      | -      | -      | _      | _     | _     | _      | -     | _     | _      | _      | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |       |       |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  |        |        |        |        |        |        |       |       |        |       |       | DMA1MD | PTGMD  |        |        |       | 0000          |

| PIVID7       | 0760  | _      | _      | _      |        |        |        | _     | _     | _      |       |       | DMA2MD | PIGND  | _      | _      |       | 0000          |

|              |       |        |        |        |        |        |        |       |       |        |       |       | DMA3MD |        |        |        |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-40: PMD REGISTER MAP FOR dsPIC33EPXXXMC50X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | QEI1MD | PWMMD  | _      | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | _      | C1MD   | AD1MD | 0000          |

| PMD2         | 0762  | 1      | _      | -      | _      | IC4MD  | IC3MD  | IC2MD  | IC1MD  | -      | _     | _     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  | 1      | _      | -      | _      | _      | CMPMD  | _      | _      | CRCMD  | _     | _     | _      | _      | _      | I2C2MD | _     | 0000          |

| PMD4         | 0766  | 1      | _      | -      | _      | _      | _      | _      | _      | -      | _     | _     | _      | REFOMD | CTMUMD | _      | _     | 0000          |

| PMD6         | 076A  | -      | _      | ı      | _      | ı      | PWM3MD | PWM2MD | PWM1MD | _      | ı     | ı     | _      | _      | -      | -      | ı     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  |        |        |        |        |        |        |        |        |        |       |       | DMA1MD | PTGMD  | _      |        | _     | 0000          |

| FINIDI       | 0760  | _      | _      | _      | _      | _      | _      | _      | _      | _      | _     | _     | DMA2MD | FIGNID | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA3MD |        |        |        |       |               |

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## 5.2 RTSP Operation

RTSP allows the user application to erase a single page of memory and to program two instruction words at a time. See the General Purpose and Motor Control Family tables (Table 1 and Table 2, respectively) for the page sizes of each device.

For more information on erasing and programming Flash memory, refer to "Flash Programming" (DS70609) in the "dsPIC33/PIC24 Family Reference Manual".

# 5.3 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. The processor stalls (waits) until the programming operation is finished.

For erase and program times, refer to Parameters D137a and D137b (Page Erase Time), and D138a and D138b (Word Write Cycle Time) in Table 30-14 in **Section 30.0 "Electrical Characteristics"**.

Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

# 5.3.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

Programmers can program two adjacent words (24 bits x 2) of program Flash memory at a time on every other word address boundary (0x000002, 0x000006, 0x000000A, etc.). To do this, it is necessary to erase the page that contains the desired address of the location the user wants to change.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user application must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS

Refer to **Flash Programming**" (DS70609) in the "dsPIC33/PIC24 Family Reference Manual" for details and codes examples on programming using RTSP.

## 5.4 Flash Memory Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser:

http://www.microchip.com/wwwproducts/

Devices.aspx?dDocName=en555464

#### 5.4.1 KEY RESOURCES

- "Flash Programming" (DS70609) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- · Development Tools

## 5.5 Control Registers

Four SFRs are used to erase and write the program Flash memory: NVMCON, NVMKEY, NVMADRH and NVMADRL.

The NVMCON register (Register 5-1) enables and initiates Flash memory erase and write operations.

NVMKEY (Register 5-4) is a write-only register that is used for write protection. To start a programming or erase sequence, the user application must consecutively write 0x55 and 0xAA to the NVMKEY register.

There are two NVM Address registers: NVMADRH and NVMADRL. These two registers, when concatenated, form the 24-bit Effective Address (EA) of the selected word for programming operations or the selected page for erase operations.

The NVMADRH register is used to hold the upper 8 bits of the EA, while the NVMADRL register is used to hold the lower 16 bits of the EA.

## 6.1 Reset Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note:

In the event you are not able to access the product page using the link above, enter this URL in your browser:

http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en555464

#### 6.1.1 KEY RESOURCES

- "Reset" (DS70602) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- · Development Tools

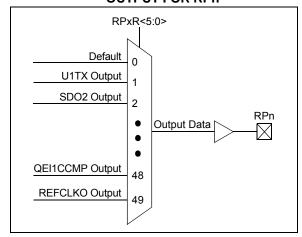

## 11.4.4.2 Output Mapping

In contrast to inputs, the outputs of the Peripheral Pin Select options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPORx registers are used to control output mapping. Like the RPINRx registers, each register contains sets of 6-bit fields, with each set associated with one RPn pin (see Register 11-18 through Register 11-27). The value of the bit field corresponds to one of the peripherals and that peripheral's output is mapped to the pin (see Table 11-3 and Figure 11-3).

A null output is associated with the output register Reset value of '0'. This is done to ensure that remappable outputs remain disconnected from all output pins by default.

FIGURE 11-3: MULTIPLEXING REMAPPABLE OUTPUT FOR RPn

# 11.4.4.3 Mapping Limitations

The control schema of the peripheral select pins is not limited to a small range of fixed peripheral configurations. There are no mutual or hardware-enforced lockouts between any of the peripheral mapping SFRs. Literally any combination of peripheral mappings across any or all of the RPn pins is possible. This includes both many-to-one and one-to-many mappings of peripheral inputs and outputs to pins. While such mappings may be technically possible from a configuration point of view, they may not be supportable from an electrical point of view.

TABLE 11-3: OUTPUT SELECTION FOR REMAPPABLE PINS (RPn)

| Function                | RPxR<5:0> | Output Name                                   |

|-------------------------|-----------|-----------------------------------------------|

| Default PORT            | 000000    | RPn tied to Default Pin                       |

| U1TX                    | 000001    | RPn tied to UART1 Transmit                    |

| U2TX                    | 000011    | RPn tied to UART2 Transmit                    |

| SDO2                    | 001000    | RPn tied to SPI2 Data Output                  |

| SCK2                    | 001001    | RPn tied to SPI2 Clock Output                 |

| SS2                     | 001010    | RPn tied to SPI2 Slave Select                 |

| C1TX <sup>(2)</sup>     | 001110    | RPn tied to CAN1 Transmit                     |

| OC1                     | 010000    | RPn tied to Output Compare 1 Output           |

| OC2                     | 010001    | RPn tied to Output Compare 2 Output           |

| OC3                     | 010010    | RPn tied to Output Compare 3 Output           |

| OC4                     | 010011    | RPn tied to Output Compare 4 Output           |

| C1OUT                   | 011000    | RPn tied to Comparator Output 1               |

| C2OUT                   | 011001    | RPn tied to Comparator Output 2               |

| C3OUT                   | 011010    | RPn tied to Comparator Output 3               |

| SYNCO1 <sup>(1)</sup>   | 101101    | RPn tied to PWM Primary Time Base Sync Output |

| QEI1CCMP <sup>(1)</sup> | 101111    | RPn tied to QEI 1 Counter Comparator Output   |

| REFCLKO                 | 110001    | RPn tied to Reference Clock Output            |

| C4OUT                   | 110010    | RPn tied to Comparator Output 4               |

Note 1: This function is available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This function is available in dsPIC33EPXXXGP/MC50X devices only.

# 12.2 Timer1 Control Register

#### REGISTER 12-1: T1CON: TIMER1 CONTROL REGISTER

| R/W-0              | U-0 | R/W-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------------------|-----|-------|-----|-----|-----|-----|-------|

| TON <sup>(1)</sup> | _   | TSIDL | _   | _   | _   | _   | _     |

| bit 15             |     |       |     |     |     |     | bit 8 |

| U-0   | R/W-0 | R/W-0  | R/W-0  | U-0 | R/W-0                | R/W-0              | U-0   |

|-------|-------|--------|--------|-----|----------------------|--------------------|-------|

| _     | TGATE | TCKPS1 | TCKPS0 | _   | TSYNC <sup>(1)</sup> | TCS <sup>(1)</sup> | _     |

| bit 7 |       |        |        |     |                      |                    | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **TON:** Timer1 On bit<sup>(1)</sup>

1 = Starts 16-bit Timer1

0 = Stops 16-bit Timer1

bit 14 **Unimplemented:** Read as '0'

bit 13 TSIDL: Timer1 Stop in Idle Mode bit

1 = Discontinues module operation when device enters Idle mode

0 = Continues module operation in Idle mode

bit 12-7 Unimplemented: Read as '0'

bit 6 TGATE: Timer1 Gated Time Accumulation Enable bit

When TCS = 1: This bit is ignored.

When TCS = 0:

1 = Gated time accumulation is enabled0 = Gated time accumulation is disabled

bit 5-4 TCKPS<1:0>: Timer1 Input Clock Prescale Select bits

11 = 1:256

10 = 1:64

01 = 1:8

00 = 1:1

bit 3 Unimplemented: Read as '0'

bit 2 **TSYNC:** Timer1 External Clock Input Synchronization Select bit<sup>(1)</sup>

When TCS = 1:

1 = Synchronizes external clock input

0 = Does not synchronize external clock input

When TCS = 0:

This bit is ignored.

bit 1 TCS: Timer1 Clock Source Select bit<sup>(1)</sup>

1 = External clock is from pin, T1CK (on the rising edge)

0 = Internal clock (FP)

bit 0 **Unimplemented:** Read as '0'

**Note 1:** When Timer1 is enabled in External Synchronous Counter mode (TCS = 1, TSYNC = 1, TON = 1), any attempts by user software to write to the TMR1 register are ignored.

## REGISTER 16-5: CHOP: PWMx CHOP CLOCK GENERATOR REGISTER

| R/W-0    | U-0 | U-0 | U-0 | U-0   | U-0 | R/W-0 | R/W-0   |

|----------|-----|-----|-----|-------|-----|-------|---------|

| CHPCLKEN | _   | _   | _   | _     | _   | CHOPC | LK<9:8> |

| bit 15   |     |     |     | bit 8 |     |       |         |

| R/W-0 | R/W-0        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |  |

|-------|--------------|-------|-------|-------|-------|-------|-------|--|--|--|--|

|       | CHOPCLK<7:0> |       |       |       |       |       |       |  |  |  |  |

| bit 7 |              |       |       |       |       |       |       |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 CHPCLKEN: Enable Chop Clock Generator bit

1 = Chop clock generator is enabled0 = Chop clock generator is disabled

bit 14-10 **Unimplemented:** Read as '0'

bit 9-0 CHOPCLK<9:0>: Chop Clock Divider bits

The frequency of the chop clock signal is given by the following expression:

Chop Frequency = (FP/PCLKDIV<2:0)/(CHOPCLK<9:0> + 1)

#### REGISTER 16-6: MDC: PWMx MASTER DUTY CYCLE REGISTER

| R/W-0  | R/W-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |  |

|--------|-----------|-------|-------|-------|-------|-------|-------|--|--|--|--|

|        | MDC<15:8> |       |       |       |       |       |       |  |  |  |  |

| bit 15 |           |       |       |       |       |       |       |  |  |  |  |

| R/W-0       | R/W-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |  |  |

|-------------|----------|-------|-------|-------|-------|-------|-------|--|--|--|--|--|

|             | MDC<7:0> |       |       |       |       |       |       |  |  |  |  |  |

| bit 7 bit 0 |          |       |       |       |       |       |       |  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 MDC<15:0>: PWMx Master Duty Cycle Value bits

#### REGISTER 16-14: TRIGX: PWMx PRIMARY TRIGGER COMPARE VALUE REGISTER

| R/W-0  | R/W-0        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |  |  |

|--------|--------------|-------|-------|-------|-------|-------|-------|--|--|--|--|--|

|        | TRGCMP<15:8> |       |       |       |       |       |       |  |  |  |  |  |

| bit 15 | bit 15 bit 8 |       |       |       |       |       |       |  |  |  |  |  |

| R/W-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|-----------|-------|-------|-------|---------|-------|-------|-------|--|--|--|

|           |       |       | TRGCM | 1P<7:0> |       |       |       |  |  |  |

| bit 7 bit |       |       |       |         |       |       |       |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

## bit 15-0 TRGCMP<15:0>: Trigger Control Value bits

When the primary PWMx functions in local time base, this register contains the compare values that can trigger the ADC module.

# REGISTER 16-15: FCLCONx: PWMx FAULT CURRENT-LIMIT CONTROL REGISTER<sup>(1)</sup>

```

bit 7-3

FLTSRC<4:0>: Fault Control Signal Source Select for PWM Generator # bits

11111 = Fault 32 (default)

11110 = Reserved

01100 = Reserved

01011 = Comparator 4

01010 = Op Amp/Comparator 3

01001 = Op Amp/Comparator 2

01000 = Op Amp/Comparator 1

00111 = Reserved

00110 = Reserved

00101 = Reserved

00100 = Reserved

00011 = Fault 4

00010 = Fault 3

00001 = Fault 2

00000 = Fault 1

bit 2

FLTPOL: Fault Polarity for PWM Generator # bit<sup>(2)</sup>

1 = The selected Fault source is active-low

0 = The selected Fault source is active-high

bit 1-0

FLTMOD<1:0>: Fault Mode for PWM Generator # bits

11 = Fault input is disabled

10 = Reserved

01 = The selected Fault source forces PWMxH, PWMxL pins to FLTDAT values (cycle)

00 = The selected Fault source forces PWMxH, PWMxL pins to FLTDAT values (latched condition)

```

- Note 1: If the PWMLOCK Configuration bit (FOSCSEL<6>) is a '1', the IOCONx register can only be written after the unlock sequence has been executed.

- 2: These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

# 18.3 SPIx Control Registers

#### REGISTER 18-1: SPIXSTAT: SPIX STATUS AND CONTROL REGISTER

| R/W-0  | U-0 | R/W-0   | U-0 | U-0 | R/W-0 | R/W-0       | R/W-0 |

|--------|-----|---------|-----|-----|-------|-------------|-------|

| SPIEN  | _   | SPISIDL | _   | _   |       | SPIBEC<2:0> | 1     |

| bit 15 |     |         |     |     |       |             | bit 8 |

| R/W-0 | R/C-0, HS | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R-0, HS, HC | R-0, HS, HC |

|-------|-----------|--------|--------|--------|--------|-------------|-------------|

| SRMPT | SPIROV    | SRXMPT | SISEL2 | SISEL1 | SISEL0 | SPITBF      | SPIRBF      |

| bit 7 |           |        |        |        |        | •           | bit 0       |

| Legend:           | C = Clearable bit | HS = Hardware Settable bit | t HC = Hardware Clearable bit |

|-------------------|-------------------|----------------------------|-------------------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, re  | ad as '0'                     |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared       | x = Bit is unknown            |

bit 15 SPIEN: SPIx Enable bit

1 = Enables the module and configures SCKx, SDOx, SDIx and  $\overline{SSx}$  as serial port pins

0 = Disables the module

bit 14 **Unimplemented:** Read as '0'

bit 13 SPISIDL: SPIx Stop in Idle Mode bit

1 = Discontinues the module operation when device enters Idle mode

0 = Continues the module operation in Idle mode

bit 12-11 **Unimplemented:** Read as '0'

bit 10-8 SPIBEC<2:0>: SPIx Buffer Element Count bits (valid in Enhanced Buffer mode)

Master mode:

Number of SPIx transfers that are pending.

Slave mode:

Number of SPIx transfers that are unread.

bit 7 SRMPT: SPIx Shift Register (SPIxSR) Empty bit (valid in Enhanced Buffer mode)

1 = SPIx Shift register is empty and Ready-To-Send or receive the data

0 = SPIx Shift register is not empty

bit 6 SPIROV: SPIx Receive Overflow Flag bit

1 = A new byte/word is completely received and discarded; the user application has not read the previous data in the SPIxBUF register

0 = No overflow has occurred

bit 5 SRXMPT: SPIx Receive FIFO Empty bit (valid in Enhanced Buffer mode)

1 = RX FIFO is empty

0 = RX FIFO is not empty

bit 4-2 SISEL<2:0>: SPIx Buffer Interrupt Mode bits (valid in Enhanced Buffer mode)

111 = Interrupt when the SPIx transmit buffer is full (SPITBF bit is set)

110 = Interrupt when last bit is shifted into SPIxSR and as a result, the TX FIFO is empty

101 = Interrupt when the last bit is shifted out of SPIxSR and the transmit is complete

100 = Interrupt when one data is shifted into the SPIxSR and as a result, the TX FIFO has one open memory location

011 = Interrupt when the SPIx receive buffer is full (SPIRBF bit is set)

010 = Interrupt when the SPIx receive buffer is 3/4 or more full

001 = Interrupt when data is available in the receive buffer (SRMPT bit is set)

000 = Interrupt when the last data in the receive buffer is read and as a result, the buffer is empty (SRXMPT bit is set)

## REGISTER 21-10: CxCFG2: ECANx BAUD RATE CONFIGURATION REGISTER 2

| U-0    | R/W-x  | U-0                | U-0 | U-0     | R/W-x   | R/W-x   | R/W-x |

|--------|--------|--------------------|-----|---------|---------|---------|-------|

| _      | WAKFIL | /AKFIL — — SEG2PH2 |     | SEG2PH2 | SEG2PH1 | SEG2PH0 |       |

| bit 15 |        |                    |     |         |         |         | bit 8 |

| R/W-x    | R/W-x | R/W-x   | R/W-x   | R/W-x   | R/W-x  | R/W-x  | R/W-x  |

|----------|-------|---------|---------|---------|--------|--------|--------|

| SEG2PHTS | SAM   | SEG1PH2 | SEG1PH1 | SEG1PH0 | PRSEG2 | PRSEG1 | PRSEG0 |

| bit 7    |       |         |         |         |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 Unimplemented: Read as '0'

bit 14 WAKFIL: Select CAN Bus Line Filter for Wake-up bit

1 = Uses CAN bus line filter for wake-up

0 = CAN bus line filter is not used for wake-up

bit 13-11 **Unimplemented:** Read as '0'

bit 10-8 **SEG2PH<2:0>:** Phase Segment 2 bits

111 = Length is 8 x TQ

•

•

000 = Length is 1 x TQ

bit 7 SEG2PHTS: Phase Segment 2 Time Select bit

1 = Freely programmable

0 = Maximum of SEG1PHx bits or Information Processing Time (IPT), whichever is greater

bit 6 SAM: Sample of the CAN Bus Line bit

1 = Bus line is sampled three times at the sample point

0 = Bus line is sampled once at the sample point

bit 5-3 **SEG1PH<2:0>:** Phase Segment 1 bits

111 = Length is 8 x TQ

.

000 = Length is 1 x TQ

bit 2-0 PRSEG<2:0>: Propagation Time Segment bits

111 = Length is 8 x TQ

•

•

•

000 = Length is  $1 \times TQ$

#### REGISTER 22-2: CTMUCON2: CTMU CONTROL REGISTER 2

| R/W-0   | R/W-0   | R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0    |

|---------|---------|----------|----------|----------|----------|----------|----------|

| EDG1MOD | EDG1POL | EDG1SEL3 | EDG1SEL2 | EDG1SEL1 | EDG1SEL0 | EDG2STAT | EDG1STAT |

| bit 15  |         |          |          |          |          |          | bit 8    |

| R/W-0   | R/W-0   | R/W-0    | R/W-0    | R/W-0    | R/W-0    | U-0 | U-0   |

|---------|---------|----------|----------|----------|----------|-----|-------|

| EDG2MOD | EDG2POL | EDG2SEL3 | EDG2SEL2 | EDG2SEL1 | EDG2SEL0 | _   | _     |

| bit 7   |         |          |          |          |          |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 EDG1MOD: Edge 1 Edge Sampling Mode Selection bit

1 = Edge 1 is edge-sensitive 0 = Edge 1 is level-sensitive

bit 14 EDG1POL: Edge 1 Polarity Select bit

1 = Edge 1 is programmed for a positive edge response 0 = Edge 1 is programmed for a negative edge response

bit 13-10 **EDG1SEL<3:0>:** Edge 1 Source Select bits

1xxx = Reserved 01xx = Reserved 0011 = CTED1 pin 0010 = CTED2 pin 0001 = OC1 module 0000 = Timer1 module

bit 9 EDG2STAT: Edge 2 Status bit

Indicates the status of Edge 2 and can be written to control the edge source.

1 = Edge 2 has occurred 0 = Edge 2 has not occurred

bit 8 **EDG1STAT:** Edge 1 Status bit

Indicates the status of Edge 1 and can be written to control the edge source.

1 = Edge 1 has occurred 0 = Edge 1 has not occurred

bit 7 **EDG2MOD:** Edge 2 Edge Sampling Mode Selection bit

1 = Edge 2 is edge-sensitive0 = Edge 2 is level-sensitive

bit 6 **EDG2POL:** Edge 2 Polarity Select bit

1 = Edge 2 is programmed for a positive edge response 0 = Edge 2 is programmed for a negative edge response

bit 5-2 **EDG2SEL<3:0>:** Edge 2 Source Select bits

1111 = Reserved 01xx = Reserved 0100 = CMP1 module 0011 = CTED2 pin 0010 = CTED1 pin 0001 = OC1 module 0000 = IC1 module

bit 1-0 **Unimplemented:** Read as '0'

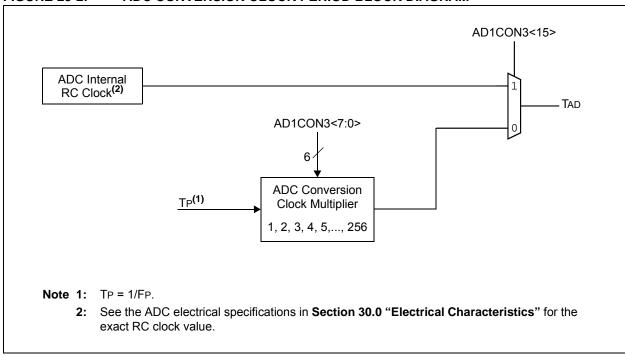

FIGURE 23-2: ADC CONVERSION CLOCK PERIOD BLOCK DIAGRAM

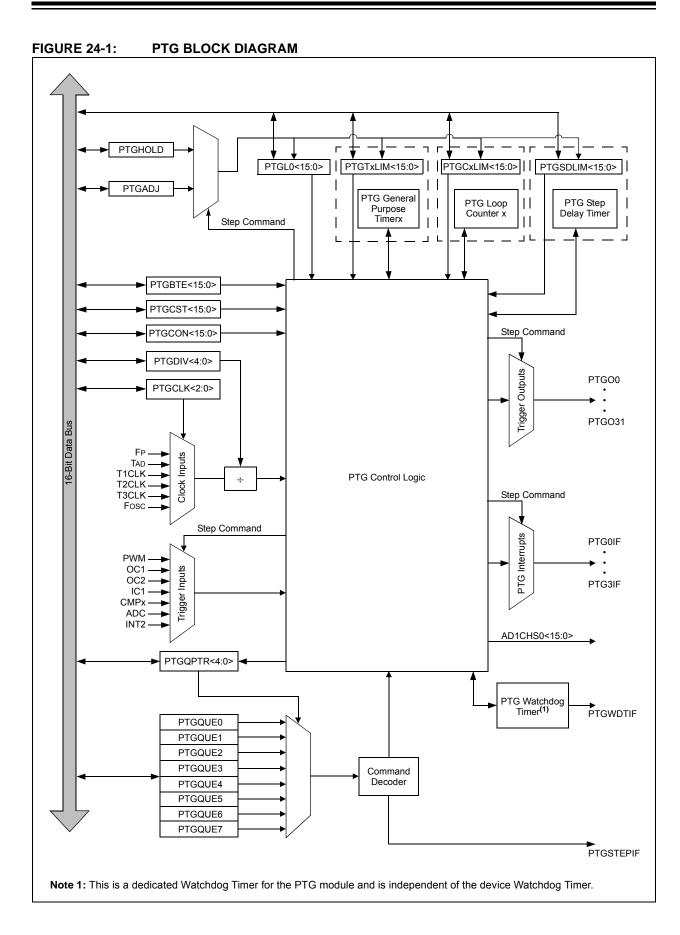

TABLE 24-1: PTG STEP COMMAND FORMAT (CONTINUED)

| bit 3-0 | Step<br>Command        | OPTION<3:0> | Option Description                               |

|---------|------------------------|-------------|--------------------------------------------------|

|         | PTGWHI(1)              | 0000        | PWM Special Event Trigger. (3)                   |

|         | or (1)                 | 0001        | PWM master time base synchronization output. (3) |

|         | PTGWLO(1)              | 0010        | PWM1 interrupt. <sup>(3)</sup>                   |

|         |                        | 0011        | PWM2 interrupt. <sup>(3)</sup>                   |

|         |                        | 0100        | PWM3 interrupt. <sup>(3)</sup>                   |

|         |                        | 0101        | Reserved.                                        |

|         |                        | 0110        | Reserved.                                        |

|         |                        | 0111        | OC1 Trigger event.                               |

|         |                        | 1000        | OC2 Trigger event.                               |

|         |                        | 1001        | IC1 Trigger event.                               |

|         |                        | 1010        | CMP1 Trigger event.                              |

|         |                        | 1011        | CMP2 Trigger event.                              |

|         |                        | 1100        | CMP3 Trigger event.                              |

|         |                        | 1101        | CMP4 Trigger event.                              |

|         |                        | 1110        | ADC conversion done interrupt.                   |

|         |                        | 1111        | INT2 external interrupt.                         |

|         | PTGIRQ <sup>(1)</sup>  | 0000        | Generate PTG Interrupt 0.                        |

|         |                        | 0001        | Generate PTG Interrupt 1.                        |

|         |                        | 0010        | Generate PTG Interrupt 2.                        |

|         |                        | 0011        | Generate PTG Interrupt 3.                        |

|         |                        | 0100        | Reserved.                                        |

|         |                        | •           | •                                                |

|         |                        | •           | •                                                |

|         |                        | •           | •                                                |

|         | (2)                    | 1111        | Reserved.                                        |

|         | PTGTRIG <sup>(2)</sup> | 00000       | PTGO0.                                           |

|         |                        | 00001       | PTGO1.                                           |

|         | •                      |             | •                                                |

|         |                        | •           | •                                                |

|         |                        | •           | •                                                |

|         |                        | 11110       | PTGO30.                                          |

|         |                        | 11111       | PTGO31.                                          |

Note 1: All reserved commands or options will execute but have no effect (i.e., execute as a NOP instruction).

**3:** This feature is only available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

<sup>2:</sup> Refer to Table 24-2 for the trigger output descriptions.

| dsPIC33EPXXXGP | '50X, dsPIC33EPX | XXMC20X/50X A | AND PIC24EPXX | XGP/MC20X |

|----------------|------------------|---------------|---------------|-----------|

| NOTES:         |                  |               |               |           |

|                |                  |               |               |           |

|                |                  |               |               |           |

|                |                  |               |               |           |

|                |                  |               |               |           |

|                |                  |               |               |           |

|                |                  |               |               |           |

|                |                  |               |               |           |

|                |                  |               |               |           |

|                |                  |               |               |           |

|                |                  |               |               |           |

|                |                  |               |               |           |

|                |                  |               |               |           |

|                |                  |               |               |           |

# TABLE 30-4: DC TEMPERATURE AND VOLTAGE SPECIFICATIONS

| DC CHARACTERISTICS |        |                                                                  | Standard Operating Conditions (see Note 1): 3.0V to 3.6V (unless otherwise stated)<br>Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |   |     |      |                 |  |

|--------------------|--------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|------|-----------------|--|

| Param<br>No.       | Symbol | Characteristic                                                   | Min. Typ. Max. Units Conditions                                                                                                                                                                                                                                  |   |     |      |                 |  |

| Operating Voltage  |        |                                                                  |                                                                                                                                                                                                                                                                  |   |     |      |                 |  |

| DC10               | VDD    | Supply Voltage                                                   | 3.0                                                                                                                                                                                                                                                              | _ | 3.6 | V    |                 |  |

| DC16               | VPOR   | VDD Start Voltage<br>to Ensure Internal<br>Power-on Reset Signal | _                                                                                                                                                                                                                                                                | _ | Vss | V    |                 |  |

| DC17               | SVDD   | VDD Rise Rate<br>to Ensure Internal<br>Power-on Reset Signal     | 0.03                                                                                                                                                                                                                                                             | _ | _   | V/ms | 0V-1V in 100 ms |  |

Note 1: Device is functional at VBORMIN < VDD < VDDMIN. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Device functionality is tested but not characterized. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

# TABLE 30-5: FILTER CAPACITOR (CEFC) SPECIFICATIONS

|              | Standard Operating Conditions (unless otherwise stated):  Operating temperature $-40^{\circ}\text{C} \leq \text{TA} \leq +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \leq \text{TA} \leq +125^{\circ}\text{C}$ for Extended |                                                |     |    |  |    |                                                       |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|-----|----|--|----|-------------------------------------------------------|--|

| Param<br>No. | Symbol   Characteristics   Min   Tyn   Max   Units   Comments                                                                                                                                                                            |                                                |     |    |  |    | Comments                                              |  |

|              | CEFC                                                                                                                                                                                                                                     | External Filter Capacitor Value <sup>(1)</sup> | 4.7 | 10 |  | μF | Capacitor must have a low series resistance (< 1 Ohm) |  |

**Note 1:** Typical VCAP voltage = 1.8 volts when VDD ≥ VDDMIN.

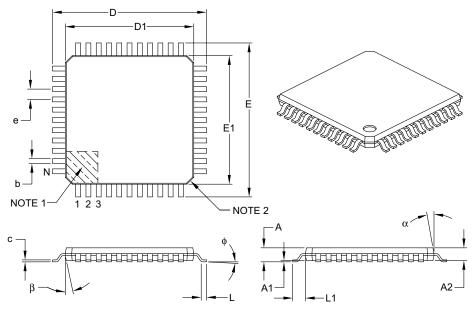

# 44-Lead Plastic Thin Quad Flatpack (PT) – 10x10x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units     |          | NOM   MAX   44   0.80 BSC   -   1.20   1.00   1.05   -   0.15   0.60   0.75   1.00 BEE |      |  |

|--------------------------|-----------|----------|----------------------------------------------------------------------------------------|------|--|

| Dimensi                  | on Limits | MIN      | NOM                                                                                    | MAX  |  |

| Number of Leads          | N         |          | 44                                                                                     |      |  |

| Lead Pitch               | е         |          | 0.80 BSC                                                                               |      |  |

| Overall Height           | Α         | _        | _                                                                                      | 1.20 |  |

| Molded Package Thickness | A2        | 0.95     | 1.00                                                                                   | 1.05 |  |

| Standoff                 | A1        | 0.05     | _                                                                                      | 0.15 |  |

| Foot Length              | L         | 0.45     | 0.60                                                                                   | 0.75 |  |

| Footprint                | L1        | 1.00 REF |                                                                                        |      |  |

| Foot Angle               | ф         | 0°       | 3.5°                                                                                   | 7°   |  |

| Overall Width            | E         |          | 12.00 BSC                                                                              |      |  |

| Overall Length           | D         |          | 12.00 BSC                                                                              |      |  |

| Molded Package Width     | E1        |          | 10.00 BSC                                                                              |      |  |

| Molded Package Length    | D1        |          | 10.00 BSC                                                                              |      |  |

| Lead Thickness           | С         | 0.09     | _                                                                                      | 0.20 |  |

| Lead Width               | b         | 0.30     | 0.37                                                                                   | 0.45 |  |

| Mold Draft Angle Top     | α         | 11°      | 12°                                                                                    | 13°  |  |

| Mold Draft Angle Bottom  | β         | 11°      | 12°                                                                                    | 13°  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Chamfers at corners are optional; size may vary.

- 3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-076B