Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 60 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 35                                                                             |

| Program Memory Size        | 32KB (10.7K x 24)                                                              |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 2K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 9x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-VFTLA Exposed Pad                                                           |

| Supplier Device Package    | 44-VTLA (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep32gp204t-e-tl |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

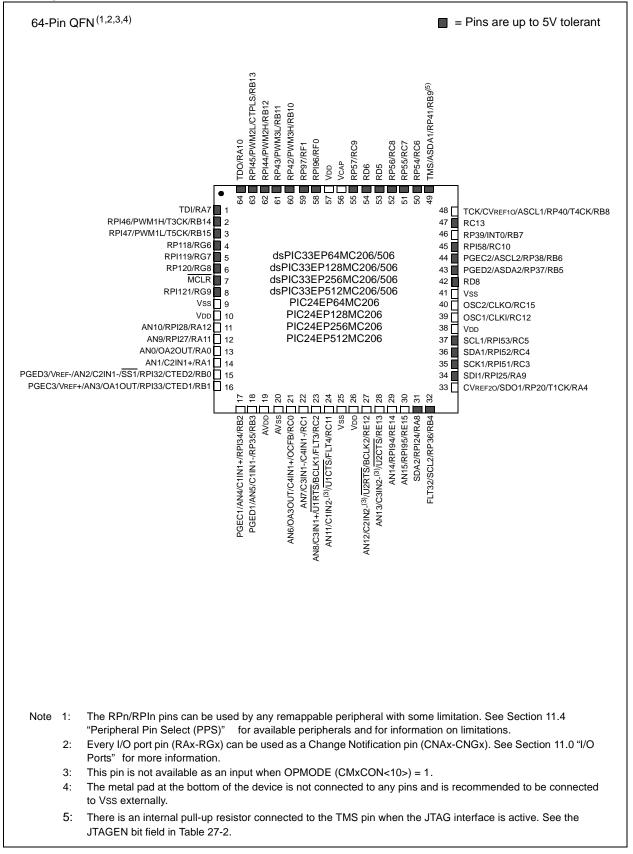

### Pin Diagrams (Continued)

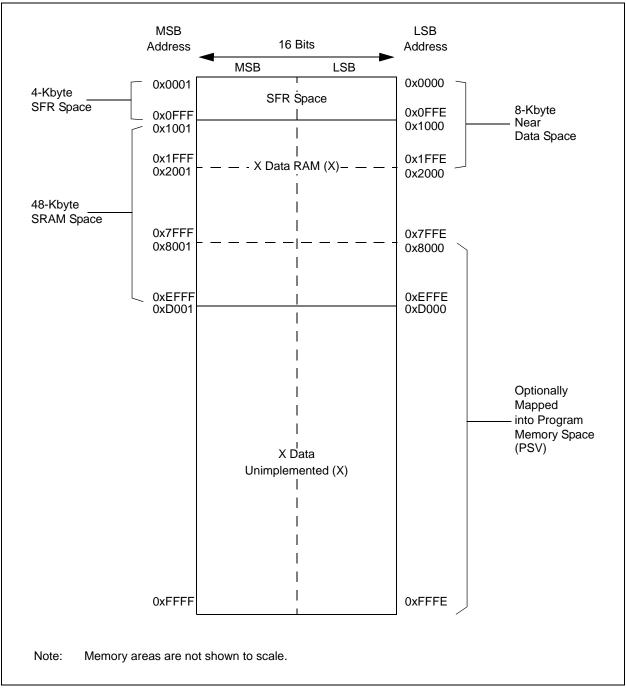

## 4.0 MEMORY ORGANIZATION

Note: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXGP50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Program Memory" (DS70613) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X architecture features separate program and data memory spaces, and buses. This architecture also allows the direct access of program memory from the Data Space (DS) during code execution.

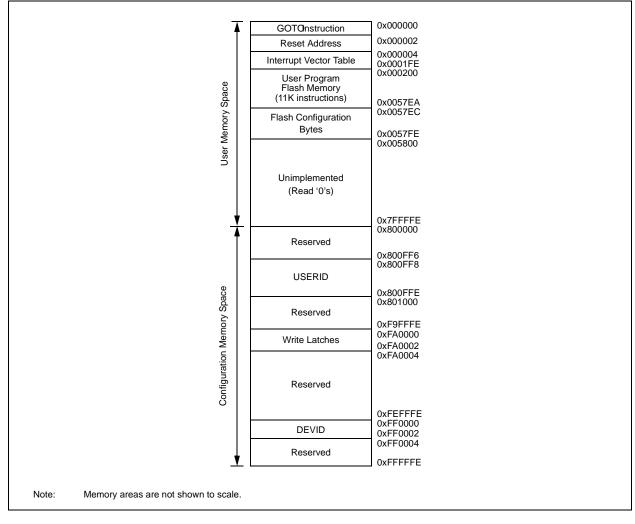

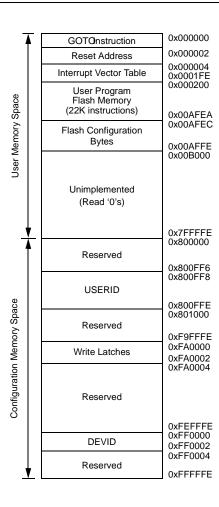

#### 4.1 Program Address Space

The program address memory space of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices is 4M instructions. The space is addressable by a 24-bit value derived either from the 23-bit PC during program execution, or from table operation or Data Space remapping, as described in Section 4.8 "Interfacing Program and Data Memory Spaces" .

User application access to the program memory space is restricted to the lower half of the address range (0x000000 to 0x7FFFF). The exception is the use of TBLRD operations, which use TBLPAG<7> to read Device ID sections of the configuration memory space.

The program memory maps, which are presented by device family and memory size, are shown in Figure 4-1 through Figure 4-5.

# FIGURE 4-1: PROGRAM MEMORY MAP FOR dsPI C33EP32GP50X, dsPIC33EP32MC20X/50X AND PIC24EP32GP/MC20X DEVICES

# FIGURE 4-2: PROGRAM MEMORY MAP FOR dsPI C33EP64GP50X, dsPIC33EP64MC20X/50X AND PIC24EP64GP/MC20X DEVICES

Note: Memory areas are not shown to scale.

#### FIGURE 4-16: DATA MEMORY MAP FOR PIC24EP512GP/MC20X/50X DEVICES

# TABLE 4-27: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EPXXXGP/MC204/504 AND PIC24EPXXXGP/MC204 DEVICES ONLY DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12     | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7      | Bit        | : 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2      | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|------------|--------|--------|-------|-------|------------|------------|-----|-------|-------|-------|------------|-------|-------|---------------|

| RPOR0        | 0680  |        | —      |        |            | RP35   | R<5:0> |       |       |            |            | _   |       |       | ł     | RP20R<5:0> |       |       | 0000          |

| RPOR1        | 0682  |        | -      |        | RP37R<5:0> |        |        |       | —     | RP36R<5:0> |            |     |       |       | 0000  |            |       |       |               |

| RPOR2        | 0684  |        | -      |        | RP39R<5:0> |        |        |       | —     | RP38R<5:0> |            |     |       | 0000  |       |            |       |       |               |

| RPOR3        | 0686  |        | -      |        | RP41R<5:0> |        |        |       |       | —          | RP40R<5:0> |     |       |       | 0000  |            |       |       |               |

| RPOR4        | 0688  |        | -      |        | RP43R<5:0> |        |        |       | —     | RP42R<5:0> |            |     |       | 0000  |       |            |       |       |               |

| RPOR5        | 068A  |        | _      |        |            | RP55   | R<5:0> |       |       |            |            | —   |       |       | I     | RP54R<5:0> |       |       | 0000          |

| RPOR6        | 068C  |        | -      |        |            | RP57   | R<5:0> |       |       |            |            | _   |       |       | I     | RP56R<5:0> |       |       | 0000          |

# TABLE 4-28: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EPXXXGP/MC206/506 AND PIC24EPXXXGP/MC206 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12     | Bit 11 | Bit 10 | Bit 9 | Bit 8 E | Bit 7 | 3it 6      | Bit 5 | Bit 4  | Bit 3 E | Bit 2 E | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|------------|--------|--------|-------|---------|-------|------------|-------|--------|---------|---------|-------|-------|---------------|

| RPOR0        | 0680  | —      | -      |        |            | RP35   | R<5:0> |       |         | —     | -          |       |        | RP20    | R<5:0>  |       |       | 0000          |

| RPOR1        | 0682  | —      | —      |        | RP37R<5:0> |        |        | _     | —       |       | RP36R<5:0> |       |        |         | 0000    |       |       |               |

| RPOR2        | 0684  | _      | —      |        |            | RP39   | R<5:0> |       |         |       | —          |       |        | RP38    | R<5:0>  |       |       | 0000          |

| RPOR3        | 0686  | _      | —      |        |            | RP41   | R<5:0> |       |         |       | —          |       |        | RP40    | R<5:0>  |       |       | 0000          |

| RPOR4        | 0688  | _      | —      |        |            | RP43   | R<5:0> |       |         |       | —          |       |        | RP42    | R<5:0>  |       |       | 0000          |

| RPOR5        | 068A  | _      | —      |        |            | RP55   | R<5:0> |       |         |       | —          |       |        | RP54    | R<5:0>  |       |       | 0000          |

| RPOR6        | 068C  | _      | —      |        | RP57R<5:0> |        |        |       | —       |       |            | RP56  | R<5:0> |         |         | 0000  |       |               |

| RPOR7        | 068E  | —      | —      |        |            | RP97   | R<5:0> |       |         | _     | —          | —     | —      | —       | _       | —     | —     | 0000          |

| RPOR8        | 0690  | _      | —      |        |            | RP118  | R<5:0> |       |         |       | —          | —     | —      | —       | —       | —     | —     | 0000          |

| RPOR9        | 0692  | —      | -      | _      | —          | _      | _      | _     | -       | —     | —          |       |        | RP120   | )R<5:0> |       |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## REGISTER 9-1: OSCCON: OS CILLATOR CONTROL REGISTER <sup>(1)</sup> (CONTINUED)

- bit 4 Unimplemented: Read as '0'

- bit 3 CF: Clock Fail Detect bit<sup>(3)</sup>

- 1 = FSCM has detected clock failure

- 0 = FSCM has not detected clock failure

- bit 2-1 Unimplemented: Read as '0'

- bit 0 OSWEN: Oscillator Switch Enable bit

- 1 = Requests oscillator switch to selection specified by the NOSC<2:0> bits

- 0 = Oscillator switch is complete

- Note 1: Writes to this register require an unlock sequence. Refer to "Oscillator" (DS70580) in the "dsPIC33/ PIC24 Family Reference Manual" (available from the Microchip web site) for details.

- 2: Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transitional clock source between the two PLL modes.

- 3: This bit should only be cleared in software. Setting the bit in software (= 1) will have the same effect as an actual oscillator failure and trigger an oscillator failure trap.

REGISTER 9-2: CLKDIV: CLOCK DIVISOR REGISTER (CONTINUED)

# bit 4-0 PLLPRE<4:0>: PLL Phase Detector Input Divider Select bits (also denoted as 'N1', PLL prescaler) 11111 = Input divided by 33 • • 00001 = Input divided by 3 00000 = Input divided by 2 (default)

- Note 1: The DOZE<2:0> bits can only be written to when the DOZEN bit is clear. If DOZEN = 1, any writes to DOZE<2:0> are ignored.

- 2: This bit is cleared when the ROI bit is set and an interrupt occurs.

- 3: The DOZEN bit cannot be set if DOZE<2:0> = 000. If DOZE<2:0> = 000, any attempt by user software to set the DOZEN bit is ignored.

| U-0                   | R/W-0        | R/W-0                                                                              | R/W-0 | R/W-0                | R/W-0          | R/W-0           | R/W-0 |  |  |  |  |

|-----------------------|--------------|------------------------------------------------------------------------------------|-------|----------------------|----------------|-----------------|-------|--|--|--|--|

| _                     |              |                                                                                    |       | IC4R<6:0>            |                |                 |       |  |  |  |  |

| it 15                 |              |                                                                                    |       |                      |                |                 | bit 8 |  |  |  |  |

|                       |              |                                                                                    |       |                      |                |                 |       |  |  |  |  |

| U-0                   | R/W-0        | R/W-0                                                                              | R/W-0 | R/W-0                | R/W-0          | R/W-0           | R/W-0 |  |  |  |  |

| —                     |              |                                                                                    |       | IC3R<6:0>            |                |                 |       |  |  |  |  |

| oit 7                 |              |                                                                                    |       |                      |                |                 | bit 0 |  |  |  |  |

| ogondu                |              |                                                                                    |       |                      |                |                 |       |  |  |  |  |

| ₋egend:<br>R = Readat | ole bit      | W = Writable                                                                       | hit   | U = Unimplen         | nented hit rea | ad as '0'       |       |  |  |  |  |

| -n = Value a          |              | '1' = Bit is set                                                                   |       | '0' = Bit is clea    |                | x = Bit is unkr | nown  |  |  |  |  |

|                       |              |                                                                                    |       |                      |                |                 |       |  |  |  |  |

| bit 15                | Unimplement  | ed: Read as '                                                                      | O'    |                      |                |                 |       |  |  |  |  |

| bit 14-8              |              | Assign Input Ca<br>-2 for input pin                                                |       | to the Correspondent | onding RPn P   | in bits         |       |  |  |  |  |

|                       |              | 1111001 = Input tied to RPI121                                                     |       |                      |                |                 |       |  |  |  |  |

|                       |              |                                                                                    |       |                      |                |                 |       |  |  |  |  |

|                       |              |                                                                                    |       |                      |                |                 |       |  |  |  |  |

|                       | 0000001 = Ir | nput tied to CM                                                                    | P1    |                      |                |                 |       |  |  |  |  |

|                       | 0000000 = Ir | nput tied to Vss                                                                   | i     |                      |                |                 |       |  |  |  |  |

| bit 7                 | Unimplement  | ed: Read as '                                                                      | D'    |                      |                |                 |       |  |  |  |  |

| bit 6-0               |              | IC3R<6:0>: Assign Input Capture 3 (IC3) to the Corresponding RPn Pin bits          |       |                      |                |                 |       |  |  |  |  |

|                       |              | (see Table 11-2 for input pin selection numbers)<br>1111001 = Input tied to RPI121 |       |                      |                |                 |       |  |  |  |  |

|                       |              |                                                                                    | 121   |                      |                |                 |       |  |  |  |  |

|                       |              |                                                                                    |       |                      |                |                 |       |  |  |  |  |

|                       | 0000001 – Ir | nput tied to CM                                                                    | D1    |                      |                |                 |       |  |  |  |  |

|                       |              | nput tied to UN                                                                    |       |                      |                |                 |       |  |  |  |  |

|                       |              | •                                                                                  |       |                      |                |                 |       |  |  |  |  |

#### REGISTER 11-5: RPINR8: PERIPHERAL PIN SELECT INPUT REGISTER 8

### 15.1 Output Compare Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 15.1.1 KEY RESOURCES

- "Output Compare" (DS70358) in the "dsPIC33/ PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- Development Tools

## 16.0 HIGH-SPEED PWM MODULE (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXGP/MC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "High-Speed PWM" (DS70645) in the "dsPIC33/PIC24 Family Reference Manual', which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices support a dedicated Pulse-Width Modulation (PWM) module with up to 6 outputs.

The high-speed PWMx module consists of the following major features:

- Three PWM generators

- Two PWM outputs per PWM generator

- Individual period and duty cycle for each PWM pair

- Duty cycle, dead time, phase shift and frequency resolution of Tcy/2 (7.14 ns at Fcy = 70MHz)

- Independent Fault and current-limit inputs for six PWM outputs

- · Redundant output

- Center-Aligned PWM mode

- Output override control

- Chop mode (also known as Gated mode)

- Special Event Trigger

- Prescaler for input clock

- PWMxL and PWMxH output pin swapping

- Independent PWM frequency, duty cycle and phase-shift changes for each PWM generator

- Dead-time compensation

- Enhanced Leading-Edge Blanking (LEB) functionality

- Frequency resolution enhancement

- PWM capture functionality

Note: In Edge-Aligned PWM mode, the duty cycle, dead time, phase shift and frequency resolution are 8.32 ns.

The high-speed PWMx module contains up to three PWM generators. Each PWM generator provides two PWM outputs: PWMxH and PWMxL. The master time base generator provides a synchronous signal as a common time base to synchronize the various PWM outputs. The individual PWM outputs are available on the output pins of the device. The input Fault signals and current-limit signals, when enabled, can monitor and protect the system by placing the PWM outputs into a known "safe" state.

Each PWMx can generate a trigger to the ADC module to sample the analog signal at a specific instance during the PWM period. In addition, the high-speed PWMx module also generates a Special Event Trigger to the ADC module based on either of the two master time bases.

The high-speed PWMx module can synchronize itself with an external signal or can act as a synchronizing source to any external device. The SYNCI1 input pin that utilizes PPS, can synchronize the high-speed PWMx module with an external signal. The SYNCO1 pin is an output pin that provides a synchronous signal to an external device.

Figure 16-1 illustrates an architectural overview of the high-speed PWMx module and its interconnection with the CPU and other peripherals.

### 16.1 PWM Faults

The PWMx module incorporates multiple external Fault inputs to include FLT1 and FLT2 which are remappable using the PPS feature, FLT3 and FLT4 which are available only on the larger 44-pin and 64-pin packages, and FLT32 which has been implemented with Class B safety features, and is available on a fixed pin on all dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

These Faults provide a safe and reliable way to safely shut down the PWM outputs when the Fault input is asserted.

#### 16.1.1 PWM FAULTS AT RESET

During any Reset event, the PWMx module maintains ownership of the Class B Fault, FLT32. At Reset, this Fault is enabled in Latched mode to ensure the fail-safe power-up of the application. The application software must clear the PWM Fault before enabling the highspeed motor control PWMx module. To clear the Fault condition, the FLT32 pin must first be pulled low externally or the internal pull-down resistor in the CNPDx register can be enabled.

Note: The Fault mode may be changed using the FLTMOD<1:0> bits (FCLCON<1:0>), regardless of the state of FLT32.

#### REGISTER 20-2: UxSTA: UART x STATUS AND CONTROL REGISTER (CONTINUED)

| bit 5   | ADDEN: Address Character Detect bit (bit 8 of received data = 1)                                                                                                                                                        |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Address Detect mode is enabled; if 9-bit mode is not selected, this does not take effect</li> <li>0 = Address Detect mode is disabled</li> </ul>                                                           |

| bit 4   | RIDLE: Receiver Idle bit (read-only)                                                                                                                                                                                    |

|         | 1 = Receiver is Idle<br>0 = Receiver is active                                                                                                                                                                          |

| bit 3   | PERR: Parity Error Status bit (read-only)                                                                                                                                                                               |

|         | <ul><li>1 = Parity error has been detected for the current character (character at the top of the receive FIFO)</li><li>0 = Parity error has not been detected</li></ul>                                                |

| bit 2   | FERR: Framing Error Status bit (read-only)                                                                                                                                                                              |

|         | <ul> <li>1 = Framing error has been detected for the current character (character at the top of the receive FIFO)</li> <li>0 = Framing error has not been detected</li> </ul>                                           |

| bit 1   | OERR: Receive Buffer Overrun Error Status bit (clear/read-only)                                                                                                                                                         |

|         | <ul> <li>1 = Receive buffer has overflowed</li> <li>0 = Receive buffer has not overflowed; clearing a previously set OERR bit (1 o 0 transition) resets the receiver buffer and the UxRSR to the empty state</li> </ul> |

| bit 0   | URXDA: UARTx Receive Buffer Data Available bit (read-only)                                                                                                                                                              |

|         | <ul> <li>1 = Receive buffer has data, at least one more character can be read</li> <li>0 = Receive buffer is empty</li> </ul>                                                                                           |

| Note 1. | Refer to the "I IART" (DS70582) section in the "dsPIC33/PIC24 Family Reference Manual" for information                                                                                                                  |

Note 1: Refer to the "UART" (DS70582) section in the "dsPIC33/PIC24 Family Reference Manual" for information on enabling the UARTx module for transmit operation.

#### REGISTER 23-5: AD1CHS123: ADC1 INPUT CHANNEL 1, 2, 3 SELECT REGISTER

|        | /W-0  |

|--------|-------|

| hit 45 | 123SB |

| bit 15 | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0    | R/W-0    | R/W-0   |

|-------|-----|-----|-----|-----|----------|----------|---------|

| —     | _   |     | —   | —   | CH123NA1 | CH123NA0 | CH123SA |

| bit 7 |     |     |     |     |          |          | bit 0   |

## Legend:

| Legend:           |                  |                             |                    |  |

|-------------------|------------------|-----------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |  |

bit 15-11 Unimplemented: Read as '0'

bit 10-9 CH123NB<1:0>: Channel 1, 2, 3 Negative Input Select for Sample MUXB bits In 12-bit mode (AD21B = 1), CH123NB is Unimplemented and is Read as '0':

| Value               |         | ADC Channel |       |

|---------------------|---------|-------------|-------|

| value               | CH1     | CH2         | CH3   |

| 11                  | AN9     | AN10        | AN11  |

| 10 <sup>(1,2)</sup> | OA3/AN6 | AN7         | AN8   |

| 0x                  | Vrefl   | Vrefl       | Vrefl |

bit 8 CH123SB: Channel 1, 2, 3 Positive Input Select for Sample MUXB bit In 12-bit mode (AD21B = 1), CH123SB is Unimplemented and is Read as '0':

| Value              |         | ADC Channel |         |

|--------------------|---------|-------------|---------|

| value              | CH1     | CH2         | CH3     |

| 1 <sup>(2)</sup>   | OA1/AN3 | OA2/AN0     | OA3/AN6 |

| 0 <sup>(1,2)</sup> | OA2/AN0 | AN1         | AN2     |

bit 7-3 Unimplemented: Read as '0'

bit 2-1 CH123NA<1:0>: Channel 1, 2, 3 Negative Input Select for Sample MUXA bits In 12-bit mode (AD21B = 1), CH123NA is Unimplemented and is Read as '0':

| Value               |         | ADC Channel |       |

|---------------------|---------|-------------|-------|

| value               | CH1     | CH2         | CH3   |

| 11                  | AN9     | AN10        | AN11  |

| 10 <sup>(1,2)</sup> | OA3/AN6 | AN7         | AN8   |

| 0x                  | Vrefl   | Vrefl       | Vrefl |

- Note 1: AN0 through AN7 are repurposed when comparator and op amp functionality is enabled. See Figure 23-1 to determine how enabling a particular op amp or comparator affects selection choices for Channels 1, 2 and 3.

- 2: The OAx input is used if the corresponding op amp is selected (OPMODE (CMxCON<10>) = 1); otherwise, the ANx input is used.

## REGISTER 24-12: PTGQPTR: PTG STEP QUEUE POINTER REGISTER<sup>(1)</sup>

| U-0        | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 |  |  |  |

|------------|-----|-----|-----|-----|-----|-----|-----|--|--|--|

| —          | —   |     | _   | _   |     |     | —   |  |  |  |

| bit 15 bit |     |     |     |     |     |     |     |  |  |  |

| U-0   | U-0 | U-0 | R/W-0        | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|-------|-----|-----|--------------|-------|-------|-------|-------|--|--|

| —     | —   | —   | PTGQPTR<4:0> |       |       |       |       |  |  |

| bit 7 |     |     |              |       |       |       | bit 0 |  |  |

| Legend:           |                  |                                                     |                    |  |  |

|-------------------|------------------|-----------------------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | W = Writable bit U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                                | x = Bit is unknown |  |  |

bit 15-5 Unimplemented: Read as '0'

bit 4-0 PTGQPTR<4:0>: PTG Step Queue Pointer Register bits

This register points to the currently active Step command in the Step queue.

Note 1: This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

## REGISTER 24-13: PTGQUEX: PTG STEP QUEUE REGISTER x (x = 0-7) $^{(1,3)}$

| R/W-0                            | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|----------------------------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| STEP(2x + 1)<7:0> <sup>(2)</sup> |       |       |       |       |       |       |       |  |  |

| bit 15                           |       |       |       |       |       |       | bit 8 |  |  |

| R/W-0                        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|------------------------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| STEP(2x)<7:0> <sup>(2)</sup> |       |       |       |       |       |       |       |  |  |

| bit 7                        |       |       |       |       |       |       |       |  |  |

| Legend:           |                                                                      |                      |                    |  |

|-------------------|----------------------------------------------------------------------|----------------------|--------------------|--|

| R = Readable bit  | R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |

| -n = Value at POR | '1' = Bit is set                                                     | '0' = Bit is cleared | x = Bit is unknown |  |

| bit 15-8 | STEP(2x + 1)<7:0>: PTG Step Queue Pointer Register bits <sup>(2)</sup> |

|----------|------------------------------------------------------------------------|

|          | A queue location for storage of the $STEP(2x + 1)$ command byte.       |

| bit 7-0  | STEP(2x)<7:0>: PTG Step Queue Pointer Register bits <sup>(2)</sup>     |

|          | A queue location for storage of the STEP(2x) command byte.             |

- Note 1: This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

- 2: Refer to Table 24-1 for the Step command encoding.

3: The Step registers maintain their values on any type of Reset.

REGISTER 25-3: CM4CON: COMPARATOR 4 CONTROL REGISTER (CONTINUED)

- bit 5 Unimplemented: Read as '0'

- bit 4 CREF: Comparator Reference Select bit (VIN+ input)<sup>(1)</sup>

- 1 = VIN+ input connects to internal CVREFIN voltage

- 0 = VIN+ input connects to C4IN1+ pin

- bit 3-2 Unimplemented: Read as '0'

- bit 1-0 CCH<1:0>: Comparator Channel Select bits<sup>(1)</sup>

- 11 = VIN- input of comparator connects to OA3/AN6

- 10 = VIN- input of comparator connects to OA2/AN0

- 01 = VIN- input of comparator connects to OA1/AN3

- 00 = VIN- input of comparator connects to C4IN1-

- Note 1: Inputs that are selected and not available will be tied to Vss. See the "Pin Diagrams" section for available inputs for each package.

#### REGISTER 26-3: CRCXORH: CRC XOR POLYNOMIAL HIGH REGISTER

| R/W-0                                | R/W-0 | R/W-0            | R/W-0        | R/W-0            | R/W-0     | R/W-0           | R/W-0 |

|--------------------------------------|-------|------------------|--------------|------------------|-----------|-----------------|-------|

|                                      |       |                  | X<3          | 1:24>            |           |                 |       |

| bit 15                               |       |                  |              |                  |           |                 | bit 8 |

|                                      |       |                  |              |                  |           |                 |       |

| R/W-0                                | R/W-0 | R/W-0            | R/W-0        | R/W-0            | R/W-0     | R/W-0           | R/W-0 |

|                                      |       |                  | X<2          | 3:16>            |           |                 |       |

| bit 7                                |       |                  |              |                  |           |                 | bit 0 |

| Legend:                              |       |                  |              |                  |           |                 |       |

| -                                    |       |                  |              |                  |           |                 |       |

| R = Readable bit 		 W = Writable bit |       | oit              | U = Unimpler | mented bit, rea  | ad as '0' |                 |       |

| -n = Value at POR                    |       | '1' = Bit is set |              | '0' = Bit is cle | ared      | x = Bit is unkr | nown  |

bit 15-0 X<31:16>: XOR of Polynomial Term X<sup>n</sup> Enable bits

#### REGISTER 26-4: CRCXORL: CRC XOR POLYNOMIAL LOW REGISTER

| R/W-0                             | R/W-0 | R/W-0            | R/W-0                              | R/W-0                | R/W-0 | R/W-0              | R/W-0 |

|-----------------------------------|-------|------------------|------------------------------------|----------------------|-------|--------------------|-------|

|                                   |       |                  | Х<                                 | :15:8>               |       |                    |       |

| bit 15                            |       |                  |                                    |                      |       |                    | bit 8 |

|                                   |       |                  |                                    |                      |       |                    |       |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0                              | R/W-0                | R/W-0 | R/W-0              | U-0   |

|                                   |       |                  | X<7:1>                             |                      |       |                    | _     |

| bit 7                             |       |                  |                                    |                      |       |                    | bit 0 |

|                                   |       |                  |                                    |                      |       |                    |       |

| Legend:                           |       |                  |                                    |                      |       |                    |       |

| R = Readable bit W = Writable bit |       | bit              | U = Unimplemented bit, read as '0' |                      |       |                    |       |

| -n = Value at POR                 |       | '1' = Bit is set |                                    | '0' = Bit is cleared |       | x = Bit is unknown |       |

bit 15-1 X<15:1>: XOR of Polynomial Term X<sup>n</sup> Enable bits

bit 0 Unimplemented: Read as '0'

| Bit Field             | Description                                                                                                                                                                                   |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WDTPRE                | Watchdog Timer Prescaler bit<br>1 = 1:128<br>0 = 1:32                                                                                                                                         |

| WDTPOST<3:0>          | Watchdog Timer Postscaler bits<br>1111 = 1:32,768<br>1110 = 1:16,384<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                                         |

| WDTWIN<1:0>           | Watchdog Window Select bits<br>11 = WDT window is 25% of WDT period<br>10 = WDT window is 37.5% of WDT period<br>01 = WDT window is 50% of WDT period<br>00 = WDT window is 75% of WDT period |

| ALTI2C1               | Alternate I2C1 pin<br>1 = I2C1 is mapped to the SDA1/SCL1 pins<br>0 = I2C1 is mapped to the ASDA1/ASCL1 pins                                                                                  |

| ALTI2C2               | Alternate I2C2 pin<br>1 = I2C2 is mapped to the SDA2/SCL2 pins<br>0 = I2C2 is mapped to the ASDA2/ASCL2 pins                                                                                  |

| JTAGEN <sup>(2)</sup> | JTAG Enable bit<br>1 = JTAG is enabled<br>0 = JTAG is disabled                                                                                                                                |

| ICS<1:0>              | ICD Communication Channel Select bits<br>11 = Communicate on PGEC1 and PGED1<br>10 = Communicate on PGEC2 and PGED2<br>01 = Communicate on PGEC3 and PGED3<br>00 = Reserved, do not use       |

| TABLE 27-2: ( | CONFIGURATION BITS DESCRIPTION (CONTINUED) |

|---------------|--------------------------------------------|

|---------------|--------------------------------------------|

Note 1: This bit is only available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

2: When JTAGEN = 1, an internal pull-up resistor is enabled on the TMS pin. Erased devices default to JTAGEN = 1. Applications requiring I/O pins in a high-impedance state (tri-state) in Reset should use pins other than TMS for this purpose.

| TABL               | E 28-2:              | INSTR          | UCTION SET OVERVIEW    |                                          |               |                               |                          |

|--------------------|----------------------|----------------|------------------------|------------------------------------------|---------------|-------------------------------|--------------------------|

| Base<br>Instr<br># | Assembly<br>Mnemonic |                | Assembly Syntax        | Description                              | # of<br>Words | # of<br>Cycles <sup>(2)</sup> | Status Flags<br>Affected |

| 1                  | ADD                  | ADD            | Act                    | Add Accumulators                         | 1             | 1                             | OA,OB,SA,SB              |

|                    |                      | ADD            | f                      | f = f + WREG                             | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | ADD            | f,WREG                 | WREG = f + WREG                          | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | ADD            | #lit10,Wn              | Wd = lit10 + Wd                          | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | ADD            | Wb,Ws,Wd               | Wd = Wb + Ws                             | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | ADD            | Wb,#lit5,Wd            | Wd = Wb + lit5                           | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | ADD            | Wso,#Slit4,Acc         | 16-bit Signed Add to Accumulator         | 1             | 1                             | OA,OB,SA,SB              |

| 2                  | ADDC                 | ADDC           | f                      | f = f + WREG + (C)                       | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | ADDC           | f,WREG                 | WREG = f + WREG + (C)                    | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | ADDC           | #lit10,Wn              | Wd = lit10 + Wd + (C)                    | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | ADDC           | Wb,Ws,Wd               | Wd = Wb + Ws + (C)                       | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | ADDC           | Wb,#lit5,Wd            | Wd = Wb + lit5 + (C)                     | 1             | 1                             | C,DC,N,OV,Z              |

| 3                  | AND                  | AND            | f                      | f = f .AND. WREG                         | 1             | 1                             | N,Z                      |

|                    |                      | AND            | f,WREG                 | WREG = f .AND. WREG                      | 1             | 1                             | N,Z                      |

|                    |                      | AND            | #lit10,Wn              | Wd = lit10 .AND. Wd                      | 1             | 1                             | N,Z                      |

|                    |                      | AND            | Wb,Ws,Wd               | Wd = Wb .AND. Ws                         | 1             | 1                             | N,Z                      |

|                    |                      | AND            | Wb,#lit5,Wd            | Wd = Wb .AND. lit5                       | 1             | 1                             | N,Z                      |

| 4                  | ASR                  | ASR            | f                      | f = Arithmetic Right Shift f             | 1             | 1                             | C,N,OV,Z                 |

|                    | _                    | ASR            | f,WREG                 | WREG = Arithmetic Right Shift f          | 1             | 1                             | C,N,OV,Z                 |

|                    |                      | ASR            | Ws,Wd                  | Wd = Arithmetic Right Shift Ws           | 1             | 1                             | C,N,OV,Z                 |

|                    |                      | ASR            | Wb,Wns,Wnd             | Wnd = Arithmetic Right Shift Wb by Wns   | 1             | 1                             | N,Z                      |

|                    |                      | ASR            | Wb,#lit5,Wnd           | Wnd = Arithmetic Right Shift Wb by lit5  | 1             | 1                             | N,Z                      |

| 5                  | BCLR                 | BCLR           | f,#bit4                | Bit Clear f                              | 1             | 1                             | None                     |

| •                  | 2021                 | BCLR           | Ws,#bit4               | Bit Clear Ws                             | 1             | 1                             | None                     |

| 6                  | BRA                  | BRA            | C,Expr                 | Branch if Carry                          | 1             | 1 (4)                         | None                     |

| •                  | 2.0.0                | BRA            | GE,Expr                | Branch if greater than or equal          | 1             | 1 (4)                         | None                     |

|                    |                      | BRA            | GEU,Expr               | Branch if unsigned greater than or equal | 1             | 1 (4)                         | None                     |

|                    |                      | BRA            | GT,Expr                | Branch if greater than                   | 1             | 1 (4)                         | None                     |

|                    |                      | BRA            | GTU,Expr               | Branch if unsigned greater than          | 1             | 1 (4)                         | None                     |

|                    |                      | BRA            | LE,Expr                | Branch if less than or equal             | 1             | 1 (4)                         | None                     |

|                    |                      | BRA            | LEU,Expr               | Branch if unsigned less than or equal    | 1             | 1 (4)                         | None                     |

|                    |                      | BRA            | LT,Expr                | Branch if less than                      | 1             | 1 (4)                         | None                     |

|                    |                      | BRA            | LTU,Expr               | Branch if unsigned less than             | 1             | 1 (4)                         | None                     |

|                    |                      | BRA            | N,Expr                 | Branch if Negative                       | 1             | 1 (4)                         | None                     |

|                    |                      | BRA            | NC,Expr                | Branch if Not Carry                      | 1             | 1 (4)                         | None                     |

|                    |                      | BRA            | NN,Expr                | Branch if Not Negative                   | 1             | 1 (4)                         | None                     |

|                    |                      | BRA            | NOV,Expr               | Branch if Not Overflow                   | 1             | 1 (4)                         | None                     |

|                    |                      | BRA            | NZ,Expr                | Branch if Not Zero                       | 1             | 1 (4)                         | None                     |

|                    |                      | BRA            | OA,Expr <sup>(1)</sup> | Branch if Accumulator A overflow         | 1             | 1 (4)                         | None                     |

|                    |                      | BRA            | OB,Expr <sup>(1)</sup> | Branch if Accumulator B overflow         | 1             | 1 (4)                         | None                     |

|                    |                      | BRA            | OV,Expr <sup>(1)</sup> | Branch if Overflow                       | 1             | 1 (4)                         | None                     |

|                    |                      | BRA            | SA,Expr <sup>(1)</sup> | Branch if Accumulator A saturated        | 1             | 1 (4)                         | None                     |

|                    |                      | BRA            | SB,Expr <sup>(1)</sup> | Branch if Accumulator B saturated        | 1             | 1 (4)                         | None                     |

|                    |                      | BRA            | Expr                   | Branch Unconditionally                   | 1             | 4                             | None                     |

|                    |                      | BRA            | Z,Expr                 | Branch if Zero                           | 1             | 4 1 (4)                       | None                     |

|                    |                      | BRA            | Vn                     | Computed Branch                          | 1             | 4                             | None                     |

| 7                  | BSET                 | BSET           | f,#bit4                | Bit Set f                                | 1             | 4                             | None                     |

| '                  | DOLI                 | BSET           | Ws,#bit4               | Bit Set Ws                               | 1             | 1                             | None                     |

| 8                  | BSW                  | BSW.C          | Ws,#bit4               | Write C bit to Ws <wb></wb>              | 1             | 1                             | None                     |

| 0                  | 5000                 | BSW.C<br>BSW.Z |                        |                                          |               |                               |                          |

|                    |                      | D311.2         | Ws,Wb                  | Write Z bit to Ws <wb></wb>              | 1             | 1                             | None                     |

### TABLE 28-2: INSTRUCTION SET OVERVIEW

Note 1: These instructions are available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

#### 29.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16 and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

#### 29.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

#### 29.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

### 29.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility