Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 70 MIPs                                                                        |

| Connectivity               | I²C, IrDA, LINbus, SPI, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 35                                                                             |

| Program Memory Size        | 32KB (10.7K x 24)                                                              |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 2K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 9x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

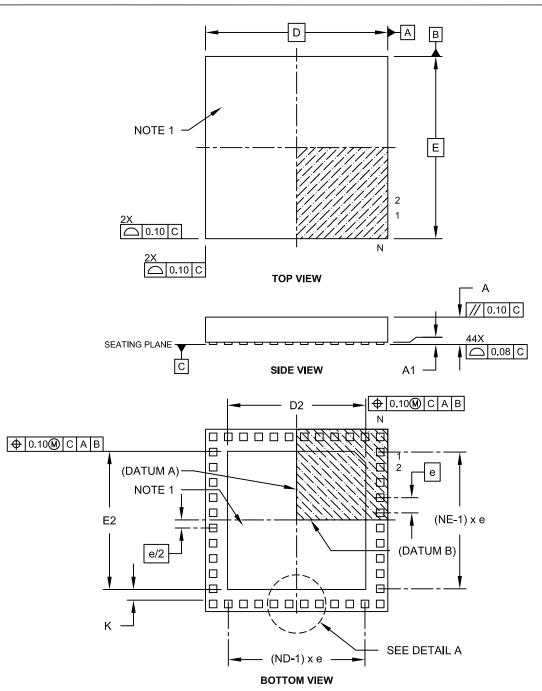

| Package / Case             | 44-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 44-QFN (8x8)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep32gp204t-i-ml |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 4   | 4-9:  | INPUT                               |                       | JRE 1 T | HROUG  | H INPU                                   | Т САРТ | URE 4 | REGIST       | ER MA        | Р        |       |       |       |          |          |       |               |

|-----------|-------|-------------------------------------|-----------------------|---------|--------|------------------------------------------|--------|-------|--------------|--------------|----------|-------|-------|-------|----------|----------|-------|---------------|

| File Name | Addr. | Bit 15                              | Bit 14                | Bit 13  | Bit 12 | Bit 11                                   | Bit 10 | Bit 9 | Bit 8        | Bit 7        | Bit 6    | Bit 5 | Bit 4 | Bit 3 | Bit 2    | Bit 1    | Bit 0 | All<br>Resets |

| IC1CON1   | 0140  | _                                   | —                     | ICSIDL  | 10     | ICTSEL<2:0> ICI<1:0> ICOV ICBNE ICM<2:0> |        |       | ICM<2:0>     |              | 0000     |       |       |       |          |          |       |               |

| IC1CON2   | 0142  | _                                   | _                     |         | _      |                                          | —      | —     | IC32         | ICTRIG       | TRIGSTAT |       |       | S     | YNCSEL<4 | :0>      |       | 000D          |

| IC1BUF    | 0144  |                                     |                       |         |        |                                          |        | Inp   | ut Capture ' | 1 Buffer Reg | gister   |       |       |       |          |          |       | xxxx          |

| IC1TMR    | 0146  |                                     | Input Capture 1 Timer |         |        |                                          |        |       |              |              |          |       |       | 0000  |          |          |       |               |

| IC2CON1   | 0148  |                                     | _                     | ICSIDL  | 10     | ICTSEL<2:0> ICI<1:0> ICOV ICBNE          |        |       |              |              | ICM<2:0> |       | 0000  |       |          |          |       |               |

| IC2CON2   | 014A  | IC32 ICTRIG TRIGSTAT - SYNCSEL<4:0> |                       |         |        |                                          |        |       |              |              | 000D     |       |       |       |          |          |       |               |

| IC2BUF    | 014C  |                                     |                       |         |        |                                          |        | Inp   | ut Capture 2 | 2 Buffer Reg | gister   |       |       |       |          |          |       | xxxx          |

| IC2TMR    | 014E  |                                     |                       |         |        |                                          |        |       | Input Capt   | ture 2 Time  | r        |       |       |       |          |          |       | 0000          |

| IC3CON1   | 0150  |                                     | _                     | ICSIDL  | 10     | CTSEL<2:0                                | >      | —     | _            |              | ICI<1    | :0>   | ICOV  | ICBNE |          | ICM<2:0> |       | 0000          |

| IC3CON2   | 0152  |                                     | _                     |         |        |                                          | —      | —     | IC32         | ICTRIG       | TRIGSTAT |       |       | S     | YNCSEL<4 | :0>      |       | 000D          |

| IC3BUF    | 0154  |                                     |                       |         |        |                                          |        | Inp   | ut Capture 3 | 3 Buffer Reg | gister   |       |       |       |          |          |       | xxxx          |

| IC3TMR    | 0156  |                                     |                       |         |        |                                          |        |       | Input Capt   | ture 3 Time  | r        |       |       |       |          |          |       | 0000          |

| IC4CON1   | 0158  |                                     | _                     | ICSIDL  | 10     | CTSEL<2:0                                | >      | —     | _            |              | ICI<1    | :0>   | ICOV  | ICBNE |          | ICM<2:0> |       | 0000          |

| IC4CON2   | 015A  | _                                   | _                     |         | _      |                                          | -      | _     | IC32         | ICTRIG       | TRIGSTAT | -     |       | S     | YNCSEL<4 | :0>      |       | 000D          |

| IC4BUF    | 015C  |                                     |                       |         |        |                                          |        | Inp   | ut Capture 4 | 4 Buffer Reg | gister   |       |       |       |          |          |       | xxxx          |

| IC4TMR    | 015E  |                                     |                       |         |        |                                          |        |       | Input Capt   | ure 4 Time   | r        |       |       |       |          |          |       | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| IABLE 4-2  | 23: E            | CAN1 I         | REGIST | ER MA  | P WHE  | N WIN  | (CICIE | <l1<0></l1<0> | •) = 1 FC | OR dsPIC | 33EPX    | XXMC/G | P50X D | EVICES | ONLY ( |       | NUED) |               |

|------------|------------------|----------------|--------|--------|--------|--------|--------|---------------|-----------|----------|----------|--------|--------|--------|--------|-------|-------|---------------|

| File Name  | Addr             | Bit 15         | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9         | Bit 8     | Bit 7    | Bit 6    | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

| C1RXF11EID | D 046E EID<15:8> |                |        |        |        |        |        | EID<7:0>      |           |          |          |        |        |        | xxxx   |       |       |               |

| C1RXF12SID | 0470             | 0470 SID<10:3> |        |        |        |        |        |               |           |          | SID<2:0> |        | _      | EXIDE  | _      | EID<1 | 7:16> | xxxx          |

| C1RXF12EID | 0472             | I72 EID<15:8>  |        |        |        |        |        | EID<7:0>      |           |          |          |        |        | xxxx   |        |       |       |               |

| C1RXF13SID | 0474             | SID<10:3>      |        |        |        |        |        |               |           | SID<2:0> |          | _      | EXIDE  | —      | EID<1  | 7:16> | xxxx  |               |

| C1RXF13EID | 0476             |                |        |        | EID<   | :15:8> |        |               |           | EID<7:0> |          |        |        |        |        |       | xxxx  |               |

| C1RXF14SID | 0478             |                |        |        | SID<   | :10:3> |        |               |           |          | SID<2:0> |        | _      | EXIDE  | —      | EID<1 | 7:16> | xxxx          |

| C1RXF14EID | 047A             | 147A EID<15:8> |        |        |        |        |        | EID<7:0>      |           |          |          |        |        |        | xxxx   |       |       |               |

| C1RXF15SID | 047C             | C SID<10:3>    |        |        |        |        |        |               | SID<2:0>  |          | _        | EXIDE  | _      | EID<1  | 7:16>  | xxxx  |       |               |

| C1RXF15EID | 047E             |                |        |        | EID<   | :15:8> |        |               |           |          |          |        | EID<   | 7:0>   |        |       |       | xxxx          |

#### ECANI DECISTED MAD WHEN WIN (CICTDI 1 -0.) 1 EOD doDIC22EDXXXMC/CDE0X DEVICES ONLY (CONTINUED) TARIE 1 22.

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| R/SO-0 <sup>(1</sup>         | ) R/W-0 <sup>(1)</sup>                     | R/W-0 <sup>(1)</sup>        | R/W-0                         | U-0                     | U-0                     | U-0                     | U-0                    |

|------------------------------|--------------------------------------------|-----------------------------|-------------------------------|-------------------------|-------------------------|-------------------------|------------------------|

| WR                           | WREN                                       | WRERR                       | NVMSIDL <sup>(2)</sup>        | _                       |                         | —                       |                        |

| bit 15                       | I                                          | 1                           | 1                             |                         |                         |                         | bit 8                  |

|                              |                                            |                             |                               |                         |                         |                         |                        |

| U-0                          | U-0                                        | U-0                         | U-0                           | R/W-0 <sup>(1)</sup>    | R/W-0 <sup>(1)</sup>    | R/W-0 <sup>(1)</sup>    | R/W-0 <sup>(1)</sup>   |

| _                            | —                                          | —                           | —                             | NVMOP3 <sup>(3,4)</sup> | NVMOP2 <sup>(3,4)</sup> | NVMOP1 <sup>(3,4)</sup> | NVMOP0 <sup>(3,4</sup> |

| bit 7                        |                                            |                             |                               |                         |                         |                         | bit (                  |

| lagandi                      |                                            | SO - Sottab                 | la Only hit                   |                         |                         |                         |                        |

| L <b>egend:</b><br>R = Reada | ble hit                                    | SO = Settab<br>W = Writable | -                             | II – I Inimplem         | nented bit, read        | ae 'O'                  |                        |

| -n = Value                   |                                            | '1' = Bit is se             |                               | '0' = Bit is clea       |                         | x = Bit is unkr         |                        |

|                              |                                            | 1 - Dit 13 30               |                               |                         |                         |                         | lowin                  |

| bit 15                       | WR: Write Co                               | ontrol bit(1)               |                               |                         |                         |                         |                        |

|                              |                                            |                             | ory program or                | erase operation         | on; the operatio        | n is self-timed         | and the bit is         |

|                              | cleared b                                  | y hardware o                | nce the operati               | on is complete          |                         |                         |                        |

|                              | -                                          |                             | ration is comple              | ete and inactive        | 9                       |                         |                        |

| bit 14                       | WREN: Write                                |                             | n/erase operati               | 000                     |                         |                         |                        |

|                              |                                            |                             | /erase operatio               |                         |                         |                         |                        |

| oit 13                       |                                            |                             | Error Flag bit <sup>(1)</sup> |                         |                         |                         |                        |

|                              | 1 = An impro                               | per program o               | r erase sequend               |                         | rmination has oc        | curred (bit is se       | t automatically        |

|                              |                                            | et attempt of th            | e WR bit)<br>operation com    | olotod pormally         |                         |                         |                        |

| bit 12                       |                                            |                             | le Control bit <sup>(2)</sup> | Sieteu normaliy         |                         |                         |                        |

|                              |                                            |                             | r goes into Star              | ndbv mode duri          | ina Idle mode           |                         |                        |

|                              |                                            |                             | r is active durin             |                         |                         |                         |                        |

| bit 11-4                     | Unimplemen                                 | ted: Read as                | '0'                           |                         |                         |                         |                        |

| bit 3-0                      | NVMOP<3:0>                                 | NVM Operation               | ation Select bits             | <sub>3</sub> (1,3,4)    |                         |                         |                        |

|                              | 1111 <b>= Rese</b>                         |                             |                               |                         |                         |                         |                        |

|                              | 1110 = Rese<br>1101 = Rese                 |                             |                               |                         |                         |                         |                        |

|                              | 1100 <b>= Rese</b>                         |                             |                               |                         |                         |                         |                        |

|                              | 1011 <b>= Rese</b>                         |                             |                               |                         |                         |                         |                        |

|                              | 1010 = Rese<br>0011 = Memo                 |                             | e operation                   |                         |                         |                         |                        |

|                              | 0010 = Rese                                | rved                        | -                             |                         |                         |                         |                        |

|                              |                                            |                             | ord program ope               | eration <sup>(5)</sup>  |                         |                         |                        |

|                              | 0000 <b>= Rese</b>                         | rvea                        |                               |                         |                         |                         |                        |

|                              | These bits can onl                         | -                           |                               |                         |                         |                         |                        |

|                              | If this bit is set, the (TVREG) before Fla |                             |                               |                         | d upon exiting lo       | dle mode, there         | is a delay             |

|                              | All other combinati                        |                             | •                             |                         |                         |                         |                        |

| <b>.</b> .                   |                                            |                             |                               | in ploinenteu.          |                         |                         |                        |

| 4:                           | Execution of the P                         | wrsav instruc               | tion is ianored               | while any of th         | e NVM operatio          | ns are in progr         | ess.                   |

#### REGISTER 5-1: NVMCON: NONVOLATILE MEMORY (NVM) CONTROL REGISTER

| R/S-0                | U-0                                                                           | U-0                             | U-0                   | U-0              | U-0              | U-0             | U-0     |  |  |  |  |  |

|----------------------|-------------------------------------------------------------------------------|---------------------------------|-----------------------|------------------|------------------|-----------------|---------|--|--|--|--|--|

| FORCE <sup>(1)</sup> |                                                                               | _                               | _                     | —                |                  | _               |         |  |  |  |  |  |

| bit 15               |                                                                               |                                 |                       |                  |                  |                 | bit 8   |  |  |  |  |  |

|                      |                                                                               |                                 |                       |                  |                  |                 |         |  |  |  |  |  |

| R/W-0                | R/W-0                                                                         | R/W-0                           | R/W-0                 | R/W-0            | R/W-0            | R/W-0           | R/W-0   |  |  |  |  |  |

| IRQSEL7              | IRQSEL6                                                                       | IRQSEL5                         | IRQSEL4               | IRQSEL3          | IRQSEL2          | IRQSEL1         | IRQSEL0 |  |  |  |  |  |

| bit 7                |                                                                               |                                 |                       |                  |                  |                 | bit     |  |  |  |  |  |

| Legend:              |                                                                               | S = Settable b                  | oit                   |                  |                  |                 |         |  |  |  |  |  |

| R = Readable         | bit                                                                           | W = Writable                    | bit                   | U = Unimpler     | mented bit, read | d as '0'        |         |  |  |  |  |  |

| -n = Value at F      | POR                                                                           | '1' = Bit is set                |                       | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |  |  |  |  |  |

|                      |                                                                               |                                 |                       |                  |                  |                 |         |  |  |  |  |  |

| bit 15               | FORCE: Force                                                                  | e DMA Transfe                   | er bit <sup>(1)</sup> |                  |                  |                 |         |  |  |  |  |  |

|                      | 1 = Forces a                                                                  | single DMA tra                  | insfer (Manua         | l mode)          |                  |                 |         |  |  |  |  |  |

|                      | 0 = Automatic DMA transfer initiation by DMA request                          |                                 |                       |                  |                  |                 |         |  |  |  |  |  |

| bit 14-8             | Unimplemen                                                                    | ted: Read as 'd                 | )'                    |                  |                  |                 |         |  |  |  |  |  |

| bit 7-0              | IRQSEL<7:0>: DMA Peripheral IRQ Number Select bits                            |                                 |                       |                  |                  |                 |         |  |  |  |  |  |

|                      | 01000110 = ECAN1 - TX Data Request(2)                                         |                                 |                       |                  |                  |                 |         |  |  |  |  |  |

|                      |                                                                               | IC4 – Input Ca                  |                       |                  |                  |                 |         |  |  |  |  |  |

|                      |                                                                               | IC3 – Input Ca                  |                       |                  |                  |                 |         |  |  |  |  |  |

|                      |                                                                               | ECAN1 – RX D<br>SPI2 Transfer I | -                     |                  |                  |                 |         |  |  |  |  |  |

|                      |                                                                               |                                 |                       | itter            |                  |                 |         |  |  |  |  |  |

|                      | 00011111 = UART2TX – UART2 Transmitter<br>00011110 = UART2RX – UART2 Receiver |                                 |                       |                  |                  |                 |         |  |  |  |  |  |

|                      | 00011100 = TMR5 - Timer5                                                      |                                 |                       |                  |                  |                 |         |  |  |  |  |  |

|                      | 00011011 = TMR4 – Timer4                                                      |                                 |                       |                  |                  |                 |         |  |  |  |  |  |

|                      | 00011010 = OC4 – Output Compare 4                                             |                                 |                       |                  |                  |                 |         |  |  |  |  |  |

|                      | 00011001 = OC3 – Output Compare 3                                             |                                 |                       |                  |                  |                 |         |  |  |  |  |  |

|                      | 00001101 = ADC1 – ADC1 Convert done                                           |                                 |                       |                  |                  |                 |         |  |  |  |  |  |

|                      | 00001100 = UART1TX – UART1 Transmitter                                        |                                 |                       |                  |                  |                 |         |  |  |  |  |  |

|                      | 00001011 = UART1RX – UART1 Receiver                                           |                                 |                       |                  |                  |                 |         |  |  |  |  |  |

|                      | 00001010 = SPI1 – Transfer Done                                               |                                 |                       |                  |                  |                 |         |  |  |  |  |  |

|                      | 00001000 = TMR3 – Timer3<br>00000111 = TMR2 – Timer2                          |                                 |                       |                  |                  |                 |         |  |  |  |  |  |

|                      | 00000111 = 1MR2 - 1Imer2<br>00000110 = OC2 - Output Compare 2                 |                                 |                       |                  |                  |                 |         |  |  |  |  |  |

|                      |                                                                               | IC2 – Input Ca                  |                       |                  |                  |                 |         |  |  |  |  |  |

|                      | 0000010 =                                                                     | OC1 – Output (                  | Compare 1             |                  |                  |                 |         |  |  |  |  |  |

|                      |                                                                               | IC1 – Input Ca                  |                       |                  |                  |                 |         |  |  |  |  |  |

|                      | 00000000 =                                                                    | INT0 – Externa                  | I Interrupt 0         |                  |                  |                 |         |  |  |  |  |  |

#### REGISTER 8-2: DMAXREQ: DMA CHANNEL x IRQ SELECT REGISTER

- **Note 1:** The FORCE bit cannot be cleared by user software. The FORCE bit is cleared by hardware when the forced DMA transfer is complete or the channel is disabled (CHEN = 0).

- 2: This selection is available in dsPIC33EPXXXGP/MC50X devices only.

| U-0                                          | U-0                                                                                                                                                                          | U-0                                                                                                                                                                                                                          | U-0                                                                                                                              | U-0                               | U-0                      | U-0                         | U-0  |  |  |

|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--------------------------|-----------------------------|------|--|--|

|                                              | _                                                                                                                                                                            | _                                                                                                                                                                                                                            | _                                                                                                                                | _                                 | _                        | _                           | _    |  |  |

| bit 15                                       |                                                                                                                                                                              |                                                                                                                                                                                                                              |                                                                                                                                  |                                   |                          |                             | bit  |  |  |

|                                              |                                                                                                                                                                              |                                                                                                                                                                                                                              |                                                                                                                                  |                                   |                          |                             |      |  |  |

| U-0                                          | U-0                                                                                                                                                                          | U-0                                                                                                                                                                                                                          | R/W-0                                                                                                                            | R/W-0                             | U-0                      | U-0                         | U-0  |  |  |

| _                                            | -                                                                                                                                                                            | _                                                                                                                                                                                                                            | DMA0MD <sup>(1)</sup><br>DMA1MD <sup>(1)</sup><br>DMA2MD <sup>(1)</sup><br>DMA3MD <sup>(1)</sup>                                 | PTGMD                             | _                        | _                           | _    |  |  |

| bit 7                                        |                                                                                                                                                                              |                                                                                                                                                                                                                              |                                                                                                                                  |                                   |                          |                             | bit  |  |  |

| <b>Legend:</b><br>R = Readab<br>-n = Value a |                                                                                                                                                                              | W = Writable<br>'1' = Bit is set                                                                                                                                                                                             |                                                                                                                                  | U = Unimplen<br>'0' = Bit is clea | nented bit, read<br>ared | l as '0'<br>x = Bit is unkn | iown |  |  |

| bit 15-5<br>bit 4                            | DMA0MD: DM<br>1 = DMA0 mo<br>0 = DMA0 mo<br>DMA1MD: DM<br>1 = DMA1 mo<br>0 = DMA1 mo<br>DMA2MD: DM<br>1 = DMA2 mo<br>0 = DMA2 mo<br>DMA3MD: DM<br>1 = DMA3 mo<br>0 = DMA3 mo | ted: Read as '<br>MA0 Module Di<br>odule is disable<br>odule is enable<br>MA1 Module Di<br>odule is disable<br>MA2 Module Di<br>odule is disable<br>odule is enable<br>MA3 Module Di<br>odule is disable<br>odule is disable | sable bit <sup>(1)</sup><br>d<br>sable bit <sup>(1)</sup><br>d<br>sable bit <sup>(1)</sup><br>d<br>sable bit <sup>(1)</sup><br>d |                                   |                          |                             |      |  |  |

| bit 3                                        | PTGMD: PTG Module Disable bit<br>1 = PTG module is disabled<br>0 = PTG module is enabled                                                                                     |                                                                                                                                                                                                                              |                                                                                                                                  |                                   |                          |                             |      |  |  |

| bit 2-0                                      | Unimplement                                                                                                                                                                  | ted: Read as '                                                                                                                                                                                                               | 0'                                                                                                                               |                                   |                          |                             |      |  |  |

| Note 1: T                                    | his single bit ena                                                                                                                                                           | ables and disal                                                                                                                                                                                                              | oles all four DM                                                                                                                 | A channels.                       |                          |                             |      |  |  |

#### REGISTER 10-6: PMD7: PERIPHERAL MODULE DISABLE CONTROL REGISTER 7

## 11.4 Peripheral Pin Select (PPS)

A major challenge in general purpose devices is providing the largest possible set of peripheral features while minimizing the conflict of features on I/O pins. The challenge is even greater on low pin count devices. In an application where more than one peripheral needs to be assigned to a single pin, inconvenient workarounds in application code, or a complete redesign, may be the only option.

Peripheral Pin Select configuration provides an alternative to these choices by enabling peripheral set selection and their placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the device to their entire application, rather than trimming the application to fit the device.

The Peripheral Pin Select configuration feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of most digital peripherals to any one of these I/O pins. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

#### 11.4.1 AVAILABLE PINS

The number of available pins is dependent on the particular device and its pin count. Pins that support the Peripheral Pin Select feature include the label, "RPn" or "RPIn", in their full pin designation, where "n" is the remappable pin number. "RP" is used to designate pins that support both remappable input and output functions, while "RPI" indicates pins that support remappable input functions only.

#### 11.4.2 AVAILABLE PERIPHERALS

The peripherals managed by the Peripheral Pin Select are all digital-only peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer-related peripherals (input capture and output compare) and interrupt-on-change inputs. In comparison, some digital-only peripheral modules are never included in the Peripheral Pin Select feature. This is because the peripheral's function requires special I/O circuitry on a specific port and cannot be easily connected to multiple pins. These modules include  $I^2C^{TM}$  and the PWM. A similar requirement excludes all modules with analog inputs, such as the ADC Converter.

A key difference between remappable and nonremappable peripherals is that remappable peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-remappable peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral.

When a remappable peripheral is active on a given I/O pin, it takes priority over all other digital I/O and digital communication peripherals associated with the pin. Priority is given regardless of the type of peripheral that is mapped. Remappable peripherals never take priority over any analog functions associated with the pin.

#### 11.4.3 CONTROLLING PERIPHERAL PIN SELECT

Peripheral Pin Select features are controlled through two sets of SFRs: one to map peripheral inputs and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheralselectable pin is handled in two different ways, depending on whether an input or output is being mapped. NOTES:

| REGISTER 16-2: | PTCON2: PWMx PRIMARY MASTER CLOCK DIVIDER SELECT REGISTER 2 |

|----------------|-------------------------------------------------------------|

|----------------|-------------------------------------------------------------|

| U-0                                | U-0        | U-0            | U-0 | U-0                                | U-0                     | U-0                     | U-0         |  |  |  |

|------------------------------------|------------|----------------|-----|------------------------------------|-------------------------|-------------------------|-------------|--|--|--|

| —                                  | —          | —              | _   | —                                  | —                       | —                       | _           |  |  |  |

| bit 15                             |            |                |     |                                    |                         |                         | bit 8       |  |  |  |

|                                    |            |                |     |                                    |                         |                         |             |  |  |  |

| U-0                                | U-0        | U-0            | U-0 | U-0                                | R/W-0                   | R/W-0                   | R/W-0       |  |  |  |

| —                                  | —          | —              | _   | —                                  | PCLKDIV2 <sup>(1)</sup> | PCLKDIV1 <sup>(1)</sup> | PCLKDIV0(1) |  |  |  |

| bit 7                              |            |                |     |                                    |                         |                         | bit 0       |  |  |  |

|                                    |            |                |     |                                    |                         |                         |             |  |  |  |

| Legend:                            |            |                |     |                                    |                         |                         |             |  |  |  |

| R = Readable                       | bit        | W = Writable   | bit | U = Unimplemented bit, read as '0' |                         |                         |             |  |  |  |

| -n = Value at POR '1' = Bit is set |            |                |     | '0' = Bit is cle                   | ared                    | x = Bit is unknown      |             |  |  |  |

|                                    |            |                |     |                                    |                         |                         |             |  |  |  |

| bit 15-3                           | Unimplemen | ted: Read as ' | י'  |                                    |                         |                         |             |  |  |  |

#### bit 15-3 Unimplemented: Read as '0'

bit 2-0 PCLKDIV<2:0>: PWMx Input Clock Prescaler (Divider) Select bits<sup>(1)</sup>

- 111 = Reserved 110 = Divide-by-64 101 = Divide-by-32

- 100 = Divide-by-32100 = Divide-by-16

- 011 = Divide-by-8

- 010 = Divide-by-4

- 001 = Divide-by-2

- 000 = Divide-by-1, maximum PWMx timing resolution (power-on default)

- **Note 1:** These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

| R/W-0                                                                | R/W-0    | R/W-0    | U-0             | R/W-0, HC           | R/W-0                | R-0   | R-1   |  |  |

|----------------------------------------------------------------------|----------|----------|-----------------|---------------------|----------------------|-------|-------|--|--|

| UTXISEL1                                                             | UTXINV   | UTXISEL0 | —               | UTXBRK              | UTXEN <sup>(1)</sup> | UTXBF | TRMT  |  |  |

| bit 15                                                               |          |          |                 |                     |                      |       | bit 8 |  |  |

|                                                                      |          |          |                 |                     |                      |       |       |  |  |

| R/W-0                                                                | R/W-0    | R/W-0    | R-1             | R-0                 | R-0                  | R/C-0 | R-0   |  |  |

| URXISEL1                                                             | URXISEL0 | ADDEN    | RIDLE           | PERR                | FERR                 | OERR  | URXDA |  |  |

| bit 7                                                                |          |          |                 |                     |                      |       | bit C |  |  |

|                                                                      |          |          |                 |                     |                      |       |       |  |  |

| Legend: HC = Hardware Clearable bi                                   |          |          | e Clearable bit | t C = Clearable bit |                      |       |       |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |          |          |                 | d as '0'            |                      |       |       |  |  |

| -n = Value at                                                        | •        |          |                 |                     | x = Bit is unki      | nown  |       |  |  |

## REGISTER 20-2: UxSTA: UARTx STATUS AND CONTROL REGISTER

bit 15,13 UTXISEL<1:0>: UARTx Transmission Interrupt Mode Selection bits

- 11 = Reserved; do not use

- 10 = Interrupt when a character is transferred to the Transmit Shift Register (TSR) and as a result, the transmit buffer becomes empty

- 01 = Interrupt when the last character is shifted out of the Transmit Shift Register; all transmit operations are completed

- 00 = Interrupt when a character is transferred to the Transmit Shift Register (this implies there is at least one character open in the transmit buffer)

- bit 14 UTXINV: UARTx Transmit Polarity Inversion bit

- <u>If IREN = 0:</u> 1 = UxTX Idle state is '0'

- 0 = UxTX Idle state is '1'

- If IREN = 1:

- 1 = IrDA encoded, UxTX Idle state is '1'

- 0 = IrDA encoded, UxTX Idle state is '0'

- bit 12 Unimplemented: Read as '0'

- bit 11 UTXBRK: UARTx Transmit Break bit

- 1 = Sends Sync Break on next transmission Start bit, followed by twelve '0' bits, followed by Stop bit; cleared by hardware upon completion

- 0 = Sync Break transmission is disabled or completed

- bit 10 UTXEN: UARTx Transmit Enable bit<sup>(1)</sup> 1 = Transmit is enabled, UxTX pin is controlled by UARTx

- 0 = Transmit is disabled, any pending transmission is aborted and buffer is reset; UxTX pin is controlled by the PORT

- bit 9 UTXBF: UARTx Transmit Buffer Full Status bit (read-only)

- 1 = Transmit buffer is full

- 0 = Transmit buffer is not full, at least one more character can be written

- bit 8 TRMT: Transmit Shift Register Empty bit (read-only)

- 1 = Transmit Shift Register is empty and transmit buffer is empty (the last transmission has completed)

- 0 = Transmit Shift Register is not empty, a transmission is in progress or queued

- bit 7-6 URXISEL<1:0>: UARTx Receive Interrupt Mode Selection bits

- 11 = Interrupt is set on UxRSR transfer, making the receive buffer full (i.e., has 4 data characters)

- 10 = Interrupt is set on UxRSR transfer, making the receive buffer 3/4 full (i.e., has 3 data characters)

- 0x = Interrupt is set when any character is received and transferred from the UxRSR to the receive buffer; receive buffer has one or more characters

- **Note 1:** Refer to the "**UART**" (DS70582) section in the "*dsPIC33/PIC24 Family Reference Manual*" for information on enabling the UARTx module for transmit operation.

| R-0                                                                | R-0 | R-0                          | R-0                                                | R-0                                                                                            | R-0                                                                                       | R-0                                                                                                                  |  |  |

|--------------------------------------------------------------------|-----|------------------------------|----------------------------------------------------|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--|--|

|                                                                    |     | TERR                         | CNT<7:0>                                           |                                                                                                |                                                                                           |                                                                                                                      |  |  |

|                                                                    |     |                              |                                                    |                                                                                                |                                                                                           | bit 8                                                                                                                |  |  |

|                                                                    |     |                              |                                                    |                                                                                                |                                                                                           |                                                                                                                      |  |  |

| R-0                                                                | R-0 | R-0                          | R-0                                                | R-0                                                                                            | R-0                                                                                       | R-0                                                                                                                  |  |  |

|                                                                    |     | RERR                         | CNT<7:0>                                           |                                                                                                |                                                                                           |                                                                                                                      |  |  |

|                                                                    |     |                              |                                                    |                                                                                                |                                                                                           | bit 0                                                                                                                |  |  |

|                                                                    |     |                              |                                                    |                                                                                                |                                                                                           |                                                                                                                      |  |  |

|                                                                    |     |                              |                                                    |                                                                                                |                                                                                           |                                                                                                                      |  |  |

| R = Readable bit W = Writable bit                                  |     |                              | U = Unimplemented bit, read as '0'                 |                                                                                                |                                                                                           |                                                                                                                      |  |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is |     |                              |                                                    | x = Bit is unkr                                                                                | nown                                                                                      |                                                                                                                      |  |  |

|                                                                    | R-0 | R-0 R-0<br>it W = Writable b | TERR<br>R-0 R-0 R-0<br>RERR<br>it W = Writable bit | TERRCNT<7:0>           R-0         R-0         R-0           RERRCNT<7:0>         RERRCNT<7:0> | TERRCNT<7:0>           R-0         R-0         R-0           RERRCNT<7:0>         RERRCNT | TERRCNT<7:0>         R-0       R-0       R-0       R-0         RERRCNT<7:0>       U = Unimplemented bit, read as '0' |  |  |

bit 7-0 **RERRCNT<7:0>:** Receive Error Count bits

#### REGISTER 21-9: CxCFG1: ECANx BAUD RATE CONFIGURATION REGISTER 1

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | _   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| SJW1  | SJW0  | BRP5  | BRP4  | BRP3  | BRP2  | BRP1  | BRP0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-8 | Unimplemented: Read as '0' |

|----------|----------------------------|

|----------|----------------------------|

| bit 7-6 | SJW<1:0>: Synchronization Jump Width bits    |

|---------|----------------------------------------------|

|         | 11 = Length is 4 x TQ                        |

|         | $10 = \text{Length is } 3 \times \text{Tq}$  |

|         | $01 = \text{Length is } 2 \times \text{T} Q$ |

|         | $00 = \text{Length is } 1 \times \text{Tq}$  |

```

bit 5-0 BRP<5:0>: Baud Rate Prescaler bits

```

```

11 1111 = TQ = 2 x 64 x 1/FCAN

```

•

- 00 0010 = TQ = 2 x 3 x 1/FCAN 00 0001 = TQ = 2 x 2 x 1/FCAN

- 00 0000 = Tq = 2 x 1 x 1/FCAN

| R/W-0         | R/W-0                                                                      | R/W-0                                                                                                                      | R/W-0                                          | R/W-0                              | R/W-0                                   | R/W-0  | R/W-0  |  |  |

|---------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|------------------------------------|-----------------------------------------|--------|--------|--|--|

|               | F15B                                                                       | P<3:0>                                                                                                                     |                                                |                                    | F14BI                                   | P<3:0> |        |  |  |

| bit 15        |                                                                            |                                                                                                                            |                                                |                                    |                                         |        | bit 8  |  |  |

| R/W-0         | R/W-0                                                                      | R/W-0                                                                                                                      | R/W-0                                          | R/W-0                              | R/W-0                                   | R/W-0  | R/W-0  |  |  |

| F13BP<3:0>    |                                                                            |                                                                                                                            |                                                |                                    |                                         | P<3:0> | 1010 0 |  |  |

| bit 7         |                                                                            |                                                                                                                            |                                                |                                    |                                         |        | bit 0  |  |  |

| Legend:       |                                                                            |                                                                                                                            |                                                |                                    |                                         |        |        |  |  |

| R = Readabl   | e bit                                                                      | W = Writable                                                                                                               | bit                                            | U = Unimplemented bit, read as '0' |                                         |        |        |  |  |

| -n = Value at | t POR                                                                      | '1' = Bit is set                                                                                                           | :                                              | '0' = Bit is clea                  | '0' = Bit is cleared x = Bit is unknown |        |        |  |  |

| bit 15-12     | 1111 = Filte<br>1110 = Filte                                               | RX Buffer Ma<br>r hits received in<br>r hits received in<br>r hits received in<br>r hits received in<br>r hits received in | n RX FIFO bu<br>n RX Buffer 1<br>n RX Buffer 1 | differ<br>4                        |                                         |        |        |  |  |

| bit 11-8      | F14BP<3:0;                                                                 | RX Buffer Ma                                                                                                               | sk for Filter 1                                | 4 bits (same val                   | ues as bits<15                          | :12>)  |        |  |  |

| bit 7-4       | F13BP<3:0;                                                                 | RX Buffer Ma                                                                                                               | sk for Filter 1                                | 3 bits (same val                   | ues as bits<15                          | :12>)  |        |  |  |

| bit 3-0       | F12BP<3:0>: RX Buffer Mask for Filter 12 bits (same values as bits<15:12>) |                                                                                                                            |                                                |                                    |                                         |        |        |  |  |

#### REGISTER 21-15: CxBUFPNT4: ECANx FILTER 12-15 BUFFER POINTER REGISTER 4

#### REGISTER 21-17: CxRXFnEID: ECANx ACCEPTANCE FILTER n EXTENDED IDENTIFIER REGISTER (n = 0-15)

| R/W-x  | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|--------|-------|-------|-------|-------|-------|-------|-------|

| EID15  | EID14 | EID13 | EID12 | EID11 | EID10 | EID9  | EID8  |

| bit 15 |       |       |       |       |       |       | bit 8 |

|        |       |       |       |       |       |       |       |

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| EID7  | EID6  | EID5  | EID4  | EID3  | EID2  | EID1  | EID0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 15-0 EID<15:0>: Extended Identifier bits

1 = Message address bit, EIDx, must be '1' to match filter

0 = Message address bit, EIDx, must be '0' to match filter

#### REGISTER 21-18: CxFMSKSEL1: ECANx FILTER 7-0 MASK SELECTION REGISTER 1

| R/W-0         | R/W-0       | R/W-0                                                        | R/W-0                                                      | R/W-0                | R/W-0            | R/W-0              | R/W-0  |  |

|---------------|-------------|--------------------------------------------------------------|------------------------------------------------------------|----------------------|------------------|--------------------|--------|--|

| F7MSK<1:0>    |             | F6MS                                                         | K<1:0>                                                     | F5MSK<1:0>           |                  | F4MSK<1:0>         |        |  |

| bit 15        |             | ·                                                            |                                                            |                      |                  |                    | bit    |  |

| R/W-0         | R/W-0       | R/W-0                                                        | R/W-0                                                      | R/W-0                | R/W-0            | R/W-0              | R/W-0  |  |

| F3MS          | SK<1:0>     | F2MS                                                         | K<1:0>                                                     | F1MS                 | K<1:0>           | F0MS               | K<1:0> |  |

| bit 7         |             |                                                              |                                                            |                      |                  |                    | bit (  |  |

| Legend:       |             |                                                              |                                                            |                      |                  |                    |        |  |

| R = Readable  | e bit       | W = Writable                                                 | bit                                                        | U = Unimplen         | nented bit, read | d as '0'           |        |  |

| -n = Value at | POR         | '1' = Bit is set                                             |                                                            | '0' = Bit is cleared |                  | x = Bit is unknown |        |  |

|               | 01 = Accept | red<br>ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg | gisters contain                                            | mask                 |                  |                    |        |  |

| bit 13-12     | F6MSK<1:0   | >: Mask Source                                               | for Filter 6 bit                                           | s (same values       | s as bits<15:14  | >)                 |        |  |

| bit 11-10     | F5MSK<1:0   | >: Mask Source                                               | for Filter 5 bit                                           | s (same values       | s as bits<15:14  | >)                 |        |  |

| bit 9-8       | F4MSK<1:0   | >: Mask Source                                               | for Filter 4 bit                                           | s (same values       | s as bits<15:14  | >)                 |        |  |

| bit 7-6       | F3MSK<1:0   | >: Mask Source                                               | for Filter 3 bit                                           | s (same values       | s as bits<15:14  | >)                 |        |  |

| bit 5-4       | F2MSK<1:0   | >: Mask Source                                               | for Filter 2 bit                                           | s (same values       | s as bits<15:14  | >)                 |        |  |

| bit 3-2       | F1MSK<1:0   | >: Mask Source                                               | Mask Source for Filter 1 bits (same values as bits<15:14>) |                      |                  |                    |        |  |

|               |             |                                                              |                                                            |                      |                  | . )                |        |  |

#### REGISTER 24-12: PTGQPTR: PTG STEP QUEUE POINTER REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0 | U-0   | U-0   | U-0         | U-0   | U-0   |

|--------|-----|-----|-------|-------|-------------|-------|-------|

| —      | —   | —   | —     | —     |             | _     | —     |

| bit 15 |     |     |       |       |             |       | bit 8 |

|        |     |     |       |       |             |       |       |

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0       | R/W-0 | R/W-0 |

| _      |     |     |       |       | PTGQPTR<4:0 | >     |       |

| bit 7  |     |     |       |       |             |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-5 Unimplemented: Read as '0'

bit 4-0 **PTGQPTR<4:0>:** PTG Step Queue Pointer Register bits This register points to the currently active Step command in the Step queue.

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

## **REGISTER 24-13: PTGQUEX: PTG STEP QUEUE REGISTER x (x = 0-7)**<sup>(1,3)</sup>

| R/W-0  | R/W-0 | R/W-0 | R/W-0     | R/W-0                | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-----------|----------------------|-------|-------|-------|

|        |       |       | STEP(2x + | - 1)<7:0> <b>(2)</b> |       |       |       |

| bit 15 |       |       |           |                      |       |       | bit 8 |

|        |       |       |           |                      |       |       |       |

| R/W-0  | R/W-0 | R/W-0 | R/W-0     | R/W-0                | R/W-0 | R/W-0 | R/W-0 |

| R/W-0                        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|------------------------------|-------|-------|-------|-------|-------|-------|-------|

| STEP(2x)<7:0> <sup>(2)</sup> |       |       |       |       |       |       |       |

| bit 7                        |       |       |       |       |       |       |       |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-8 | STEP(2x + 1)<7:0>: PTG Step Queue Pointer Register bits <sup>(2)</sup> |

|----------|------------------------------------------------------------------------|

|          | A queue location for storage of the STEP(2x + 1) command byte.         |

| bit 7-0  | STEP(2x)<7:0>: PTG Step Queue Pointer Register bits <sup>(2)</sup>     |

|          | A queue location for storage of the STEP(2x) command byte.             |

- **Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

- 2: Refer to Table 24-1 for the Step command encoding.

**3:** The Step registers maintain their values on any type of Reset.

| AC CHARACTERISTICS   |                                          |                                             | $\begin{tabular}{ l l l l l l l l l l l l l l l l l l l$ |     |     |     |  |

|----------------------|------------------------------------------|---------------------------------------------|----------------------------------------------------------|-----|-----|-----|--|

| Maximum<br>Data Rate | Master<br>Transmit Only<br>(Half-Duplex) | Master<br>Transmit/Receive<br>(Full-Duplex) | Slave<br>Transmit/Receive<br>(Full-Duplex)               | CKE | СКР | SMP |  |

| 15 MHz               | Table 30-42                              | _                                           | _                                                        | 0,1 | 0,1 | 0,1 |  |

| 10 MHz               | _                                        | Table 30-43                                 | —                                                        | 1   | 0,1 | 1   |  |

| 10 MHz               | —                                        | Table 30-44                                 | —                                                        | 0   | 0,1 | 1   |  |

| 15 MHz               | —                                        | —                                           | Table 30-45                                              | 1   | 0   | 0   |  |

| 11 MHz               | —                                        | —                                           | Table 30-46                                              | 1   | 1   | 0   |  |

| 15 MHz               | _                                        | —                                           | Table 30-47                                              | 0   | 1   | 0   |  |

| 11 MHz               | _                                        | _                                           | Table 30-48                                              | 0   | 0   | 0   |  |

#### TABLE 30-41: SPI1 MAXIMUM DATA/CLOCK RATE SUMMARY

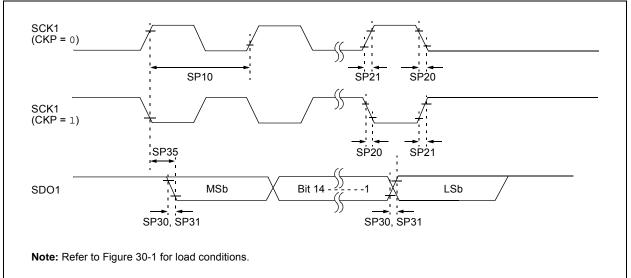

#### FIGURE 30-22: SPI1 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 0) TIMING CHARACTERISTICS

| DC CHARACTERISTICS |                 | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)}^{(1)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |                     |      |        |                                                   |

|--------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------|------|--------|---------------------------------------------------|

| Param<br>No.       | Symbol          | Characteristic                                                                                                                                                                                                                                                                                | Min. | Тур. <sup>(2)</sup> | Max. | Units  | Conditions                                        |

| Compa              | rator AC Ch     | naracteristics                                                                                                                                                                                                                                                                                |      |                     |      |        |                                                   |

| CM10               | TRESP           | Response Time <sup>(3)</sup>                                                                                                                                                                                                                                                                  | —    | 19                  | —    | ns     | V+ input step of 100 mV<br>V- input held at VDD/2 |

| CM11               | Тмс2о∨          | Comparator Mode<br>Change to Output Valid                                                                                                                                                                                                                                                     | —    | -                   | 10   | μs     |                                                   |

| Compa              | rator DC Ch     | naracteristics                                                                                                                                                                                                                                                                                |      |                     |      |        |                                                   |

| CM30               | VOFFSET         | Comparator Offset<br>Voltage                                                                                                                                                                                                                                                                  | —    | ±10                 | 40   | mV     |                                                   |