Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                   |                                                                                |

|---------------------------|--------------------------------------------------------------------------------|

|                           | B abb.                                                                         |

| roduct Status             | Active                                                                         |

| Core Processor            | PIC                                                                            |

| Core Size                 | 16-Bit                                                                         |

| peed                      | 70 MIPs                                                                        |

| onnectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| eripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| lumber of I/O             | 35                                                                             |

| rogram Memory Size        | 32KB (10.7K x 24)                                                              |

| ogram Memory Type         | FLASH                                                                          |

| EPROM Size                | -                                                                              |

| AM Size                   | 2K x 16                                                                        |

| oltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| ata Converters            | A/D 9x10b/12b                                                                  |

| scillator Type            | Internal                                                                       |

| perating Temperature      | -40°C ~ 85°C (TA)                                                              |

| ounting Type              | Surface Mount                                                                  |

| ackage / Case             | 48-UFQFN Exposed Pad                                                           |

| upplier Device Package    | 48-UQFN (6x6)                                                                  |

| urchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep32gp204t-i-mv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

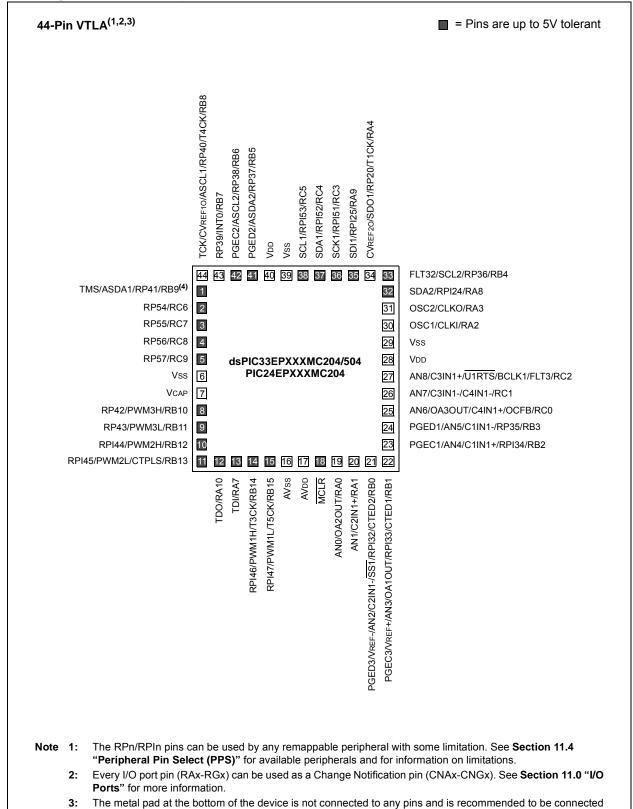

#### Pin Diagrams (Continued)

There is an internal pull-up resistor connected to the TMS pin when the JTAG interface is active. See the

to Vss externally.

JTAGEN bit field in Table 27-2.

### Pin Diagrams (Continued)

TABLE 4-1: CPU CORE REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND dsPIC33EPXXXGP50X DEVICES ONLY (CONTINUED)

| File Name | Addr. | Bit 15 | Bit 14        | Bit 13 | Bit 12 | Bit 11        | Bit 10 | Bit 9   | Bit 8     | Bit 7     | Bit 6 | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | AII<br>Resets |

|-----------|-------|--------|---------------|--------|--------|---------------|--------|---------|-----------|-----------|-------|-------|--------|-------|-------|-------|-------|---------------|

| SR        | 0042  | OA     | ОВ            | SA     | SB     | OAB           | SAB    | DA      | DC        | IPL2      | IPL1  | IPL0  | RA     | N     | OV    | Z     | С     | 0000          |

| CORCON    | 0044  | VAR    | _             | US<    | 1:0>   | EDT           |        | DL<2:0> |           | SATA      | SATB  | SATDW | ACCSAT | IPL3  | SFA   | RND   | IF    | 0020          |

| MODCON    | 0046  | XMODEN | YMODEN        | -      | -      |               | BWM    | <3:0>   |           |           | YWM<  | :3:0> |        |       | XWM<  | <3:0> |       | 0000          |

| XMODSRT   | 0048  |        |               |        |        |               |        | XMO     | DSRT<15:0 | >         |       |       |        |       |       |       | _     | 0000          |

| XMODEND   | 004A  |        |               |        |        | XMODEND<15:0> |        |         |           |           |       |       | _      | 0001  |       |       |       |               |

| YMODSRT   | 004C  |        |               |        |        | YMODSRT<15:0> |        |         |           |           |       |       | _      | 0000  |       |       |       |               |

| YMODEND   | 004E  |        |               |        |        |               |        | YMO     | DEND<15:0 | >         |       |       |        |       |       |       | _     | 0001          |

| XBREV     | 0050  | BREN   |               |        |        |               |        |         | XBF       | REV<14:0> |       |       |        |       |       |       |       | 0000          |

| DISICNT   | 0052  | _      | DISICNT<13:0> |        |        |               |        |         |           |           | 0000  |       |        |       |       |       |       |               |

| TBLPAG    | 0054  | _      | TBLPAG<7:0>   |        |        |               |        |         |           |           | 0000  |       |        |       |       |       |       |               |

| MSTRPR    | 0058  |        |               |        |        |               |        |         | MSTRPR<   | 15:0>     |       |       |        |       |       |       |       | 0000          |

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

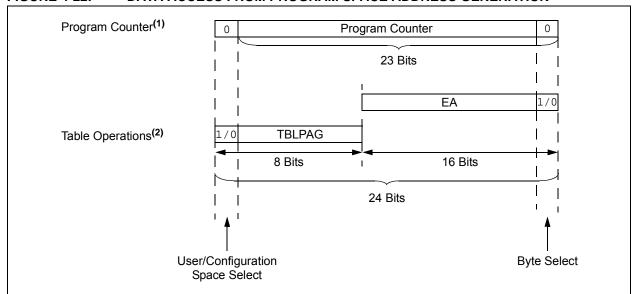

# 4.8 Interfacing Program and Data Memory Spaces

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X architecture uses a 24-bit-wide Program Space (PS) and a 16-bit-wide Data Space (DS). The architecture is also a modified Harvard scheme, meaning that data can also be present in the Program Space. To use this data successfully, it must be accessed in a way that preserves the alignment of information in both spaces.

Aside from normal execution, the architecture of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices provides two methods by which Program Space can be accessed during operation:

- Using table instructions to access individual bytes or words anywhere in the Program Space

- Remapping a portion of the Program Space into the Data Space (Program Space Visibility)

Table instructions allow an application to read or write to small areas of the program memory. This capability makes the method ideal for accessing data tables that need to be updated periodically. It also allows access to all bytes of the program word. The remapping method allows an application to access a large block of data on a read-only basis, which is ideal for look-ups from a large table of static data. The application can only access the least significant word of the program word.

TABLE 4-65: PROGRAM SPACE ADDRESS CONSTRUCTION

| Access Type            | Access        | Program Space Address     |             |                         |               |     |  |  |  |

|------------------------|---------------|---------------------------|-------------|-------------------------|---------------|-----|--|--|--|

| Access Type            | Space         | <23>                      | <22:16>     | <15>                    | <14:1>        | <0> |  |  |  |

| Instruction Access     | User          | 0                         |             | PC<22:1>                | 0             |     |  |  |  |

| (Code Execution)       |               |                           | 0xx xxxx xx | xxx xxxx xxxx xxxx xxx0 |               |     |  |  |  |

| TBLRD/TBLWT            | User          | ТВ                        | LPAG<7:0>   | Data EA<15:0>           |               |     |  |  |  |

| (Byte/Word Read/Write) |               | 0                         | xxx xxxx    | x xxxx xxxx xxxx xxxx   |               |     |  |  |  |

|                        | Configuration | TBLPAG<7:0> Data EA<15:0> |             |                         |               |     |  |  |  |

|                        |               | 1                         | xxx xxxx    | xxxx xx                 | xxx xxxx xxxx |     |  |  |  |

FIGURE 4-22: DATA ACCESS FROM PROGRAM SPACE ADDRESS GENERATION

- **Note 1:** The Least Significant bit (LSb) of Program Space addresses is always fixed as '0' to maintain word alignment of data in the Program and Data Spaces.

- **2:** Table operations are not required to be word-aligned. Table Read operations are permitted in the configuration memory space.

#### 6.1 Reset Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note:

In the event you are not able to access the product page using the link above, enter this URL in your browser:

http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en555464

#### 6.1.1 KEY RESOURCES

- "Reset" (DS70602) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- · Development Tools

## REGISTER 11-6: RPINR11: PERIPHERAL PIN SELECT INPUT REGISTER 11

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|------------|-------|-------|-------|

| _     |       |       |       | OCFAR<6:0> | >     |       |       |

| bit 7 |       |       |       |            |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-7 **Unimplemented:** Read as '0'

bit 6-0 OCFAR<6:0>: Assign Output Compare Fault A (OCFA) to the Corresponding RPn Pin bits

(see Table 11-2 for input pin selection numbers)

1111001 = Input tied to RPI121

:

0000001 = Input tied to CMP1

0000000 = Input tied to Vss

#### 12.1 Timer1 Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note:

In the event you are not able to access the product page using the link above, enter this URL in your browser:

http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en555464

#### 12.1.1 KEY RESOURCES

- "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- · Development Tools

## 16.0 HIGH-SPEED PWM MODULE (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "High-Speed PWM" (DS70645) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices support a dedicated Pulse-Width Modulation (PWM) module with up to 6 outputs.

The high-speed PWMx module consists of the following major features:

- · Three PWM generators

- · Two PWM outputs per PWM generator

- · Individual period and duty cycle for each PWM pair

- Duty cycle, dead time, phase shift and frequency resolution of Tcy/2 (7.14 ns at Fcy = 70MHz)

- Independent Fault and current-limit inputs for six PWM outputs

- · Redundant output

- · Center-Aligned PWM mode

- · Output override control

- Chop mode (also known as Gated mode)

- · Special Event Trigger

- · Prescaler for input clock

- · PWMxL and PWMxH output pin swapping

- Independent PWM frequency, duty cycle and phase-shift changes for each PWM generator

- · Dead-time compensation

- Enhanced Leading-Edge Blanking (LEB) functionality

- · Frequency resolution enhancement

- PWM capture functionality

Note:

In Edge-Aligned PWM mode, the duty cycle, dead time, phase shift and frequency resolution are 8.32 ns.

The high-speed PWMx module contains up to three PWM generators. Each PWM generator provides two PWM outputs: PWMxH and PWMxL. The master time base generator provides a synchronous signal as a common time base to synchronize the various PWM outputs. The individual PWM outputs are available on the output pins of the device. The input Fault signals and current-limit signals, when enabled, can monitor and protect the system by placing the PWM outputs into a known "safe" state.

Each PWMx can generate a trigger to the ADC module to sample the analog signal at a specific instance during the PWM period. In addition, the high-speed PWMx module also generates a Special Event Trigger to the ADC module based on either of the two master time bases.

The high-speed PWMx module can synchronize itself with an external signal or can act as a synchronizing source to any external device. The SYNCI1 input pin that utilizes PPS, can synchronize the high-speed PWMx module with an external signal. The SYNCO1 pin is an output pin that provides a synchronous signal to an external device.

Figure 16-1 illustrates an architectural overview of the high-speed PWMx module and its interconnection with the CPU and other peripherals.

#### 16.1 PWM Faults

The PWMx module incorporates multiple external Fault inputs to include FLT1 and FLT2 which are remappable using the PPS feature, FLT3 and FLT4 which are available only on the larger 44-pin and 64-pin packages, and FLT32 which has been implemented with Class B safety features, and is available on a fixed pin on all dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

These Faults provide a safe and reliable way to safely shut down the PWM outputs when the Fault input is asserted.

#### 16.1.1 PWM FAULTS AT RESET

During any Reset event, the PWMx module maintains ownership of the Class B Fault, FLT32. At Reset, this Fault is enabled in Latched mode to ensure the fail-safe power-up of the application. The application software must clear the PWM Fault before enabling the high-speed motor control PWMx module. To clear the Fault condition, the FLT32 pin must first be pulled low externally or the internal pull-down resistor in the CNPDx register can be enabled.

**Note:** The Fault mode may be changed using the FLTMOD<1:0> bits (FCLCON<1:0>), regardless of the state of FLT32.

#### 16.2 PWM Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note:

In the event you are not able to access the product page using the link above, enter this URL in your browser:

http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en555464

#### 16.2.1 KEY RESOURCES

- "High-Speed PWM" (DS70645) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- · Application Notes

- · Software Libraries

- · Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- · Development Tools

#### REGISTER 16-18: AUXCONX: PWMX AUXILIARY CONTROL REGISTER

| U-0    | U-0 | U-0 | U-0 | R/W-0     | R/W-0     | R/W-0     | R/W-0     |

|--------|-----|-----|-----|-----------|-----------|-----------|-----------|

| _      | _   | _   | _   | BLANKSEL3 | BLANKSEL2 | BLANKSEL1 | BLANKSEL0 |

| bit 15 |     |     |     |           |           |           | bit 8     |

| U-0   | U-0 | R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0   | R/W-0   |

|-------|-----|----------|----------|----------|----------|---------|---------|

| _     | _   | CHOPSEL3 | CHOPSEL2 | CHOPSEL1 | CHOPSEL0 | CHOPHEN | CHOPLEN |

| bit 7 |     |          |          |          |          |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-12 **Unimplemented:** Read as '0'

bit 11-8 BLANKSEL<3:0>: PWMx State Blank Source Select bits

The selected state blank signal will block the current-limit and/or Fault input signals (if enabled via the BCH and BCL bits in the LEBCONx register).

1001 = Reserved

0100 = Reserved

•

•

0011 = PWM3H selected as state blank source

0010 = PWM2H selected as state blank source

0001 = PWM1H selected as state blank source

0000 = No state blanking

bit 7-6 Unimplemented: Read as '0'

bit 5-2 CHOPSEL<3:0>: PWMx Chop Clock Source Select bits

The selected signal will enable and disable (CHOP) the selected PWMx outputs.

1001 = Reserved

•

•

0100 = Reserved

0011 = PWM3H selected as CHOP clock source

0010 = PWM2H selected as CHOP clock source

0001 = PWM1H selected as CHOP clock source

0000 = Chop clock generator selected as CHOP clock source

bit 1 CHOPHEN: PWMxH Output Chopping Enable bit

1 = PWMxH chopping function is enabled

0 = PWMxH chopping function is disabled

bit 0 CHOPLEN: PWMxL Output Chopping Enable bit

1 = PWMxL chopping function is enabled

0 = PWMxL chopping function is disabled

#### REGISTER 21-13: CxBUFPNT2: ECANx FILTER 4-7 BUFFER POINTER REGISTER 2

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-------|-------|-------|-------|

|        | F7BP< | <3:0> |       |       | F6BP  | <3:0> |       |

| bit 15 |       |       |       |       |       |       | bit 8 |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

|       | F5BP< | <3:0> |       |       | F4BP  | <3:0> |       |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-12 F7BP<3:0>: RX Buffer Mask for Filter 7 bits

1111 = Filter hits received in RX FIFO buffer

1110 = Filter hits received in RX Buffer 14

•

0001 = Filter hits received in RX Buffer 1

0000 = Filter hits received in RX Buffer 0

bit 11-8 F6BP<3:0>: RX Buffer Mask for Filter 6 bits (same values as bits<15:12>)

bit 7-4 F5BP<3:0>: RX Buffer Mask for Filter 5 bits (same values as bits<15:12>)

bit 3-0 F4BP<3:0>: RX Buffer Mask for Filter 4 bits (same values as bits<15:12>)

#### REGISTER 21-14: CxBUFPNT3: ECANx FILTER 8-11 BUFFER POINTER REGISTER 3

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 |

|--------|-------|-------|-------|-------|-------|--------|-------|

|        | F11BP | <3:0> |       |       | F10BF | P<3:0> |       |

| bit 15 |       |       |       |       |       |        | bit 8 |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

|       | F9BP< | <3:0> |       |       | F8BP  | <3:0> |       |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-12 F11BP<3:0>: RX Buffer Mask for Filter 11 bits

1111 = Filter hits received in RX FIFO buffer

1110 = Filter hits received in RX Buffer 14

•

0001 = Filter hits received in RX Buffer 1

0000 = Filter hits received in RX Buffer 0

bit 11-8 F10BP<3:0>: RX Buffer Mask for Filter 10 bits (same values as bits<15:12>)

bit 7-4 **F9BP<3:0>:** RX Buffer Mask for Filter 9 bits (same values as bits<15:12>)

bit 3-0 **F8BP<3:0>:** RX Buffer Mask for Filter 8 bits (same values as bits<15:12>)

#### REGISTER 25-2: CMxCON: COMPARATOR x CONTROL REGISTER (x = 1, 2 OR 3)

| R/W-0  | R/W-0              | R/W-0 | U-0 | U-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|--------------------|-------|-----|-----|--------|-------|-------|

| CON    | COE <sup>(2)</sup> | CPOL  | _   | _   | OPMODE | CEVT  | COUT  |

| bit 15 |                    |       |     |     |        |       | bit 8 |

| R/W-0  | R/W-0  | U-0 | R/W-0               | U-0 | U-0 | R/W-0               | R/W-0               |

|--------|--------|-----|---------------------|-----|-----|---------------------|---------------------|

| EVPOL1 | EVPOL0 | _   | CREF <sup>(1)</sup> | _   | _   | CCH1 <sup>(1)</sup> | CCH0 <sup>(1)</sup> |

| bit 7  |        |     |                     |     |     |                     | bit 0               |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 CON: Op Amp/Comparator Enable bit

1 = Op amp/comparator is enabled

0 = Op amp/comparator is disabled

bit 14 **COE**: Comparator Output Enable bit<sup>(2)</sup>

1 = Comparator output is present on the CxOUT pin

0 = Comparator output is internal only

bit 13 **CPOL:** Comparator Output Polarity Select bit

1 = Comparator output is inverted

0 = Comparator output is not inverted

bit 12-11 Unimplemented: Read as '0'

bit 10 **OPMODE:** Op Amp/Comparator Operation Mode Select bit

1 = Circuit operates as an op amp

0 = Circuit operates as a comparator

bit 9 **CEVT:** Comparator Event bit

1 = Comparator event according to the EVPOL<1:0> settings occurred; disables future triggers and interrupts until the bit is cleared

0 = Comparator event did not occur

bit 8 **COUT**: Comparator Output bit

When CPOL = 0 (non-inverted polarity):

1 = VIN+ > VIN-

0 = VIN+ < VIN-

When CPOL = 1 (inverted polarity):

1 = VIN+ < VIN-

0 = VIN+ > VIN-

**Note 1:** Inputs that are selected and not available will be tied to Vss. See the "**Pin Diagrams**" section for available inputs for each package.

2: This output is not available when OPMODE (CMxCON<10>) = 1.

# REGISTER 25-5: CMxMSKCON: COMPARATOR x MASK GATING CONTROL REGISTER (CONTINUED)

bit 3 ABEN: AND Gate B Input Enable bit

1 = MBI is connected to AND gate

0 = MBI is not connected to AND gate

bit 2 ABNEN: AND Gate B Input Inverted Enable bit 1 = Inverted MBI is connected to AND gate

0 = Inverted MBI is not connected to AND gate

bit 1 AAEN: AND Gate A Input Enable bit

1 = MAI is connected to AND gate

0 = MAI is not connected to AND gate

bit 0 AANEN: AND Gate A Input Inverted Enable bit

1 = Inverted MAI is connected to AND gate0 = Inverted MAI is not connected to AND gate

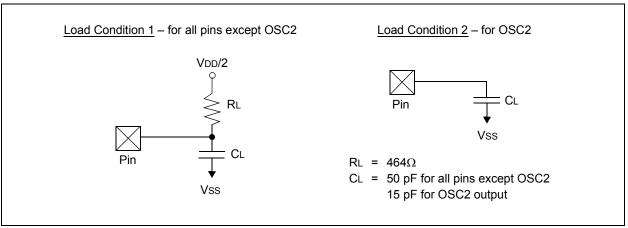

# 30.2 AC Characteristics and Timing Parameters

This section defines dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X AC characteristics and timing parameters.

TABLE 30-15: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

|                    | Standard Operating Conditions: 3.0V to 3.6V                  |  |  |  |  |  |

|--------------------|--------------------------------------------------------------|--|--|--|--|--|

|                    | (unless otherwise stated)                                    |  |  |  |  |  |

| AC CHARACTERISTICS | Operating temperature -40°C ≤ TA ≤ +85°C for Industrial      |  |  |  |  |  |

| AC CHARACTERISTICS | -40°C ≤ TA ≤ +125°C for Extended                             |  |  |  |  |  |

|                    | Operating voltage VDD range as described in Section 30.1 "DC |  |  |  |  |  |

|                    | Characteristics".                                            |  |  |  |  |  |

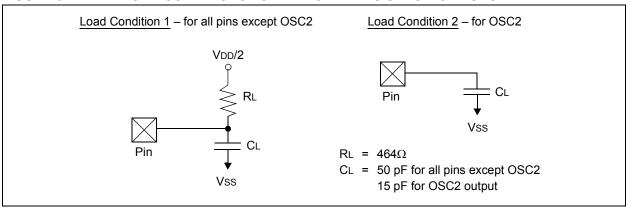

#### FIGURE 30-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

#### TABLE 30-16: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

| Param<br>No. | Symbol | Characteristic        | Min. | Тур. | Max. | Units | Conditions                                                    |

|--------------|--------|-----------------------|------|------|------|-------|---------------------------------------------------------------|

| DO50         | Cosco  | OSC2 Pin              | _    | _    | 15   | pF    | In XT and HS modes, when external clock is used to drive OSC1 |

| DO56         | Сю     | All I/O Pins and OSC2 | _    | _    | 50   | pF    | EC mode                                                       |

| DO58         | Св     | SCLx, SDAx            | _    | _    | 400  | pF    | In I <sup>2</sup> C™ mode                                     |

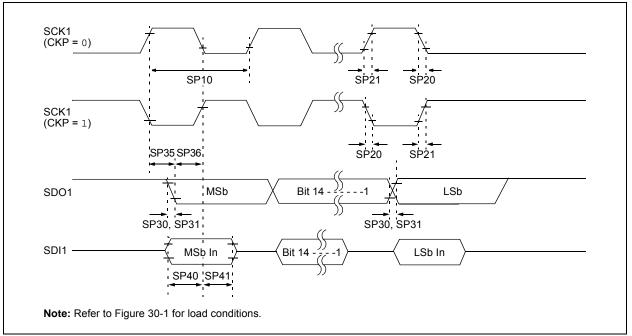

FIGURE 30-25: SPI1 MASTER MODE (FULL-DUPLEX, CKE = 0, CKP = x, SMP = 1) TIMING CHARACTERISTICS

TABLE 30-44: SPI1 MASTER MODE (FULL-DUPLEX, CKE = 0, CKP = x, SMP = 1) TIMING REQUIREMENTS

|                    |                       | ING INEGUINEINEINIG                        |           |                                                                                                                                                                                                                                                 |      |       |                             |

|--------------------|-----------------------|--------------------------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-----------------------------|

| AC CHARACTERISTICS |                       |                                            | (unless o | Standard Operating Conditions: 3.0V to 3.6V unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |      |       |                             |

| Param.             | Symbol                | Characteristic <sup>(1)</sup>              | Min.      | Typ. <sup>(2)</sup>                                                                                                                                                                                                                             | Max. | Units | Conditions                  |

| SP10               | FscP                  | Maximum SCK1 Frequency                     | _         | _                                                                                                                                                                                                                                               | 10   | MHz   | -40°C to +125°C<br>(Note 3) |

| SP20               | TscF                  | SCK1 Output Fall Time                      | _         | _                                                                                                                                                                                                                                               | _    | ns    | See Parameter DO32 (Note 4) |

| SP21               | TscR                  | SCK1 Output Rise Time                      | _         | _                                                                                                                                                                                                                                               | _    | ns    | See Parameter DO31 (Note 4) |

| SP30               | TdoF                  | SDO1 Data Output Fall Time                 | _         | _                                                                                                                                                                                                                                               | _    | ns    | See Parameter DO32 (Note 4) |

| SP31               | TdoR                  | SDO1 Data Output Rise Time                 | _         | _                                                                                                                                                                                                                                               | _    | ns    | See Parameter DO31 (Note 4) |

| SP35               | TscH2doV,<br>TscL2doV | SDO1 Data Output Valid after SCK1 Edge     | _         | 6                                                                                                                                                                                                                                               | 20   | ns    |                             |

| SP36               | TdoV2scH,<br>TdoV2scL | SDO1 Data Output Setup to First SCK1 Edge  | 30        | _                                                                                                                                                                                                                                               | _    | ns    |                             |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDI1 Data Input to SCK1 Edge | 30        | _                                                                                                                                                                                                                                               | _    | ns    |                             |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDI1 Data Input to SCK1 Edge  | 30        | _                                                                                                                                                                                                                                               | _    | ns    |                             |

- Note 1: These parameters are characterized, but are not tested in manufacturing.

- 2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

- 3: The minimum clock period for SCK1 is 100 ns. The clock generated in Master mode must not violate this specification.

- 4: Assumes 50 pF load on all SPI1 pins.

## 31.2 AC Characteristics and Timing Parameters

The information contained in this section defines dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X AC characteristics and timing parameters for high-temperature devices. However, all AC timing specifications in this section are the same as those in **Section 30.2 "AC Characteristics and Timing Parameters"**, with the exception of the parameters listed in this section.

Parameters in this section begin with an H, which denotes High temperature. For example, Parameter OS53 in **Section 30.2** "AC Characteristics and Timing Parameters" is the Industrial and Extended temperature equivalent of HOS53.

TABLE 31-9: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

| AC CHARACTERISTICS | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) |  |  |  |  |  |

|--------------------|-----------------------------------------------------------------------|--|--|--|--|--|

| AC CHARACTERISTICS | Operating temperature -40°C ≤ TA ≤ +150°C                             |  |  |  |  |  |

|                    | Operating voltage VDD range as described in Table 31-1.               |  |  |  |  |  |

#### FIGURE 31-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

TABLE 31-10: PLL CLOCK TIMING SPECIFICATIONS

| AC CHARACTERISTICS |        |                                        | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +150^{\circ}\text{C}$ |     |     |       |                             |

|--------------------|--------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------|-----------------------------|

| Param<br>No.       | Symbol | Characteristic                         | Min                                                                                                                                                      | Тур | Max | Units | Conditions                  |

| HOS53              | DCLK   | CLKO Stability (Jitter) <sup>(1)</sup> | -5                                                                                                                                                       | 0.5 | 5   | %     | Measured over 100 ms period |

Note 1: These parameters are characterized by similarity, but are not tested in manufacturing. This specification is based on clock cycle by clock cycle measurements. To calculate the effective jitter for individual time bases or communication clocks use this formula:

$$Peripheral Clock Jitter = \frac{DCLK}{\sqrt{\frac{FOSC}{Peripheral Bit Rate Clock}}}$$

For example: Fosc = 32 MHz, Dclk = 5%, SPIx bit rate clock (i.e., SCKx) is 2 MHz.

SPI SCK Jitter =

$$\left[ \frac{DCLK}{\sqrt{\left(\frac{32 \ MHz}{2 \ MHz}\right)}} \right] = \left[ \frac{5\%}{\sqrt{16}} \right] = \left[ \frac{5\%}{4} \right] = 1.25\%$$

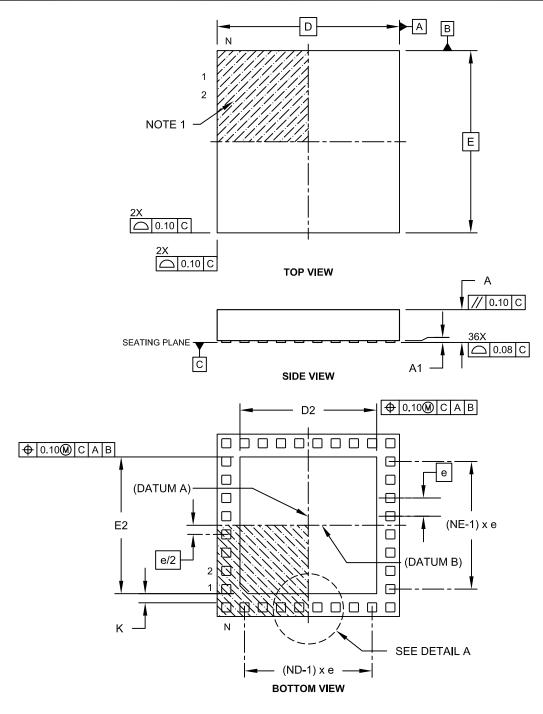

# 36-Terminal Very Thin Thermal Leadless Array Package (TL) – 5x5x0.9 mm Body with Exposed Pad [VTLA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-187C Sheet 1 of 2

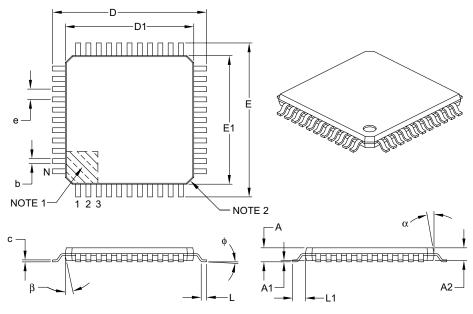

## 44-Lead Plastic Thin Quad Flatpack (PT) – 10x10x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          |                  | MILLIMETERS |          |      |  |

|--------------------------|------------------|-------------|----------|------|--|

| Dimensi                  | Dimension Limits |             |          | MAX  |  |

| Number of Leads          | N                |             | 44       |      |  |

| Lead Pitch               | е                |             | 0.80 BSC |      |  |

| Overall Height           | Α                | _           | _        | 1.20 |  |

| Molded Package Thickness | A2               | 0.95        | 1.00     | 1.05 |  |

| Standoff                 | A1               | 0.05        | _        | 0.15 |  |

| Foot Length              | L                | 0.45        | 0.60     | 0.75 |  |

| Footprint                | L1               | 1.00 REF    |          |      |  |

| Foot Angle               | ф                | 0°          | 3.5°     | 7°   |  |

| Overall Width            | E                | 12.00 BSC   |          |      |  |

| Overall Length           | D                | 12.00 BSC   |          |      |  |

| Molded Package Width     | E1               | 10.00 BSC   |          |      |  |

| Molded Package Length    | D1               | 10.00 BSC   |          |      |  |

| Lead Thickness           | С                | 0.09        | _        | 0.20 |  |

| Lead Width               | b                | 0.30        | 0.37     | 0.45 |  |

| Mold Draft Angle Top     | α                | 11°         | 12°      | 13°  |  |

| Mold Draft Angle Bottom  | β                | 11°         | 12°      | 13°  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Chamfers at corners are optional; size may vary.

- 3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-076B

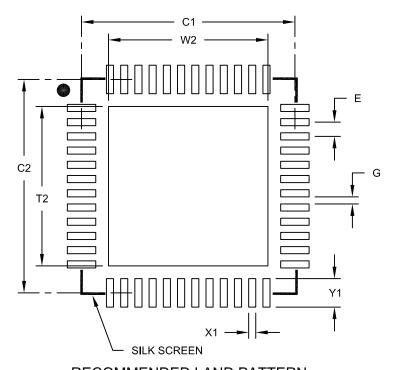

# 48-Lead Ultra Thin Plastic Quad Flat, No Lead Package (MV) - 6x6 mm Body [UQFN] With 0.40 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                            | N   | MILLIMETERS |      |      |  |

|----------------------------|-----|-------------|------|------|--|

| Dimension                  | MIN | NOM         | MAX  |      |  |

| Contact Pitch              |     | 0.40 BSC    |      |      |  |

| Optional Center Pad Width  | W2  |             |      | 4.45 |  |

| Optional Center Pad Length | T2  |             |      | 4.45 |  |

| Contact Pad Spacing        | C1  |             | 6.00 |      |  |

| Contact Pad Spacing        | C2  |             | 6.00 |      |  |

| Contact Pad Width (X28)    | X1  |             |      | 0.20 |  |

| Contact Pad Length (X28)   | Y1  |             |      | 0.80 |  |

| Distance Between Pads      | G   | 0.20        |      |      |  |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2153A

| ECAN Module                                  |          | Instruction Set                             |      |

|----------------------------------------------|----------|---------------------------------------------|------|

| Control Registers                            | 290      | Overview                                    | 390  |

| Modes of Operation                           | 289      | Summary                                     | 387  |

| Overview                                     | 287      | Symbols Used in Opcode Descriptions         | 388  |

| Resources                                    | 289      | Inter-Integrated Circuit (I <sup>2</sup> C) | 273  |

| Electrical Characteristics                   | 401      | Control Registers                           |      |

| AC                                           | 413, 471 | Resources                                   |      |

| Enhanced CAN (ECAN) Module                   |          | Internal RC Oscillator                      |      |

| Equations                                    |          | Use with WDT                                | 385  |

| Device Operating Frequency                   | 154      | Internet Address                            |      |

| FPLLO Calculation                            |          | Interrupt Controller                        | 02-7 |

| FVCO Calculation                             |          | •                                           | 121  |

|                                              |          | Control and Status Registers                |      |

| Errata                                       | 23       | INTCON1                                     |      |

| F                                            |          | INTCON2                                     |      |

| Filter Organitar (O===) Organifications      | 400      | INTCON3                                     |      |

| Filter Capacitor (CEFC) Specifications       |          | INTCON4                                     |      |

| Flash Program Memory                         |          | INTTREG                                     |      |

| Control Registers                            |          | Interrupt Vector Details                    |      |

| Programming Operations                       |          | Interrupt Vector Table (IVT)                | 127  |

| Resources                                    |          | Reset Sequence                              | 127  |

| RTSP Operation                               | 120      | Resources                                   | 131  |

| Table Instructions                           | 119      | _                                           |      |

| Flexible Configuration                       | 379      | J                                           |      |

| _                                            |          | JTAG Boundary Scan Interface                | 379  |

| G                                            |          | JTAG Interface                              |      |

| Guidelines for Getting Started               | 29       | o in Contact                                |      |

| Application Examples                         |          | M                                           |      |

| Basic Connection Requirements                |          | Memory Maps                                 |      |

|                                              |          | · ·                                         | 100  |

| CPU Logic Filter Capacitor Connection (VCAP) |          | Extended Data Space                         |      |

| Decoupling Capacitors                        |          | Memory Organization                         |      |

| External Oscillator Pins                     |          | Resources                                   |      |

| ICSP Pins                                    |          | Microchip Internet Web Site                 |      |

| Master Clear (MCLR) Pin                      |          | Modulo Addressing                           |      |

| Oscillator Value Conditions on Start-up      | 32       | Applicability                               | 115  |

| Unused I/Os                                  | 32       | Operation Example                           | 114  |

|                                              |          | Start and End Address                       | 114  |

| Н                                            |          | W Address Register Selection                | 114  |

| High-Speed PWM                               | 225      | MPLAB Assembler, Linker, Librarian          |      |

| Control Registers                            | 230      | MPLAB ICD 3 In-Circuit Debugger             |      |

| Faults                                       |          | MPLAB PM3 Device Programmer                 |      |

| Resources                                    |          | MPLAB REAL ICE In-Circuit Emulator System   |      |

| High-Temperature Electrical Characteristics  |          | MPLAB X Integrated Development              | 000  |

| Absolute Maximum Ratings                     |          | • '                                         | 207  |

| Absolute Maximum Natings                     | 407      | Environment Software                        |      |

|                                              |          | MPLAB X SIM Software Simulator              |      |

| I/O Ports                                    | 170      | MPLIB Object Librarian                      |      |

|                                              | 173      | MPLINK Object Linker                        | 398  |

| Helpful Tips                                 |          | 0                                           |      |

| Parallel I/O (PIO)                           |          | 0                                           |      |

| Resources                                    |          | Op Amp                                      |      |

| Write/Read Timing                            |          | Application Considerations                  | 358  |

| In-Circuit Debugger                          | 386      | Configuration A                             | 358  |

| In-Circuit Emulation                         | 379      | Configuration B                             | 359  |

| In-Circuit Serial Programming (ICSP)         | 379, 386 | Op Amp/Comparator                           |      |

| Input Capture                                |          | Control Registers                           |      |

| Control Registers                            |          | Resources                                   |      |

| Resources                                    |          | Open-Drain Configuration                    |      |

| Input Change Notification (ICN)              |          |                                             | 174  |

|                                              |          | Oscillator                                  | 450  |

| Instruction Addressing Modes                 |          | Control Registers                           |      |

| File Register Instructions                   |          | Resources                                   |      |

| Fundamental Modes Supported                  |          | Output Compare                              | 219  |

| MAC Instructions                             |          | Control Registers                           | 221  |

| MCU Instructions                             |          | Resources                                   | 220  |

| Move and Accumulator Instructions            | 113      |                                             |      |

| Other Instructions                           | 113      |                                             |      |