Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

⊡XFI

| 2 0 0 0 0 0                |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 60 MIPs                                                                       |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                 |

| Number of I/O              | 21                                                                            |

| Program Memory Size        | 32KB (10.7K x 24)                                                             |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | · ·                                                                           |

| RAM Size                   | 2K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 6x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-VQFN Exposed Pad                                                           |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep32mc202-e-mm |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

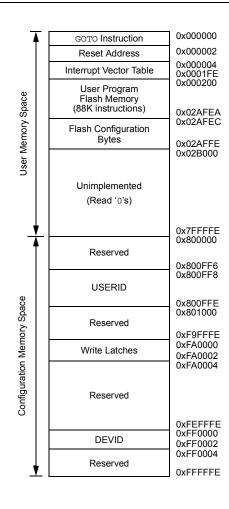

#### FIGURE 4-4: PROGRAM MEMORY MAP FOR dsPIC33EP256GP50X, dsPIC33EP256MC20X/50X AND PIC24EP256GP/MC20X DEVICES

Note: Memory areas are not shown to scale.

| TABLE        | 4-2:  | CPU C  | CORE RE      | EGISTER | R MAP F | FOR PIC | 24EPX) | XGP/M | C20X D   | EVICES   | ONLY   |       |           |          |       |       |       |               |

|--------------|-------|--------|--------------|---------|---------|---------|--------|-------|----------|----------|--------|-------|-----------|----------|-------|-------|-------|---------------|

| File<br>Name | Addr. | Bit 15 | Bit 14       | Bit 13  | Bit 12  | Bit 11  | Bit 10 | Bit 9 | Bit 8    | Bit 7    | Bit 6  | Bit 5 | Bit 4     | Bit 3    | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| W0           | 0000  |        | W0 (WREG) x2 |         |         |         |        |       |          |          |        |       |           |          |       |       | xxxx  |               |

| W1           | 0002  |        | W1 x2        |         |         |         |        |       |          |          |        |       |           |          |       | xxxx  |       |               |

| W2           | 0004  |        | W2 xxx       |         |         |         |        |       |          |          |        |       |           |          |       | xxxx  |       |               |

| W3           | 0006  |        | W3 xxx       |         |         |         |        |       |          |          |        |       |           |          | xxxx  |       |       |               |

| W4           | 0008  |        |              |         |         |         |        |       | W4       |          |        |       |           |          |       |       |       | xxxx          |

| W5           | 000A  |        |              |         |         |         |        |       | W5       |          |        |       |           |          |       |       |       | xxxx          |

| W6           | 000C  |        |              |         |         |         |        |       | W6       |          |        |       |           |          |       |       |       | xxxx          |

| W7           | 000E  |        |              |         |         |         |        |       | W7       |          |        |       |           |          |       |       |       | xxxx          |

| W8           | 0010  |        |              |         |         |         |        |       | W8       |          |        |       |           |          |       |       |       | xxxx          |

| W9           | 0012  |        |              |         |         |         |        |       | W9       |          |        |       |           |          |       |       |       | xxxx          |

| W10          | 0014  |        |              |         |         |         |        |       | W10      |          |        |       |           |          |       |       |       | xxxx          |

| W11          | 0016  |        |              |         |         |         |        |       | W11      |          |        |       |           |          |       |       |       | xxxx          |

| W12          | 0018  |        |              |         |         |         |        |       | W12      |          |        |       |           |          |       |       |       | xxxx          |

| W13          | 001A  |        |              |         |         |         |        |       | W13      |          |        |       |           |          |       |       |       | xxxx          |

| W14          | 001C  |        |              |         |         |         |        |       | W14      |          |        |       |           |          |       |       |       | xxxx          |

| W15          | 001E  |        |              |         |         |         |        |       | W15      |          |        |       |           |          |       |       |       | xxxx          |

| SPLIM        | 0020  |        |              |         |         |         |        |       | SPLIM<1  | 5:0>     |        |       |           |          |       |       |       | 0000          |

| PCL          | 002E  |        |              |         |         |         |        | P     | CL<15:1> |          |        |       |           |          |       |       | —     | 0000          |

| PCH          | 0030  | —      | -            | _       | _       | —       | —      | —     | —        | _        |        |       |           | PCH<6:0> |       |       |       | 0000          |

| DSRPAG       | 0032  | —      | -            | _       | _       | —       | —      |       |          |          |        | DSRPA | G<9:0>    |          |       |       |       | 0001          |

| DSWPAG       | 0034  | _      |              |         |         | _       |        | _     |          |          |        | DS    | SWPAG<8:0 | >        |       |       |       | 0001          |

| RCOUNT       | 0036  |        |              |         |         |         |        |       | RCOUNT<  | 15:0>    |        |       |           |          |       |       |       | 0000          |

| SR           | 0042  | _      |              |         |         | —       |        | _     | DC       | IPL2     | IPL1   | IPL0  | RA        | N        | OV    | Z     | С     | 0000          |

| CORCON       | 0044  | VAR    | _            | -       | _       | —       |        | —     | _        | -        | _      | —     | -         | IPL3     | SFA   | —     | _     | 0020          |

| DISICNT      | 0052  | _      | _            |         |         |         |        |       |          | DISICNT< | :13:0> |       |           |          |       |       |       | 0000          |

| TBLPAG       | 0054  | _      | _            | -       | -       | —       |        | —     | _        |          |        |       | TBLPA     | G<7:0>   |       |       |       | 0000          |

| MSTRPR       | 0058  |        |              |         |         |         |        |       | MSTRPR<  | 15:0>    |        |       |           |          |       |       |       | 0000          |

#### **D** I -4.0 - -

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

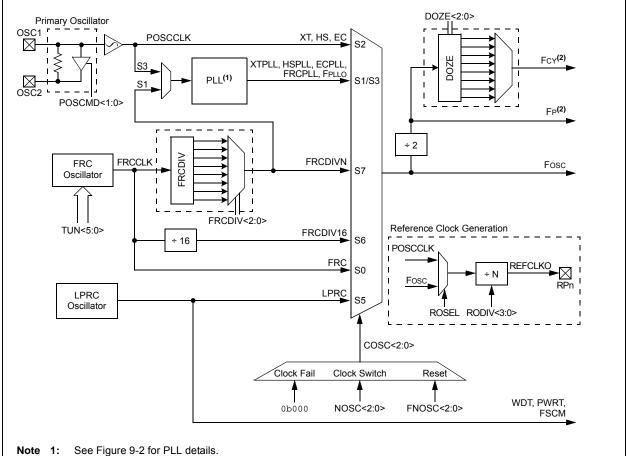

## 9.0 OSCILLATOR CONFIGURATION

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Oscillator" (DS70580) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X oscillator system provides:

- On-chip Phase-Locked Loop (PLL) to boost internal operating frequency on select internal and external oscillator sources

- On-the-fly clock switching between various clock sources

- · Doze mode for system power savings

- Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown

- Configuration bits for clock source selection

- A simplified diagram of the oscillator system is shown in Figure 9-1.

## FIGURE 9-1: OSCILLATOR SYSTEM DIAGRAM

2: The term, FP, refers to the clock source for all peripherals, while FCY refers to the clock source for the CPU. Throughout this document, FCY and FP are used interchangeably, except in the case of Doze mode. FP and FCY will be different when Doze mode is used with a doze ratio of 1:2 or lower.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0     | U-0 | U-0   | U-0   | U-0   | U-0   | U-0   | U-0   |

|---------|-----|-------|-------|-------|-------|-------|-------|

| —       | —   | —     | —     | —     | —     | —     | —     |

| bit 15  |     |       |       |       |       |       | bit 8 |

|         |     |       |       |       |       |       |       |

| U-0     | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| —       | —   | TUN5  | TUN4  | TUN3  | TUN2  | TUN1  | TUN0  |

| bit 7   |     |       |       |       |       |       | bit 0 |

|         |     |       |       |       |       |       |       |

| Logondi |     |       |       |       |       |       |       |

#### REGISTER 9-4: OSCTUN: FRC OSCILLATOR TUNING REGISTER

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-6 Unimplemented: Read as '0'

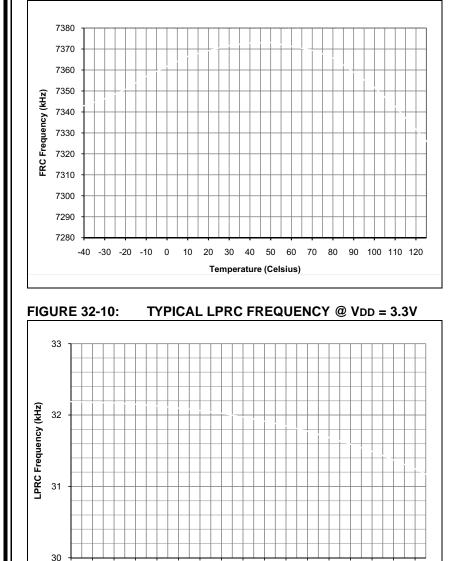

bit 5-0 **TUN<5:0>:** FRC Oscillator Tuning bits 011111 = Maximum frequency deviation of 1.453% (7.477 MHz) 011110 = Center frequency + 1.406% (7.474 MHz) •••• 000001 = Center frequency + 0.047% (7.373 MHz) 000000 = Center frequency (7.37 MHz nominal) 111111 = Center frequency - 0.047% (7.367 MHz) ••• 100001 = Center frequency - 1.453% (7.263 MHz) 100000 = Minimum frequency deviation of -1.5% (7.259 MHz)

- g) The TRISx registers control only the digital I/O output buffer. Any other dedicated or remappable active "output" will automatically override the TRIS setting. The TRISx register does not control the digital logic "input" buffer. Remappable digital "inputs" do not automatically override TRIS settings, which means that the TRISx bit must be set to input for pins with only remappable input function(s) assigned

- h) All analog pins are enabled by default after any Reset and the corresponding digital input buffer on the pin has been disabled. Only the Analog Pin Select registers control the digital input buffer, *not* the TRISx register. The user must disable the analog function on a pin using the Analog Pin Select registers in order to use any "digital input(s)" on a corresponding pin, no exceptions.

## 11.6 I/O Ports Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

#### 11.6.1 KEY RESOURCES

- "I/O Ports" (DS70598) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

## 13.0 TIMER2/3 AND TIMER4/5

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70362) of the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The Timer2/3 and Timer4/5 modules are 32-bit timers, which can also be configured as four independent 16-bit timers with selectable operating modes.

As 32-bit timers, Timer2/3 and Timer4/5 operate in three modes:

- Two Independent 16-Bit Timers (e.g., Timer2 and Timer3) with all 16-Bit Operating modes (except Asynchronous Counter mode)

- Single 32-Bit Timer

- Single 32-Bit Synchronous Counter

- They also support these features:

- Timer Gate Operation

- Selectable Prescaler Settings

- Timer Operation during Idle and Sleep modes

- Interrupt on a 32-Bit Period Register Match

- Time Base for Input Capture and Output Compare Modules (Timer2 and Timer3 only)

- ADC1 Event Trigger (32-bit timer pairs, and Timer3 and Timer5 only)

Individually, all four of the 16-bit timers can function as synchronous timers or counters. They also offer the features listed previously, except for the event trigger; this is implemented only with Timer2/3. The operating modes and enabled features are determined by setting the appropriate bit(s) in the T2CON, T3CON, and T4CON, T5CON registers. T2CON and T4CON are shown in generic form in Register 13-1. T3CON and T5CON are shown in Register 13-2.

For 32-bit timer/counter operation, Timer2 and Timer4 are the least significant word (lsw); Timer3 and Timer5 are the most significant word (msw) of the 32-bit timers.

Note: For 32-bit operation, T3CON and T5CON control bits are ignored. Only T2CON and T4CON control bits are used for setup and control. Timer2 and Timer4 clock and gate inputs are utilized for the 32-bit timer modules, but an interrupt is generated with the Timer3 and Timer5 interrupt flags.

A block diagram for an example 32-bit timer pair (Timer2/3 and Timer4/5) is shown in Figure 13-3.

Note: Only Timer2, 3, 4 and 5 can trigger a DMA data transfer.

## 14.1 Input Capture Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 14.1.1 KEY RESOURCES

- "Input Capture" (DS70352) in the "dsPIC33/ PIC24 Family Reference Manual"

- · Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

| R/W-0        | R/W-0                                                                                                    | R/W-0                              | R/W-0          | U-0               | U-0                 | U-0              | U-0          |  |  |  |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------------|------------------------------------|----------------|-------------------|---------------------|------------------|--------------|--|--|--|--|--|--|

|              | TRGD                                                                                                     | V<3:0>                             |                | —                 |                     | —                | _            |  |  |  |  |  |  |

| bit 15       |                                                                                                          |                                    |                |                   |                     |                  | bit 8        |  |  |  |  |  |  |

|              |                                                                                                          |                                    |                |                   |                     |                  |              |  |  |  |  |  |  |

| U-0          | U-0                                                                                                      | R/W-0                              | R/W-0          | R/W-0             | R/W-0               | R/W-0            | R/W-0        |  |  |  |  |  |  |

| _            |                                                                                                          |                                    |                | TRGSTF            | RT<5:0> <b>(1)</b>  |                  |              |  |  |  |  |  |  |

| bit 7        |                                                                                                          |                                    |                |                   |                     |                  | bit          |  |  |  |  |  |  |

|              |                                                                                                          |                                    |                |                   |                     |                  |              |  |  |  |  |  |  |

| Legend:      | 1. 1.4                                                                                                   |                                    |                |                   |                     |                  |              |  |  |  |  |  |  |

| R = Readab   |                                                                                                          | W = Writable                       |                | •                 | nented bit, read    |                  |              |  |  |  |  |  |  |

| -n = Value a | t POR                                                                                                    | '1' = Bit is set                   |                | '0' = Bit is clea | ared                | x = Bit is unkn  | own          |  |  |  |  |  |  |

|              |                                                                                                          |                                    |                |                   |                     |                  |              |  |  |  |  |  |  |

| bit 15-12    |                                                                                                          | <b>)&gt;:</b> Trigger # Ou         | -              |                   |                     |                  |              |  |  |  |  |  |  |

|              | 1111 = Trigger output for every 16th trigger event                                                       |                                    |                |                   |                     |                  |              |  |  |  |  |  |  |

|              | 1110 = Trigger output for every 15th trigger event                                                       |                                    |                |                   |                     |                  |              |  |  |  |  |  |  |

|              | 1101 = Trigger output for every 14th trigger event<br>1100 = Trigger output for every 13th trigger event |                                    |                |                   |                     |                  |              |  |  |  |  |  |  |

|              | 1100 = Irigger output for every 13th trigger event<br>1011 = Trigger output for every 12th trigger event |                                    |                |                   |                     |                  |              |  |  |  |  |  |  |

|              | 1011 = Trigger output for every 12th trigger event<br>1010 = Trigger output for every 11th trigger event |                                    |                |                   |                     |                  |              |  |  |  |  |  |  |

|              |                                                                                                          | ger output for ev                  |                |                   |                     |                  |              |  |  |  |  |  |  |

|              |                                                                                                          | per output for ev                  |                |                   |                     |                  |              |  |  |  |  |  |  |

|              |                                                                                                          | per output for ev                  |                |                   |                     |                  |              |  |  |  |  |  |  |

|              |                                                                                                          | ger output for ev                  |                |                   |                     |                  |              |  |  |  |  |  |  |

|              |                                                                                                          | ger output for ev                  |                |                   |                     |                  |              |  |  |  |  |  |  |

|              | 0100 = Trigger output for every 5th trigger event                                                        |                                    |                |                   |                     |                  |              |  |  |  |  |  |  |

|              |                                                                                                          | ger output for ev                  |                |                   |                     |                  |              |  |  |  |  |  |  |

|              | 0010 = Trigger output for every 3rd trigger event                                                        |                                    |                |                   |                     |                  |              |  |  |  |  |  |  |

|              |                                                                                                          | ger output for ev                  |                |                   |                     |                  |              |  |  |  |  |  |  |

|              | 0000 = Trigg                                                                                             | ger output for ev                  | ery trigger ev | ent               |                     |                  |              |  |  |  |  |  |  |

| bit 11-6     | -                                                                                                        | nted: Read as '                    |                |                   |                     |                  |              |  |  |  |  |  |  |

| bit 5-0      | TRGSTRT<                                                                                                 | 5:0>: Trigger Po                   | stscaler Start | Enable Select     | bits <sup>(1)</sup> |                  |              |  |  |  |  |  |  |

|              | 111111 = Waits 63 PWM cycles before generating the first trigger event after the module is enabled       |                                    |                |                   |                     |                  |              |  |  |  |  |  |  |

|              |                                                                                                          |                                    |                |                   |                     |                  |              |  |  |  |  |  |  |

|              | •                                                                                                        |                                    |                | ·                 |                     |                  |              |  |  |  |  |  |  |

|              | •                                                                                                        |                                    |                | -                 |                     |                  |              |  |  |  |  |  |  |

|              | •                                                                                                        |                                    |                | -                 |                     |                  |              |  |  |  |  |  |  |

|              | •<br>•<br>•                                                                                              | aits 2 PW/M ava                    | les hefore co  | nerating the fire | t trigger event :   | after the module | a is anabled |  |  |  |  |  |  |

|              |                                                                                                          | /aits 2 PWM cyc<br>/aits 1 PWM cyc |                |                   |                     |                  |              |  |  |  |  |  |  |

## REGISTER 16-12: TRGCONx: PWMx TRIGGER CONTROL REGISTER

## REGISTER 23-1: AD1CON1: ADC1 CONTROL REGISTER 1 (CONTINUED)

| bit 7-5 | SSRC<2:0>: Sample Trigger Source Select bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | If SSRCG = 1:<br>111 = Reserved<br>110 = PTGO15 primary trigger compare ends sampling and starts conversion <sup>(1)</sup><br>101 = PTGO14 primary trigger compare ends sampling and starts conversion <sup>(1)</sup><br>100 = PTGO13 primary trigger compare ends sampling and starts conversion <sup>(1)</sup><br>011 = PTGO12 primary trigger compare ends sampling and starts conversion <sup>(1)</sup><br>010 = PWM Generator 3 primary trigger compare ends sampling and starts conversion <sup>(2)</sup><br>001 = PWM Generator 2 primary trigger compare ends sampling and starts conversion <sup>(2)</sup><br>000 = PWM Generator 1 primary trigger compare ends sampling and starts conversion <sup>(2)</sup> |

|         | If SSRCG = 0:<br>111 = Internal counter ends sampling and starts conversion (auto-convert)<br>110 = CTMU ends sampling and starts conversion<br>101 = Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         | <ul> <li>101 - Reserved</li> <li>100 = Timer5 compare ends sampling and starts conversion</li> <li>011 = PWM primary Special Event Trigger ends sampling and starts conversion</li> <li>010 = Timer3 compare ends sampling and starts conversion</li> <li>001 = Active transition on the INT0 pin ends sampling and starts conversion</li> <li>000 = Clearing the Sample bit (SAMP) ends sampling and starts conversion (Manual mode)</li> </ul>                                                                                                                                                                                                                                                                        |

| bit 4   | SSRCG: Sample Trigger Source Group bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|         | See SSRC<2:0> for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| bit 3   | <ul> <li>SIMSAM: Simultaneous Sample Select bit (only applicable when CHPS&lt;1:0&gt; = 01 or 1x)</li> <li><u>In 12-bit mode (AD21B = 1), SIMSAM is Unimplemented and is Read as '0':</u></li> <li>1 = Samples CH0, CH1, CH2, CH3 simultaneously (when CHPS&lt;1:0&gt; = 1x); or samples CH0 and CH1 simultaneously (when CHPS&lt;1:0&gt; = 01)</li> <li>0 = Samples multiple channels individually in sequence</li> </ul>                                                                                                                                                                                                                                                                                              |

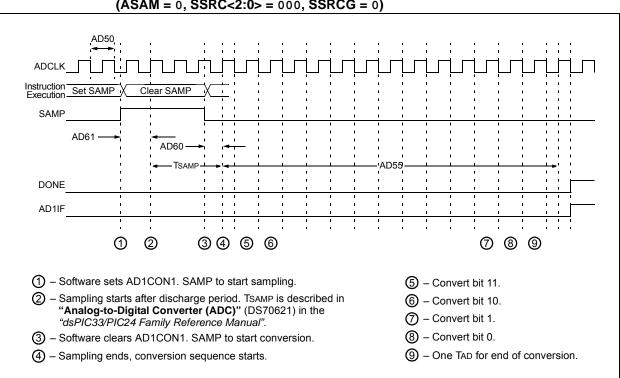

| bit 2   | ASAM: ADC1 Sample Auto-Start bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|         | <ul> <li>1 = Sampling begins immediately after the last conversion; SAMP bit is auto-set</li> <li>0 = Sampling begins when the SAMP bit is set</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| bit 1   | SAMP: ADC1 Sample Enable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|         | <ul> <li>1 = ADC Sample-and-Hold amplifiers are sampling</li> <li>0 = ADC Sample-and-Hold amplifiers are holding</li> <li>If ASAM = 0, software can write '1' to begin sampling. Automatically set by hardware if ASAM = 1. If SSRC&lt;2:0&gt; = 000, software can write '0' to end sampling and start conversion. If SSRC&lt;2:0&gt; ≠ 000, automatically cleared by hardware to end sampling and start conversion.</li> </ul>                                                                                                                                                                                                                                                                                         |

| bit 0   | DONE: ADC1 Conversion Status bit <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|         | <ul> <li>1 = ADC conversion cycle has completed</li> <li>0 = ADC conversion has not started or is in progress</li> <li>Automatically set by hardware when the ADC conversion is complete. Software can write '0' to clear the DONE status bit (software is not allowed to write '1'). Clearing this bit does NOT affect any operation in progress. Automatically cleared by hardware at the start of a new conversion.</li> </ul>                                                                                                                                                                                                                                                                                       |

| Note 1: | See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for information on this selection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

- 2: This setting is available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

- **3:** Do not clear the DONE bit in software if Auto-Sample is enabled (ASAM = 1).

## REGISTER 23-2: AD1CON2: ADC1 CONTROL REGISTER 2 (CONTINUED)

| bit 1 | BUFM: Buffer Fill Mode Select bit                                                                                                                                                                                               |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Starts the buffer filling the first half of the buffer on the first interrupt and the second half of the buffer on next interrupt</li> <li>0 = Always starts filling the buffer from the start address.</li> </ul> |

| bit 0 | ALTS: Alternate Input Sample Mode Select bit                                                                                                                                                                                    |

1 = Uses channel input selects for Sample MUXA on first sample and Sample MUXB on next sample 0 = Always uses channel input selects for Sample MUXA

# REGISTER 24-10: PTGADJ: PTG ADJUST REGISTER<sup>(1)</sup>

| R/W-0           | R/W-0                              | R/W-0          | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |

|-----------------|------------------------------------|----------------|-------|-----------------------------------------|-------|-------|-------|--|

|                 |                                    |                | PTGA  | DJ<15:8>                                |       |       |       |  |

| bit 15          |                                    |                |       |                                         |       |       | bit 8 |  |

|                 |                                    |                |       |                                         |       |       |       |  |

| R/W-0           | R/W-0                              | R/W-0          | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |

|                 |                                    |                | PTGA  | DJ<7:0>                                 |       |       |       |  |

| bit 7           |                                    |                |       |                                         |       |       | bit 0 |  |

|                 |                                    |                |       |                                         |       |       |       |  |

| Legend:         |                                    |                |       |                                         |       |       |       |  |

| R = Readable    | bit                                | W = Writable b | oit   | U = Unimplemented bit, read as '0'      |       |       |       |  |

| -n = Value at P | -n = Value at POR '1' = Bit is set |                |       | '0' = Bit is cleared x = Bit is unknown |       |       |       |  |

bit 15-0 **PTGADJ<15:0>:** PTG Adjust Register bits This register holds user-supplied data to be added to the PTGTxLIM, PTGCxLIM, PTGSDLIM or PTGL0 registers with the PTGADD command.

## REGISTER 24-11: PTGL0: PTG LITERAL 0 REGISTER<sup>(1)</sup>

| R/W-0  | R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |  |  |

|--------|-------------|-------|-------|-------|-------|-------|-------|--|--|--|--|--|

|        | PTGL0<15:8> |       |       |       |       |       |       |  |  |  |  |  |

| bit 15 |             |       |       |       |       |       | bit 8 |  |  |  |  |  |

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|--------|-------|-------|-------|

|       |       |       | PTGL  | )<7:0> |       |       |       |

| bit 7 |       |       |       |        |       |       | bit 0 |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | id as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

#### bit 15-0 PTGL0<15:0>: PTG Literal 0 Register bits

This register holds the 16-bit value to be written to the AD1CHS0 register with the  ${\tt PTGCTRL}$  Step command.

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

NOTES:

## 25.0 OP AMP/COMPARATOR MODULE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Op Amp/Comparator" (DS70357) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

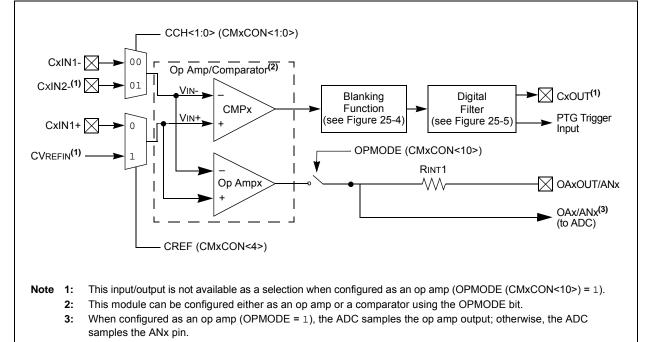

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices contain up to four comparators, which can be configured in various ways. Comparators, CMP1, CMP2 and CMP3, also have the option to be configured as op amps, with the output being brought to an external pin for gain/filtering connections. As shown in Figure 25-1, individual comparator options are specified by the comparator module's Special Function Register (SFR) control bits.

Note: Op Amp/Comparator 3 is not available on the dsPIC33EPXXXGP502/MC502/MC202 and PIC24EP256GP/MC202 (28-pin) devices.

These options allow users to:

- · Select the edge for trigger and interrupt generation

- · Configure the comparator voltage reference

- · Configure output blanking and masking

- Configure as a comparator or op amp (CMP1, CMP2 and CMP3 only)

Note: Not all op amp/comparator input/output connections are available on all devices. See the "Pin Diagrams" section for available connections.

## FIGURE 25-1: OP AMP/COMPARATOR x MODULE BLOCK DIAGRAM (MODULES 1, 2 AND 3)

# 26.3 Programmable CRC Registers

#### REGISTER 26-1: CRCCON1: CRC CONTROL REGISTER 1

| R/W-0                            | U-0                                                                                                                                                                                                                                                                                                                                                                                                                     | R/W-0                                                                                                                                                                                                                                                                                                                                             | R-0                                                                                                                                                                              | R-0                                                                         | R-0                                                                 | R-0             | R-0            |  |  |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|---------------------------------------------------------------------|-----------------|----------------|--|--|

| CRCEN                            | _                                                                                                                                                                                                                                                                                                                                                                                                                       | CSIDL                                                                                                                                                                                                                                                                                                                                             | VWORD4                                                                                                                                                                           | VWORD3                                                                      | VWORD2                                                              | VWORD1          | VWORD0         |  |  |

| bit 15                           |                                                                                                                                                                                                                                                                                                                                                                                                                         | •                                                                                                                                                                                                                                                                                                                                                 | ·                                                                                                                                                                                |                                                                             |                                                                     |                 | bit 8          |  |  |

| R-0                              | R-1                                                                                                                                                                                                                                                                                                                                                                                                                     | R/W-0                                                                                                                                                                                                                                                                                                                                             | R/W-0                                                                                                                                                                            | R/W-0                                                                       | U-0                                                                 | U-0             | U-0            |  |  |

| CRCFUL                           | CRCMPT                                                                                                                                                                                                                                                                                                                                                                                                                  | CRCISEL                                                                                                                                                                                                                                                                                                                                           | CRCGO                                                                                                                                                                            | LENDIAN                                                                     | _                                                                   | _               | —              |  |  |

| bit 7                            |                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                   | •                                                                                                                                                                                |                                                                             |                                                                     |                 | bit (          |  |  |

| Legend:                          |                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                  |                                                                             |                                                                     |                 |                |  |  |

| R = Readable                     | e bit                                                                                                                                                                                                                                                                                                                                                                                                                   | W = Writable                                                                                                                                                                                                                                                                                                                                      | bit                                                                                                                                                                              | U = Unimplen                                                                | nented bit, read                                                    | 1 as '0'        |                |  |  |

| -n = Value at                    | POR                                                                                                                                                                                                                                                                                                                                                                                                                     | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                  | '0' = Bit is cle                                                            | ared                                                                | x = Bit is unkr | nown           |  |  |

| bit 15                           | 0 = CRC mo                                                                                                                                                                                                                                                                                                                                                                                                              | dule is enabled                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                  | chines, pointer                                                             | s and CRCWD                                                         | AT/CRCDAT a     | re reset, othe |  |  |

| bit 14                           | Unimplemen                                                                                                                                                                                                                                                                                                                                                                                                              | ted: Read as '                                                                                                                                                                                                                                                                                                                                    | 0'                                                                                                                                                                               |                                                                             |                                                                     |                 |                |  |  |

| bit 13                           | CSIDL: CRC                                                                                                                                                                                                                                                                                                                                                                                                              | Stop in Idle Mo                                                                                                                                                                                                                                                                                                                                   | ode bit                                                                                                                                                                          | CSIDL: CRC Stop in Idle Mode bit                                            |                                                                     |                 |                |  |  |

|                                  | <ul> <li>1 = Discontinues module operation when device enters Idle mode</li> <li>0 = Continues module operation in Idle mode</li> </ul>                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                  |                                                                             |                                                                     |                 |                |  |  |

|                                  |                                                                                                                                                                                                                                                                                                                                                                                                                         | •                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                  |                                                                             | ldle mode                                                           |                 |                |  |  |

| bit 12-8                         | 0 = Continue<br>VWORD<4:0:                                                                                                                                                                                                                                                                                                                                                                                              | s module opera                                                                                                                                                                                                                                                                                                                                    | ation in Idle m<br>e bits                                                                                                                                                        | ode                                                                         |                                                                     |                 |                |  |  |

| bit 12-8                         | 0 = Continue<br>VWORD<4:0:<br>Indicates the                                                                                                                                                                                                                                                                                                                                                                             | s module opera                                                                                                                                                                                                                                                                                                                                    | ation in Idle m<br>e bits                                                                                                                                                        | ode                                                                         |                                                                     | of 8 when PLE   | N<4:0> > 7     |  |  |

|                                  | 0 = Continue<br>VWORD<4:0:<br>Indicates the<br>or 16 when Pl                                                                                                                                                                                                                                                                                                                                                            | s module oper<br>>: Pointer Valu<br>number of valio                                                                                                                                                                                                                                                                                               | ation in Idle m<br>e bits<br>d words in the                                                                                                                                      | ode                                                                         |                                                                     | of 8 when PLE   | N<4:0> > 7     |  |  |

|                                  | 0 = Continue<br>VWORD<4:0:<br>Indicates the<br>or 16 when Pl                                                                                                                                                                                                                                                                                                                                                            | s module operations<br>>: Pointer Valu<br>number of valid<br>LEN<4:0> $\leq$ 7.<br>C FIFO Full bit<br>ull                                                                                                                                                                                                                                         | ation in Idle m<br>e bits<br>d words in the                                                                                                                                      | ode                                                                         |                                                                     | of 8 when PLE   | N<4:0> > 7     |  |  |

| bit 12-8<br>bit 7<br>bit 6       | 0 = Continue<br>VWORD<4:0:<br>Indicates the<br>or 16 when Pl<br>CRCFUL: CR<br>1 = FIFO is fu<br>0 = FIFO is n                                                                                                                                                                                                                                                                                                           | s module operations<br>>: Pointer Valu<br>number of valid<br>LEN<4:0> $\leq$ 7.<br>C FIFO Full bit<br>ull                                                                                                                                                                                                                                         | ation in Idle m<br>e bits<br>d words in the<br>t                                                                                                                                 | ode                                                                         |                                                                     | of 8 when PLE   | N<4:0> > 7     |  |  |

| bit 7                            | 0 = Continue<br>VWORD<4:0:<br>Indicates the<br>or 16 when Pl<br>CRCFUL: CR<br>1 = FIFO is fu<br>0 = FIFO is n<br>CRCMPT: CR<br>1 = FIFO is e                                                                                                                                                                                                                                                                            | s module operatives<br>>: Pointer Valu<br>number of valid<br>LEN<4:0> $\leq$ 7.<br>C FIFO Full bit<br>ull<br>not full<br>RC FIFO Empty<br>empty                                                                                                                                                                                                   | ation in Idle m<br>e bits<br>d words in the<br>t                                                                                                                                 | ode                                                                         |                                                                     | of 8 when PLE   | N<4:0> > 7     |  |  |

| bit 7<br>bit 6                   | <ul> <li>0 = Continue</li> <li>VWORD&lt;4:0:</li> <li>Indicates the or 16 when Pl</li> <li>CRCFUL: CR</li> <li>1 = FIFO is fit</li> <li>0 = FIFO is n</li> <li>CRCMPT: CR</li> <li>1 = FIFO is e</li> <li>0 = FIFO is n</li> </ul>                                                                                                                                                                                      | s module operatives<br>>: Pointer Valu<br>number of valid<br>LEN<4: $0> \le 7$ .<br>C FIFO Full bit<br>ull<br>not full<br>RC FIFO Empty<br>empty<br>not empty                                                                                                                                                                                     | ation in Idle m<br>e bits<br>d words in the<br>t<br>v Bit                                                                                                                        | ode                                                                         |                                                                     | of 8 when PLE   | N<4:0> > 7     |  |  |

| bit 7<br>bit 6                   | <ul> <li>0 = Continue</li> <li>VWORD&lt;4:0:</li> <li>Indicates the or 16 when Pl</li> <li>CRCFUL: CR</li> <li>1 = FIFO is fit</li> <li>0 = FIFO is n</li> <li>CRCMPT: CR</li> <li>1 = FIFO is n</li> <li>0 = FIFO is n</li> <li>CRCISEL: CF</li> </ul>                                                                                                                                                                 | s module operatives<br>>: Pointer Valu<br>number of valid<br>LEN<4: $0> \le 7$ .<br>C FIFO Full bit<br>ull<br>NC FIFO Empty<br>empty<br>not empty<br>RC Interrupt Se                                                                                                                                                                              | ation in Idle m<br>e bits<br>d words in the<br>t<br>v Bit<br>election bit                                                                                                        | ode<br>FIFO. Has a m                                                        | naximum value                                                       |                 | N<4:0> > 7     |  |  |

| bit 7<br>bit 6                   | <ul> <li>0 = Continue</li> <li>VWORD&lt;4:0:</li> <li>Indicates the or 16 when Pl</li> <li>CRCFUL: CR</li> <li>1 = FIFO is fit</li> <li>0 = FIFO is n</li> <li>CRCMPT: CR</li> <li>1 = FIFO is e</li> <li>0 = FIFO is n</li> <li>CRCISEL: CF</li> <li>1 = Interrupt</li> </ul>                                                                                                                                          | s module operatives<br>>: Pointer Valu<br>number of valid<br>LEN<4: $0> \le 7$ .<br>C FIFO Full bit<br>ull<br>AC FIFO Empty<br>empty<br>not empty<br>RC Interrupt Secon FIFO is emptore<br>on FIFO is emptore                                                                                                                                     | ation in Idle m<br>e bits<br>d words in the<br>t<br>v Bit<br>election bit<br>pty; final word                                                                                     | ode<br>FIFO. Has a m<br>of data is still s                                  | naximum value<br>shifting through                                   |                 | N<4:0> > 7     |  |  |

| bit 7<br>bit 6<br>bit 5          | <ul> <li>0 = Continue</li> <li>VWORD&lt;4:0:</li> <li>Indicates the or 16 when Pl</li> <li>CRCFUL: CR</li> <li>1 = FIFO is fit</li> <li>0 = FIFO is n</li> <li>CRCMPT: CR</li> <li>1 = FIFO is e</li> <li>0 = FIFO is n</li> <li>CRCISEL: CF</li> <li>1 = Interrupt</li> </ul>                                                                                                                                          | s module operatives<br>>: Pointer Value<br>number of valid<br>LEN<4:0> $\leq$ 7.<br>C FIFO Full bit<br>uil<br>not full<br>RC FIFO Empty<br>empty<br>not empty<br>RC Interrupt Secon FIFO is empty<br>on FIFO is empty<br>on shift is compared                                                                                                     | ation in Idle m<br>e bits<br>d words in the<br>t<br>v Bit<br>election bit<br>pty; final word                                                                                     | ode<br>FIFO. Has a m<br>of data is still s                                  | naximum value<br>shifting through                                   |                 | N<4:0> > 7     |  |  |

| bit 7<br>bit 6<br>bit 5          | <ul> <li>0 = Continue</li> <li>VWORD&lt;4:0:</li> <li>Indicates the or 16 when Pl</li> <li>CRCFUL: CR</li> <li>1 = FIFO is ft</li> <li>0 = FIFO is n</li> <li>CRCMPT: CR</li> <li>1 = FIFO is e</li> <li>0 = FIFO is n</li> <li>CRCISEL: CF</li> <li>1 = Interrupt</li> <li>0 = Interrupt</li> <li>CRCGO: Star</li> </ul>                                                                                               | s module operatives<br>>: Pointer Value<br>number of valid<br>LEN<4:0> $\leq$ 7.<br>C FIFO Full bit<br>uil<br>not full<br>RC FIFO Empty<br>empty<br>not empty<br>RC Interrupt Secon FIFO is empty<br>on FIFO is empty<br>on shift is compared                                                                                                     | ation in Idle m<br>e bits<br>d words in the<br>t<br>election bit<br>pty; final word<br>plete and CRO                                                                             | ode<br>FIFO. Has a m<br>of data is still s                                  | naximum value<br>shifting through                                   |                 | N<4:0> > 7     |  |  |

| bit 7                            | <ul> <li>0 = Continue</li> <li>VWORD&lt;4:0:</li> <li>Indicates the or 16 when Pl</li> <li>CRCFUL: CR</li> <li>1 = FIFO is fit</li> <li>0 = FIFO is n</li> <li>CRCMPT: CR</li> <li>1 = FIFO is n</li> <li>CRCISEL: CF</li> <li>1 = Interrupt</li> <li>0 = Interrupt</li> <li>CRCGO: Start</li> <li>1 = Starts CF</li> </ul>                                                                                             | s module operatives<br>>: Pointer Valu<br>number of valid<br>LEN<4: $0> \le 7$ .<br>C FIFO Full bit<br>ull<br>Not full<br>RC FIFO Empty<br>mpty<br>not empty<br>RC Interrupt Secon FIFO is emponent<br>on FIFO is emponent<br>on shift is component<br>t CRC bit                                                                                  | ation in Idle m<br>e bits<br>d words in the<br>t<br>/ Bit<br>election bit<br>pty; final word<br>plete and CRC                                                                    | ode<br>FIFO. Has a m<br>of data is still s                                  | naximum value<br>shifting through                                   |                 | N<4:0> > 7     |  |  |

| bit 7<br>bit 6<br>bit 5<br>bit 4 | <ul> <li>0 = Continue</li> <li>VWORD&lt;4:0:</li> <li>Indicates the or 16 when Pl</li> <li>CRCFUL: CR</li> <li>1 = FIFO is fit</li> <li>0 = FIFO is n</li> <li>CRCMPT: CR</li> <li>1 = FIFO is e</li> <li>0 = FIFO is n</li> <li>CRCISEL: CF</li> <li>1 = Interrupt</li> <li>0 = Interrupt</li> <li>CRCGO: Start</li> <li>1 = Starts CF</li> <li>0 = CRC serii</li> <li>LENDIAN: Data</li> </ul>                        | s module operatives<br>>: Pointer Value<br>number of valide<br>LEN<4:0> $\leq$ 7.<br>C FIFO Full bit<br>ull<br>and full<br>C FIFO Empty<br>empty<br>and empty<br>RC Interrupt Secon<br>on FIFO is emplored<br>on FIFO is emplored<br>on Shift is com<br>t CRC bit<br>RC serial shifter<br>ial shifter is turn<br>ata Word Little-                 | ation in Idle m<br>e bits<br>d words in the<br>t<br>election bit<br>pty; final word<br>plete and CRC<br>r<br>ned off<br>Endian Config                                            | ode<br>FIFO. Has a m<br>of data is still s<br>CWDAT results<br>guration bit | naximum value<br>shifting through<br>are ready                      | CRC             | N<4:0> > 7     |  |  |