#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                      |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 60 MIPs                                                                       |

| Connectivity               | I²C, IrDA, LINbus, QEI, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                 |

| Number of I/O              | 21                                                                            |

| Program Memory Size        | 32KB (10.7K x 24)                                                             |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 2K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 6x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                |

| Supplier Device Package    | 28-SOIC                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep32mc202-h-so |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                 |       | 1101        |                                       |         |         |         |            |             |          |             |        | A.II  |       |        |          |          |        |        |

|-----------------|-------|-------------|---------------------------------------|---------|---------|---------|------------|-------------|----------|-------------|--------|-------|-------|--------|----------|----------|--------|--------|

| File Name       | Addr. | Bit 15      | Bit 14                                | Bit 13  | Bit 12  | Bit 11  | Bit 10     | Bit 9       | Bit 8    | Bit 7       | Bit 6  | Bit 5 | Bit 4 | Bit 3  | Bit 2    | Bit 1    | Bit 0  | Resets |

| PTGCST          | 0AC0  | PTGEN       | —                                     | PTGSIDL | PTGTOGL |         | PTGSWT     | PTGSSEN     | PTGIVIS  | PTGSTRT     | PTGWTO | _     | _     | —      | —        | PTGIT    | M<1:0> | 0000   |

| PTGCON          | 0AC2  | F           | PTGCLK<2                              | :0>     |         | F       | PTGDIV<4:0 | >           |          |             | PTGPWD | <3:0> |       | _      | P        | TGWDT<2: | 0>     | 0000   |

| PTGBTE          | 0AC4  |             | ADCTS<4:1> IC4TSS IC3TSS IC2TSS IC1TS |         |         |         |            |             | IC1TSS   | OC4CS       | OC3CS  | OC2CS | OC1CS | OC4TSS | OC3TSS   | OC2TSS   | OC1TSS | 0000   |

| PTGHOLD         | 0AC6  |             |                                       |         |         |         |            |             | PTGHOLD  | <15:0>      |        |       |       |        |          |          |        | 0000   |

| <b>PTGT0LIM</b> | 0AC8  |             | PTGT0LIM<15:0>                        |         |         |         |            |             |          |             |        |       |       |        |          |          |        | 0000   |

| PTGT1LIM        | 0ACA  |             | PTGT1LIM<15:0>                        |         |         |         |            |             |          |             |        |       |       |        |          |          |        | 0000   |

| PTGSDLIM        | 0ACC  |             | PTGSDLIM<15:0>                        |         |         |         |            |             |          |             | 0000   |       |       |        |          |          |        |        |

| <b>PTGC0LIM</b> | 0ACE  |             | PTGC0LIM<15:0>                        |         |         |         |            |             |          |             | 0000   |       |       |        |          |          |        |        |

| PTGC1LIM        | 0AD0  |             |                                       |         |         |         |            |             | PTGC1LIN | <15:0>      |        |       |       |        |          |          |        | 0000   |

| PTGADJ          | 0AD2  |             |                                       |         |         |         |            |             | PTGADJ<  | <15:0>      |        |       |       |        |          | 0000     |        |        |

| PTGL0           | 0AD4  |             |                                       |         |         |         |            |             | PTGL0<   | 15:0>       |        |       |       |        |          |          |        | 0000   |

| PTGQPTR         | 0AD6  | —           | —                                     | —       | —       | _       | —          | —           | _        | —           | —      | -     |       | P      | TGQPTR<4 | 4:0>     |        | 0000   |

| PTGQUE0         | 0AD8  |             |                                       |         | STEP    | 1<7:0>  |            |             |          |             |        |       | STEPO | )<7:0> |          |          |        | 0000   |

| PTGQUE1         | 0ADA  |             |                                       |         | STEP    | '3<7:0> |            |             |          |             |        |       | STEP2 | 2<7:0> |          |          |        | 0000   |

| PTGQUE2         | 0ADC  |             |                                       |         | STEP    | 25<7:0> |            |             |          |             |        |       | STEP4 | <7:0>  |          |          |        | 0000   |

| PTGQUE3         | 0ADE  |             |                                       |         | STEP    | 7<7:0>  |            |             |          |             |        |       | STEP6 | 6<7:0> |          |          |        | 0000   |

| PTGQUE4         | 0AE0  | STEP9<7:0>  |                                       |         |         |         |            | STEP8<7:0>  |          |             |        |       | 0000  |        |          |          |        |        |

| PTGQUE5         | 0AE2  | STEP11<7:0> |                                       |         |         |         |            | STEP10<7:0> |          |             |        |       | 0000  |        |          |          |        |        |

| PTGQUE6         | 0AE4  |             | STEP13<7:0>                           |         |         |         |            |             |          | STEP12<7:0> |        |       |       |        | 0000     |          |        |        |

| PTGQUE7         | 0AE6  |             |                                       |         | STEP    | 15<7:0> |            |             |          |             |        |       | STEP1 | 4<7:0> |          |          |        | 0000   |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

DS70000657H-page 78

## TABLE 4-19: SPI1 AND SPI2 REGISTER MAP

| SFR Name | Addr. | Bit 15                                       | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8        | Bit 7       | Bit 6      | Bit 5  | Bit 4 | Bit 3      | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|----------|-------|----------------------------------------------|--------|---------|--------|--------|--------|------------|--------------|-------------|------------|--------|-------|------------|-------|--------|--------|---------------|

| SPI1STAT | 0240  | SPIEN                                        | _      | SPISIDL | _      | _      | 5      | SPIBEC<2:0 | >            | SRMPT       | SPIROV     | SRXMPT |       | SISEL<2:0> |       | SPITBF | SPIRBF | 0000          |

| SPI1CON1 | 0242  | _                                            | _      | _       | DISSCK | DISSDO | MODE16 | SMP        | CKE          | SSEN        | CKP        | MSTEN  |       | SPRE<2:0>  |       | PPRE   | <1:0>  | 0000          |

| SPI1CON2 | 0244  | FRMEN                                        | SPIFSD | FRMPOL  | _      | _      |        | _          | _            | —           | _          | _      | _     | _          | _     | FRMDLY | SPIBEN | 0000          |

| SPI1BUF  | 0248  |                                              |        |         |        |        |        | SPI1 Tra   | insmit and R | eceive Buff | er Registe | r      |       |            |       |        |        | 0000          |

| SPI2STAT | 0260  | SPIEN                                        | _      | SPISIDL | _      | _      | ŝ      | SPIBEC<2:0 | >            | SRMPT       | SPIROV     | SRXMPT |       | SISEL<2:0> |       | SPITBF | SPIRBF | 0000          |

| SPI2CON1 | 0262  | _                                            | _      | _       | DISSCK | DISSDO | MODE16 | SMP        | CKE          | SSEN        | CKP        | MSTEN  |       | SPRE<2:0>  |       | PPRE   | <1:0>  | 0000          |

| SPI2CON2 | 0264  | FRMEN                                        | SPIFSD | FRMPOL  | _      | _      |        | _          | _            | —           | _          | _      | _     | _          | _     | FRMDLY | SPIBEN | 0000          |

| SPI2BUF  | 0268  | SPI2 Transmit and Receive Buffer Register 00 |        |         |        |        |        | 0000       |              |             |            |        |       |            |       |        |        |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

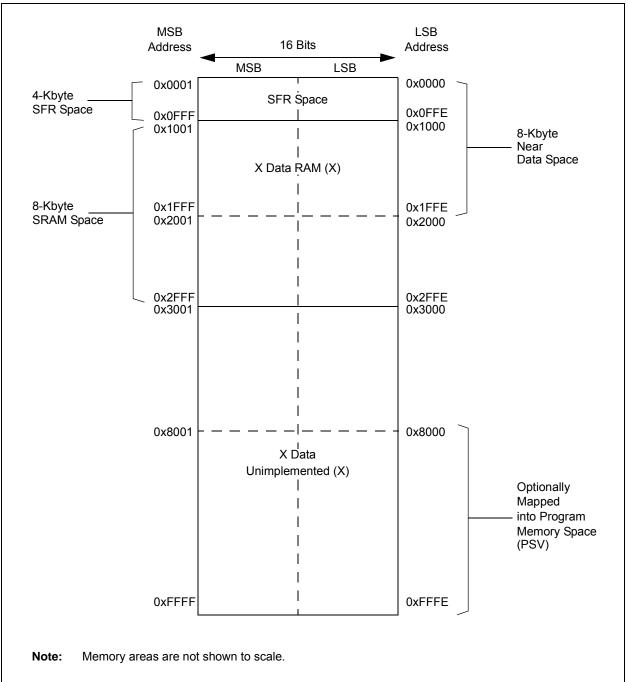

#### 4.4.1 PAGED MEMORY SCHEME

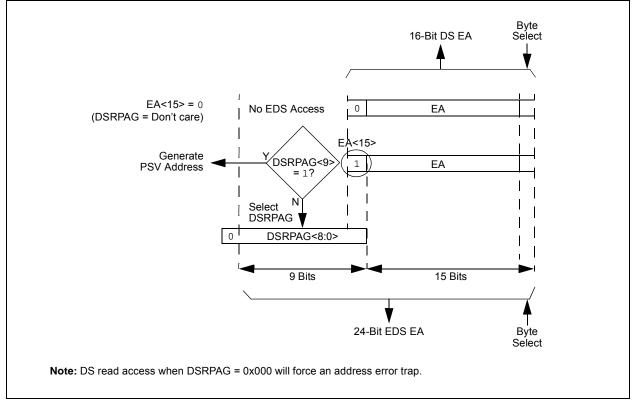

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X architecture extends the available Data Space through a paging scheme, which allows the available Data Space to be accessed using MOV instructions in a linear fashion for pre-modified and post-modified Effective Addresses (EA). The upper half of the base Data Space address is used in conjunction with the Data Space Page registers, the 10-bit Read Page register (DSRPAG) or the 9-bit Write Page register (DSWPAG), to form an Extended Data Space (EDS) address or Program Space Visibility (PSV) address. The Data Space Page registers are located in the SFR space.

Construction of the EDS address is shown in Example 4-1. When DSRPAG<9> = 0 and the base address bit, EA<15> = 1, the DSRPAG<8:0> bits are concatenated onto EA<14:0> to form the 24-bit EDS read address. Similarly, when base address bit, EA<15> = 1, DSWPAG<8:0> are concatenated onto EA<14:0> to form the 24-bit EDS write address.

#### 4.6.3 MODULO ADDRESSING APPLICABILITY

Modulo Addressing can be applied to the Effective Address (EA) calculation associated with any W register. Address boundaries check for addresses equal to:

- The upper boundary addresses for incrementing buffers

- The lower boundary addresses for decrementing buffers

It is important to realize that the address boundaries check for addresses less than, or greater than, the upper (for incrementing buffers) and lower (for decrementing buffers) boundary addresses (not just equal to). Address changes can, therefore, jump beyond boundaries and still be adjusted correctly.

Note: The modulo corrected Effective Address is written back to the register only when Pre-Modify or Post-Modify Addressing mode is used to compute the Effective Address. When an address offset (such as [W7 + W2]) is used, Modulo Addressing correction is performed but the contents of the register remain unchanged.

## 4.7 Bit-Reversed Addressing (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X Devices Only)

Bit-Reversed Addressing mode is intended to simplify data reordering for radix-2 FFT algorithms. It is supported by the X AGU for data writes only.

The modifier, which can be a constant value or register contents, is regarded as having its bit order reversed. The address source and destination are kept in normal order. Thus, the only operand requiring reversal is the modifier.

# 4.7.1 BIT-REVERSED ADDRESSING IMPLEMENTATION

Bit-Reversed Addressing mode is enabled when all these conditions are met:

- BWMx bits (W register selection) in the MODCON register are any value other than '1111' (the stack cannot be accessed using Bit-Reversed Addressing)

- The BREN bit is set in the XBREV register

- The addressing mode used is Register Indirect with Pre-Increment or Post-Increment

If the length of a bit-reversed buffer is  $M = 2^{N}$  bytes, the last 'N' bits of the data buffer start address must be zeros.

XBREV<14:0> is the Bit-Reversed Addressing modifier, or 'pivot point', which is typically a constant. In the case of an FFT computation, its value is equal to half of the FFT data buffer size.

| Note: | All bit-reversed EA calculations assume    |

|-------|--------------------------------------------|

|       | word-sized data (LSb of every EA is always |

|       | clear). The XBREVx value is scaled         |

|       | accordingly to generate compatible (byte)  |

|       | addresses.                                 |

When enabled, Bit-Reversed Addressing is executed only for Register Indirect with Pre-Increment or Post-Increment Addressing and word-sized data writes. It does not function for any other addressing mode or for byte-sized data and normal addresses are generated instead. When Bit-Reversed Addressing is active, the W Address Pointer is always added to the address modifier (XBREVx) and the offset associated with the Register Indirect Addressing mode is ignored. In addition, as word-sized data is a requirement, the LSb of the EA is ignored (and always clear).

Note: Modulo Addressing and Bit-Reversed Addressing can be enabled simultaneously using the same W register, but Bit-Reversed Addressing operation will always take precedence for data writes when enabled.

If Bit-Reversed Addressing has already been enabled by setting the BREN (XBREV<15>) bit, a write to the XBREV register should not be immediately followed by an indirect read operation using the W register that has been designated as the Bit-Reversed Pointer.

## 9.0 OSCILLATOR CONFIGURATION

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Oscillator" (DS70580) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

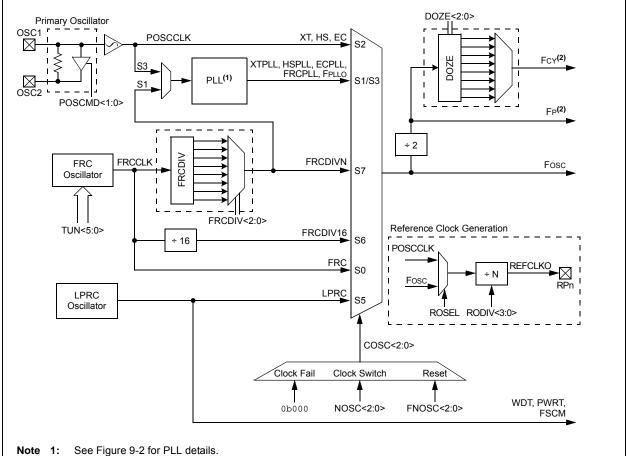

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X oscillator system provides:

- On-chip Phase-Locked Loop (PLL) to boost internal operating frequency on select internal and external oscillator sources

- On-the-fly clock switching between various clock sources

- · Doze mode for system power savings

- Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown

- Configuration bits for clock source selection

- A simplified diagram of the oscillator system is shown in Figure 9-1.

#### FIGURE 9-1: OSCILLATOR SYSTEM DIAGRAM

2: The term, FP, refers to the clock source for all peripherals, while FCY refers to the clock source for the CPU. Throughout this document, FCY and FP are used interchangeably, except in the case of Doze mode. FP and FCY will be different when Doze mode is used with a doze ratio of 1:2 or lower.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0     | U-0 | U-0   | U-0   | U-0   | U-0   | U-0   | U-0   |

|---------|-----|-------|-------|-------|-------|-------|-------|

| —       | —   | —     | —     | —     | —     | —     | —     |

| bit 15  |     |       |       |       |       |       | bit 8 |

|         |     |       |       |       |       |       |       |

| U-0     | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| —       | —   | TUN5  | TUN4  | TUN3  | TUN2  | TUN1  | TUN0  |

| bit 7   |     |       |       |       |       |       | bit 0 |

|         |     |       |       |       |       |       |       |

| Logondi |     |       |       |       |       |       |       |

#### REGISTER 9-4: OSCTUN: FRC OSCILLATOR TUNING REGISTER

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-6 Unimplemented: Read as '0'

bit 5-0 **TUN<5:0>:** FRC Oscillator Tuning bits 011111 = Maximum frequency deviation of 1.453% (7.477 MHz) 011110 = Center frequency + 1.406% (7.474 MHz) •••• 000001 = Center frequency + 0.047% (7.373 MHz) 000000 = Center frequency (7.37 MHz nominal) 111111 = Center frequency - 0.047% (7.367 MHz) ••• 100001 = Center frequency - 1.453% (7.263 MHz) 100000 = Minimum frequency deviation of -1.5% (7.259 MHz)

#### REGISTER 11-8: RPINR14: PERIPHERAL PIN SELECT INPUT REGISTER 14 (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

| U-0          | R/W-0                     | R/W-0                                                                                              | R/W-0                      | R/W-0             | R/W-0           | R/W-0              | R/W-0 |  |

|--------------|---------------------------|----------------------------------------------------------------------------------------------------|----------------------------|-------------------|-----------------|--------------------|-------|--|

| —            |                           |                                                                                                    |                            | QEB1R<6:0>        |                 |                    |       |  |

| bit 15       |                           |                                                                                                    |                            |                   |                 |                    | bit 8 |  |

|              |                           |                                                                                                    |                            |                   |                 |                    |       |  |

| U-0          | R/W-0                     | R/W-0                                                                                              | R/W-0                      | R/W-0             | R/W-0           | R/W-0              | R/W-0 |  |

| —            |                           |                                                                                                    |                            | QEA1R<6:0>        |                 |                    |       |  |

| bit 7        |                           |                                                                                                    |                            |                   |                 |                    | bit 0 |  |

|              |                           |                                                                                                    |                            |                   |                 |                    |       |  |

| Legend:      |                           |                                                                                                    |                            |                   |                 |                    |       |  |

| R = Readat   | ole bit                   | W = Writable                                                                                       | bit                        | U = Unimplen      | nented bit, rea | ad as '0'          |       |  |

| -n = Value a | at POR                    | '1' = Bit is set                                                                                   |                            | '0' = Bit is clea | ared            | x = Bit is unknown |       |  |

|              | 1111001 =                 | 1-2 for input pin<br>Input tied to RPI<br>Input tied to CM<br>Input tied to Vss                    | 121<br>P1                  |                   |                 |                    |       |  |

| bit 7        | Unimpleme                 | nted: Read as '                                                                                    | 0'                         |                   |                 |                    |       |  |

| bit 6-0      | (see Table 1<br>1111001 = | >: Assign A (QE<br>1-2 for input pin<br>Input tied to RPI<br>Input tied to CM<br>Input tied to Vss | selection nun<br>121<br>P1 |                   | n Pin bits      |                    |       |  |

# 15.2 Output Compare Control Registers

## REGISTER 15-1: OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1

| U-0           | U-0                          | R/W-0                                                                                                                                 | R/W-0             | R/W-0             | R/W-0                  | U-0              | R/W-0         |  |  |  |

|---------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------|------------------------|------------------|---------------|--|--|--|

|               | 0-0                          | OCSIDL                                                                                                                                | OCTSEL2           | OCTSEL1           | OCTSEL0                |                  | ENFLTB        |  |  |  |

| <br>bit 15    |                              | COOIDE                                                                                                                                |                   | OUTOLLI           | OUTOLLU                |                  | bit 8         |  |  |  |

| Sit 10        |                              |                                                                                                                                       |                   |                   |                        |                  |               |  |  |  |

| R/W-0         | U-0                          | R/W-0, HSC                                                                                                                            | R/W-0, HSC        | R/W-0             | R/W-0                  | R/W-0            | R/W-0         |  |  |  |

| ENFLT         |                              | OCFLTB                                                                                                                                | OCFLTA            | TRIGMODE          | OCM2                   | OCM1             | OCM0          |  |  |  |

| bit 7         |                              |                                                                                                                                       |                   |                   |                        |                  | bit 0         |  |  |  |

|               |                              |                                                                                                                                       |                   |                   |                        |                  |               |  |  |  |

| Legend:       |                              | HSC = Hardware Settable/Clearable bit                                                                                                 |                   |                   |                        |                  |               |  |  |  |

| R = Read      | able bit                     | W = Writable I                                                                                                                        | oit               | U = Unimplem      | nented bit, read       | as '0'           |               |  |  |  |

| -n = Value    | e at POR                     | '1' = Bit is set                                                                                                                      |                   | '0' = Bit is clea | ared                   | x = Bit is unkn  | own           |  |  |  |

|               |                              |                                                                                                                                       |                   |                   |                        |                  |               |  |  |  |

| bit 15-14     | Unimplemen                   | ted: Read as '0                                                                                                                       | )'                |                   |                        |                  |               |  |  |  |

| bit 13        | OCSIDL: Out                  | tput Compare x                                                                                                                        | Stop in Idle Mo   | de Control bit    |                        |                  |               |  |  |  |

|               |                              | ompare x Halts                                                                                                                        |                   |                   |                        |                  |               |  |  |  |

|               | •                            | compare x conti                                                                                                                       | •                 |                   | ode                    |                  |               |  |  |  |

| bit 12-10     |                              | )>: Output Com                                                                                                                        | pare x Clock S    | elect bits        |                        |                  |               |  |  |  |

|               | 111 = Periph<br>110 = Reserv | eral clock (FP)                                                                                                                       |                   |                   |                        |                  |               |  |  |  |

|               | 101 = PTGO                   |                                                                                                                                       |                   |                   |                        |                  |               |  |  |  |

|               |                              | is the clock so                                                                                                                       |                   |                   | hronous clock          | is supported)    |               |  |  |  |

|               |                              | is the clock so                                                                                                                       |                   |                   |                        |                  |               |  |  |  |

|               |                              | ( is the clock so<br>( is the clock so                                                                                                |                   |                   |                        |                  |               |  |  |  |

|               |                              | is the clock so                                                                                                                       |                   |                   |                        |                  |               |  |  |  |

| bit 9         | Unimplemen                   | ted: Read as '0                                                                                                                       | )'                |                   |                        |                  |               |  |  |  |

| bit 8         | ENFLTB: Fau                  | ult B Input Enab                                                                                                                      | le bit            |                   |                        |                  |               |  |  |  |

|               |                              | compare Fault B<br>compare Fault B                                                                                                    |                   |                   |                        |                  |               |  |  |  |

| bit 7         | -                            | ult A Input Enab                                                                                                                      |                   |                   |                        |                  |               |  |  |  |

|               | 1 = Output C                 | ompare Fault A<br>compare Fault A                                                                                                     | input (OCFA)      |                   |                        |                  |               |  |  |  |

| bit 6         | •                            | ted: Read as '0                                                                                                                       | • • •             |                   |                        |                  |               |  |  |  |

| bit 5         | OCFLTB: PW                   | M Fault B Con                                                                                                                         | dition Status bit |                   |                        |                  |               |  |  |  |

|               |                              | ult B condition of Fault B condition                                                                                                  |                   |                   |                        |                  |               |  |  |  |

| bit 4         |                              | OCFLTA: PWM Fault A Condition Status bit                                                                                              |                   |                   |                        |                  |               |  |  |  |

|               |                              | <ul> <li>1 = PWM Fault A condition on OCFA pin has occurred</li> <li>0 = No PWM Fault A condition on OCFA pin has occurred</li> </ul> |                   |                   |                        |                  |               |  |  |  |

| Note 1:       | OCvR and OCvE                | OCxR and OCxRS are double-buffered in PWM mode only.                                                                                  |                   |                   |                        |                  |               |  |  |  |

| Note 1.<br>2: | Each Output Cor              |                                                                                                                                       |                   | -                 | irce. See <b>Secti</b> | on 24.0 "Perin   | heral Trigger |  |  |  |

| 2.            | Generator (PTG               |                                                                                                                                       |                   |                   |                        | 5.1 2 7.0 1 611p |               |  |  |  |

|               | PTGO4 = OC1                  |                                                                                                                                       |                   |                   |                        |                  |               |  |  |  |

|               | PTGO5 = OC2                  | PTGO5 = OC2<br>PTGO6 = OC3                                                                                                            |                   |                   |                        |                  |               |  |  |  |

|               | PTGO6 = OC3 $PTGO7 = OC4$    |                                                                                                                                       |                   |                   |                        |                  |               |  |  |  |

|               |                              |                                                                                                                                       |                   |                   |                        |                  |               |  |  |  |

## 16.0 HIGH-SPEED PWM MODULE (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "High-Speed PWM" (DS70645) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices support a dedicated Pulse-Width Modulation (PWM) module with up to 6 outputs.

The high-speed PWMx module consists of the following major features:

- Three PWM generators

- Two PWM outputs per PWM generator

- Individual period and duty cycle for each PWM pair

- Duty cycle, dead time, phase shift and frequency resolution of Tcy/2 (7.14 ns at Fcy = 70MHz)

- Independent Fault and current-limit inputs for six PWM outputs

- · Redundant output

- Center-Aligned PWM mode

- Output override control

- Chop mode (also known as Gated mode)

- Special Event Trigger

- Prescaler for input clock

- PWMxL and PWMxH output pin swapping

- Independent PWM frequency, duty cycle and phase-shift changes for each PWM generator

- Dead-time compensation

- Enhanced Leading-Edge Blanking (LEB) functionality

- Frequency resolution enhancement

- PWM capture functionality

**Note:** In Edge-Aligned PWM mode, the duty cycle, dead time, phase shift and frequency resolution are 8.32 ns.

The high-speed PWMx module contains up to three PWM generators. Each PWM generator provides two PWM outputs: PWMxH and PWMxL. The master time base generator provides a synchronous signal as a common time base to synchronize the various PWM outputs. The individual PWM outputs are available on the output pins of the device. The input Fault signals and current-limit signals, when enabled, can monitor and protect the system by placing the PWM outputs into a known "safe" state.

Each PWMx can generate a trigger to the ADC module to sample the analog signal at a specific instance during the PWM period. In addition, the high-speed PWMx module also generates a Special Event Trigger to the ADC module based on either of the two master time bases.

The high-speed PWMx module can synchronize itself with an external signal or can act as a synchronizing source to any external device. The SYNCI1 input pin that utilizes PPS, can synchronize the high-speed PWMx module with an external signal. The SYNC01 pin is an output pin that provides a synchronous signal to an external device.

Figure 16-1 illustrates an architectural overview of the high-speed PWMx module and its interconnection with the CPU and other peripherals.

## 16.1 PWM Faults

The PWMx module incorporates multiple external Fault inputs to include FLT1 and FLT2 which are remappable using the PPS feature, FLT3 and FLT4 which are available only on the larger 44-pin and 64-pin packages, and FLT32 which has been implemented with Class B safety features, and is available on a fixed pin on all dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

These Faults provide a safe and reliable way to safely shut down the PWM outputs when the Fault input is asserted.

#### 16.1.1 PWM FAULTS AT RESET

During any Reset event, the PWMx module maintains ownership of the Class B Fault, FLT32. At Reset, this Fault is enabled in Latched mode to ensure the fail-safe power-up of the application. The application software must clear the PWM Fault before enabling the highspeed motor control PWMx module. To clear the Fault condition, the FLT32 pin must first be pulled low externally or the internal pull-down resistor in the CNPDx register can be enabled.

Note: The Fault mode may be changed using the FLTMOD<1:0> bits (FCLCON<1:0>), regardless of the state of FLT32.

## 21.5 ECAN Message Buffers

ECAN Message Buffers are part of RAM memory. They are not ECAN Special Function Registers. The user application must directly write into the RAM area that is configured for ECAN Message Buffers. The location and size of the buffer area is defined by the user application.

#### BUFFER 21-1: ECAN™ MESSAGE BUFFER WORD 0

| U-0           | U-0                                           | U-0               | R/W-x         | R/W-x                              | R/W-x | R/W-x           | R/W-x |  |  |

|---------------|-----------------------------------------------|-------------------|---------------|------------------------------------|-------|-----------------|-------|--|--|

|               | —                                             | _                 | SID10         | SID9                               | SID8  | SID7            | SID6  |  |  |

| bit 15        |                                               |                   |               |                                    |       |                 | bit 8 |  |  |

| R/W-x         | R/W-x                                         | R/W-x             | R/W-x         | R/W-x                              | R/W-x | R/W-x           | R/W-x |  |  |

| SID5          | SID4                                          | SID3              | SID2          | SID1                               | SID0  | SRR             | IDE   |  |  |

| bit 7         |                                               |                   |               |                                    |       |                 | bit 0 |  |  |

| Legend:       |                                               |                   |               |                                    |       |                 |       |  |  |

| R = Readabl   | e bit                                         | W = Writable      | bit           | U = Unimplemented bit, read as '0' |       |                 |       |  |  |

| -n = Value at | POR                                           | '1' = Bit is set  |               | '0' = Bit is cle                   | eared | x = Bit is unkr | nown  |  |  |

|               |                                               |                   |               |                                    |       |                 |       |  |  |

| bit 15-13     | Unimplemen                                    | ted: Read as '    | כי            |                                    |       |                 |       |  |  |

| bit 12-2      | <b>SID&lt;10:0&gt;:</b> S                     | Standard Identifi | ier bits      |                                    |       |                 |       |  |  |

| bit 1         | SRR: Substitu                                 | ute Remote Re     | quest bit     |                                    |       |                 |       |  |  |

|               | When IDE =                                    | 0:                |               |                                    |       |                 |       |  |  |

|               | 1 = Message                                   | will request rer  | note transmis | ssion                              |       |                 |       |  |  |

|               | 0 = Normal m                                  | nessage           |               |                                    |       |                 |       |  |  |

|               | When IDE = 1                                  | <u>1:</u>         |               |                                    |       |                 |       |  |  |

|               | The SRR bit r                                 | must be set to '  | 1'.           |                                    |       |                 |       |  |  |

| bit 0         | IDE: Extende                                  | d Identifier bit  |               |                                    |       |                 |       |  |  |

|               | 1 = Message will transmit Extended Identifier |                   |               |                                    |       |                 |       |  |  |

|               | 0 = Message                                   | will transmit St  | andard Identi | fier                               |       |                 |       |  |  |

|               |                                               |                   |               |                                    |       |                 |       |  |  |

#### BUFFER 21-2: ECAN™ MESSAGE BUFFER WORD 1

| U-0             | U-0   | U-0              | U-0   | R/W-x            | R/W-x            | R/W-x           | R/W-x |

|-----------------|-------|------------------|-------|------------------|------------------|-----------------|-------|

| —               | —     | —                | _     | EID17            | EID16            | EID15           | EID14 |

| bit 15          |       |                  |       |                  |                  |                 | bit 8 |

|                 |       |                  |       |                  |                  |                 |       |

| R/W-x           | R/W-x | R/W-x            | R/W-x | R/W-x            | R/W-x            | R/W-x           | R/W-x |

| EID13           | EID12 | EID11            | EID10 | EID9             | EID8             | EID7            | EID6  |

| bit 7           |       |                  |       |                  |                  |                 | bit 0 |

|                 |       |                  |       |                  |                  |                 |       |

| Legend:         |       |                  |       |                  |                  |                 |       |

| R = Readable    | bit   | W = Writable I   | bit   | U = Unimpler     | nented bit, read | as '0'          |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

|                 |       |                  |       |                  |                  |                 |       |

bit 15-12 Unimplemented: Read as '0'

bit 11-0 EID<17:6>: Extended Identifier bits

# 23.0 10-BIT/12-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

- **Note 1:** This data sheet summarizes the features of the dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. То complement the information in this data sheet. refer to "Analog-to-Digital Converter (ADC)" (DS70621) in the "dsPIC33/PIC24 Family Reference Manual', which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices have one ADC module. The ADC module supports up to 16 analog input channels.

On ADC1, the AD12B bit (AD1CON1<10>) allows the ADC module to be configured by the user as either a 10-bit, 4 Sample-and-Hold (S&H) ADC (default configuration) or a 12-bit, 1 S&H ADC.

Note: The ADC module needs to be disabled before modifying the AD12B bit.

## 23.1 Key Features

## 23.1.1 10-BIT ADC CONFIGURATION

The 10-bit ADC configuration has the following key features:

- Successive Approximation (SAR) conversion

- · Conversion speeds of up to 1.1 Msps

- · Up to 16 analog input pins

- Connections to three internal op amps

- Connections to the Charge Time Measurement Unit (CTMU) and temperature measurement diode

- Channel selection and triggering can be controlled by the Peripheral Trigger Generator (PTG)

- External voltage reference input pins

- · Simultaneous sampling of:

- Up to four analog input pins

- Three op amp outputs

- Combinations of analog inputs and op amp outputs

- Automatic Channel Scan mode

- Selectable conversion Trigger source

- · Selectable Buffer Fill modes

- Four result alignment options (signed/unsigned, fractional/integer)

- Operation during CPU Sleep and Idle modes

#### 23.1.2 12-BIT ADC CONFIGURATION

The 12-bit ADC configuration supports all the features listed above, with the exception of the following:

- In the 12-bit configuration, conversion speeds of up to 500 ksps are supported

- There is only one S&H amplifier in the 12-bit configuration; therefore, simultaneous sampling of multiple channels is not supported.

Depending on the particular device pinout, the ADC can have up to 16 analog input pins, designated AN0 through AN15. These analog inputs are shared with op amp inputs and outputs, comparator inputs, and external voltage references. When op amp/comparator functionality is enabled, or an external voltage reference is used, the analog input that shares that pin is no longer available. The actual number of analog input pins, op amps and external voltage reference input configuration depends on the specific device.

A block diagram of the ADC module is shown in Figure 23-1. Figure 23-2 provides a diagram of the ADC conversion clock period.

#### REGISTER 23-5: AD1CHS123: ADC1 INPUT CHANNEL 1, 2, 3 SELECT REGISTER (CONTINUED)

bit 0

**CH123SA:** Channel 1, 2, 3 Positive Input Select for Sample MUXA bit In 12-bit mode (AD21B = 1), CH123SA is Unimplemented and is Read as '0':

| Value          | ADC Channel |         |         |  |  |  |  |  |

|----------------|-------------|---------|---------|--|--|--|--|--|

| value          | CH1         | CH2     | CH3     |  |  |  |  |  |

| 1 <b>(2)</b>   | OA1/AN3     | OA2/AN0 | OA3/AN6 |  |  |  |  |  |

| 0 <b>(1,2)</b> | OA2/AN0     | AN1     | AN2     |  |  |  |  |  |

**Note 1:** AN0 through AN7 are repurposed when comparator and op amp functionality is enabled. See Figure 23-1 to determine how enabling a particular op amp or comparator affects selection choices for Channels 1, 2 and 3.

2: The OAx input is used if the corresponding op amp is selected (OPMODE (CMxCON<10>) = 1); otherwise, the ANx input is used.

## 24.2 PTG Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 24.2.1 KEY RESOURCES

- "Peripheral Trigger Generator" (DS70669) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

| oit 3-0 | Step<br>Command        | OPTION<3:0> | Option Description                                                                                      |

|---------|------------------------|-------------|---------------------------------------------------------------------------------------------------------|

|         | PTGCTRL(1)             | 0000        | Reserved.                                                                                               |

|         |                        | 0001        | Reserved.                                                                                               |

|         |                        | 0010        | Disable Step Delay Timer (PTGSD).                                                                       |

|         |                        | 0011        | Reserved.                                                                                               |

|         |                        | 0100        | Reserved.                                                                                               |

|         |                        | 0101        | Reserved.                                                                                               |

|         |                        | 0110        | Enable Step Delay Timer (PTGSD).                                                                        |

|         |                        | 0111        | Reserved.                                                                                               |

|         |                        | 1000        | Start and wait for the PTG Timer0 to match the Timer0 Limit Register.                                   |

|         |                        | 1001        | Start and wait for the PTG Timer1 to match the Timer1 Limit Register.                                   |

|         |                        | 1010        | Reserved.                                                                                               |

|         |                        | 1011        | Wait for the software trigger bit transition from low-to-high before continuing (PTGSWT = $0$ to $1$ ). |

|         |                        | 1100        | Copy contents of the Counter 0 register to the AD1CHS0 register.                                        |

|         |                        | 1101        | Copy contents of the Counter 1 register to the AD1CHS0 register.                                        |

|         |                        | 1110        | Copy contents of the Literal 0 register to the AD1CHS0 register.                                        |

|         |                        | 1111        | Generate triggers indicated in the Broadcast Trigger Enable register (PTGBTE).                          |

|         | PTGADD(1)              | 0000        | Add contents of the PTGADJ register to the Counter 0 Limit register (PTGC0LIM).                         |

|         |                        | 0001        | Add contents of the PTGADJ register to the Counter 1 Limit register (PTGC1LIM).                         |

|         |                        | 0010        | Add contents of the PTGADJ register to the Timer0 Limit register (PTGT0LIM).                            |

|         |                        | 0011        | Add contents of the PTGADJ register to the Timer1 Limit register (PTGT1LIM).                            |

|         |                        | 0100        | Add contents of the PTGADJ register to the Step Delay Limit register (PTGSDLIM)                         |

|         |                        | 0101        | Add contents of the PTGADJ register to the Literal 0 register (PTGL0).                                  |

|         |                        | 0110        | Reserved.                                                                                               |

|         |                        | 0111        | Reserved.                                                                                               |

|         | PTGCOPY <sup>(1)</sup> | 1000        | Copy contents of the PTGHOLD register to the Counter 0 Limit register (PTGC0LIM).                       |

|         |                        | 1001        | Copy contents of the PTGHOLD register to the Counter 1 Limit register (PTGC1LIM).                       |

|         |                        | 1010        | Copy contents of the PTGHOLD register to the Timer0 Limit register (PTGT0LIM).                          |

|         |                        | 1011        | Copy contents of the PTGHOLD register to the Timer1 Limit register (PTGT1LIM).                          |

|         |                        | 1100        | Copy contents of the PTGHOLD register to the Step Delay Limit register (PTGSDLIM).                      |

|         |                        | 1101        | Copy contents of the PTGHOLD register to the Literal 0 register (PTGL0).                                |

|         |                        | 1110        | Reserved.                                                                                               |

|         |                        | 1111        | Reserved.                                                                                               |

## TABLE 24-1: PTG STEP COMMAND FORMAT (CONTINUED)

Note 1: All reserved commands or options will execute but have no effect (i.e., execute as a NOP instruction).

2: Refer to Table 24-2 for the trigger output descriptions.

3: This feature is only available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

| AC CHARAG            | CTERISTICS                               |                                             | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |     |     |     |

|----------------------|------------------------------------------|---------------------------------------------|-------------------------------------------------------|-----|-----|-----|

| Maximum<br>Data Rate | Master<br>Transmit Only<br>(Half-Duplex) | Master<br>Transmit/Receive<br>(Full-Duplex) | Slave<br>Transmit/Receive<br>(Full-Duplex)            | CKE | СКР | SMP |

| 15 MHz               | Table 30-33                              | _                                           | _                                                     | 0,1 | 0,1 | 0,1 |

| 9 MHz                | _                                        | Table 30-34                                 | —                                                     | 1   | 0,1 | 1   |

| 9 MHz                | —                                        | Table 30-35                                 | —                                                     | 0   | 0,1 | 1   |

| 15 MHz               | —                                        | —                                           | Table 30-36                                           | 1   | 0   | 0   |

| 11 MHz               | _                                        | —                                           | Table 30-37                                           | 1   | 1   | 0   |

| 15 MHz               | —                                        | —                                           | Table 30-38                                           | 0   | 1   | 0   |

| 11 MHz               | —                                        | —                                           | Table 30-39                                           | 0   | 0   | 0   |

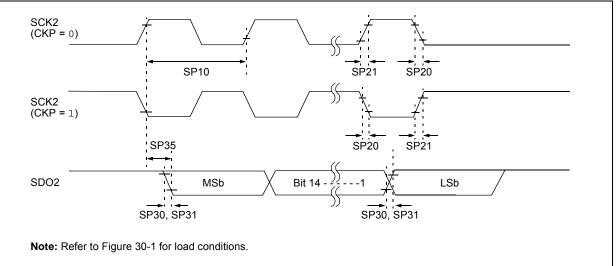

#### TABLE 30-33: SPI2 MAXIMUM DATA/CLOCK RATE SUMMARY

#### FIGURE 30-14: SPI2 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 0) TIMING CHARACTERISTICS

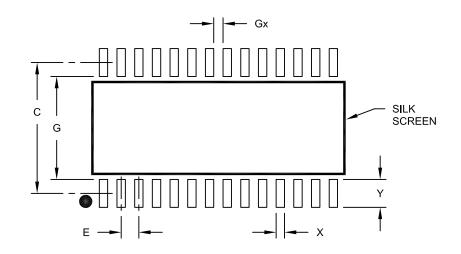

28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## RECOMMENDED LAND PATTERN

|                          | Units | N    |          | S    |

|--------------------------|-------|------|----------|------|

| Dimension Limits         |       | MIN  | NOM      | MAX  |

| Contact Pitch            | Е     |      | 1.27 BSC |      |

| Contact Pad Spacing      | С     |      | 9.40     |      |

| Contact Pad Width (X28)  | Х     |      |          | 0.60 |

| Contact Pad Length (X28) | Y     |      |          | 2.00 |

| Distance Between Pads    | Gx    | 0.67 |          |      |

| Distance Between Pads    | G     | 7.40 |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2052A

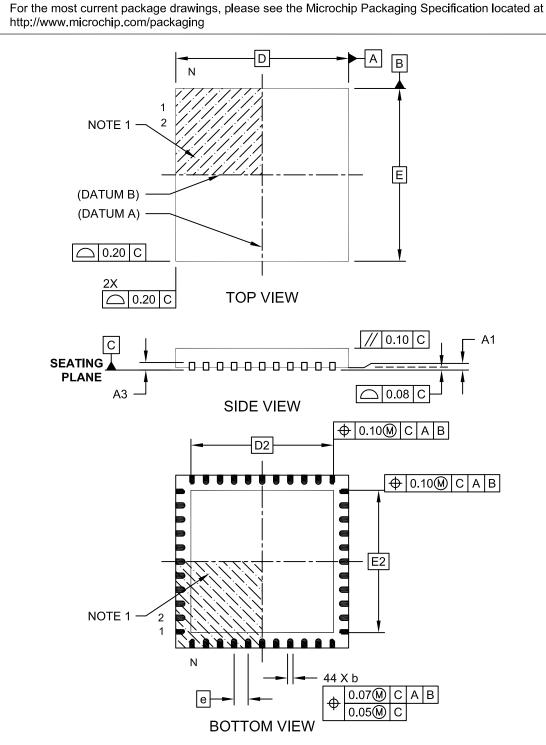

## 44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN]

Note:

Microchip Technology Drawing C04-103C Sheet 1 of 2

## **Revision F (November 2012)**

Removed "Preliminary" from data sheet footer.

#### **Revision G (March 2013)**

This revision includes the following global changes:

- changes "FLTx" pin function to "FLTx" on all occurrences

- adds Section 31.0 "High-Temperature Electrical Characteristics" for high-temperature (+150°C) data

This revision also includes minor typographical and formatting changes throughout the text.

Other major changes are referenced by their respective section in Table A-5.

| Section Name                                                         | Update Description                                                                                                                                                                                                                                                                                                                                                                   |

|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cover Section                                                        | <ul> <li>Changes internal oscillator specification to 1.0%</li> <li>Changes I/O sink/source values to 12 mA or 6 mA</li> <li>Corrects 44-pin VTLA pin diagram (pin 32 now shows as 5V tolerant)</li> </ul>                                                                                                                                                                           |

| Section 4.0 "Memory<br>Organization"                                 | <ul> <li>Deletes references to Configuration Shadow registers</li> <li>Corrects the spelling of the JTAGIP and PTGWDTIP bits throughout</li> <li>Corrects the Reset value of all IOCON registers as C000h</li> <li>Adds footnote to Table 4-42 to indicate the absence of Comparator 3 in 28-pin devices</li> </ul>                                                                  |

| Section 6.0 "Resets"                                                 | <ul> <li>Removes references to cold and warm Resets, and clarifies the initial configuration of<br/>the device clock source on all Resets</li> </ul>                                                                                                                                                                                                                                 |

| Section 7.0 "Interrupt<br>Controller"                                | Corrects the definition of GIE as "Global Interrupt Enable" (not "General")                                                                                                                                                                                                                                                                                                          |

| Section 9.0 "Oscillator<br>Configuration"                            | <ul> <li>Clarifies the behavior of the CF bit when cleared in software</li> <li>Removes POR behavior footnotes from all control registers</li> <li>Corrects the tuning range of the TUN&lt;5:0&gt; bits in Register 9-4 to an overall range ±1.5%</li> </ul>                                                                                                                         |

| Section 13.0 "Timer2/3 and Timer4/5"                                 | <ul> <li>Clarifies the presence of the ADC Trigger in 16-bit Timer3 and Timer5, as well as the<br/>32-bit timers</li> </ul>                                                                                                                                                                                                                                                          |

| Section 15.0 "Output<br>Compare"                                     | <ul> <li>Corrects the first trigger source for SYNCSEL&lt;4:0&gt; (OCxCON2&lt;4:0&gt;) as OCxRS<br/>match</li> </ul>                                                                                                                                                                                                                                                                 |

| Section 16.0 "High-Speed<br>PWM Module"                              | <ul> <li>Clarifies the source of the PWM interrupts in Figure 16-1</li> <li>Corrects the Reset states of IOCONx&lt;15:14&gt; in Register 16-13 as '11'</li> </ul>                                                                                                                                                                                                                    |

| Section 17.0 "Quadrature<br>Encoder Interface (QEI)<br>Module"       | <ul> <li>Clarifies the operation of the IMV&lt;1:0&gt; bits (QEICON&lt;9:8&gt;) with updated text and additional notes</li> <li>Corrects the first prescaler value for QFVDIV&lt;2:0&gt; (QEI10C&lt;13:11&gt;), now 1:128</li> </ul>                                                                                                                                                 |

| Section 23.0 "10-Bit/12-Bit<br>Analog-to-Digital Converter<br>(ADC)" | <ul> <li>Adds note to Figure 23-1 that Op Amp 3 is not available in 28-pin devices</li> <li>Changes "sample clock" to "sample trigger" in AD1CON1 (Register 23-1)</li> <li>Clarifies footnotes on op amp usage in Registers 23-5 and 23-6</li> </ul>                                                                                                                                 |

| Section 25.0 "Op Amp/<br>Comparator Module"                          | <ul> <li>Adds Note text to indicate that Comparator 3 is unavailable in 28-pin devices</li> <li>Splits Figure 25-1 into two figures for clearer presentation (Figure 25-1 for Op amp/<br/>Comparators 1 through 3, Figure 25-2 for Comparator 4). Subsequent figures are<br/>renumbered accordingly.</li> <li>Corrects reference description in xxxxx (now (AVDD+AVSS)/2)</li> </ul> |

| Section 27.0 "Special Features"                                      | <ul> <li>Changes CMSTAT&lt;15&gt; in Register 25-1 to "PSIDL"</li> <li>Corrects the addresses of all Configuration bytes for 512 Kbyte devices</li> </ul>                                                                                                                                                                                                                            |

#### TABLE A-5: MAJOR SECTION UPDATES

## INDEX

## Α

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| AC Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1                                                                            |

| 10-Bit ADC Conversion Requirements 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5                                                                            |

| 12-Bit ADC Conversion Requirements 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3                                                                            |

| ADC Module45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 9                                                                            |

| ADC Module (10-Bit Mode)461, 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3                                                                            |

| ADC Module (12-Bit Mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3                                                                            |