#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                        |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 70 MIPs                                                                       |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                 |

| Number of I/O              | 21                                                                            |

| Program Memory Size        | 32KB (10.7K x 24)                                                             |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 2K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 6x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                |

| Supplier Device Package    | 28-SSOP                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep32mc202-i-ss |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

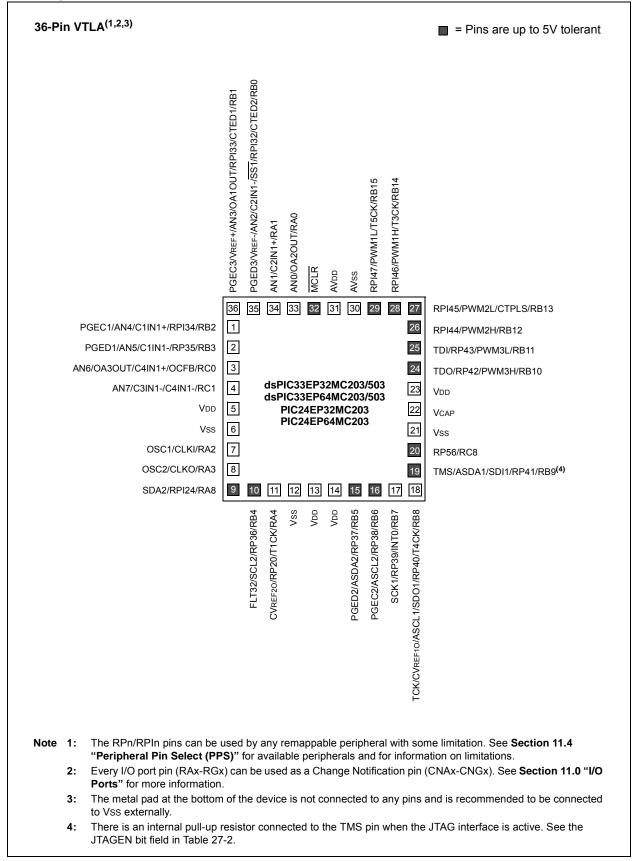

### Pin Diagrams (Continued)

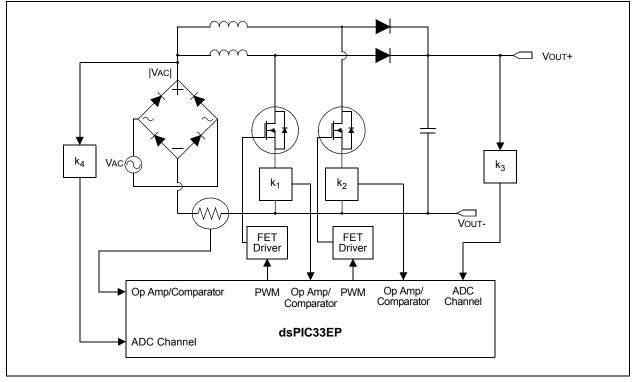

#### FIGURE 2-7: INTERLEAVED PFC

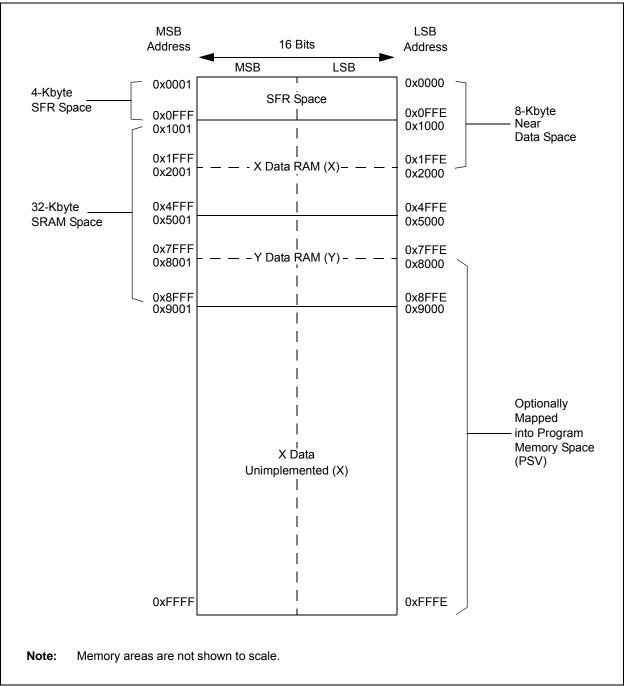

# FIGURE 4-10: DATA MEMORY MAP FOR dsPIC33EP256MC20X/50X AND dsPIC33EP256GP50X DEVICES

### TABLE 4-49: PORTD REGISTER MAP FOR PIC24EPXXXGP/MC206 AND dsPIC33EPXXXGP/MC206/506 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7 | Bit 6  | Bit 5  | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|--------|-------|--------|--------|-------|-------|-------|-------|-------|---------------|

| TRISD        | 0E30  | _      | _      | _      |        | _      | _      | _     | TRISD8 |       | TRISD6 | TRISD5 |       |       |       |       | _     | 0160          |

| PORTD        | 0E32  | _      | _      |        | _      | _      | _      |       | RD8    | —     | RD6    | RD5    | —     | _     | _     | _     |       | xxxx          |

| LATD         | 0E34  | _      | _      |        | _      | _      | _      |       | LATD8  | —     | LATD6  | LATD5  | —     | _     | _     | _     |       | xxxx          |

| ODCD         | 0E36  | _      |        |        | -      |        |        |       | ODCD8  | —     | ODCD6  | ODCD5  | —     | _     | _     | _     |       | 0000          |

| CNEND        | 0E38  | _      |        |        | -      |        |        |       | CNIED8 | —     | CNIED6 | CNIED5 | —     | _     | _     | _     |       | 0000          |

| CNPUD        | 0E3A  | _      | _      |        | _      | _      | _      |       | CNPUD8 | —     | CNPUD6 | CNPUD5 | —     | _     | _     | _     |       | 0000          |

| CNPDD        | 0E3C  | _      | _      |        | _      | _      | _      |       | CNPDD8 | —     | CNPDD6 | CNPDD5 | —     | _     | _     | _     |       | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-50: PORTE REGISTER MAP FOR PIC24EPXXXGP/MC206 AND dsPIC33EPXXXGP/MC206/506 DEVICES ONLY

| File<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|---------|---------|---------|---------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| TRISE        | 0E40  | TRISE15 | TRISE14 | TRISE13 | TRISE12 | —      | _      | _     | —     | _     |       | -     | —     | —     | _     | —     |       | F000          |

| PORTE        | 0E42  | RE15    | RE14    | RE13    | RE12    | _      | —      | —     | —     |       | —     | —     | _     | —     | —     | —     | —     | xxxx          |

| LATE         | 0E44  | LATE15  | LATE14  | LATE13  | LATE12  | _      | _      |       | —     | _     | _     |       | _     | —     | -     | —     | _     | xxxx          |

| ODCE         | 0E46  | ODCE15  | ODCE14  | ODCE13  | ODCE12  | —      | -      | -     | -     |       |       | -     | —     | —     | _     | _     |       | 0000          |

| CNENE        | 0E48  | CNIEE15 | CNIEE14 | CNIEE13 | CNIEE12 | _      | —      | —     | —     | -     | —     | —     | _     | —     | —     | —     | —     | 0000          |

| CNPUE        | 0E4A  | CNPUE15 | CNPUE14 | CNPUE13 | CNPUE12 | _      | _      |       | —     | _     | _     |       | _     | —     | -     | —     | _     | 0000          |

| CNPDE        | 0E4C  | CNPDE15 | CNPDE14 | CNPDE13 | CNPDE12 | _      | _      | _     | _     | -     | _     | —     | _     | —     | _     | _     | _     | 0000          |

| ANSELE       | 0E4E  | ANSE15  | ANSE14  | ANSE13  | ANSE12  |        | —      | _     | —     | _     | _     | _     |       |       | _     |       | _     | F000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-51: PORTF REGISTER MAP FOR PIC24EPXXXGP/MC206 AND dsPIC33EPXXXGP/MC206/506 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|--------|--------|---------------|

| TRISF        | 0E50  | —      | -      | —      |        | —      |        | —     | -     | -     | —     | -     | -     | —     | -     | TRISF1 | TRISF0 | 0003          |

| PORTF        | 0E52  | —      | —      | _      | —      | —      | —      | —     | _     | —     | —     | —     | —     | —     | —     | RF1    | RF0    | xxxx          |

| LATF         | 0E54  | —      | —      | —      | —      | —      | —      | —     | —     | —     | —     | —     | —     | —     | —     | LATF1  | LATF0  | xxxx          |

| ODCF         | 0E56  | _      | -      | _      | -      | —      | -      | —     |       |       | —     |       |       | _     | -     | ODCF1  | ODCF0  | 0000          |

| CNENF        | 0E58  |        | —      | -      |        | —      | -      | _     | -     | -     | —     | -     | -     | —     | -     | CNIEF1 | CNIEF0 | 0000          |

| CNPUF        | 0E5A  | —      | —      | —      | —      | —      | —      | —     | —     | —     | —     | —     | —     | —     | —     | CNPUF1 | CNPUF0 | 0000          |

| CNPDF        | 0E5C  | _      | _      | _      | _      | -      |        | _     | _     | _     | _     | _     | _     | _     | -     | CNPDF1 | CNPDF0 | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

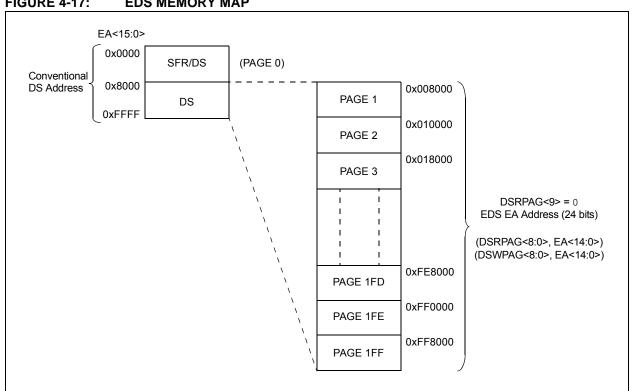

#### 4.4.2 EXTENDED X DATA SPACE

The lower portion of the base address space range, between 0x0000 and 0x7FFF, is always accessible regardless of the contents of the Data Space Page registers. It is indirectly addressable through the register indirect instructions. It can be regarded as being located in the default EDS Page 0 (i.e., EDS address range of 0x000000 to 0x007FFF with the base address bit, EA<15> = 0, for this address range). However, Page 0 cannot be accessed through the upper 32 Kbytes, 0x8000 to 0xFFFF, of base Data Space, in combination with DSRPAG = 0x000 or DSWPAG = 0x000. Consequently, DSRPAG and DSWPAG are initialized to 0x001 at Reset.

- Note 1: DSxPAG should not be used to access Page 0. An EDS access with DSxPAG set to 0x000 will generate an address error trap.

- 2: Clearing the DSxPAG in software has no effect.

The remaining pages, including both EDS and PSV pages, are only accessible using the DSRPAG or DSWPAG registers in combination with the upper 32 Kbytes, 0x8000 to 0xFFFF, of the base address, where base address bit, EA<15> = 1.

For example, when DSRPAG = 0x001 or DSWPAG = 0x001, accesses to the upper 32 Kbytes, 0x8000 to 0xFFFF, of the Data Space will map to the EDS address range of 0x008000 to 0x00FFFF. When DSRPAG = 0x002 or DSWPAG = 0x002, accesses to the upper 32 Kbytes of the Data Space will map to the EDS address range of 0x010000 to 0x017FFF and so on, as shown in the EDS memory map in Figure 4-17.

For more information on the PSV page access using Data Space Page registers, refer to the "**Program Space Visibility from Data Space**" section in "**Program Memory**" (DS70613) of the "*dsPIC33/ PIC24 Family Reference Manual*".

#### FIGURE 4-17: EDS MEMORY MAP

NOTES:

| R/W-1           | R/W-1              | R/W-0                                  | R/W-0                      | R/W-0                | R/W-0                     | R/W-0           | R/W-0  |

|-----------------|--------------------|----------------------------------------|----------------------------|----------------------|---------------------------|-----------------|--------|

| PENH            | PENL               | POLH                                   | POLL                       | PMOD1 <sup>(1)</sup> | PMOD0 <sup>(1)</sup>      | OVRENH          | OVRENL |

| bit 15          |                    | •                                      |                            |                      |                           |                 | bit    |

| R/W-0           | R/W-0              | R/W-0                                  | R/W-0                      | R/W-0                | R/W-0                     | R/W-0           |        |

| -               | -                  | -                                      |                            | -                    | -                         | -               | R/W-0  |

| OVRDAT1         | OVRDAT0            | FLTDAT1                                | FLTDAT0                    | CLDAT1               | CLDAT0                    | SWAP            | OSYNC  |

| bit 7           |                    |                                        |                            |                      |                           |                 | bit    |

| Legend:         |                    |                                        |                            |                      |                           |                 |        |

| R = Readable    | bit                | W = Writable                           | bit                        | U = Unimpler         | nented bit, read          | l as '0'        |        |

| -n = Value at F | POR                | '1' = Bit is set                       |                            | '0' = Bit is cle     | ared                      | x = Bit is unkr | nown   |

| bit 15          |                    | xH Output Pin                          | Ownorship hit              |                      |                           |                 |        |

| bit 15          |                    | odule controls                         | •                          |                      |                           |                 |        |

|                 |                    | dule controls F                        |                            |                      |                           |                 |        |

| bit 14          |                    | L Output Pin                           | •                          |                      |                           |                 |        |

|                 | 1 = PWMx mo        | odule controls                         | PWMxL pin                  |                      |                           |                 |        |

|                 | 0 = GPIO mo        | dule controls F                        | WMxL pin                   |                      |                           |                 |        |

| bit 13          | POLH: PWM          | xH Output Pin                          | Polarity bit               |                      |                           |                 |        |

|                 |                    | oin is active-low                      |                            |                      |                           |                 |        |

|                 |                    | oin is active-hig                      | •                          |                      |                           |                 |        |

| bit 12          |                    | L Output Pin F                         | •                          |                      |                           |                 |        |

|                 |                    | in is active-low<br>in is active-hig   |                            |                      |                           |                 |        |

| bit 11-10       | PMOD<1:0>:         | PWMx # I/O F                           | in Mode bits <sup>(1</sup> | )                    |                           |                 |        |

|                 | 11 = Reserve       | ,                                      |                            |                      |                           |                 |        |

|                 |                    | /O pin pair is ir<br>/O pin pair is ir |                            |                      |                           |                 |        |

|                 |                    | O pin pair is in<br>O pin pair is ir   |                            |                      |                           |                 |        |

| bit 9           |                    | verride Enable                         | •                          |                      |                           |                 |        |

|                 |                    | <1> controls or                        |                            |                      |                           |                 |        |

|                 |                    | nerator contro                         | •                          | •                    |                           |                 |        |

| bit 8           | OVRENL: Ov         | erride Enable                          | for PWMxL Pir              | n bit                |                           |                 |        |

|                 | 1 = OVRDAT         | <0> controls or                        | utput on PWM               | xL pin               |                           |                 |        |

|                 | •                  | nerator contro                         |                            |                      |                           |                 |        |

| bit 7-6         |                    |                                        |                            |                      | de is Enabled b           |                 |        |

|                 |                    |                                        |                            |                      | by OVRDAT<<br>by OVRDAT<0 |                 |        |

| bit 5-4         | FLTDAT<1:0         | >: Data for PW                         | MxH and PWN                | ۰<br>MxL Pins if FLT | MOD is Enable             | ed bits         |        |

|                 | If Fault is active | ve, PWMxH is                           | driven to the s            | tate specified       | by FLTDAT<1>.             |                 |        |

|                 | If Fault is active | ve, PWMxL is                           | driven to the s            | tate specified b     | by FLTDAT<0>.             |                 |        |

| bit 3-2         | CLDAT<1:0>         | : Data for PWN                         | /IxH and PWM               | xL Pins if CLM       | 10D is Enabled            | bits            |        |

|                 |                    |                                        |                            | •                    | ecified by CLDA           |                 |        |

|                 |                    | IS AULIVE. F VVI                       |                            |                      |                           |                 |        |

| Note 1: The     |                    |                                        |                            |                      | enabled (PTEN             |                 |        |

## REGISTER 16-13: IOCONx: PWMx I/O CONTROL REGISTER<sup>(2)</sup>

2: If the PWMLOCK Configuration bit (FOSCSEL<6>) is a '1', the IOCONx register can only be written after the unlock sequence has been executed.

## 19.1 I<sup>2</sup>C Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this UDL increases |

|-------|---------------------------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                                               |

|       | http://www.microchip.com/wwwproducts/                                                                   |

|       | Devices.aspx?dDocName=en555464                                                                          |

### 19.1.1 KEY RESOURCES

- "Inter-Integrated Circuit (I<sup>2</sup>C)" (DS70330) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

#### REGISTER 20-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 5 | <ul> <li>ADDEN: Address Character Detect bit (bit 8 of received data = 1)</li> <li>1 = Address Detect mode is enabled; if 9-bit mode is not selected, this does not take effect</li> <li>0 = Address Detect mode is disabled</li> </ul>                                                          |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4 | RIDLE: Receiver Idle bit (read-only)<br>1 = Receiver is Idle<br>0 = Receiver is active                                                                                                                                                                                                           |

| bit 3 | <b>PERR:</b> Parity Error Status bit (read-only) 1 = Parity error has been detected for the current character (character at the top of the receive FIFO) 0 = Parity error has not been detected                                                                                                  |

| bit 2 | <pre>FERR: Framing Error Status bit (read-only) 1 = Framing error has been detected for the current character (character at the top of the receive FIFO) 0 = Framing error has not been detected</pre>                                                                                           |

| bit 1 | <ul> <li>OERR: Receive Buffer Overrun Error Status bit (clear/read-only)</li> <li>1 = Receive buffer has overflowed</li> <li>0 = Receive buffer has not overflowed; clearing a previously set OERR bit (1 → 0 transition) resets the receiver buffer and the UxRSR to the empty state</li> </ul> |

| bit 0 | <ul> <li>URXDA: UARTx Receive Buffer Data Available bit (read-only)</li> <li>1 = Receive buffer has data, at least one more character can be read</li> <li>0 = Receive buffer is empty</li> </ul>                                                                                                |

**Note 1:** Refer to the "**UART**" (DS70582) section in the "*dsPIC33/PIC24 Family Reference Manual*" for information on enabling the UARTx module for transmit operation.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

## REGISTER 21-13: CxBUFPNT2: ECANx FILTER 4-7 BUFFER POINTER REGISTER 2

| R/W-0            |       |                  |       |                     |                |                 |       |

|------------------|-------|------------------|-------|---------------------|----------------|-----------------|-------|

|                  | R/W-0 | R/W-0            | R/W-0 | R/W-0               | R/W-0          | R/W-0           | R/W-0 |

|                  | F7BF  | °<3:0>           |       |                     | F6BF           | P<3:0>          |       |

| bit 15           |       |                  |       |                     |                |                 | bit 8 |

| R/W-0            | R/W-0 | R/W-0            | R/W-0 | R/W-0               | R/W-0          | R/W-0           | R/W-0 |

|                  | F5BF  | °<3:0>           |       |                     | F4BF           | P<3:0>          |       |

| bit 7            |       |                  |       |                     |                |                 | bit 0 |

| Legend:          |       |                  |       |                     |                |                 |       |

| R = Readable bi  | t     | W = Writable     | bit   | U = Unimplemer      | nted bit, read | d as '0'        |       |

| -n = Value at PO | R     | '1' = Bit is set |       | '0' = Bit is cleare | d              | x = Bit is unkr | nown  |

|          | 1110 = Filter hits received in RX Buffer 14                              |

|----------|--------------------------------------------------------------------------|

|          |                                                                          |

|          | •                                                                        |

|          | 0001 = Filter hits received in RX Buffer 1                               |

|          | 0000 = Filter hits received in RX Buffer 0                               |

| bit 11-8 | F6BP<3:0>: RX Buffer Mask for Filter 6 bits (same values as bits<15:12>) |

| bit 7-4  | F5BP<3:0>: RX Buffer Mask for Filter 5 bits (same values as bits<15:12>) |

| bit 3-0  | F4BP<3:0>: RX Buffer Mask for Filter 4 bits (same values as bits<15:12>) |

#### REGISTER 21-14: CxBUFPNT3: ECANx FILTER 8-11 BUFFER POINTER REGISTER 3

| R/W-0         | R/W-0                                              | R/W-0                                                                                         | R/W-0                                          | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|---------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------|------------------------------------------------|------------------|-----------------|-----------------|-------|

|               | F11BF                                              | P<3:0>                                                                                        |                                                |                  | F10B            | SP<3:0>         |       |

| bit 15        |                                                    |                                                                                               |                                                |                  |                 |                 | bit 8 |

| R/W-0         | R/W-0                                              | R/W-0                                                                                         | R/W-0                                          | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|               | F9BP                                               | 2<3:0>                                                                                        |                                                |                  | F8B             | P<3:0>          |       |

| bit 7         |                                                    |                                                                                               |                                                |                  |                 |                 | bit 0 |

| Legend:       |                                                    |                                                                                               |                                                |                  |                 |                 |       |

| R = Readabl   | le bit                                             | W = Writable                                                                                  | bit                                            | U = Unimplen     | nented bit, rea | d as '0'        |       |

| -n = Value at | t POR                                              | '1' = Bit is set                                                                              |                                                | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

| bit 15-12     | 1111 = Filter<br>1110 = Filter<br>•<br>•<br>•<br>• | RX Buffer Mar<br>hits received ir<br>hits received ir<br>hits received ir<br>hits received ir | n RX FIFO bu<br>n RX Buffer 1<br>n RX Buffer 1 | iffer<br>4       |                 |                 |       |

| bit 11-8      | F10BP<3:0>                                         | : RX Buffer Ma                                                                                | sk for Filter 1                                | 0 bits (same val | ues as bits<1   | 5:12>)          |       |

| bit 7-4       | F9BP<3:0>:                                         | RX Buffer Mas                                                                                 | k for Filter 9 b                               | oits (same value | s as bits<15:1  | 2>)             |       |

| bit 3-0       | F8BP<3:0>:                                         | RX Buffer Mas                                                                                 | k for Filter 8 k                               | oits (same value | s as bits<15:1  | 2>)             |       |

|               |                                                    |                                                                                               |                                                |                  |                 |                 |       |

© 2011-2013 Microchip Technology Inc.

## 22.0 CHARGE TIME MEASUREMENT UNIT (CTMU)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Charge Time Measurement Unit (CTMU)" (DS70661) in the "dsPIC33/PIC24 Family Reference Manual", which is available on the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Charge Time Measurement Unit is a flexible analog module that provides accurate differential time measurement between pulse sources, as well as asynchronous pulse generation. Its key features include:

- Four Edge Input Trigger Sources

- Polarity Control for Each Edge Source

- Control of Edge Sequence

- Control of Response to Edges

- · Precise Time Measurement Resolution of 1 ns

- Accurate Current Source Suitable for Capacitive Measurement

- On-Chip Temperature Measurement using a Built-in Diode

Together with other on-chip analog modules, the CTMU can be used to precisely measure time, measure capacitance, measure relative changes in capacitance or generate output pulses that are independent of the system clock.

The CTMU module is ideal for interfacing with capacitive-based sensors. The CTMU is controlled through three registers: CTMUCON1, CTMUCON2 and CTMUICON. CTMUCON1 and CTMUCON2 enable the module and control edge source selection, edge source polarity selection and edge sequencing. The CTMUICON register controls the selection and trim of the current source.

| R/W-0         | R/W-0                                                      | R/W-0                                 | R/W-0            | R/W-0              | R/W-0           | R/W-0           | R/W-0    |  |  |

|---------------|------------------------------------------------------------|---------------------------------------|------------------|--------------------|-----------------|-----------------|----------|--|--|

| EDG1MOD       | EDG1POL                                                    | EDG1SEL3                              | EDG1SEL2         | EDG1SEL1           | EDG1SEL0        | EDG2STAT        | EDG1STAT |  |  |

| bit 15        |                                                            | 1                                     |                  | 11                 |                 |                 | bit 8    |  |  |

|               |                                                            |                                       |                  |                    |                 |                 |          |  |  |

| R/W-0         | R/W-0                                                      | R/W-0                                 | R/W-0            | R/W-0              | R/W-0           | U-0             | U-0      |  |  |

| EDG2MOD       | EDG2POL                                                    | EDG2SEL3                              | EDG2SEL2         | EDG2SEL1           | EDG2SEL0        | —               | _        |  |  |

| bit 7         |                                                            |                                       |                  | 1 1                |                 | 1               | bit (    |  |  |

|               |                                                            |                                       |                  |                    |                 |                 |          |  |  |

| Legend:       |                                                            |                                       |                  |                    |                 |                 |          |  |  |

| R = Readabl   | le bit                                                     | W = Writable                          | oit              | U = Unimplem       | ented bit, read | l as '0'        |          |  |  |

| -n = Value at | POR                                                        | '1' = Bit is set                      |                  | '0' = Bit is clea  | red             | x = Bit is unkr | nown     |  |  |

|               |                                                            |                                       |                  |                    |                 |                 |          |  |  |

| bit 15        | EDG1MOD: E                                                 | Edge 1 Edge Sa                        | ampling Mode     | Selection bit      |                 |                 |          |  |  |

|               | 1 = Edge 1 is                                              | s edge-sensitive                      | 9                |                    |                 |                 |          |  |  |

|               | •                                                          | s level-sensitive                     |                  |                    |                 |                 |          |  |  |

| bit 14        |                                                            | dge 1 Polarity                        |                  |                    |                 |                 |          |  |  |

|               | 1 = Edge 1 is programmed for a positive edge response      |                                       |                  |                    |                 |                 |          |  |  |

| L:1 40 40     | 0 = Edge 1 is programmed for a negative edge response      |                                       |                  |                    |                 |                 |          |  |  |

| bit 13-10     | EDG1SEL<3:0>: Edge 1 Source Select bits<br>1xxx = Reserved |                                       |                  |                    |                 |                 |          |  |  |

|               | 01xx = Reserved                                            |                                       |                  |                    |                 |                 |          |  |  |

|               |                                                            | 011x = Reserved<br>0011 = CTED1 pin   |                  |                    |                 |                 |          |  |  |

|               | 0010 = CTEE                                                | •                                     |                  |                    |                 |                 |          |  |  |

|               | 0001 = OC1                                                 |                                       |                  |                    |                 |                 |          |  |  |

| hit O         | 0000 = Timer                                               |                                       | :+               |                    |                 |                 |          |  |  |

| bit 9         |                                                            | Edge 2 Status b                       |                  | vritten to control | the odge cou    | reo             |          |  |  |

|               | 1 = Edge 2 h                                               |                                       |                  |                    | the edge sou    | ice.            |          |  |  |

|               |                                                            | as not occurred                       | 1                |                    |                 |                 |          |  |  |

| bit 8         | EDG1STAT: E                                                | Edge 1 Status b                       | it               |                    |                 |                 |          |  |  |

|               |                                                            |                                       | 1 and can be v   | vritten to control | the edge sou    | rce.            |          |  |  |

|               | 1 = Edge 1 h                                               |                                       |                  |                    |                 |                 |          |  |  |

|               | -                                                          | as not occurred                       |                  |                    |                 |                 |          |  |  |

| bit 7         |                                                            | Edge 2 Edge Sa                        |                  | Selection bit      |                 |                 |          |  |  |

|               |                                                            | s edge-sensitive<br>s level-sensitive |                  |                    |                 |                 |          |  |  |

| bit 6         | •                                                          | dge 2 Polarity                        |                  |                    |                 |                 |          |  |  |

| Sit 0         |                                                            | s programmed f                        |                  | dae response       |                 |                 |          |  |  |

|               |                                                            | s programmed f                        |                  |                    |                 |                 |          |  |  |

| bit 5-2       | EDG2SEL<3                                                  | :0>: Edge 2 So                        | urce Select bits | 3                  |                 |                 |          |  |  |

|               | 1111 <b>= Rese</b>                                         | rved                                  |                  |                    |                 |                 |          |  |  |

|               | 01xx = Rese                                                |                                       |                  |                    |                 |                 |          |  |  |

|               | 0100 = CMP <sup>2</sup><br>0011 = CTEE                     |                                       |                  |                    |                 |                 |          |  |  |

|               | 0010 = CTEE                                                |                                       |                  |                    |                 |                 |          |  |  |

|               |                                                            | Ji pili                               |                  |                    |                 |                 |          |  |  |

|               | 0001 = OC1                                                 | module                                |                  |                    |                 |                 |          |  |  |

|               |                                                            | module                                |                  |                    |                 |                 |          |  |  |

#### REGISTER 22-2: CTMUCON2: CTMU CONTROL REGISTER 2

#### REGISTER 23-5: AD1CHS123: ADC1 INPUT CHANNEL 1, 2, 3 SELECT REGISTER (CONTINUED)

bit 0

**CH123SA:** Channel 1, 2, 3 Positive Input Select for Sample MUXA bit In 12-bit mode (AD21B = 1), CH123SA is Unimplemented and is Read as '0':

| Value          |         | ADC Channel |         |

|----------------|---------|-------------|---------|

| value          | CH1     | CH2         | CH3     |

| 1 <b>(2)</b>   | OA1/AN3 | OA2/AN0     | OA3/AN6 |

| 0 <b>(1,2)</b> | OA2/AN0 | AN1         | AN2     |

**Note 1:** AN0 through AN7 are repurposed when comparator and op amp functionality is enabled. See Figure 23-1 to determine how enabling a particular op amp or comparator affects selection choices for Channels 1, 2 and 3.

2: The OAx input is used if the corresponding op amp is selected (OPMODE (CMxCON<10>) = 1); otherwise, the ANx input is used.

# REGISTER 25-5: CMxMSKCON: COMPARATOR x MASK GATING CONTROL REGISTER (CONTINUED)

bit 3 ABEN: AND Gate B Input Enable bit 1 = MBI is connected to AND gate 0 = MBI is not connected to AND gate bit 2 ABNEN: AND Gate B Input Inverted Enable bit 1 = Inverted MBI is connected to AND gate 0 = Inverted MBI is not connected to AND gate bit 1 AAEN: AND Gate A Input Enable bit 1 = MAI is connected to AND gate 0 = MAI is not connected to AND gate bit 0 AANEN: AND Gate A Input Inverted Enable bit 1 = Inverted MAI is connected to AND gate 0 = Inverted MAI is not connected to AND gate

# TABLE 30-38:SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0)TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                                 | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                     |                          |       |                             |  |

|--------------------|-----------------------|-------------------------------------------------|-------------------------------------------------------|---------------------|--------------------------|-------|-----------------------------|--|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>                   | Min.                                                  | Typ. <sup>(2)</sup> | Max.                     | Units | Conditions                  |  |

| SP70               | FscP                  | Maximum SCK2 Input<br>Frequency                 | -                                                     | —                   | Lesser<br>of FP<br>or 11 | MHz   | (Note 3)                    |  |

| SP72               | TscF                  | SCK2 Input Fall Time                            |                                                       | _                   | —                        | ns    | See Parameter DO32 (Note 4) |  |

| SP73               | TscR                  | SCK2 Input Rise Time                            | _                                                     | _                   | —                        | ns    | See Parameter DO31 (Note 4) |  |

| SP30               | TdoF                  | SDO2 Data Output Fall Time                      | _                                                     | —                   | —                        | ns    | See Parameter DO32 (Note 4) |  |

| SP31               | TdoR                  | SDO2 Data Output Rise Time                      | —                                                     | —                   | —                        | ns    | See Parameter DO31 (Note 4) |  |

| SP35               | TscH2doV,<br>TscL2doV | SDO2 Data Output Valid after<br>SCK2 Edge       | —                                                     | 6                   | 20                       | ns    |                             |  |

| SP36               | TdoV2scH,<br>TdoV2scL | SDO2 Data Output Setup to<br>First SCK2 Edge    | 30                                                    | —                   | _                        | ns    |                             |  |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDI2 Data Input to SCK2 Edge      | 30                                                    | —                   | _                        | ns    |                             |  |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDI2 Data Input to SCK2 Edge       | 30                                                    | _                   | _                        | ns    |                             |  |

| SP50               | TssL2scH,<br>TssL2scL | $\overline{SS2}$ ↓ to SCK2 ↑ or SCK2 ↓<br>Input | 120                                                   | —                   | —                        | ns    |                             |  |

| SP51               | TssH2doZ              | SS2 ↑ to SDO2 Output<br>High-Impedance          | 10                                                    | _                   | 50                       | ns    | (Note 4)                    |  |

| SP52               | TscH2ssH<br>TscL2ssH  | SS2 ↑ after SCK2 Edge                           | 1.5 TCY + 40                                          | —                   | —                        | ns    | (Note 4)                    |  |

| SP60               | TssL2doV              | SDO2 Data Output Valid after<br>SS2 Edge        | —                                                     | _                   | 50                       | ns    |                             |  |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCK2 is 91 ns. Therefore, the SCK2 clock generated by the master must not violate this specification.

4: Assumes 50 pF load on all SPI2 pins.

| AC CHARA             | CTERISTICS                               |                                             | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |     |     |     |  |  |

|----------------------|------------------------------------------|---------------------------------------------|-------------------------------------------------------|-----|-----|-----|--|--|

| Maximum<br>Data Rate | Master<br>Transmit Only<br>(Half-Duplex) | Master<br>Transmit/Receive<br>(Full-Duplex) | Slave<br>Transmit/Receive<br>(Full-Duplex)            | CKE | СКР | SMP |  |  |

| 15 MHz               | Table 30-42                              | _                                           | _                                                     | 0,1 | 0,1 | 0,1 |  |  |

| 10 MHz               | _                                        | Table 30-43                                 | —                                                     | 1   | 0,1 | 1   |  |  |

| 10 MHz               | —                                        | Table 30-44                                 | —                                                     | 0   | 0,1 | 1   |  |  |

| 15 MHz               | —                                        | —                                           | Table 30-45                                           | 1   | 0   | 0   |  |  |

| 11 MHz               | —                                        | —                                           | Table 30-46                                           | 1   | 1   | 0   |  |  |

| 15 MHz               | _                                        | —                                           | Table 30-47                                           | 0   | 1   | 0   |  |  |

| 11 MHz               | _                                        | —                                           | Table 30-48                                           | 0   | 0   | 0   |  |  |

#### TABLE 30-41: SPI1 MAXIMUM DATA/CLOCK RATE SUMMARY

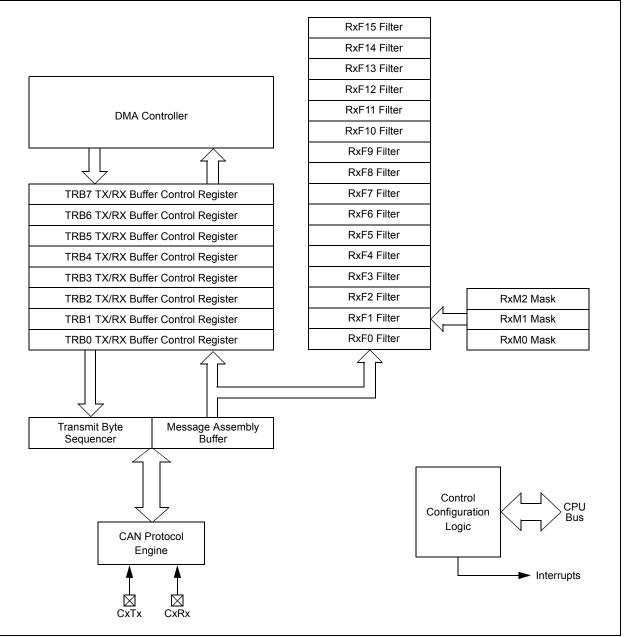

### FIGURE 30-22: SPI1 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 0) TIMING CHARACTERISTICS

| AC CHA       | RACTER            | ISTICS                        |                           | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |                    |                        |  |

|--------------|-------------------|-------------------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------|------------------------|--|

| Param<br>No. | Symbol<br>TLO:SCL | Characteristic <sup>(4)</sup> |                           | Min. <sup>(1)</sup> Ma                                                                                                                                                                                                                                                                |      | °C ≤ IA ≤<br>Units | +125°C for Extended    |  |

| IM10         |                   | Clock Low Time                | 100 kHz mode              | Tcy/2 (BRG + 2)                                                                                                                                                                                                                                                                       | _    | μS                 |                        |  |

|              |                   |                               | 400 kHz mode              | TCY/2 (BRG + 2)                                                                                                                                                                                                                                                                       |      | μ <b>S</b>         |                        |  |

|              |                   |                               | 1 MHz mode <sup>(2)</sup> | TCY/2 (BRG + 2)                                                                                                                                                                                                                                                                       |      | μs                 |                        |  |

| IM11         | THI:SCL           | Clock High Time               | 100 kHz mode              | Tcy/2 (BRG + 2)                                                                                                                                                                                                                                                                       |      | μS                 |                        |  |

|              |                   |                               | 400 kHz mode              | Tcy/2 (BRG + 2)                                                                                                                                                                                                                                                                       |      | μ <b>S</b>         |                        |  |

|              |                   |                               | 1 MHz mode <sup>(2)</sup> | TCY/2 (BRG + 2)                                                                                                                                                                                                                                                                       |      | μS                 |                        |  |

| IM20         | TF:SCL            | SDAx and SCLx                 | 100 kHz mode              |                                                                                                                                                                                                                                                                                       | 300  | ns                 | CB is specified to be  |  |

|              |                   | Fall Time                     | 400 kHz mode              | 20 + 0.1 Св                                                                                                                                                                                                                                                                           | 300  | ns                 | from 10 to 400 pF      |  |

|              |                   |                               | 1 MHz mode <sup>(2)</sup> |                                                                                                                                                                                                                                                                                       | 100  | ns                 | -                      |  |

| IM21         | TR:SCL            | SDAx and SCLx<br>Rise Time    | 100 kHz mode              |                                                                                                                                                                                                                                                                                       | 1000 | ns                 | CB is specified to be  |  |

|              |                   |                               | 400 kHz mode              | 20 + 0.1 Св                                                                                                                                                                                                                                                                           | 300  | ns                 | from 10 to 400 pF      |  |

|              |                   |                               | 1 MHz mode <sup>(2)</sup> |                                                                                                                                                                                                                                                                                       | 300  | ns                 | -                      |  |

| IM25         | TSU:DAT           | Data Input<br>Setup Time      | 100 kHz mode              | 250                                                                                                                                                                                                                                                                                   |      | ns                 |                        |  |

|              |                   |                               | 400 kHz mode              | 100                                                                                                                                                                                                                                                                                   |      | ns                 |                        |  |

|              |                   |                               | 1 MHz mode <sup>(2)</sup> | 40                                                                                                                                                                                                                                                                                    |      | ns                 | -                      |  |

| IM26         | Thd:dat           | Data Input<br>Hold Time       | 100 kHz mode              | 0                                                                                                                                                                                                                                                                                     |      | μS                 |                        |  |

|              |                   |                               | 400 kHz mode              | 0                                                                                                                                                                                                                                                                                     | 0.9  | ,<br>μS            |                        |  |

|              |                   |                               | 1 MHz mode <sup>(2)</sup> | 0.2                                                                                                                                                                                                                                                                                   |      | μs                 | -                      |  |

| IM30         | Tsu:sta           | Start Condition<br>Setup Time | 100 kHz mode              | Tcy/2 (BRG + 2)                                                                                                                                                                                                                                                                       |      | μ <b>S</b>         | Only relevant for      |  |

|              |                   |                               | 400 kHz mode              | Tcy/2 (BRG + 2)                                                                                                                                                                                                                                                                       |      | μS                 | Repeated Start         |  |

|              |                   |                               | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 2)                                                                                                                                                                                                                                                                       |      | μs                 | condition              |  |

| IM31         | THD:STA           | Start Condition<br>Hold Time  | 100 kHz mode              | Tcy/2 (BRG + 2)                                                                                                                                                                                                                                                                       |      | μ <b>s</b>         | After this period, the |  |

|              |                   |                               | 400 kHz mode              | Tcy/2 (BRG +2)                                                                                                                                                                                                                                                                        |      | μS                 | first clock pulse is   |  |

|              |                   |                               | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 2)                                                                                                                                                                                                                                                                       |      | μS                 | generated              |  |

| IM33         | Tsu:sto           | Stop Condition                | 100 kHz mode              | Tcy/2 (BRG + 2)                                                                                                                                                                                                                                                                       | _    | μS                 |                        |  |

|              |                   | Setup Time                    | 400 kHz mode              | Tcy/2 (BRG + 2)                                                                                                                                                                                                                                                                       | _    | μS                 |                        |  |

|              |                   |                               | 1 MHz mode <sup>(2)</sup> | TCY/2 (BRG + 2)                                                                                                                                                                                                                                                                       | _    | μS                 |                        |  |

| IM34         | THD:STO           | Stop Condition<br>Hold Time   | 100 kHz mode              | Tcy/2 (BRG + 2)                                                                                                                                                                                                                                                                       | _    | μS                 |                        |  |

|              |                   |                               | 400 kHz mode              | TCY/2 (BRG + 2)                                                                                                                                                                                                                                                                       | _    | μS                 |                        |  |

|              |                   |                               | 1 MHz mode <sup>(2)</sup> | TCY/2 (BRG + 2)                                                                                                                                                                                                                                                                       | _    | μS                 |                        |  |

| IM40         | TAA:SCL           | Output Valid<br>From Clock    | 100 kHz mode              | —                                                                                                                                                                                                                                                                                     | 3500 | ns                 |                        |  |

|              |                   |                               | 400 kHz mode              | —                                                                                                                                                                                                                                                                                     | 1000 | ns                 |                        |  |

|              |                   |                               | 1 MHz mode <sup>(2)</sup> | —                                                                                                                                                                                                                                                                                     | 400  | ns                 |                        |  |

| IM45         | TBF:SDA           | Bus Free Time                 | 100 kHz mode              | 4.7                                                                                                                                                                                                                                                                                   | _    | μs                 | Time the bus must be   |  |

|              |                   |                               | 400 kHz mode              | 1.3                                                                                                                                                                                                                                                                                   | _    | μ <b>s</b>         | free before a new      |  |

|              |                   |                               | 1 MHz mode <sup>(2)</sup> | 0.5                                                                                                                                                                                                                                                                                   |      | μ <b>s</b>         | transmission can star  |  |

| IM50         | Св                | Bus Capacitive L              |                           | _                                                                                                                                                                                                                                                                                     | 400  | pF                 |                        |  |

| IM51         | TPGD              | Pulse Gobbler De              | -                         | 65                                                                                                                                                                                                                                                                                    | 390  | ns                 | (Note 3)               |  |

#### TABLE 30-49: I2Cx BUS DATA TIMING REQUIREMENTS (MASTER MODE)

Note 1: BRG is the value of the l<sup>2</sup>C<sup>™</sup> Baud Rate Generator. Refer to "Inter-Integrated Circuit (l<sup>2</sup>C<sup>™</sup>)" (DS70330) in the "dsPIC33/PIC24 Family Reference Manual". Please see the Microchip web site for the latest family reference manual sections.

- 2: Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

- **3:** Typical value for this parameter is 130 ns.

- 4: These parameters are characterized, but not tested in manufacturing.

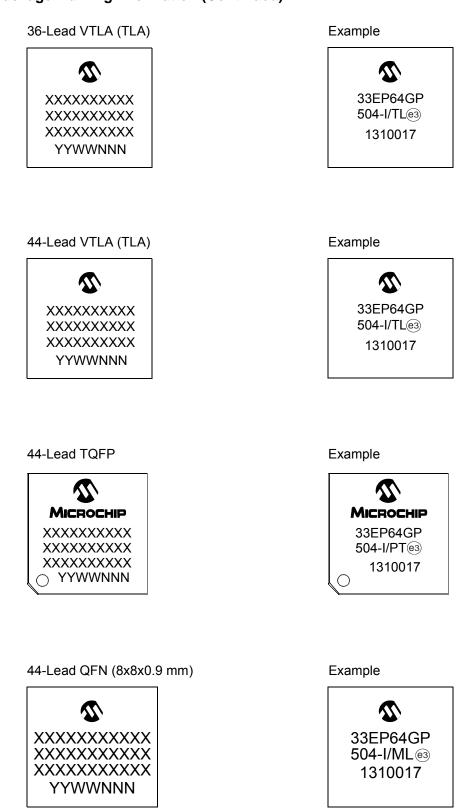

#### 33.1 Package Marking Information (Continued)

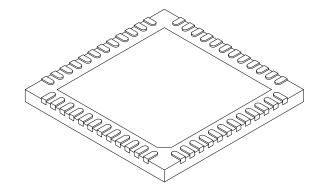

48-Lead Plastic Ultra Thin Quad Flat, No Lead Package (MV) – 6x6x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units  | N        | <b>ILLIMETER</b> | S    |  |  |

|------------------------|--------|----------|------------------|------|--|--|

| Dimension              | Limits | MIN      | NOM              | MAX  |  |  |

| Number of Pins         | N      | 48       |                  |      |  |  |

| Pitch                  | е      |          | 0.40 BSC         |      |  |  |

| Overall Height         | Α      | 0.45     | 0.50             | 0.55 |  |  |

| Standoff               | A1     | 0.00     | 0.02             | 0.05 |  |  |

| Contact Thickness      | A3     |          | 0.127 REF        |      |  |  |

| Overall Width          | E      | 6.00 BSC |                  |      |  |  |

| Exposed Pad Width      | E2     | 4.45     | 4.60             | 4.75 |  |  |

| Overall Length         | D      | 6.00 BSC |                  |      |  |  |

| Exposed Pad Length     | D2     | 4.45     | 4.60             | 4.75 |  |  |

| Contact Width          | b      | 0.15     | 0.20             | 0.25 |  |  |

| Contact Length         | L      | 0.30     | 0.40             | 0.50 |  |  |

| Contact-to-Exposed Pad | K      | 0.20     | -                | -    |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-153A Sheet 2 of 2