Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                      |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 60 MIPs                                                                       |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                 |

| Number of I/O              | 25                                                                            |

| Program Memory Size        | 32KB (10.7K x 24)                                                             |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 2K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 8x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 36-VFTLA Exposed Pad                                                          |

| Supplier Device Package    | 36-VTLA (5x5)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep32mc203-h-tl |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 1-1:         PINOUT I/O DESCRIPTIONS (CONTINUED) |             |                |       |                                                                |  |  |  |  |  |

|--------------------------------------------------------|-------------|----------------|-------|----------------------------------------------------------------|--|--|--|--|--|

| Pin Name <sup>(4)</sup>                                | Pin<br>Type | Buffer<br>Type | PPS   | Description                                                    |  |  |  |  |  |

| U2CTS                                                  | I           | ST             | No    | UART2 Clear-To-Send.                                           |  |  |  |  |  |

| U2RTS                                                  | 0           | —              | No    | UART2 Ready-To-Send.                                           |  |  |  |  |  |

| U2RX                                                   | I           | ST             | Yes   | UART2 receive.                                                 |  |  |  |  |  |

| U2TX                                                   | 0           | —              | Yes   | UART2 transmit.                                                |  |  |  |  |  |

| BCLK2                                                  | 0           | ST             | No    | UART2 IrDA <sup>®</sup> baud clock output.                     |  |  |  |  |  |

| SCK1                                                   | I/O         | ST             | No    | Synchronous serial clock input/output for SPI1.                |  |  |  |  |  |

| SDI1                                                   | I           | ST             | No    | SPI1 data in.                                                  |  |  |  |  |  |

| SDO1                                                   | 0           | —              | No    | SPI1 data out.                                                 |  |  |  |  |  |

| SS1                                                    | I/O         | ST             | No    | SPI1 slave synchronization or frame pulse I/O.                 |  |  |  |  |  |

| SCK2                                                   | I/O         | ST             | Yes   | Synchronous serial clock input/output for SPI2.                |  |  |  |  |  |

| SDI2                                                   | I           | ST             | Yes   | SPI2 data in.                                                  |  |  |  |  |  |

| SDO2                                                   | 0           | _              | Yes   | SPI2 data out.                                                 |  |  |  |  |  |

| SS2                                                    | I/O         | ST             | Yes   | SPI2 slave synchronization or frame pulse I/O.                 |  |  |  |  |  |

| SCL1                                                   | I/O         | ST             | No    | Synchronous serial clock input/output for I2C1.                |  |  |  |  |  |

| SDA1                                                   | I/O         | ST             | No    | Synchronous serial data input/output for I2C1.                 |  |  |  |  |  |

| ASCL1                                                  | I/O         | ST             | No    | Alternate synchronous serial clock input/output for I2C1.      |  |  |  |  |  |

| ASDA1                                                  | I/O         | ST             | No    | Alternate synchronous serial data input/output for I2C1.       |  |  |  |  |  |

| SCL2                                                   | I/O         | ST             | No    | Synchronous serial clock input/output for I2C2.                |  |  |  |  |  |

| SDA2                                                   | I/O         | ST             | No    | Synchronous serial data input/output for I2C2.                 |  |  |  |  |  |

| ASCL2                                                  | I/O         | ST             | No    | Alternate synchronous serial clock input/output for I2C2.      |  |  |  |  |  |

| ASDA2                                                  | I/O         | ST             | No    | Alternate synchronous serial data input/output for I2C2.       |  |  |  |  |  |

| TMS <sup>(5)</sup>                                     | Ι           | ST             | No    | JTAG Test mode select pin.                                     |  |  |  |  |  |

| TCK                                                    | I.          | ST             | No    | JTAG test clock input pin.                                     |  |  |  |  |  |

| TDI                                                    | I.          | ST             | No    | JTAG test data input pin.                                      |  |  |  |  |  |

| TDO                                                    | 0           | —              | No    | JTAG test data output pin.                                     |  |  |  |  |  |

| C1RX <sup>(2)</sup>                                    | Ι           | ST             | Yes   | ECAN1 bus receive pin.                                         |  |  |  |  |  |

| C1TX <sup>(2)</sup>                                    | 0           | —              | Yes   | ECAN1 bus transmit pin.                                        |  |  |  |  |  |

| FLT1 <sup>(1)</sup> , FLT2 <sup>(1)</sup>              | I           | ST             | Yes   | PWM Fault Inputs 1 and 2.                                      |  |  |  |  |  |

| FLT3 <sup>(1)</sup> , FLT4 <sup>(1)</sup>              | I           | ST             | No    | PWM Fault Inputs 3 and 4.                                      |  |  |  |  |  |

| FLT32 <sup>(1,3)</sup>                                 | I           | ST             | No    | PWM Fault Input 32 (Class B Fault).                            |  |  |  |  |  |

| DTCMP1-DTCMP3 <sup>(1)</sup>                           | I           | ST             | Yes   | PWM Dead-Time Compensation Inputs 1 through 3.                 |  |  |  |  |  |

| PWM1L-PWM3L <sup>(1)</sup>                             | 0           | —              | No    | PWM Low Outputs 1 through 3.                                   |  |  |  |  |  |

| PWM1H-PWM3H <sup>(1)</sup>                             | 0           | —              | No    | PWM High Outputs 1 through 3.                                  |  |  |  |  |  |

| SYNCI1 <sup>(1)</sup>                                  | I.          | ST             | Yes   | PWM Synchronization Input 1.                                   |  |  |  |  |  |

| SYNCO1 <sup>(1)</sup>                                  | 0           | —              | Yes   | PWM Synchronization Output 1.                                  |  |  |  |  |  |

| INDX1 <sup>(1)</sup>                                   | I           | ST             | Yes   | Quadrature Encoder Index1 pulse input.                         |  |  |  |  |  |

| HOME1 <sup>(1)</sup>                                   | I           | ST             | Yes   | Quadrature Encoder Home1 pulse input.                          |  |  |  |  |  |

| QEA1 <sup>(1)</sup>                                    | I           | ST             | Yes   | Quadrature Encoder Phase A input in QEI1 mode. Auxiliary timer |  |  |  |  |  |

| (4)                                                    |             |                |       | external clock/gate input in Timer mode.                       |  |  |  |  |  |

|                                                        |             |                |       | Quadrature Encoder Phase B input in QEI1 mode. Auxiliary timer |  |  |  |  |  |

|                                                        |             |                |       | external clock/gate input in Timer mode.                       |  |  |  |  |  |

| CNTCMP1 <sup>(1)</sup>                                 | 0           | —              | Yes   | Quadrature Encoder Compare Output 1.                           |  |  |  |  |  |

| Legend: CMOS = CM                                      | 109 00      | mnatible       | innut | or output Analog = Analog input P = Power                      |  |  |  |  |  |

# TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

Legend:

CMOS = CMOS compatible input or output

Analog = Analog input

ST = Schmitt Trigger input with CMOS levels

O = Output

PPS = Peripheral Pin Select

TTL = TTL input buffer

P = Power I = Input

Note 1: This pin is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This pin is available on dsPIC33EPXXXGP/MC50X devices only.

3: This is the default Fault on Reset for dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices. See Section 16.0 "High-Speed PWM Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)" for more information.

4: Not all pins are available in all packages variants. See the "Pin Diagrams" section for pin availability.

5: There is an internal pull-up resistor connected to the TMS pin when the JTAG interface is active. See the JTAGEN bit field in Table 27-2.

# 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to 3 MHz <  $F_{IN}$  < 5.5 MHz to comply with device PLL start-up conditions. This means that if the external oscillator frequency is outside this range, the application must start-up in the FRC mode first. The default PLL settings after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV and PLLFBD, to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source. Note that clock switching must be enabled in the device Configuration Word.

# 2.8 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state.

Alternatively, connect a 1k to 10k resistor between Vss and unused pins, and drive the output to logic low.

# 2.9 Application Examples

- · Induction heating

- Uninterruptable Power Supplies (UPS)

- DC/AC inverters

- · Compressor motor control

- · Washing machine 3-phase motor control

- BLDC motor control

- · Automotive HVAC, cooling fans, fuel pumps

- Stepper motor control

- · Audio and fluid sensor monitoring

- · Camera lens focus and stability control

- Speech (playback, hands-free kits, answering machines, VoIP)

- Consumer audio

- Industrial and building control (security systems and access control)

- · Barcode reading

- Networking: LAN switches, gateways

- Data storage device management

- · Smart cards and smart card readers

Examples of typical application connections are shown in Figure 2-4 through Figure 2-8.

## FIGURE 2-4: BOOST CONVERTER IMPLEMENTATION

| R/W-0               | U-0                                                                                      | R/W-0                                                    | R/W-0                   | R/W-0                       | R-0                       | R-0                | R-0                |  |  |  |  |  |  |

|---------------------|------------------------------------------------------------------------------------------|----------------------------------------------------------|-------------------------|-----------------------------|---------------------------|--------------------|--------------------|--|--|--|--|--|--|

| VAR                 | —                                                                                        | US1 <sup>(1)</sup>                                       | US0 <sup>(1)</sup>      | EDT <sup>(1,2)</sup>        | DL2 <sup>(1)</sup>        | DL1 <sup>(1)</sup> | DL0 <sup>(1)</sup> |  |  |  |  |  |  |

| bit 15              |                                                                                          |                                                          |                         |                             |                           |                    | bit                |  |  |  |  |  |  |

| R/W-0               | R/W-0                                                                                    | R/W-1                                                    | R/W-0                   | R/C-0                       | R-0                       | R/W-0              | R/W-0              |  |  |  |  |  |  |

| SATA <sup>(1)</sup> | SATB <sup>(1)</sup>                                                                      | SATDW <sup>(1)</sup>                                     | ACCSAT <sup>(1)</sup>   | IPL3(3)                     | SFA                       | RND <sup>(1)</sup> | IF(1)              |  |  |  |  |  |  |

| bit 7               |                                                                                          |                                                          |                         |                             | I                         | 1                  | bit                |  |  |  |  |  |  |

| Legend:             |                                                                                          | C = Clearable                                            | e bit                   |                             |                           |                    |                    |  |  |  |  |  |  |

| R = Readabl         | e bit                                                                                    | W = Writable                                             | bit                     | U = Unimpler                | mented bit, read          | d as '0'           |                    |  |  |  |  |  |  |

| -n = Value at       | POR                                                                                      | '1' = Bit is set                                         | t                       | '0' = Bit is cle            | ared                      | x = Bit is unkr    | nown               |  |  |  |  |  |  |

| bit 15              | 1 = Variable                                                                             | le Exception Pro<br>exception proce                      | essing latency          | is enabled                  |                           |                    |                    |  |  |  |  |  |  |

| bit 14              |                                                                                          | nted: Read as                                            |                         |                             |                           |                    |                    |  |  |  |  |  |  |

| bit 13-12           | -                                                                                        | SP Multiply Uns                                          |                         | Control bits <sup>(1)</sup> |                           |                    |                    |  |  |  |  |  |  |

|                     | 01 = DSP er<br>00 = DSP er                                                               | ngine multiplies<br>ngine multiplies<br>ngine multiplies | are unsigned are signed |                             |                           |                    |                    |  |  |  |  |  |  |

| bit 11              | •                                                                                        | O Loop Terminatives executing Dot<br>t                   |                         |                             | iteration                 |                    |                    |  |  |  |  |  |  |

| bit 10-8            | DL<2:0>: DO Loop Nesting Level Status bits <sup>(1)</sup><br>111 = 7 DO loops are active |                                                          |                         |                             |                           |                    |                    |  |  |  |  |  |  |

|                     | •                                                                                        |                                                          |                         |                             |                           |                    |                    |  |  |  |  |  |  |

|                     | •                                                                                        |                                                          |                         |                             |                           |                    |                    |  |  |  |  |  |  |

|                     | 001 = 1 DO k<br>000 = 0 DO k                                                             | oop is active<br>oops are active                         |                         |                             |                           |                    |                    |  |  |  |  |  |  |

| bit 7               | SATA: ACCA                                                                               | A Saturation En                                          | able bit <sup>(1)</sup> |                             |                           |                    |                    |  |  |  |  |  |  |

|                     |                                                                                          | ator A saturatio<br>ator A saturatio                     |                         |                             |                           |                    |                    |  |  |  |  |  |  |

| bit 6               | SATB: ACCE                                                                               | B Saturation En                                          | able bit <sup>(1)</sup> |                             |                           |                    |                    |  |  |  |  |  |  |

|                     |                                                                                          | ator B saturatio<br>ator B saturatio                     |                         |                             |                           |                    |                    |  |  |  |  |  |  |

| bit 5               | SATDW: Dat                                                                               | ta Space Write                                           | from DSP Engi           | ne Saturation               | Enable bit <sup>(1)</sup> |                    |                    |  |  |  |  |  |  |

|                     |                                                                                          | ace write satura<br>ace write satura                     |                         | I                           |                           |                    |                    |  |  |  |  |  |  |

| bit 4               |                                                                                          | cumulator Satu                                           |                         | elect bit <sup>(1)</sup>    |                           |                    |                    |  |  |  |  |  |  |

|                     |                                                                                          | uration (super s<br>uration (normal                      | ,                       |                             |                           |                    |                    |  |  |  |  |  |  |

| bit 3               |                                                                                          | nterrupt Priority                                        |                         |                             |                           |                    |                    |  |  |  |  |  |  |

|                     |                                                                                          | errupt Priority Le<br>errupt Priority Le                 |                         |                             |                           |                    |                    |  |  |  |  |  |  |

|                     | his bit is availabl<br>his bit is always                                                 |                                                          | PXXXMC20X/              | 50X and dsPlo               | C33EPXXXGP                | 50X devices on     | ly.                |  |  |  |  |  |  |

| <b>4.</b> []        | no bit io aiwayo                                                                         | 1000 03 0.                                               |                         |                             |                           |                    |                    |  |  |  |  |  |  |

# REGISTER 3-2: CORCON: CORE CONTROL REGISTER

**3:** The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

# 4.2 Data Address Space

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X CPU has a separate 16-bit-wide data memory space. The Data Space is accessed using separate Address Generation Units (AGUs) for read and write operations. The data memory maps, which are presented by device family and memory size, are shown in Figure 4-7 through Figure 4-16.

All Effective Addresses (EAs) in the data memory space are 16 bits wide and point to bytes within the Data Space. This arrangement gives a base Data Space address range of 64 Kbytes (32K words).

The base Data Space address is used in conjunction with a Read or Write Page register (DSRPAG or DSWPAG) to form an Extended Data Space, which has a total address range of 16 Mbytes.

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices implement up to 52 Kbytes of data memory (4 Kbytes of data memory for Special Function Registers and up to 48 Kbytes of data memory for RAM). If an EA points to a location outside of this area, an all-zero word or byte is returned.

# 4.2.1 DATA SPACE WIDTH

The data memory space is organized in byteaddressable, 16-bit-wide blocks. Data is aligned in data memory and registers as 16-bit words, but all Data Space EAs resolve to bytes. The Least Significant Bytes (LSBs) of each word have even addresses, while the Most Significant Bytes (MSBs) have odd addresses.

## 4.2.2 DATA MEMORY ORGANIZATION AND ALIGNMENT

To maintain backward compatibility with PIC<sup>®</sup> MCU devices and improve Data Space memory usage efficiency, the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X instruction set supports both word and byte operations. As a consequence of byte accessibility, all Effective Address calculations are internally scaled to step through word-aligned memory. For example, the core recognizes that Post-Modified Register Indirect Addressing mode [Ws++] results in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

A data byte read, reads the complete word that contains the byte, using the LSb of any EA to determine which byte to select. The selected byte is placed onto the LSB of the data path. That is, data memory and registers are organized as two parallel, byte-wide entities with shared (word) address decode but separate write lines. Data byte writes only write to the corresponding side of the array or register that matches the byte address. All word accesses must be aligned to an even address. Misaligned word data fetches are not supported, so care must be taken when mixing byte and word operations, or translating from 8-bit MCU code. If a misaligned read or write is attempted, an address error trap is generated. If the error occurred on a read, the instruction underway is completed. If the error occurred on a write, the instruction is executed but the write does not occur. In either case, a trap is then executed, allowing the system and/or user application to examine the machine state prior to execution of the address Fault.

All byte loads into any W register are loaded into the LSB. The MSB is not modified.

A Sign-Extend (SE) instruction is provided to allow user applications to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, user applications can clear the MSB of any W register by executing a Zero-Extend (ZE) instruction on the appropriate address.

# 4.2.3 SFR SPACE

The first 4 Kbytes of the Near Data Space, from 0x0000 to 0x0FFF, is primarily occupied by Special Function Registers (SFRs). These are used by the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X core and peripheral modules for controlling the operation of the device.

SFRs are distributed among the modules that they control and are generally grouped together by module. Much of the SFR space contains unused addresses; these are read as '0'.

**Note:** The actual set of peripheral features and interrupts varies by the device. Refer to the corresponding device tables and pinout diagrams for device-specific information.

# 4.2.4 NEAR DATA SPACE

The 8-Kbyte area, between 0x0000 and 0x1FFF, is referred to as the Near Data Space. Locations in this space are directly addressable through a 13-bit absolute address field within all memory direct instructions. Additionally, the whole Data Space is addressable using MOV instructions, which support Memory Direct Addressing mode with a 16-bit address field, or by using Indirect Addressing mode using a working register as an Address Pointer.

## TABLE 4-39: PMD REGISTER MAP FOR dsPIC33EPXXXGP50X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   |        |       |       | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | —      | C1MD   | AD1MD | 0000          |

| PMD2         | 0762  |        | _      | _      | -      | IC4MD  | IC3MD  | IC2MD | IC1MD | _      | _     | _     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  | _      | _      | _      | _      | _      | CMPMD  |       |       | CRCMD  | _     | —     | —      |        | —      | I2C2MD |       | 0000          |

| PMD4         | 0766  | _      | _      | _      | _      | _      | _      |       |       | _      | _     | —     | —      | REFOMD | CTMUMD |        |       | 0000          |

| PMD6         | 076A  | _      |        | _      | _      | _      |        |       |       | _      |       | —     | —      |        | —      |        |       | 0000          |

|              |       |        |        |        |        |        |        |       |       |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  |        |        |        |        |        |        |       |       |        |       |       | DMA1MD | PTGMD  |        |        |       | 0000          |

| FIND7        | 0700  | _      | _      | _      | _      | _      | _      | _     | _     | _      | —     | _     | DMA2MD | FIGND  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |       |       |        |       |       | DMA3MD |        |        |        |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-40: PMD REGISTER MAP FOR dsPIC33EPXXXMC50X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | QEI1MD | PWMMD  | _      | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | —      | C1MD   | AD1MD | 0000          |

| PMD2         | 0762  | _      | —      | —      | —      | IC4MD  | IC3MD  | IC2MD  | IC1MD  | _      | _     | —     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  | _      | _      | _      | _      | _      | CMPMD  | _      | _      | CRCMD  | _     | _     | _      | _      | _      | I2C2MD | _     | 0000          |

| PMD4         | 0766  | _      | _      | _      | _      | _      | _      | _      | _      | _      | _     | _     | _      | REFOMD | CTMUMD | _      | _     | 0000          |

| PMD6         | 076A  | —      | —      |        | _      | —      | PWM3MD | PWM2MD | PWM1MD | —      | _     |       | _      | —      | —      | —      | -     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  |        |        |        |        |        |        |        |        |        |       |       | DMA1MD | PTGMD  |        |        |       | 0000          |

| FIVID7       | 0700  | _      | _      | _      | _      | _      | _      | _      | _      | —      | —     | _     | DMA2MD | FIGND  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA3MD |        |        |        |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

DS70000657H-page 95

| U-0             | U-0                                                                                          | U-0                                                                                                                                                                     | U-0                                                                             | R-0               | R-0              | R-0             | R-0     |  |  |  |  |  |  |

|-----------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-------------------|------------------|-----------------|---------|--|--|--|--|--|--|

|                 | —                                                                                            |                                                                                                                                                                         |                                                                                 | ILR3              | ILR2             | ILR1            | ILR0    |  |  |  |  |  |  |

| bit 15          |                                                                                              |                                                                                                                                                                         |                                                                                 |                   |                  |                 | bit 8   |  |  |  |  |  |  |

| R-0             | R-0                                                                                          | R-0                                                                                                                                                                     | R-0                                                                             | R-0               | R-0              | R-0             | R-0     |  |  |  |  |  |  |

| VECNUM7         | VECNUM6                                                                                      | VECNUM5                                                                                                                                                                 | VECNUM4                                                                         | VECNUM3           | VECNUM2          | VECNUM1         | VECNUM0 |  |  |  |  |  |  |

| bit 7           |                                                                                              |                                                                                                                                                                         |                                                                                 |                   |                  |                 | bit C   |  |  |  |  |  |  |

| Legend:         |                                                                                              |                                                                                                                                                                         |                                                                                 |                   |                  |                 |         |  |  |  |  |  |  |

| R = Readable    | bit                                                                                          | W = Writable                                                                                                                                                            | bit                                                                             | U = Unimplen      | nented bit, read | as '0'          |         |  |  |  |  |  |  |

| -n = Value at I | POR                                                                                          | '1' = Bit is set                                                                                                                                                        |                                                                                 | '0' = Bit is clea | ared             | x = Bit is unkr | nown    |  |  |  |  |  |  |

| bit 15-12       | Unimplemen                                                                                   | ted: Read as '                                                                                                                                                          | 0'                                                                              |                   |                  |                 |         |  |  |  |  |  |  |

| bit 11-8        | ILR<3:0>: New CPU Interrupt Priority Level bits                                              |                                                                                                                                                                         |                                                                                 |                   |                  |                 |         |  |  |  |  |  |  |

|                 | 1111 = CPU Interrupt Priority Level is 15                                                    |                                                                                                                                                                         |                                                                                 |                   |                  |                 |         |  |  |  |  |  |  |

|                 | •                                                                                            |                                                                                                                                                                         |                                                                                 |                   |                  |                 |         |  |  |  |  |  |  |

|                 | •                                                                                            |                                                                                                                                                                         |                                                                                 |                   |                  |                 |         |  |  |  |  |  |  |

|                 | 0001 = CPU Interrupt Priority Level is 1<br>0000 = CPU Interrupt Priority Level is 0         |                                                                                                                                                                         |                                                                                 |                   |                  |                 |         |  |  |  |  |  |  |

| bit 7-0         | VECNUM<7:0>: Vector Number of Pending Interrupt bits                                         |                                                                                                                                                                         |                                                                                 |                   |                  |                 |         |  |  |  |  |  |  |

|                 | 11111111 = 255, Reserved; do not use                                                         |                                                                                                                                                                         |                                                                                 |                   |                  |                 |         |  |  |  |  |  |  |

|                 | •                                                                                            |                                                                                                                                                                         |                                                                                 |                   |                  |                 |         |  |  |  |  |  |  |

|                 | •                                                                                            |                                                                                                                                                                         |                                                                                 |                   |                  |                 |         |  |  |  |  |  |  |

|                 | 00001000 = 8<br>00000111 = 7<br>00000110 = 8<br>00000101 = 8<br>00000100 = 7<br>00000011 = 3 | 9, IC1 – Input (<br>8, INT0 – Exter<br>7, Reserved; d<br>6, Generic soft<br>5, DMAC error<br>4, Math error tr<br>3, Stack error t<br>2, Generic hard<br>1, Address erro | rnal Interrupt C<br>o not use<br>error trap<br>trap<br>rap<br>d trap<br>or trap | )                 |                  |                 |         |  |  |  |  |  |  |

# REGISTER 7-7: INTTREG: INTERRUPT CONTROL AND STATUS REGISTER

NOTES:

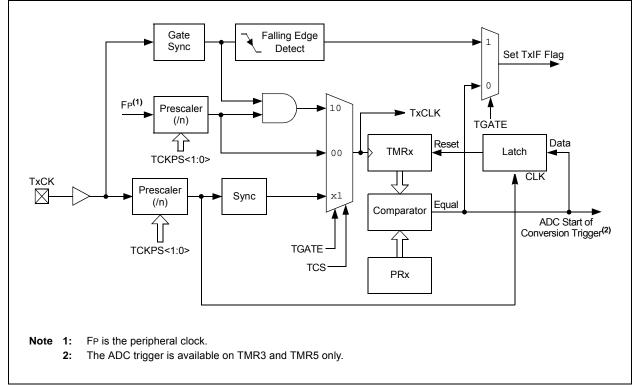

## FIGURE 13-2: TYPE C TIMER BLOCK DIAGRAM (x = 3 AND 5)

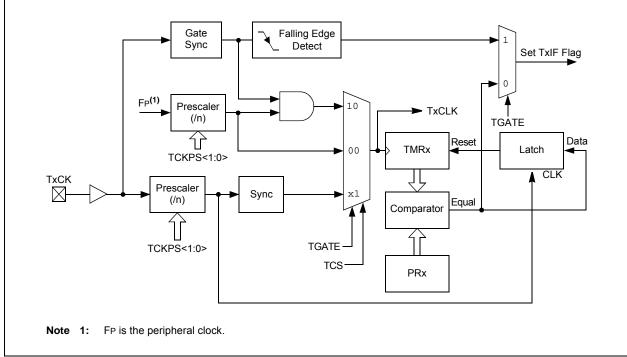

# FIGURE 13-1:TYPE B TIMER BLOCK DIAGRAM (x = 2 AND 4)

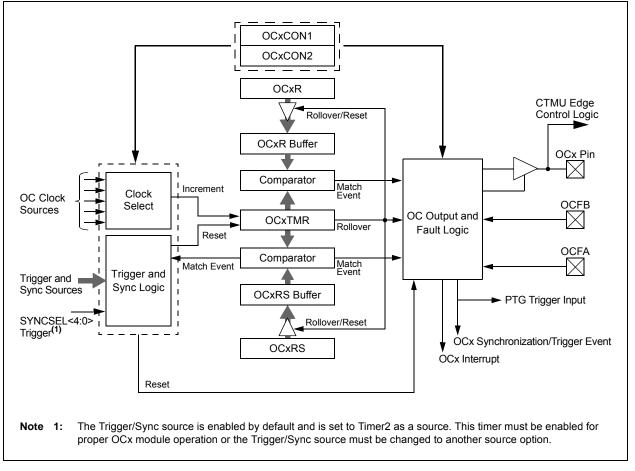

# 15.0 OUTPUT COMPARE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Output Compare" (DS70358) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The output compare module can select one of seven available clock sources for its time base. The module compares the value of the timer with the value of one or two compare registers depending on the operating mode selected. The state of the output pin changes when the timer value matches the compare register value. The output compare module generates either a single output pulse or a sequence of output pulses, by changing the state of the output pin on the compare match events. The output compare module can also generate interrupts on compare match events and trigger DMA data transfers.

Note: See "Output Compare" (DS70358) in the "dsPIC33/PIC24 Family Reference Manual" for OCxR and OCxRS register restrictions.

## REGISTER 16-1: PTCON: PWMx TIME BASE CONTROL REGISTER (CONTINUED)

| bit 6-4 | SYNCSRC<2:0>: Synchronous Source Selection bits <sup>(1)</sup><br>111 = Reserved<br>100 = Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3-0 | 100 = Reserved<br>011 = PTGO17 <sup>(2)</sup><br>010 = PTGO16 <sup>(2)</sup><br>001 = Reserved<br>000 = SYNCI1 input from PPS<br>SEVTPS<3:0>: PWMx Special Event Trigger Output Postscaler Select bits <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|         | <ul> <li>1111 = 1:16 Postscaler generates Special Event Trigger on every sixteenth compare match event</li> <li>.</li> <l< td=""></l<></ul> |

|         | 0000 = 1:1 Postscaler generates Special Event Trigger on every second compare match event                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

- **Note 1:** These bits should be changed only when PTEN = 0. In addition, when using the SYNCI1 feature, the user application must program the period register with a value that is slightly larger than the expected period of the external synchronization input signal.

- 2: See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for information on this selection.

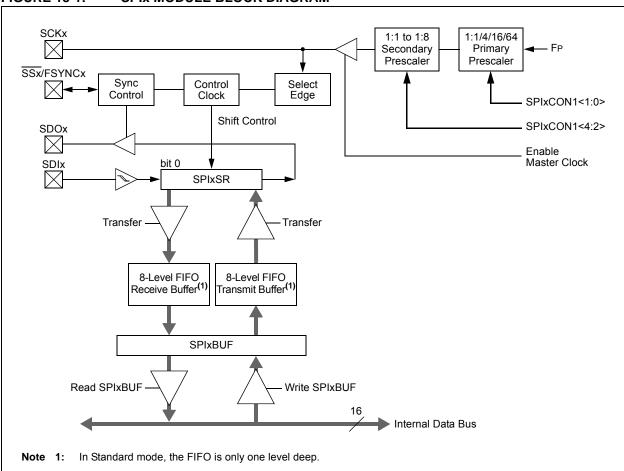

#### FIGURE 18-1: SPIX MODULE BLOCK DIAGRAM

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

# 24.0 PERIPHERAL TRIGGER GENERATOR (PTG) MODULE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Peripheral Trigger Generator (PTG)" (DS70669) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

# 24.1 Module Introduction

The Peripheral Trigger Generator (PTG) provides a means to schedule complex high-speed peripheral operations that would be difficult to achieve using software. The PTG module uses 8-bit commands, called "Steps", that the user writes to the PTG Queue registers (PTGQUE0-PTGQUE7), which perform operations, such as wait for input signal, generate output trigger and wait for timer.

The PTG module has the following major features:

- Multiple clock sources

- Two 16-bit general purpose timers

- Two 16-bit general limit counters

- Configurable for rising or falling edge triggering

- Generates processor interrupts to include:

- Four configurable processor interrupts

- Interrupt on a Step event in Single-Step modeInterrupt on a PTG Watchdog Timer time-out

- Able to receive trigger signals from these peripherals:

- ADC

- PWM

- Output Compare

- Input Capture

- Op Amp/Comparator

- INT2

- Able to trigger or synchronize to these peripherals:

- Watchdog Timer

- Output Compare

- Input Capture

- ADC

- PWM

- Op Amp/Comparator

#### REGISTER 25-3: CM4CON: COMPARATOR 4 CONTROL REGISTER (CONTINUED)

- bit 5 Unimplemented: Read as '0'

- bit 4 **CREF:** Comparator Reference Select bit (VIN+ input)<sup>(1)</sup>

- 1 = VIN+ input connects to internal CVREFIN voltage

- 0 = VIN+ input connects to C4IN1+ pin

- bit 3-2 Unimplemented: Read as '0'

- bit 1-0 CCH<1:0>: Comparator Channel Select bits<sup>(1)</sup>

- 11 = VIN- input of comparator connects to OA3/AN6

- 10 = VIN- input of comparator connects to OA2/AN0

- 01 = VIN- input of comparator connects to OA1/AN3

- 00 = VIN- input of comparator connects to C4IN1-

- Note 1: Inputs that are selected and not available will be tied to Vss. See the "Pin Diagrams" section for available inputs for each package.

# 29.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

- Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- · Simulators

- MPLAB X SIM Software Simulator

- · Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

## 29.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac  $OS^{®}$  X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

Feature-Rich Editor:

- Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- · Call graph window

- Project-Based Workspaces:

- · Multiple projects

- Multiple tools

- · Multiple configurations

- · Simultaneous debugging sessions

File History and Bug Tracking:

- · Local file history feature

- Built-in support for Bugzilla issue tracker

# 29.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

# 29.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

## 29.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

# 29.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

# 29.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

# 29.11 Demonstration/Development Boards, Evaluation Kits and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

# 29.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

# 33.0 PACKAGING INFORMATION

# 33.1 Package Marking Information

## 28-Lead SPDIP

#### 28-Lead SOIC (.300")

28-Lead SSOP

Example dsPIC33EP64GP 502-I/SP@3 1310017

# Example

## Example

28-Lead QFN-S (6x6x0.9 mm)

Example

| Legend | : XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>* | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator ((e3))<br>can be found on the outer packaging for this package. |

|--------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | be carried                               | nt the full Microchip part number cannot be marked on one line, it will<br>d over to the next line, thus limiting the number of available<br>of or customer-specific information.                                                                                                                                                                                              |

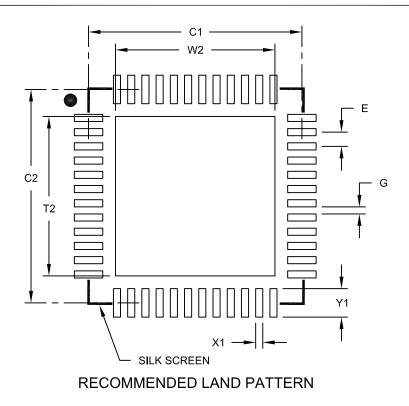

48-Lead Ultra Thin Plastic Quad Flat, No Lead Package (MV) - 6x6 mm Body [UQFN] With 0.40 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | MILLIMETERS     |      |      |      |  |  |

|----------------------------|-----------------|------|------|------|--|--|

| Dimensior                  | n Limits        | MIN  | NOM  | MAX  |  |  |

| Contact Pitch              | Contact Pitch E |      |      |      |  |  |

| Optional Center Pad Width  | W2              |      |      | 4.45 |  |  |

| Optional Center Pad Length | T2              |      |      | 4.45 |  |  |

| Contact Pad Spacing        | C1              |      | 6.00 |      |  |  |

| Contact Pad Spacing        | C2              |      | 6.00 |      |  |  |

| Contact Pad Width (X28)    | X1              |      |      | 0.20 |  |  |

| Contact Pad Length (X28)   | Y1              |      |      | 0.80 |  |  |

| Distance Between Pads      | G               | 0.20 |      |      |  |  |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2153A

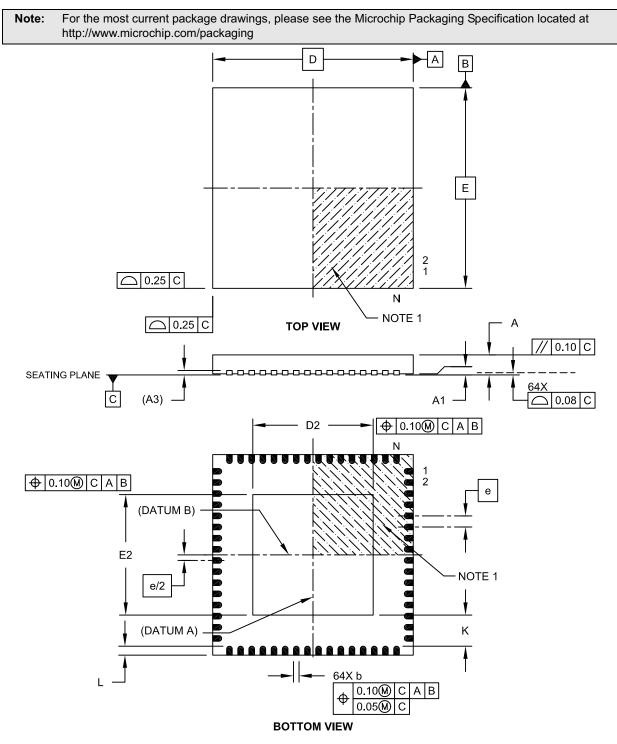

# 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body with 5.40 x 5.40 Exposed Pad [QFN]

Microchip Technology Drawing C04-154A Sheet 1 of 2