Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 60 MIPs                                                                        |

| Connectivity               | I²C, IrDA, LINbus, QEI, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                  |

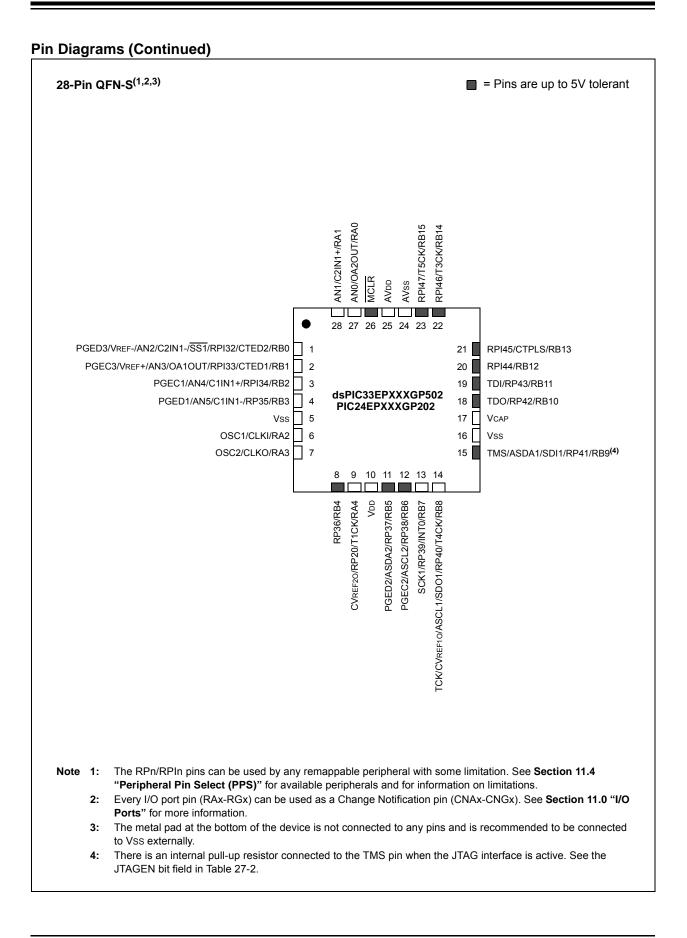

| Number of I/O              | 25                                                                             |

| Program Memory Size        | 32KB (10.7K x 24)                                                              |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 2K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 8x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

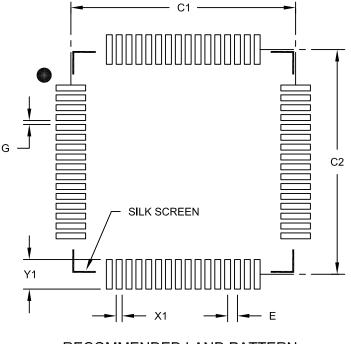

| Package / Case             | 36-VFTLA Exposed Pad                                                           |

| Supplier Device Package    | 36-VTLA (5x5)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep32mc203t-e-tl |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Referenced Sources**

This device data sheet is based on the following individual chapters of the *"dsPIC33/PIC24 Family Reference Manual"*. These documents should be considered as the general reference for the operation of a particular module or device feature.

Note 1: To access the documents listed below, browse to the documentation section of the dsPIC33EP64MC506 product page of the Microchip web site (www.microchip.com) or select a family reference manual section from the following list.

> In addition to parameters, features and other documentation, the resulting page provides links to the related family reference manual sections.

- "Introduction" (DS70573)

- "CPU" (DS70359)

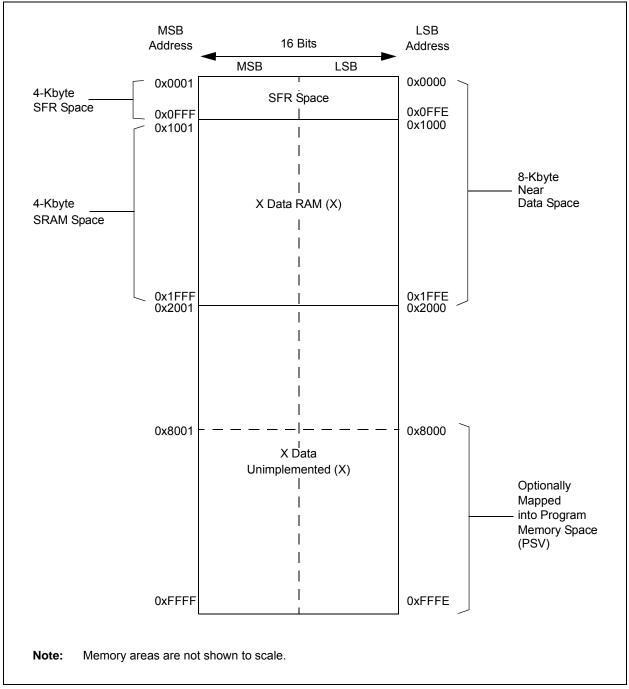

- "Data Memory" (DS70595)

- "Program Memory" (DS70613)

- "Flash Programming" (DS70609)

- "Interrupts" (DS70600)

- "Oscillator" (DS70580)

- "Reset" (DS70602)

- "Watchdog Timer and Power-Saving Modes" (DS70615)

- "I/O Ports" (DS70598)

- "Timers" (DS70362)

- "Input Capture" (DS70352)

- "Output Compare" (DS70358)

- "High-Speed PWM" (DS70645)

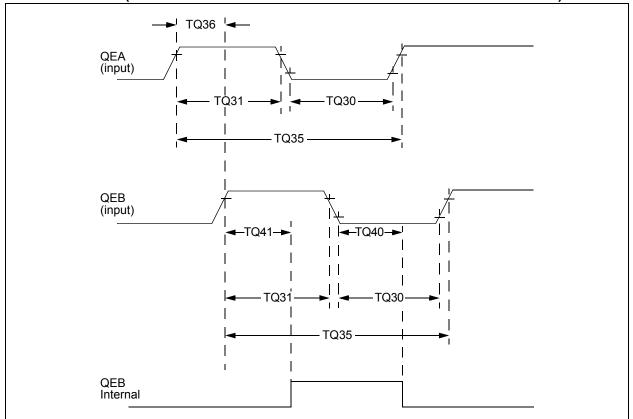

- "Quadrature Encoder Interface (QEI)" (DS70601)

- "Analog-to-Digital Converter (ADC)" (DS70621)

- "UART" (DS70582)

- "Serial Peripheral Interface (SPI)" (DS70569)

- "Inter-Integrated Circuit (I<sup>2</sup>C<sup>™</sup>)" (DS70330)

- "Enhanced Controller Area Network (ECAN™)" (DS70353)

- "Direct Memory Access (DMA)" (DS70348)

- "CodeGuard™ Security" (DS70634)

- "Programming and Diagnostics" (DS70608)

- "Op Amp/Comparator" (DS70357)

- "Programmable Cyclic Redundancy Check (CRC)" (DS70346)

- "Device Configuration" (DS70618)

- "Peripheral Trigger Generator (PTG)" (DS70669)

- "Charge Time Measurement Unit (CTMU)" (DS70661)

#### **TABLE 4-3**: INTERRUPT CONTROLLER REGISTER MAP FOR PIC24EPXXXGP20X DEVICES ONLY

| TADLL        | τу.   |        |        |            | VELEN  |        |        |            |        |       |              | DEVICE      |         |             |          |              |         |               |

|--------------|-------|--------|--------|------------|--------|--------|--------|------------|--------|-------|--------------|-------------|---------|-------------|----------|--------------|---------|---------------|

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8  | Bit 7 | Bit 6        | Bit 5       | Bit 4   | Bit 3       | Bit 2    | Bit 1        | Bit 0   | All<br>Resets |

| IFS0         | 0800  |        | DMA1IF | AD1IF      | U1TXIF | U1RXIF | SPI1IF | SPI1EIF    | T3IF   | T2IF  | OC2IF        | IC2IF       | DMA0IF  | T1IF        | OC1IF    | IC1IF        | INTOIF  | 0000          |

| IFS1         | 0802  | U2TXIF | U2RXIF | INT2IF     | T5IF   | T4IF   | OC4IF  | OC3IF      | DMA2IF | _     | _            | —           | INT1IF  | CNIF        | CMIF     | MI2C1IF      | SI2C1IF | 0000          |

| IFS2         | 0804  |        | _      | _          | -      |        | _      | —          | _      | _     | IC4IF        | IC3IF       | DMA3IF  | _           | —        | SPI2IF       | SPI2EIF | 0000          |

| IFS3         | 0806  | _      | _      | _          | _      | _      | _      | _          | _      | _     | _            | _           | _       | _           | MI2C2IF  | SI2C2IF      | _       | 0000          |

| IFS4         | 0808  | _      | _      | CTMUIF     | _      | _      | _      | _          | _      | _     | _            | _           | _       | CRCIF       | U2EIF    | U1EIF        | _       | 0000          |

| IFS8         | 0810  | JTAGIF | ICDIF  |            | _      | _      | _      | —          | —      | _     | _            | _           | _       | _           | —        | —            | —       | 0000          |

| IFS9         | 0812  | _      | _      | _          | _      | _      | _      | —          | —      | _     | PTG3IF       | PTG2IF      | PTG1IF  | PTG0IF      | PTGWDTIF | PTGSTEPIF    | _       | 0000          |

| IEC0         | 0820  | _      | DMA1IE | AD1IE      | U1TXIE | U1RXIE | SPI1IE | SPI1EIE    | T3IE   | T2IE  | OC2IE        | IC2IE       | DMA0IE  | T1IE        | OC1IE    | IC1IE        | INT0IE  | 0000          |

| IEC1         | 0822  | U2TXIE | U2RXIE | INT2IE     | T5IE   | T4IE   | OC4IE  | OC3IE      | DMA2IE | _     | _            | _           | INT1IE  | CNIE        | CMIE     | MI2C1IE      | SI2C1IE | 0000          |

| IEC2         | 0824  | _      | _      | _          | _      | _      | _      | _          | _      | _     | IC4IE        | IC3IE       | DMA3IE  | _           | _        | SPI2IE       | SPI2EIE | 0000          |

| IEC3         | 0826  | _      | _      | _          | _      | _      | _      | —          | —      | _     | _            | _           | _       | _           | MI2C2IE  | SI2C2IE      | —       | 0000          |

| IEC4         | 0828  | _      | _      | CTMUIE     | _      | _      | _      | _          | _      | _     | _            | _           | _       | CRCIE       | U2EIE    | U1EIE        | _       | 0000          |

| IEC8         | 0830  | JTAGIE | ICDIE  | _          | _      | _      | _      | _          | _      | _     | _            | _           | _       | _           | _        | _            | _       | 0000          |

| IEC9         | 0832  | _      | _      | _          | _      | _      | _      | —          | —      | _     | PTG3IE       | PTG2IE      | PTG1IE  | PTG0IE      | PTGWDTIE | PTGSTEPIE    | _       | 0000          |

| IPC0         | 0840  | _      |        | T1IP<2:0>  |        | _      | (      | OC1IP<2:0  | >      | _     | — IC1IP<2:0> |             | —       | INT0IP<2:0> |          | 4444         |         |               |

| IPC1         | 0842  | _      |        | T2IP<2:0>  |        | _      | (      | OC2IP<2:0  | >      | _     |              | IC2IP<2:0>  |         | _           | C        | 0MA0IP<2:0>  |         | 4444          |

| IPC2         | 0844  | _      | U      | J1RXIP<2:0 | >      | _      | ;      | SPI1IP<2:0 | >      | _     |              | SPI1EIP<2:0 | >       | _           |          | T3IP<2:0>    |         | 4444          |

| IPC3         | 0846  | _      | _      | _          | _      | _      | D      | )MA1IP<2:  | 0>     | _     |              | AD1IP<2:0>  |         | _           | ι        | J1TXIP<2:0>  |         | 0444          |

| IPC4         | 0848  |        |        | CNIP<2:0>  |        |        |        | CMIP<2:0   | >      | _     |              | MI2C1IP<2:0 | >       | _           | S        | SI2C1IP<2:0> |         | 4444          |

| IPC5         | 084A  | _      | _      | _          | _      | _      | _      | _          | _      | _     | _            | _           | _       | _           | I        | INT1IP<2:0>  |         | 0004          |

| IPC6         | 084C  | _      |        | T4IP<2:0>  |        | _      | (      | OC4IP<2:0  | >      | _     |              | OC3IP<2:0>  |         | _           | C        | )ma2IP<2:0>  |         | 4444          |

| IPC7         | 084E  |        | I      | U2TXIP<2:0 | >      |        | L      | J2RXIP<2:  | )>     | _     |              | INT2IP<2:0> |         | _           |          | T5IP<2:0>    |         | 4444          |

| IPC8         | 0850  |        | _      | _          | _      |        | _      | —          | —      | _     |              | SPI2IP<2:0> |         | _           | S        | SPI2EIP<2:0> |         | 0044          |

| IPC9         | 0852  |        | _      | _          | _      |        |        | IC4IP<2:0  | >      | _     |              | IC3IP<2:0>  |         | _           | C        | 0MA3IP<2:0>  |         | 0444          |

| IPC12        | 0858  |        | _      | _          | _      |        | N      | 112C2IP<2: | 0>     | _     |              | SI2C2IP<2:0 | >       | _           | _        | _            | _       | 0440          |

| IPC16        | 0860  |        |        | CRCIP<2:0> | >      |        |        | U2EIP<2:0  | >      | _     |              | U1EIP<2:0>  |         | _           | _        | _            | _       | 4440          |

| IPC19        | 0866  |        | _      | _          | _      | _      | _      | _          | _      | _     |              | CTMUIP<2:0  | >       | _           | _        | _            | _       | 0040          |

| IPC35        | 0886  |        |        | JTAGIP<2:0 | >      | _      |        | ICDIP<2:0  | >      | _     | _            | _           | _       | _           | _        | _            | _       | 4400          |

| IPC36        | 0888  | _      |        | PTG0IP<2:0 | >      | _      | PT     | GWDTIP<    | 2:0>   | _     | P            | TGSTEPIP<2  | :0>     | _           | _        | —            | _       | 4440          |

| IPC37        | 088A  | _      | _      | _          | _      | _      | F      | PTG3IP<2:  | )>     | _     |              | PTG2IP<2:0  | >       | _           | F        | PTG1IP<2:0>  |         | 0444          |

| INTCON1      | 08C0  | NSTDIS | OVAERR | OVBERR     | _      |        |        |            | —      | _     | DIV0ERR      | DMACERR     | MATHERR | ADDRERR     | STKERR   | OSCFAIL      |         | 0000          |

| INTCON2      | 08C2  | GIE    | DISI   | SWTRAP     | _      |        |        |            | _      | _     |              | —           | —       | _           | INT2EP   | INT1EP       | INT0EP  | 8000          |

| INTCON3      | 08C4  | _      | _      |            | _      |        |        | _          | _      | _     | _            | DAE         | DOOVR   | _           | _        | —            |         | 0000          |

| INTCON4      | 08C6  |        | _      | _          | _      | _      | _      | —          | _      | _     | _            | _           | _       | _           | _        |              | SGHT    | 0000          |

| INTTREG      | 08C8  | _      |        |            | _      |        | ILR<   | 3:0>       |        |       |              |             | VECN    | UM<7:0>     |          |              |         | 0000          |

|              |       |        |        |            |        |        |        |            |        |       |              |             |         |             |          |              |         |               |

- = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

#### 4.5 Instruction Addressing Modes

The addressing modes shown in Table 4-63 form the basis of the addressing modes optimized to support the specific features of individual instructions. The addressing modes provided in the MAC class of instructions differ from those in the other instruction types.

#### 4.5.1 FILE REGISTER INSTRUCTIONS

Most file register instructions use a 13-bit address field (f) to directly address data present in the first 8192 bytes of data memory (Near Data Space). Most file register instructions employ a working register, W0, which is denoted as WREG in these instructions. The destination is typically either the same file register or WREG (with the exception of the MUL instruction), which writes the result to a register or register pair. The MOV instruction allows additional flexibility and can access the entire Data Space.

#### 4.5.2 MCU INSTRUCTIONS

The three-operand MCU instructions are of the form:

Operand 3 = Operand 1 <function> Operand 2

where Operand 1 is always a working register (that is, the addressing mode can only be Register Direct), which is referred to as Wb. Operand 2 can be a W register fetched from data memory or a 5-bit literal. The result location can either be a W register or a data memory location. The following addressing modes are supported by MCU instructions:

- Register Direct

- · Register Indirect

- · Register Indirect Post-Modified

- Register Indirect Pre-Modified

- 5-Bit or 10-Bit Literal

- Note: Not all instructions support all the addressing modes given above. Individual instructions can support different subsets of these addressing modes.

#### TABLE 4-63: FUNDAMENTAL ADDRESSING MODES SUPPORTED

| Addressing Mode                                           | Description                                                                                           |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| File Register Direct                                      | The address of the file register is specified explicitly.                                             |

| Register Direct                                           | The contents of a register are accessed directly.                                                     |

| Register Indirect                                         | The contents of Wn form the Effective Address (EA).                                                   |

| Register Indirect Post-Modified                           | The contents of Wn form the EA. Wn is post-modified (incremented or decremented) by a constant value. |

| Register Indirect Pre-Modified                            | Wn is pre-modified (incremented or decremented) by a signed constant value to form the EA.            |

| Register Indirect with Register Offset (Register Indexed) | The sum of Wn and Wb forms the EA.                                                                    |

| Register Indirect with Literal Offset                     | The sum of Wn and a literal forms the EA.                                                             |

|                 | 12. 2007.00    |                                       |              |                                         |                  |          |        |

|-----------------|----------------|---------------------------------------|--------------|-----------------------------------------|------------------|----------|--------|

| U-0             | U-0            | U-0                                   | U-0          | U-0                                     | U-0              | U-0      | U-0    |

| —               | —              | —                                     | —            | —                                       | —                | —        | —      |

| bit 15          |                |                                       |              |                                         |                  |          | bit 8  |

|                 |                |                                       |              |                                         |                  |          |        |

| U-0             | U-0            | U-0                                   | U-0          | R-0                                     | R-0              | R-0      | R-0    |

| —               |                | —                                     | —            | RQCOL3                                  | RQCOL2           | RQCOL1   | RQCOL0 |

| bit 7           |                |                                       |              |                                         |                  |          | bit 0  |

|                 |                |                                       |              |                                         |                  |          |        |

| Legend:         |                |                                       |              |                                         |                  |          |        |

| R = Readable    | bit            | W = Writable                          | bit          | U = Unimpler                            | mented bit, read | l as '0' |        |

| -n = Value at F | POR            | '1' = Bit is set                      |              | '0' = Bit is cleared x = Bit is unknown |                  |          |        |

|                 |                |                                       |              |                                         |                  |          |        |

| bit 15-4        | Unimplemen     | ted: Read as '                        | כ'           |                                         |                  |          |        |

| bit 3           | RQCOL3: DN     | /IA Channel 3 T                       | ransfer Requ | est Collision F                         | ag bit           |          |        |

|                 |                | e and interrupt<br>est collision is d |              | st collision is d                       | etected          |          |        |

| <b>h</b> # 0    | •              |                                       |              | est Callisian Fl                        | aa hit           |          |        |

| bit 2           |                | /IA Channel 2 T<br>ce and interrupt   | •            |                                         | 0                |          |        |

|                 |                | e and interrupt<br>est collision is d |              |                                         | elecieu          |          |        |

| bit 1           | RQCOL1: DN     | /IA Channel 1 T                       | ransfer Requ | est Collision F                         | ag bit           |          |        |

|                 | 1 = User for   | e and interrupt                       | -based reque | st collision is d                       | etected          |          |        |

|                 | 0 = No reque   | est collision is d                    | etected      |                                         |                  |          |        |

| bit 0           | RQCOLO: DN     | /IA Channel 0 T                       | ransfer Requ | est Collision F                         | lag bit          |          |        |

|                 | 1 = User force | e and interrupt                       | -based reque | st collision is d                       | etected          |          |        |

#### REGISTER 8-12: DMARQC: DMA REQUEST COLLISION STATUS REGISTER

0 = No request collision is detected

| U-0                               | U-0                         | U-0                                          | U-0            | U-0              | U-0              | U-0             | U-0   |

|-----------------------------------|-----------------------------|----------------------------------------------|----------------|------------------|------------------|-----------------|-------|

| -                                 | —                           | —                                            | —              | —                | —                | —               | —     |

| bit 15                            |                             |                                              |                |                  |                  |                 | bit 8 |

| U-0                               | U-0                         | U-0                                          | U-0            | R-1              | R-1              | R-1             | R-1   |

| _                                 | _                           | _                                            | _              |                  | LSTC             | H<3:0>          |       |

| bit 7                             | bit 7                       |                                              |                |                  |                  |                 | bit 0 |

| Legend:                           |                             |                                              |                |                  |                  |                 |       |

| R = Readable bit W = Writable bit |                             |                                              |                | U = Unimpler     | mented bit, read | 1 as '0'        |       |

| -n = Value a                      | at POR                      | '1' = Bit is set                             |                | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

|                                   |                             |                                              |                |                  |                  |                 |       |

| bit 15-4                          | Unimplemen                  | ted: Read as '                               | 0'             |                  |                  |                 |       |

| bit 3-0                           | LSTCH<3:0>                  | : Last DMAC C                                | hannel Active  | e Status bits    |                  |                 |       |

|                                   | 1111 = No DI<br>1110 = Rese | MA transfer has<br>rved                      | s occurred sir | nce system Res   | set              |                 |       |

|                                   | •                           |                                              |                |                  |                  |                 |       |

|                                   | •                           |                                              |                |                  |                  |                 |       |

|                                   | •                           |                                              |                |                  |                  |                 |       |

|                                   |                             | rved<br>data transfer wa<br>data transfer wa |                |                  |                  |                 |       |

|                                   |                             | data transfer wa                             |                |                  |                  |                 |       |

#### REGISTER 8-13: DMALCA: DMA LAST CHANNEL ACTIVE STATUS REGISTER

0001 = Last data transfer was handled by Channel 0 0000 = Last data transfer was handled by Channel 0

|                                    | REGISTER 10-3: PMD3: PERIPHERAL MODULE DISABLE CONTROL REGISTER 3 |                |                                        |                                    |       |        |       |  |  |  |  |  |

|------------------------------------|-------------------------------------------------------------------|----------------|----------------------------------------|------------------------------------|-------|--------|-------|--|--|--|--|--|

| U-0                                | U-0                                                               | U-0            | U-0                                    | U-0                                | R/W-0 | U-0    | U-0   |  |  |  |  |  |

| —                                  | _                                                                 | —              | —                                      | —                                  | CMPMD | —      | —     |  |  |  |  |  |

| bit 15                             |                                                                   |                |                                        |                                    |       |        | bit 8 |  |  |  |  |  |

|                                    |                                                                   |                |                                        |                                    |       |        |       |  |  |  |  |  |

| R/W-0                              | U-0                                                               | U-0            | U-0                                    | U-0                                | U-0   | R/W-0  | U-0   |  |  |  |  |  |

| CRCMD                              | —                                                                 | —              | _                                      | —                                  | —     | I2C2MD | —     |  |  |  |  |  |

| bit 7                              |                                                                   |                |                                        |                                    |       |        | bit C |  |  |  |  |  |

|                                    |                                                                   |                |                                        |                                    |       |        |       |  |  |  |  |  |

| Legend:                            |                                                                   |                |                                        |                                    |       |        |       |  |  |  |  |  |

| R = Readable                       | bit                                                               | W = Writable I | bit                                    | U = Unimplemented bit, read as '0' |       |        |       |  |  |  |  |  |

| -n = Value at POR '1' = Bit is set |                                                                   |                | '0' = Bit is cleared x = Bit is unknow |                                    |       | own    |       |  |  |  |  |  |

#### REGISTER 10-3: PMD3: PERIPHERAL MODULE DISABLE CONTROL REGISTER 3

| bit 10  | CMPMD: Comparator Module Disable bit |

|---------|--------------------------------------|

|         | 1 = Comparator module is disabled    |

|         | 0 = Comparator module is enabled     |

| bit 9-8 | Unimplemented: Read as '0'           |

| bit 7   | CRCMD: CRC Module Disable bit        |

|         | 1 = CRC module is disabled           |

|         | 0 = CRC module is enabled            |

| bit 6-2 | Unimplemented: Read as '0'           |

| bit 1   | I2C2MD: I2C2 Module Disable bit      |

|         | 1 = I2C2 module is disabled          |

|         | 0 = I2C2 module is enabled           |

| bit 0   | Unimplemented: Read as '0'           |

|         |                                      |

#### REGISTER 10-4: PMD4: PERIPHERAL MODULE DISABLE CONTROL REGISTER 4

|        | -   |     |     |        |        |     |       |

|--------|-----|-----|-----|--------|--------|-----|-------|

| U-0    | U-0 | U-0 | U-0 | U-0    | U-0    | U-0 | U-0   |

| —      | —   |     |     | —      | —      | —   | —     |

| bit 15 |     |     |     |        |        |     | bit 8 |

|        |     |     |     |        |        |     |       |

| U-0    | U-0 | U-0 | U-0 | R/W-0  | R/W-0  | U-0 | U-0   |

| —      | —   | —   | —   | REFOMD | CTMUMD | —   | —     |

| bit 7  |     |     |     |        |        |     | bit 0 |

|        |     |     |     |        |        |     |       |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-4 | Unimplemented: Read as '0'                                 |

|----------|------------------------------------------------------------|

| bit 3    | <b>REFOMD:</b> Reference Clock Module Disable bit          |

|          | <ol> <li>1 = Reference clock module is disabled</li> </ol> |

|          | 0 = Reference clock module is enabled                      |

| bit 2    | CTMUMD: CTMU Module Disable bit                            |

|          | 1 = CTMU module is disabled                                |

|          | 0 = CTMU module is enabled                                 |

| bit 1-0  | Unimplemented: Read as '0'                                 |

$\ensuremath{\textcircled{}^\circ}$  2011-2013 Microchip Technology Inc.

| R/W-0                        | R/W-0                                                                                                                                                                  | R/W-0                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W-0                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                              |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          | IC2R<6:0>                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| ·                            |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 8                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| R/W-0                        | R/W-0                                                                                                                                                                  | R/W-0                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W-0                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|                              |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          | IC1R<6:0>                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|                              |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit C                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|                              |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| e bit                        | W = Writable b                                                                                                                                                         | it                                                                                                                                                                                                                                                                                                                                       | U = Unimplem                                                                                                                                                                                             | nented bit, rea                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | d as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| POR                          | '1' = Bit is set                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                          | '0' = Bit is clea                                                                                                                                                                                        | ared                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | x = Bit is unkr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | x = Bit is unknown                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| •                            |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          | nbers)                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|                              |                                                                                                                                                                        | 1                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| Unimplemer                   | nted: Read as '0                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| (see Table 11<br>1111001 = I | I-2 for input pin's nput tied to RPI1                                                                                                                                  | election num<br>21                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                          | onding RPn Pi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | n bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|                              | e bit<br>POR<br>Unimplemen<br>IC2R<6:0>: /<br>(see Table 11<br>1111001 = I<br>0000001 = I<br>0000000 = I<br>Unimplemen<br>IC1R<6:0>: /<br>(see Table 11<br>1111001 = I | e bit W = Writable b<br>POR '1' = Bit is set<br>Unimplemented: Read as '0<br>IC2R<6:0>: Assign Input Cap<br>(see Table 11-2 for input pin s<br>1111001 = Input tied to RPI1<br>0000001 = Input tied to CMP<br>0000000 = Input tied to Vss<br>Unimplemented: Read as '0<br>IC1R<6:0>: Assign Input Cap<br>(see Table 11-2 for input pin s | e bit W = Writable bit<br>POR '1' = Bit is set<br>Unimplemented: Read as '0'<br>IC2R<6:0>: Assign Input Capture 2 (IC2)<br>(see Table 11-2 for input pin selection num<br>1111001 = Input tied to RPI121 | R/W-0       R/W-0       R/W-0       R/W-0         IC1R<6:0>       IC1R<6:0>         e bit       W = Writable bit       U = Unimplem         POR       '1' = Bit is set       '0' = Bit is clear         Unimplemented:       Read as '0'         IC2R<6:0>:       Assign Input Capture 2 (IC2) to the Correspond (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121         .         .         0000001 = Input tied to CMP1         0000000 = Input tied to Vss         Unimplemented:         Read as '0'         IC1R<6:0>:         Assign Input Capture 1 (IC1) to the Correspond (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         . | R/W-0       R/W-0       R/W-0       R/W-0         IC1R<6:0>         e bit       W = Writable bit       U = Unimplemented bit, real         POR       '1' = Bit is set       '0' = Bit is cleared         Unimplemented:       Read as '0'         IC2R<6:0>:       Assign Input Capture 2 (IC2) to the Corresponding RPn Pi (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121       .         .       .         0000001 = Input tied to CMP1         0000000 = Input tied to Vss         Unimplemented:         Read as '0'         IC1R<6:0>:         Assign Input Capture 1 (IC1) to the Corresponding RPn Pi (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         . | R/W-0       R/W-0       R/W-0       R/W-0       R/W-0         IC1R<6:0>    e bit W = Writable bit U = Unimplemented bit, read as '0' POR '1' = Bit is set '0' = Bit is cleared x = Bit is unkr Unimplemented: Read as '0' IC2R<6:0>: Assign Input Capture 2 (IC2) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) 1111001 = Input tied to RPI121 <p< td=""></p<> |  |  |

#### REGISTER 11-4: RPINR7: PERIPHERAL PIN SELECT INPUT REGISTER 7

|        |     |       |       | DD20  |         |       |       |

|--------|-----|-------|-------|-------|---------|-------|-------|

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 |

| bit 15 |     |       |       |       |         |       | bit 8 |

|        |     |       |       | RP35  | iR<5:0> |       |       |

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 |

#### REGISTER 11-18: RPOR0: PERIPHERAL PIN SELECT OUTPUT REGISTER 0

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|--------|-------|-------|

| —     | —   |       |       | RP20  | R<5:0> |       |       |

| bit 7 |     |       |       |       |        |       | bit 0 |

|       |     |       |       |       |        |       |       |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP35R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP35 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP20R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP20 Output Pin bits (see Table 11-3 for peripheral function numbers) |

#### REGISTER 11-19: RPOR1: PERIPHERAL PIN SELECT OUTPUT REGISTER 1

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|---------|-------|-------|

| —      | —   |       |       | RP37  | ′R<5:0> |       |       |

| bit 15 |     |       |       |       |         |       | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|--------|-------|-------|

| —     | —   |       |       | RP36  | R<5:0> |       |       |

| bit 7 |     |       |       |       |        |       | bit 0 |