Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 60 MIPs                                                                       |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                 |

| Number of I/O              | 35                                                                            |

| Program Memory Size        | 32KB (10.7K x 24)                                                             |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 2K x 16                                                                       |

| /oltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 9x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 44-VQFN Exposed Pad                                                           |

| Supplier Device Package    | 44-QFN (8x8)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep32mc204-e-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

| Pin Name <sup>(4)</sup> | Pin<br>Type | Buffer<br>Type | PPS | Description                                                                   |

|-------------------------|-------------|----------------|-----|-------------------------------------------------------------------------------|

| C1IN1-                  | I           | Analog         | No  | Op Amp/Comparator 1 Negative Input 1.                                         |

| C1IN2-                  | ı           | Analog         | No  | Comparator 1 Negative Input 2.                                                |

| C1IN1+                  | I           | Analog         | No  | Op Amp/Comparator 1 Positive Input 1.                                         |

| OA1OUT                  | 0           | Analog         | No  | Op Amp 1 output.                                                              |

| C1OUT                   | 0           |                | Yes | Comparator 1 output.                                                          |

| C2IN1-                  | ı           | Analog         | No  | Op Amp/Comparator 2 Negative Input 1.                                         |

| C2IN2-                  | I           | Analog         | No  | Comparator 2 Negative Input 2.                                                |

| C2IN1+                  | I           | Analog         | No  | Op Amp/Comparator 2 Positive Input 1.                                         |

| OA2OUT                  | О           | Analog         | No  | Op Amp 2 output.                                                              |

| C2OUT                   | 0           | _              | Yes | Comparator 2 output.                                                          |

| C3IN1-                  | I           | Analog         | No  | Op Amp/Comparator 3 Negative Input 1.                                         |

| C3IN2-                  | I           | Analog         | No  | Comparator 3 Negative Input 2.                                                |

| C3IN1+                  | I           | Analog         | No  | Op Amp/Comparator 3 Positive Input 1.                                         |

| OA3OUT                  | О           | Analog         | No  | Op Amp 3 output.                                                              |

| C3OUT                   | 0           | _              | Yes | Comparator 3 output.                                                          |

| C4IN1-                  | I           | Analog         | No  | Comparator 4 Negative Input 1.                                                |

| C4IN1+                  | I           | Analog         | No  | Comparator 4 Positive Input 1.                                                |

| C4OUT                   | 0           | _              | Yes | Comparator 4 output.                                                          |

| CVREF10                 | 0           | Analog         | No  | Op amp/comparator voltage reference output.                                   |

| CVREF20                 | 0           | Analog         | No  | Op amp/comparator voltage reference divided by 2 output.                      |

| PGED1                   | I/O         | ST             | No  | Data I/O pin for Programming/Debugging Communication Channel 1.               |

| PGEC1                   | ı           | ST             | No  | Clock input pin for Programming/Debugging Communication Channel 1.            |

| PGED2                   | I/O         | ST             | No  | Data I/O pin for Programming/Debugging Communication Channel 2.               |

| PGEC2                   | ı           | ST             | No  | Clock input pin for Programming/Debugging Communication Channel 2.            |

| PGED3                   | I/O         | ST             | No  | Data I/O pin for Programming/Debugging Communication Channel 3.               |

| PGEC3                   | l           | ST             | No  | Clock input pin for Programming/Debugging Communication Channel 3.            |

| MCLR                    | I/P         | ST             | No  | Master Clear (Reset) input. This pin is an active-low Reset to the device.    |

| AVDD                    | Р           | Р              | No  | Positive supply for analog modules. This pin must be connected at all times.  |

| AVss                    | Р           | Р              | No  | Ground reference for analog modules. This pin must be connected at all times. |

| VDD                     | Р           | _              | No  | Positive supply for peripheral logic and I/O pins.                            |

| VCAP                    | Р           | _              | No  | CPU logic filter capacitor connection.                                        |

| Vss                     | Р           | _              | No  | Ground reference for logic and I/O pins.                                      |

| VREF+                   | I           | Analog         | No  | Analog voltage reference (high) input.                                        |

| VREF-                   | I           | Analog         | No  | Analog voltage reference (low) input.                                         |

Legend:CMOS = CMOS compatible input or outputAnalog = Analog inputP = PowerST = Schmitt Trigger input with CMOS levelsO = OutputI = InputPPS = Peripheral Pin SelectTTL = TTL input buffer

Note 1: This pin is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

- 2: This pin is available on dsPIC33EPXXXGP/MC50X devices only.

- 3: This is the default Fault on Reset for dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices. See Section 16.0 "High-Speed PWM Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)" for more information.

- 4: Not all pins are available in all packages variants. See the "Pin Diagrams" section for pin availability.

- 5: There is an internal pull-up resistor connected to the TMS pin when the JTAG interface is active. See the JTAGEN bit field in Table 27-2.

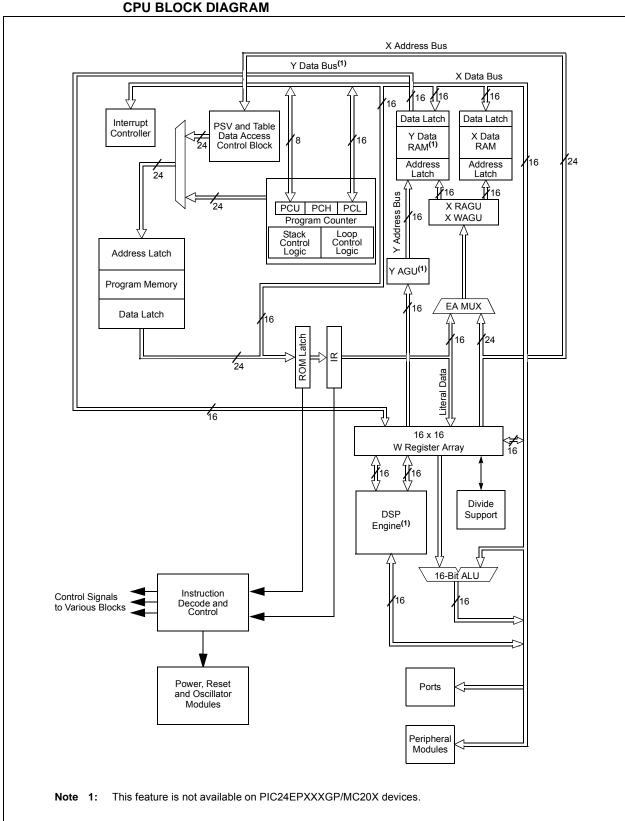

FIGURE 3-1: dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X CPU BLOCK DIAGRAM

### 4.2.5 X AND Y DATA SPACES

The dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X core has two Data Spaces, X and Y. These Data Spaces can be considered either separate (for some DSP instructions) or as one unified linear address range (for MCU instructions). The Data Spaces are accessed using two Address Generation Units (AGUs) and separate data paths. This feature allows certain instructions to concurrently fetch two words from RAM, thereby enabling efficient execution of DSP algorithms, such as Finite Impulse Response (FIR) filtering and Fast Fourier Transform (FFT).

The X Data Space is used by all instructions and supports all addressing modes. X Data Space has separate read and write data buses. The X read data bus is the read data path for all instructions that view Data Space as combined X and Y address space. It is also the X data prefetch path for the dual operand DSP instructions (MAC class).

The Y Data Space is used in concert with the X Data Space by the MAC class of instructions (CLR, ED, EDAC, MAC, MOVSAC, MPY, MPY. N and MSC) to provide two concurrent data read paths.

Both the X and Y Data Spaces support Modulo Addressing mode for all instructions, subject to addressing mode restrictions. Bit-Reversed Addressing mode is only supported for writes to X Data Space. Modulo Addressing and Bit-Reversed Addressing are not present in PIC24EPXXXGP/MC20X devices.

All data memory writes, including in DSP instructions, view Data Space as combined X and Y address space. The boundary between the X and Y Data Spaces is device-dependent and is not user-programmable.

### 4.3 Memory Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser: http://www.microchip.com/wwwproducts/Devices.aspx?dDocName=en555464

### 4.3.1 KEY RESOURCES

- "Program Memory" (DS70613) in the "dsPIC33/ PIC24 Family Reference Manual"

- · Code Samples

- · Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- · Development Tools

### 5.0 FLASH PROGRAM MEMORY

Note 1: This data sheet summarizes features of the dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Flash Programming" (DS70609) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

> 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices contain internal Flash program memory for storing and executing application code. The memory is readable, writable and erasable during normal operation over the entire VDD range.

Flash memory can be programmed in two ways:

- In-Circuit Serial Programming™ (ICSP™) programming capability

- Run-Time Self-Programming (RTSP)

allows for a dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X device to be serially programmed while in the end application circuit. This is done with two lines for programming clock and programming data (one of the

alternate programming pin pairs: PGECx/PGEDx), and three other lines for power (VDD), ground (VSS) and Master Clear (MCLR). This allows customers to manufacture boards with unprogrammed devices and then program the device just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

RTSP is accomplished using TBLRD (Table Read) and TBLWT (Table Write) instructions. With RTSP, the user application can write program memory data a single program memory word, and erase program memory in blocks or 'pages' of 1024 instructions (3072 bytes) at a

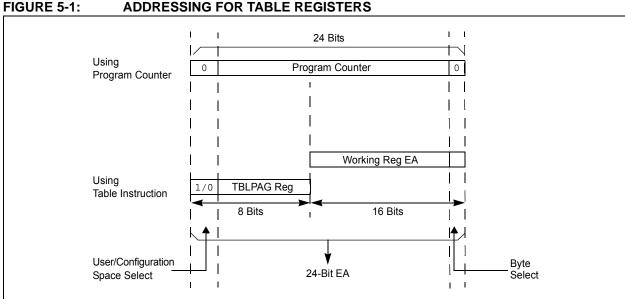

### 5.1 **Table Instructions and Flash Programming**

Regardless of the method used, all programming of Flash memory is done with the Table Read and Table Write instructions. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using bits<7:0> of the TBLPAG register and the Effective Address (EA) from a W register, specified in the table instruction, as shown in Figure 5-1.

The TBLRDL and the TBLWTL instructions are used to read or write to bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes.

The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

### REGISTER 7-7: INTTREG: INTERRUPT CONTROL AND STATUS REGISTER

| U-0    | U-0 | U-0 | U-0 | R-0  | R-0  | R-0  | R-0   |

|--------|-----|-----|-----|------|------|------|-------|

| _      |     | _   | _   | ILR3 | ILR2 | ILR1 | ILR0  |

| bit 15 |     |     |     |      |      |      | bit 8 |

| R-0     |

|---------|---------|---------|---------|---------|---------|---------|---------|

| VECNUM7 | VECNUM6 | VECNUM5 | VECNUM4 | VECNUM3 | VECNUM2 | VECNUM1 | VECNUM0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-12 **Unimplemented:** Read as '0'

bit 11-8 ILR<3:0>: New CPU Interrupt Priority Level bits

1111 = CPU Interrupt Priority Level is 15

•

.

0001 = CPU Interrupt Priority Level is 1 0000 = CPU Interrupt Priority Level is 0

bit 7-0 **VECNUM<7:0>:** Vector Number of Pending Interrupt bits

11111111 = 255, Reserved; do not use

•

•

00001001 = 9, IC1 - Input Capture 1

00001000 = 8, INT0 – External Interrupt 0

00000111 = 7, Reserved; do not use

00000110 = 6, Generic soft error trap

00000101 = 5, DMAC error trap

00000100 = 4, Math error trap

00000011 = 3, Stack error trap

00000010 = 2, Generic hard trap

00000001 = 1, Address error trap

00000000 = 0, Oscillator fail trap

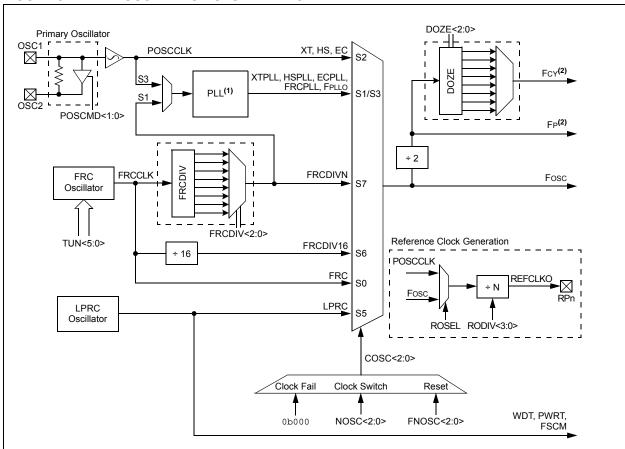

### 9.0 OSCILLATOR CONFIGURATION

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Oscillator" (DS70580) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X oscillator system provides:

- On-chip Phase-Locked Loop (PLL) to boost internal operating frequency on select internal and external oscillator sources

- On-the-fly clock switching between various clock sources

- · Doze mode for system power savings

- Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown

- · Configuration bits for clock source selection

A simplified diagram of the oscillator system is shown in Figure 9-1.

### FIGURE 9-1: OSCILLATOR SYSTEM DIAGRAM

- Note 1: See Figure 9-2 for PLL details.

- 2: The term, FP, refers to the clock source for all peripherals, while FCY refers to the clock source for the CPU. Throughout this document, FCY and FP are used interchangeably, except in the case of Doze mode. FP and FCY will be different when Doze mode is used with a doze ratio of 1:2 or lower.

### REGISTER 9-4: OSCTUN: FRC OSCILLATOR TUNING REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| _     | _   | TUN5  | TUN4  | TUN3  | TUN2  | TUN1  | TUN0  |

| bit 7 |     |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-6 **Unimplemented:** Read as '0'

bit 5-0 **TUN<5:0>:** FRC Oscillator Tuning bits

011111 = Maximum frequency deviation of 1.453% (7.477 MHz)

011110 = Center frequency + 1.406% (7.474 MHz)

• • •

000001 = Center frequency + 0.047% (7.373 MHz)

000000 = Center frequency (7.37 MHz nominal)

111111 = Center frequency – 0.047% (7.367 MHz)

• • •

100001 = Center frequency – 1.453% (7.263 MHz)

100000 = Minimum frequency deviation of -1.5% (7.259 MHz)

### 10.0 POWER-SAVING FEATURES

# Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Watchdog Timer and Power-Saving Modes" (DS70615) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices provide the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of peripherals being clocked constitutes lower consumed power.

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices can manage power consumption in four ways:

- Clock Frequency

- · Instruction-Based Sleep and Idle modes

- · Software-Controlled Doze mode

- · Selective Peripheral Control in Software

Combinations of these methods can be used to selectively tailor an application's power consumption while still maintaining critical application features, such as timing-sensitive communications.

# 10.1 Clock Frequency and Clock Switching

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices allow a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or high-precision oscillators by simply changing the NOSCx bits (OSCCON<10:8>). The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in **Section 9.0 "Oscillator Configuration"**.

# 10.2 Instruction-Based Power-Saving

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices have two special power-saving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution. Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. The assembler syntax of the PWRSAV instruction is shown in Example 10-1.

Note: SLEEP\_MODE and IDLE\_MODE are constants defined in the assembler include file for the selected device.

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to "wake-up".

### **EXAMPLE 10-1:** PWRSAV INSTRUCTION SYNTAX

PWRSAV #SLEEP\_MODE ; Put the device into Sleep mode PWRSAV #IDLE\_MODE ; Put the device into Idle mode

### REGISTER 11-6: RPINR11: PERIPHERAL PIN SELECT INPUT REGISTER 11

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|------------|-------|-------|-------|

| _     |       |       |       | OCFAR<6:0> | >     |       |       |

| bit 7 |       |       |       |            |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-7 **Unimplemented:** Read as '0'

bit 6-0 OCFAR<6:0>: Assign Output Compare Fault A (OCFA) to the Corresponding RPn Pin bits

(see Table 11-2 for input pin selection numbers)

1111001 = Input tied to RPI121

:

0000001 = Input tied to CMP1

0000000 = Input tied to Vss

### REGISTER 21-19: CxFMSKSEL2: ECANx FILTER 15-8 MASK SELECTION REGISTER 2

| R/W-0  | R/W-0  | R/W-0 | R/W-0  | R/W-0 | R/W-0   | R/W-0 | R/W-0   |

|--------|--------|-------|--------|-------|---------|-------|---------|

| F15MSI | K<1:0> | F14MS | K<1:0> | F13MS | SK<1:0> | F12MS | SK<1:0> |

| bit 15 |        |       |        | •     |         | •     | bit 8   |

| R/W-0 | R/W-0  | R/W-0 | R/W-0  | R/W-0 | R/W-0  | R/W-0 | R/W-0  |

|-------|--------|-------|--------|-------|--------|-------|--------|

| F11MS | K<1:0> | F10MS | K<1:0> | F9MS  | K<1:0> | F8MSI | K<1:0> |

| bit 7 |        |       |        |       |        |       | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | F15MSK<1:0>: Mask Source for Filter 15 bits  11 = Reserved  10 = Acceptance Mask 2 registers contain mask  01 = Acceptance Mask 1 registers contain mask  00 = Acceptance Mask 0 registers contain mask |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-12 | F14MSK<1:0>: Mask Source for Filter 14 bits (same values as bits<15:14>)                                                                                                                                |

| bit 11-10 | F13MSK<1:0>: Mask Source for Filter 13 bits (same values as bits<15:14>)                                                                                                                                |

| bit 9-8   | F12MSK<1:0>: Mask Source for Filter 12 bits (same values as bits<15:14>)                                                                                                                                |

| bit 7-6   | F11MSK<1:0>: Mask Source for Filter 11 bits (same values as bits<15:14>)                                                                                                                                |

| bit 5-4   | F10MSK<1:0>: Mask Source for Filter 10 bits (same values as bits<15:14>)                                                                                                                                |

| bit 3-2   | F9MSK<1:0>: Mask Source for Filter 9 bits (same values as bits<15:14>)                                                                                                                                  |

| bit 1-0   | F8MSK<1:0>: Mask Source for Filter 8 bits (same values as bits<15:14>)                                                                                                                                  |

### 23.2 ADC Helpful Tips

- 1. The SMPIx control bits in the AD1CON2 register:

- Determine when the ADC interrupt flag is set and an interrupt is generated, if enabled.

- b) When the CSCNA bit in the AD1CON2 registers is set to '1', this determines when the ADC analog scan channel list, defined in the AD1CSSL/AD1CSSH registers, starts over from the beginning.

- c) When the DMA peripheral is not used (ADDMAEN = 0), this determines when the ADC Result Buffer Pointer to ADC1BUF0-ADC1BUFF gets reset back to the beginning at ADC1BUF0.

- d) When the DMA peripheral is used (ADDMAEN = 1), this determines when the DMA Address Pointer is incremented after a sample/conversion operation. ADC1BUF0 is the only ADC buffer used in this mode. The ADC Result Buffer Pointer to ADC1BUF0-ADC1BUFF gets reset back to the beginning at ADC1BUF0. The DMA address is incremented after completion of every 32nd sample/conversion operation. Conversion results are stored in the ADC1BUF0 register for transfer to RAM using DMA.

- 2. When the DMA module is disabled (ADDMAEN = 0), the ADC has 16 result buffers. ADC conversion results are stored sequentially in ADC1BUF0-ADC1BUFF, regardless of which analog inputs are being used subject to the SMPIx bits and the condition described in 1c) above. There is no relationship between the ANx input being measured and which ADC buffer (ADC1BUF0-ADC1BUFF) that the conversion results will be placed in.

- 3. When the DMA module is enabled (ADDMAEN = 1), the ADC module has only 1 ADC result buffer (i.e., ADC1BUF0) per ADC peripheral and the ADC conversion result must be read, either by the CPU or DMA Controller, before the next ADC conversion is complete to avoid overwriting the previous value.

- 4. The DONE bit (AD1CON1<0>) is only cleared at the start of each conversion and is set at the completion of the conversion, but remains set indefinitely, even through the next sample phase until the next conversion begins. If application code is monitoring the DONE bit in any kind of software loop, the user must consider this behavior because the CPU code execution is faster than the ADC. As a result, in Manual Sample mode, particularly where the user's code is setting the SAMP bit (AD1CON1<1>), the DONE bit should also be cleared by the user application just before setting the SAMP bit.

5. Enabling op amps, comparator inputs and external voltage references can limit the availability of analog inputs (ANx pins). For example, when Op Amp 2 is enabled, the pins for ANO, AN1 and AN2 are used by the op amp's inputs and output. This negates the usefulness of Alternate Input mode since the MUXA selections use ANO-AN2. Carefully study the ADC block diagram to determine the configuration that will best suit your application. Configuration examples are available in the "Analog-to-Digital Converter (ADC)" (DS70621) section in the "dsPIC33/PIC24 Family Reference Manual".

### 23.3 ADC Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser: http://www.microchip.com/wwwproducts/Devices.aspx?dDocName=en555464

### 23.3.1 KEY RESOURCES

- "Analog-to-Digital Converter (ADC)" (DS70621) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- · Development Tools

### 24.3 PTG Control Registers

### REGISTER 24-1: PTGCST: PTG CONTROL/STATUS REGISTER

| R/W-0  | U-0 | R/W-0   | R/W-0   | U-0 | R/W-0                 | R/W-0                  | R/W-0   |

|--------|-----|---------|---------|-----|-----------------------|------------------------|---------|

| PTGEN  | _   | PTGSIDL | PTGTOGL | _   | PTGSWT <sup>(2)</sup> | PTGSSEN <sup>(3)</sup> | PTGIVIS |

| bit 15 |     |         |         |     |                       |                        | bit 8   |

| R/W-0   | HS-0    | U-0 | U-0 | U-0 | U-0 | R/V                    | V-0                    |

|---------|---------|-----|-----|-----|-----|------------------------|------------------------|

| PTGSTRT | PTGWDTO | _   | _   | _   | _   | PTGITM1 <sup>(1)</sup> | PTGITM0 <sup>(1)</sup> |

| bit 7   |         |     |     |     |     |                        | bit 0                  |

| Legend:           | HS = Hardware Settable bit |                             |                    |  |  |

|-------------------|----------------------------|-----------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read | d as '0'           |  |  |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown |  |  |

bit 15 **PTGEN:** Module Enable bit

1 = PTG module is enabled 0 = PTG module is disabled

0 - PTG Module is disabled

bit 14 **Unimplemented:** Read as '0'

bit 13 **PTGSIDL:** PTG Stop in Idle Mode bit

1 = Discontinues module operation when device enters Idle mode

0 = Continues module operation in Idle mode

bit 12 PTGTOGL: PTG TRIG Output Toggle Mode bit

1 = Toggle state of the PTGOx for each execution of the PTGTRIG command

0 = Each execution of the PTGTRIG command will generate a single PTGOx pulse determined by the value in the PTGPWDx bits

bit 11 **Unimplemented:** Read as '0'

bit 10 **PTGSWT:** PTG Software Trigger bit<sup>(2)</sup>

1 = Triggers the PTG module

0 = No action (clearing this bit will have no effect)

bit 9 **PTGSSEN:** PTG Enable Single-Step bit<sup>(3)</sup>

1 = Enables Single-Step mode

0 = Disables Single-Step mode

bit 8 **PTGIVIS:** PTG Counter/Timer Visibility Control bit

1 = Reads of the PTGSDLIM, PTGCxLIM or PTGTxLIM registers return the current values of their corresponding counter/timer registers (PTGSD, PTGCx, PTGTx)

0 = Reads of the PTGSDLIM, PTGCxLIM or PTGTxLIM registers return the value previously written to those limit registers

bit 7 PTGSTRT: PTG Start Sequencer bit

1 = Starts to sequentially execute commands (Continuous mode)

0 = Stops executing commands

bit 6 **PTGWDTO:** PTG Watchdog Timer Time-out Status bit

1 = PTG Watchdog Timer has timed out 0 = PTG Watchdog Timer has not timed out.

bit 5-2 **Unimplemented:** Read as '0'

**Note 1:** These bits apply to the PTGWHI and PTGWLO commands only.

2: This bit is only used with the PTGCTRL step command software trigger option.

3: Use of the PTG Single-Step mode is reserved for debugging tools only.

TABLE 28-1: SYMBOLS USED IN OPCODE DESCRIPTIONS (CONTINUED)

| Field | Description                                                                                                                                                                                                                                                    |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Wm,Wn | Dividend, Divisor working register pair (direct addressing)                                                                                                                                                                                                    |

| Wm*Wm | Multiplicand and Multiplier working register pair for Square instructions ∈ {W4 * W4,W5 * W5,W6 * W6,W7 * W7}                                                                                                                                                  |

| Wm*Wn | Multiplicand and Multiplier working register pair for DSP instructions ∈ {W4 * W5,W4 * W6,W4 * W7,W5 * W6,W5 * W7,W6 * W7}                                                                                                                                     |

| Wn    | One of 16 working registers ∈ {W0W15}                                                                                                                                                                                                                          |

| Wnd   | One of 16 destination working registers ∈ {W0W15}                                                                                                                                                                                                              |

| Wns   | One of 16 source working registers ∈ {W0W15}                                                                                                                                                                                                                   |

| WREG  | W0 (working register used in file register instructions)                                                                                                                                                                                                       |

| Ws    | Source W register ∈ { Ws, [Ws], [Ws++], [Ws], [++Ws], [Ws] }                                                                                                                                                                                                   |

| Wso   | Source W register ∈ { Wns, [Wns++], [Wns], [++Wns], [Wns], [Wns+Wb] }                                                                                                                                                                                          |

| Wx    | X Data Space Prefetch Address register for DSP instructions ∈ {[W8] + = 6, [W8] + = 4, [W8] + = 2, [W8], [W8] - = 6, [W8] - = 4, [W8] - = 2, [W9] + = 6, [W9] + = 4, [W9] + = 2, [W9], [W9] - = 6, [W9] - = 4, [W9] - = 2, [W9 + W12], none}                   |

| Wxd   | X Data Space Prefetch Destination register for DSP instructions ∈ {W4W7}                                                                                                                                                                                       |

| Wy    | Y Data Space Prefetch Address register for DSP instructions  ∈ {[W10] + = 6, [W10] + = 4, [W10] + = 2, [W10], [W10] - = 6, [W10] - = 4, [W10] - = 2,  [W11] + = 6, [W11] + = 4, [W11] + = 2, [W11], [W11] - = 6, [W11] - = 4, [W11] - = 2,  [W11 + W12], none} |

| Wyd   | Y Data Space Prefetch Destination register for DSP instructions ∈ {W4W7}                                                                                                                                                                                       |

TABLE 30-11: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS (CONTINUED)

| DC CH        | ARACTEF | RISTICS                                                         | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |      |                     |       | +85°C for Industrial                                                                                                      |

|--------------|---------|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------|-------|---------------------------------------------------------------------------------------------------------------------------|

| Param<br>No. | Symbol  | Characteristic                                                  | Min.                                                                                                                                                                                                                                             | Тур. | Max.                | Units | Conditions                                                                                                                |

| DI60a        | licl    | Input Low Injection Current                                     | 0                                                                                                                                                                                                                                                | _    | <sub>-5</sub> (4,7) | mA    | All pins except VDD, VSS, AVDD, AVSS, MCLR, VCAP and RB7                                                                  |

| DI60b        | lich    | Input High Injection Current                                    | 0                                                                                                                                                                                                                                                | _    | +5(5,6,7)           | mA    | All pins except VDD, VSS,<br>AVDD, AVSS, MCLR, VCAP,<br>RB7 and all 5V tolerant<br>pins <sup>(6)</sup>                    |

| DI60c        | ∑lict   | Total Input Injection Current (sum of all I/O and control pins) | -20 <sup>(8)</sup>                                                                                                                                                                                                                               | _    | +20(8)              | mA    | Absolute instantaneous sum of all $\pm$ input injection currents from all I/O pins (   IICL +   IICH   ) $\leq \sum$ IICT |

- Note 1: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current can be measured at different input voltages.

- 2: Negative current is defined as current sourced by the pin.

- 3: See the "Pin Diagrams" section for the 5V tolerant I/O pins.

- 4: VIL source < (Vss 0.3). Characterized but not tested.

- 5: Non-5V tolerant pins VIH source > (VDD + 0.3), 5V tolerant pins VIH source > 5.5V. Characterized but not tested.

- 6: Digital 5V tolerant pins cannot tolerate any "positive" input injection current from input sources > 5.5V.

- 7: Non-zero injection currents can affect the ADC results by approximately 4-6 counts.

- **8:** Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the mathematical "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. Characterized but not tested.

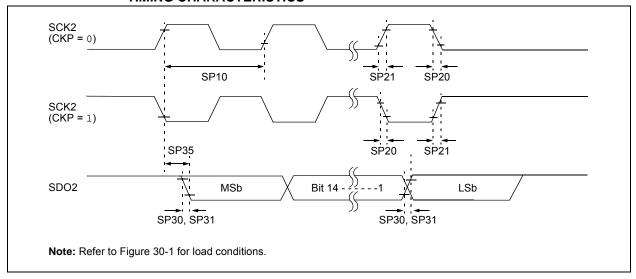

TABLE 30-33: SPI2 MAXIMUM DATA/CLOCK RATE SUMMARY

| AC CHARA             | CTERISTICS                               |                                             |                                            | dard Operating Conditions: 3.0V to 3.6V ass otherwise stated) ating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |     |     |

|----------------------|------------------------------------------|---------------------------------------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|

| Maximum<br>Data Rate | Master<br>Transmit Only<br>(Half-Duplex) | Master<br>Transmit/Receive<br>(Full-Duplex) | Slave<br>Transmit/Receive<br>(Full-Duplex) | CKE                                                                                                                                                                                                                                  | СКР | SMP |

| 15 MHz               | Table 30-33                              | _                                           | _                                          | 0,1                                                                                                                                                                                                                                  | 0,1 | 0,1 |

| 9 MHz                |                                          | Table 30-34                                 | _                                          | 1                                                                                                                                                                                                                                    | 0,1 | 1   |

| 9 MHz                |                                          | Table 30-35                                 | _                                          | 0                                                                                                                                                                                                                                    | 0,1 | 1   |

| 15 MHz               |                                          | _                                           | Table 30-36                                | 1                                                                                                                                                                                                                                    | 0   | 0   |

| 11 MHz               |                                          | _                                           | Table 30-37                                | 1                                                                                                                                                                                                                                    | 1   | 0   |

| 15 MHz               |                                          | _                                           | Table 30-38                                | 0                                                                                                                                                                                                                                    | 1   | 0   |

| 11 MHz               | _                                        | _                                           | Table 30-39                                | 0                                                                                                                                                                                                                                    | 0   | 0   |

FIGURE 30-14: SPI2 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 0) TIMING CHARACTERISTICS

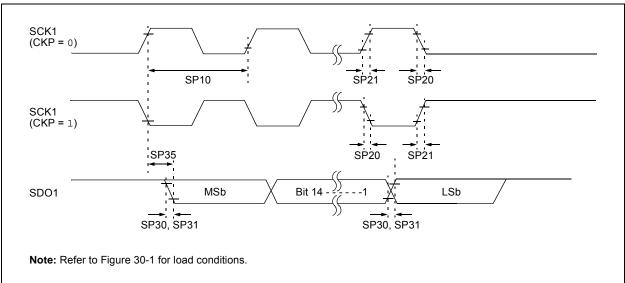

TABLE 30-41: SPI1 MAXIMUM DATA/CLOCK RATE SUMMARY

| AC CHARA             | CTERISTICS                               |                                             | (unless otherwise s                        | andard Operating Conditions: 3.0V to 3.6V nless otherwise stated) perating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extende |     |     |

|----------------------|------------------------------------------|---------------------------------------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|

| Maximum<br>Data Rate | Master<br>Transmit Only<br>(Half-Duplex) | Master<br>Transmit/Receive<br>(Full-Duplex) | Slave<br>Transmit/Receive<br>(Full-Duplex) | CKE                                                                                                                                                                                                                                        | СКР | SMP |

| 15 MHz               | Table 30-42                              | _                                           | _                                          | 0,1                                                                                                                                                                                                                                        | 0,1 | 0,1 |

| 10 MHz               | _                                        | Table 30-43                                 | _                                          | 1                                                                                                                                                                                                                                          | 0,1 | 1   |

| 10 MHz               | _                                        | Table 30-44                                 | _                                          | 0                                                                                                                                                                                                                                          | 0,1 | 1   |

| 15 MHz               | _                                        |                                             | Table 30-45                                | 1                                                                                                                                                                                                                                          | 0   | 0   |

| 11 MHz               | _                                        |                                             | Table 30-46                                | 1                                                                                                                                                                                                                                          | 1   | 0   |

| 15 MHz               | <u> </u>                                 |                                             | Table 30-47                                | 0                                                                                                                                                                                                                                          | 1   | 0   |

| 11 MHz               | <del>-</del>                             | _                                           | Table 30-48                                | 0                                                                                                                                                                                                                                          | 0   | 0   |

FIGURE 30-22: SPI1 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 0) TIMING CHARACTERISTICS

**TABLE 30-56: CTMU CURRENT SOURCE SPECIFICATIONS**

| DC CHARA     | ACTERISTI   | cs                                                 | Standard Operating Conditions:3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |       |      | . ≤ +85°C for Industrial |                                   |

|--------------|-------------|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|--------------------------|-----------------------------------|

| Param<br>No. | Symbol      | Characteristic                                     | Min.                                                                                                                                                                                                                                            | Тур.  | Max. | Units                    | Conditions                        |

| CTMU Curi    | rent Source | 9                                                  |                                                                                                                                                                                                                                                 |       |      |                          |                                   |

| CTMUI1       | IOUT1       | Base Range <sup>(1)</sup>                          | 0.29                                                                                                                                                                                                                                            | _     | 0.77 | μA                       | CTMUICON<9:8> = 01                |

| CTMUI2       | IOUT2       | 10x Range <sup>(1)</sup>                           | 3.85                                                                                                                                                                                                                                            | _     | 7.7  | μA                       | CTMUICON<9:8> = 10                |

| CTMUI3       | Іоит3       | 100x Range <sup>(1)</sup>                          | 38.5                                                                                                                                                                                                                                            | _     | 77   | μA                       | CTMUICON<9:8> = 11                |

| CTMUI4       | Iout4       | 1000x Range <sup>(1)</sup>                         | 385                                                                                                                                                                                                                                             | _     | 770  | μA                       | CTMUICON<9:8> = 00                |

| CTMUFV1      | VF          | Temperature Diode Forward Voltage <sup>(1,2)</sup> | _                                                                                                                                                                                                                                               | 0.598 | _    | V                        | TA = +25°C,<br>CTMUICON<9:8> = 01 |

|              |             |                                                    | _                                                                                                                                                                                                                                               | 0.658 | _    | V                        | TA = +25°C,<br>CTMUICON<9:8> = 10 |

|              |             |                                                    |                                                                                                                                                                                                                                                 | 0.721 | _    | V                        | TA = +25°C,<br>CTMUICON<9:8> = 11 |

| CTMUFV2      | VFVR        | Temperature Diode Rate of                          | _                                                                                                                                                                                                                                               | -1.92 | _    | mV/°C                    | CTMUICON<9:8> = 01                |

|              |             | Change <sup>(1,2,3)</sup>                          | _                                                                                                                                                                                                                                               | -1.74 |      | mV/°C                    | CTMUICON<9:8> = 10                |

|              |             |                                                    | _                                                                                                                                                                                                                                               | -1.56 | _    | mV/°C                    | CTMUICON<9:8> = 11                |

Note 1: Nominal value at center point of current trim range (CTMUICON<15:10> = 000000).

- VREF+ = AVDD = 3.3V

- · ADC configured for 10-bit mode

- ADC module configured for conversion speed of 500 ksps

- All PMDx bits are cleared (PMDx = 0)

- Executing a while(1) statement

- · Device operating from the FRC with no PLL

<sup>2:</sup> Parameters are characterized but not tested in manufacturing.

**<sup>3:</sup>** Measurements taken with the following conditions:

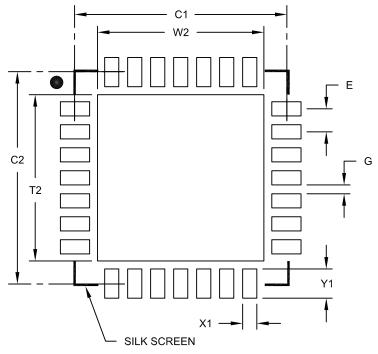

# 28-Lead Plastic Quad Flat, No Lead Package (MM) – 6x6x0.9 mm Body [QFN-S] with 0.40 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                            |        | MILLIM | ETERS    |      |

|----------------------------|--------|--------|----------|------|

| Dimension                  | Limits | MIN    | NOM      | MAX  |

| Contact Pitch              | Е      |        | 0.65 BSC |      |

| Optional Center Pad Width  | W2     |        |          | 4.70 |

| Optional Center Pad Length | T2     |        |          | 4.70 |

| Contact Pad Spacing        | C1     |        | 6.00     |      |

| Contact Pad Spacing        | C2     |        | 6.00     |      |

| Contact Pad Width (X28)    | X1     |        |          | 0.40 |

| Contact Pad Length (X28)   | Y1     |        |          | 0.85 |

| Distance Between Pads      | G      | 0.25   |          |      |

### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2124A

## **Revision D (December 2011)**

This revision includes typographical and formatting changes throughout the data sheet text.

All other major changes are referenced by their respective section in Table A-3.

TABLE A-3: MAJOR SECTION UPDATES

| Section Name                                                                                                                                                            | Update Description                                                                                                                                                                                                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "16-bit Microcontrollers<br>and Digital Signal<br>Controllers (up to<br>512-Kbyte Flash and<br>48-Kbyte SRAM) with High-<br>Speed PWM, Op amps, and<br>Advanced Analog" | Removed the Analog Comparators column and updated the Op amps/Comparators column in Table 1 and Table 2.                                                                                                                                         |

| Section 21.0 "Enhanced<br>CAN (ECAN™) Module<br>(dsPIC33EPXXXGP/MC50X<br>Devices Only)"                                                                                 | Updated the CANCKS bit value definitions in CiCTRL1: ECAN Control Register 1 (see Register 21-1).                                                                                                                                                |

| Section 30.0 "Electrical Characteristics"                                                                                                                               | Updated the VBOR specifications and/or its related note in the following electrical characteristics tables:  • Table 30-1  • Table 30-4  • Table 30-12  • Table 30-15  • Table 30-16  • Table 30-56  • Table 30-57  • Table 30-59  • Table 30-60 |

| Р                                          |          | Q                                         |     |

|--------------------------------------------|----------|-------------------------------------------|-----|

| Packaging                                  | 479      | QEI                                       |     |

| Details                                    | 505      | Control Registers                         | 252 |

| Marking                                    | 479, 481 | Resources                                 | 251 |

| Peripheral Module Disable (PMD)            | 165      | Quadrature Encoder Interface (QEI)        | 249 |

| Peripheral Pin Select (PPS)                | 175      | D                                         |     |

| Available Peripherals                      | 175      | R                                         |     |

| Available Pins                             | 175      | Register Maps                             |     |

| Control                                    | 175      | ADC1                                      | 84  |

| Control Registers                          | 183      | CPU Core (dsPIC33EPXXXMC20X/50X,          |     |

| Input Mapping                              | 176      | dsPIC33EPXXXGP50X Devices)                |     |

| Output Selection for Remappable Pins       | 180      | CPU Core (PIC24EPXXXGP/MC20X Devices)     |     |

| Pin Selection for Selectable Input Sources | 178      | CRC                                       |     |

| Selectable Input Sources                   | 177      | CTMU                                      |     |

| Peripheral Trigger Generator (PTG) Module  | 337      | DMAC                                      | 98  |

| PICkit 3 In-Circuit Debugger/Programmer    | 399      | ECAN1 (When WIN (C1CTRL1) = 0 or 1)       |     |

| Pinout I/O Descriptions (table)            | 26       | for dsPIC33EPXXXMC/GP50X Devices          | 85  |

| Power-Saving Features                      |          | ECAN1 (When WIN (C1CTRL1) = 0) for        |     |

| Clock Frequency                            | 163      | dsPIC33EPXXXMC/GP50X Devices              | 85  |

| Clock Switching                            |          | ECAN1 (WIN (C1CTRL1) = 1) for             |     |

| Instruction-Based Modes                    | 163      | dsPIC33EPXXXMC/GP50X Devices              |     |

| ldle                                       | 164      | I2C1 and I2C2                             |     |

| Interrupts Coincident with Power           |          | Input Capture 1 through Input Capture 4   | 76  |

| Save Instructions                          | 164      | Interrupt Controller                      |     |

| Sleep                                      | 164      | (dsPIC33EPXXXGP50X Devices)               | 69  |

| Resources                                  |          | Interrupt Controller                      |     |

| Program Address Space                      |          | (dsPIC33EPXXXMC20X Devices)               | 71  |

| Construction                               | 117      | Interrupt Controller                      |     |

| Data Access from Program Memory Using      |          | (dsPIC33EPXXXMC50X Devices)               | 73  |

| Table Instructions                         | 118      | Interrupt Controller                      |     |

| Memory Map (dsPIC33EP128GP50X,             |          | (PIC24EPXXXGP20X Devices)                 | 66  |

| dsPIC33EP128MC20X/50X,                     |          | Interrupt Controller                      |     |

| PIC24EP128GP/MC20X Devices)                | 47       | (PIC24EPXXXMC20X Devices)                 |     |

| Memory Map (dsPIC33EP256GP50X,             |          | JTAG Interface                            |     |

| dsPIC33EP256MC20X/50X,                     |          | NVM                                       |     |

| PIC24EP256GP/MC20X Devices)                | 48       | Op Amp/Comparator                         |     |

| Memory Map (dsPIC33EP32GP50X,              |          | Output Compare 1 through Output Compare 4 | //  |

| dsPIC33EP32MC20X/50X,                      |          | Peripheral Pin Select Input               | 0.4 |

| PIC24EP32GP/MC20X Devices)                 | 45       | (dsPIC33EPXXXGP50X Devices)               | 91  |

| Memory Map (dsPIC33EP512GP50X,             |          | Peripheral Pin Select Input               | 00  |

| dsPIC33EP512MC20X/50X,                     |          | (dsPIC33EPXXXMC20X Devices)               | 92  |

| PIC24EP512GP/MC20X Devices)                | 49       | Peripheral Pin Select Input               | 04  |

| Memory Map (dsPIC33EP64GP50X,              |          | (dsPIC33EPXXXMC50X Devices)               | 91  |

| dsPIC33EP64MC20X/50X,                      | 40       | Peripheral Pin Select Input               | 00  |

| PIC24EP64GP/MC20X Devices)                 | 46       | (PIC24EPXXXGP20X Devices)                 | 90  |

| Table Read High Instructions               |          | Peripheral Pin Select Input               | 00  |

| TBLRDH                                     |          | (PIC24EPXXXMC20X Devices)                 | 90  |

| Table Read Low Instructions (TBLRDL)       | 118      | Peripheral Pin Select Output              |     |

| Program Memory                             |          | (dsPIC33EPXXXGP/MC202/502,                | 0.0 |

| Organization                               |          | PIC24EPXXXGP/MC202 Devices)               | 88  |

| Reset Vector                               |          | Peripheral Pin Select Output              |     |

| Programmable CRC Generator                 |          | (dsPIC33EPXXXGP/MC203/503,                | 0.0 |

| Control Registers                          |          | PIC24EPXXXGP/MC203 Devices)               | 00  |

| Overview                                   |          | Peripheral Pin Select Output              |     |

| Resources                                  |          | (dsPIC33EPXXXGP/MC204/504,                | 00  |

| Programmer's Model                         |          | PIC24EPXXXGP/MC204 Devices)               | 69  |

| Register Descriptions                      | 37       | Peripheral Pin Select Output              |     |

| PTG                                        | 0.10     | (dsPIC33EPXXXGP/MC206/506,                | 00  |

| Control Registers                          |          | PIC24EPXXGP/MC206 Devices)                |     |

| Introduction                               |          | PMD (dsPIC33EPXXXGP50X Devices)           |     |

| Output Descriptions                        |          | PMD (dsPIC33EPXXXMC20X Devices)           |     |

| Resources                                  |          | PMD (dsPIC33EPXXXMC50X Devices)           |     |

| Step Commands and Format                   | 350      | PMD (PIC24EPXXXGP20X Devices)             | 94  |