Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                      |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 60 MIPs                                                                       |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                 |

| Number of I/O              | 35                                                                            |

| Program Memory Size        | 32KB (10.7K x 24)                                                             |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | ·                                                                             |

| RAM Size                   | 2K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 9x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 44-VQFN Exposed Pad                                                           |

| Supplier Device Package    | 44-QFN (8x8)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep32mc204-h-ml |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

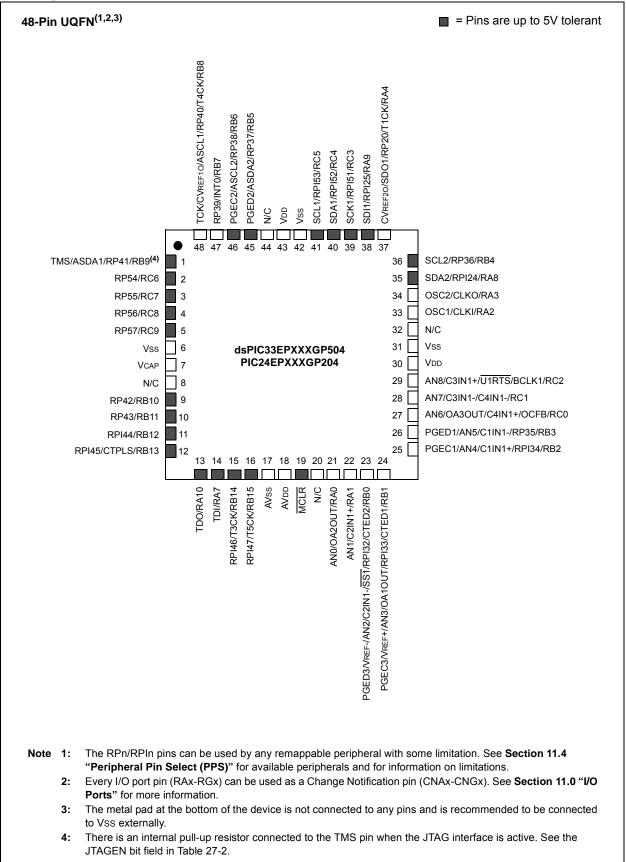

#### Pin Diagrams (Continued)

#### **TABLE 4-3**: INTERRUPT CONTROLLER REGISTER MAP FOR PIC24EPXXXGP20X DEVICES ONLY

| TADLL        | τу.   |        |        |            | VELEN  |        |        |            |        |       |         | DEVICE      |         |         |          |              |         |               |

|--------------|-------|--------|--------|------------|--------|--------|--------|------------|--------|-------|---------|-------------|---------|---------|----------|--------------|---------|---------------|

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8  | Bit 7 | Bit 6   | Bit 5       | Bit 4   | Bit 3   | Bit 2    | Bit 1        | Bit 0   | All<br>Resets |

| IFS0         | 0800  |        | DMA1IF | AD1IF      | U1TXIF | U1RXIF | SPI1IF | SPI1EIF    | T3IF   | T2IF  | OC2IF   | IC2IF       | DMA0IF  | T1IF    | OC1IF    | IC1IF        | INTOIF  | 0000          |

| IFS1         | 0802  | U2TXIF | U2RXIF | INT2IF     | T5IF   | T4IF   | OC4IF  | OC3IF      | DMA2IF | _     | _       | —           | INT1IF  | CNIF    | CMIF     | MI2C1IF      | SI2C1IF | 0000          |

| IFS2         | 0804  |        | _      | _          | -      |        | _      | —          | _      | _     | IC4IF   | IC3IF       | DMA3IF  | _       | —        | SPI2IF       | SPI2EIF | 0000          |

| IFS3         | 0806  | _      | _      | _          | _      | _      | _      | _          | _      | _     | _       | _           | _       | _       | MI2C2IF  | SI2C2IF      | _       | 0000          |

| IFS4         | 0808  | _      | _      | CTMUIF     | _      | _      | _      | _          | _      | _     | _       | _           | _       | CRCIF   | U2EIF    | U1EIF        | _       | 0000          |

| IFS8         | 0810  | JTAGIF | ICDIF  |            | _      | _      | _      | —          | —      | _     | _       | _           | _       | _       | —        | —            | —       | 0000          |

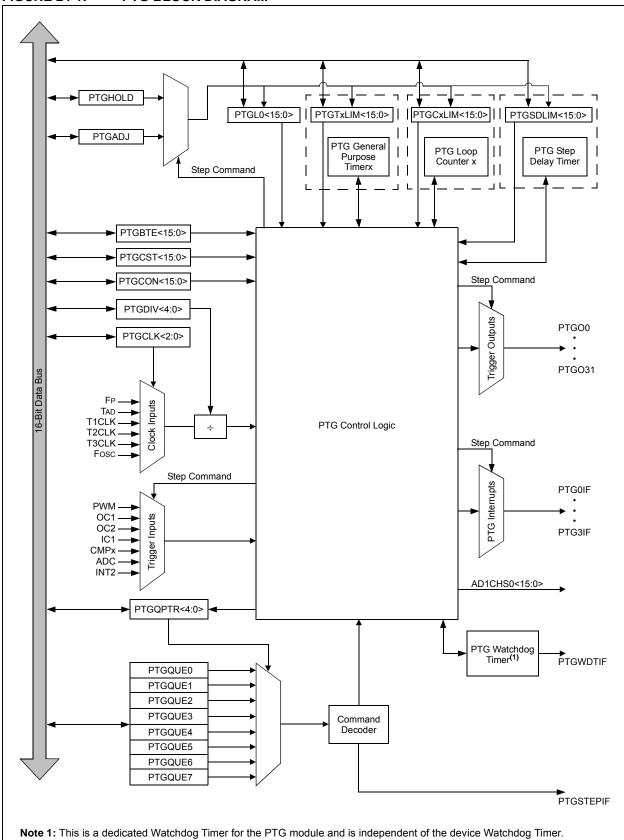

| IFS9         | 0812  | _      | _      | _          | _      | _      | _      | —          | —      | _     | PTG3IF  | PTG2IF      | PTG1IF  | PTG0IF  | PTGWDTIF | PTGSTEPIF    | _       | 0000          |

| IEC0         | 0820  | _      | DMA1IE | AD1IE      | U1TXIE | U1RXIE | SPI1IE | SPI1EIE    | T3IE   | T2IE  | OC2IE   | IC2IE       | DMA0IE  | T1IE    | OC1IE    | IC1IE        | INT0IE  | 0000          |

| IEC1         | 0822  | U2TXIE | U2RXIE | INT2IE     | T5IE   | T4IE   | OC4IE  | OC3IE      | DMA2IE | _     | _       | _           | INT1IE  | CNIE    | CMIE     | MI2C1IE      | SI2C1IE | 0000          |

| IEC2         | 0824  | _      | _      | _          | _      | _      | _      | _          | _      | _     | IC4IE   | IC3IE       | DMA3IE  | _       | _        | SPI2IE       | SPI2EIE | 0000          |

| IEC3         | 0826  | _      | _      | _          | _      | _      | _      | —          | —      | _     | _       | _           | _       | _       | MI2C2IE  | SI2C2IE      | —       | 0000          |

| IEC4         | 0828  | _      | _      | CTMUIE     | _      | _      | _      | _          | _      | _     | _       | _           | _       | CRCIE   | U2EIE    | U1EIE        | _       | 0000          |

| IEC8         | 0830  | JTAGIE | ICDIE  | _          | _      | _      | _      | _          | _      | _     | _       | _           | _       | _       | _        | _            | _       | 0000          |

| IEC9         | 0832  | _      | _      | _          | _      | _      | _      | —          | —      | _     | PTG3IE  | PTG2IE      | PTG1IE  | PTG0IE  | PTGWDTIE | PTGSTEPIE    | _       | 0000          |

| IPC0         | 0840  | _      |        | T1IP<2:0>  |        | _      | (      | OC1IP<2:0  | >      | _     |         | IC1IP<2:0>  |         | —       |          | INT0IP<2:0>  |         | 4444          |

| IPC1         | 0842  | _      |        | T2IP<2:0>  |        | _      | (      | OC2IP<2:0  | >      | _     |         | IC2IP<2:0>  |         | _       | C        | 0MA0IP<2:0>  |         | 4444          |

| IPC2         | 0844  | _      | U      | J1RXIP<2:0 | >      | _      | ;      | SPI1IP<2:0 | >      | _     |         | SPI1EIP<2:0 | >       | _       |          | T3IP<2:0>    |         | 4444          |

| IPC3         | 0846  | _      | _      | _          | _      | _      | D      | )MA1IP<2:  | 0>     | _     |         | AD1IP<2:0>  |         | _       | ι        | J1TXIP<2:0>  |         | 0444          |

| IPC4         | 0848  |        |        | CNIP<2:0>  |        |        |        | CMIP<2:0   | >      | _     |         | MI2C1IP<2:0 | >       | _       | S        | SI2C1IP<2:0> |         | 4444          |

| IPC5         | 084A  | _      | _      | _          | _      | _      | _      | _          | _      | _     | _       | —           | _       | _       | I        | INT1IP<2:0>  |         | 0004          |

| IPC6         | 084C  | _      |        | T4IP<2:0>  |        | _      | (      | OC4IP<2:0  | >      | _     |         | OC3IP<2:0>  |         | _       | C        | )ma2IP<2:0>  |         | 4444          |

| IPC7         | 084E  |        | 1      | U2TXIP<2:0 | >      |        | L      | J2RXIP<2:  | )>     | _     |         | INT2IP<2:0> |         | _       |          | T5IP<2:0>    |         | 4444          |

| IPC8         | 0850  |        | _      | _          | _      |        | _      | —          | —      | _     |         | SPI2IP<2:0> |         | _       | S        | SPI2EIP<2:0> |         | 0044          |

| IPC9         | 0852  |        | _      | _          |        |        |        | IC4IP<2:0  | >      | _     |         | IC3IP<2:0>  |         | _       | C        | 0MA3IP<2:0>  |         | 0444          |

| IPC12        | 0858  |        | _      | _          |        |        | N      | 112C2IP<2: | 0>     | _     |         | SI2C2IP<2:0 | >       | _       | _        | _            | _       | 0440          |

| IPC16        | 0860  |        |        | CRCIP<2:0> | >      |        |        | U2EIP<2:0  | >      | _     |         | U1EIP<2:0>  |         | _       | _        | _            | _       | 4440          |

| IPC19        | 0866  |        | _      | _          | _      | _      | _      | _          | _      | _     |         | CTMUIP<2:0  | >       | _       | _        | _            | _       | 0040          |

| IPC35        | 0886  |        |        | JTAGIP<2:0 | >      | _      |        | ICDIP<2:0  | >      | _     | _       | _           | _       | _       | _        | _            | _       | 4400          |

| IPC36        | 0888  | _      |        | PTG0IP<2:0 | >      | _      | PT     | GWDTIP<    | 2:0>   | _     | P       | TGSTEPIP<2  | :0>     | _       | _        | —            | _       | 4440          |

| IPC37        | 088A  | _      | _      | _          | _      | _      | F      | PTG3IP<2:  | )>     | _     |         | PTG2IP<2:0  | >       | _       | F        | PTG1IP<2:0>  |         | 0444          |

| INTCON1      | 08C0  | NSTDIS | OVAERR | OVBERR     | _      |        |        |            | —      | _     | DIV0ERR | DMACERR     | MATHERR | ADDRERR | STKERR   | OSCFAIL      |         | 0000          |

| INTCON2      | 08C2  | GIE    | DISI   | SWTRAP     | _      |        |        |            | _      | _     |         | —           | —       | _       | INT2EP   | INT1EP       | INT0EP  | 8000          |

| INTCON3      | 08C4  | _      | _      | _          | _      |        |        | _          | _      | _     | _       | DAE         | DOOVR   | _       | _        | —            |         | 0000          |

| INTCON4      | 08C6  |        | _      | _          | _      | _      | _      | —          | _      | _     | _       | _           | _       | _       | _        |              | SGHT    | 0000          |

| INTTREG      | 08C8  | _      |        |            | _      |        | ILR<   | 3:0>       |        |       |         |             | VECN    | UM<7:0> |          |              |         | 0000          |

|              |       |        |        |            |        |        |        |            |        |       |         |             |         |         |          |              |         |               |

- = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-0         | R/W-0                                     | U-0                                    | U-0           | R/W-0                 | U-0               | R/W-0            | R/W-0         |

|---------------|-------------------------------------------|----------------------------------------|---------------|-----------------------|-------------------|------------------|---------------|

| TRAPF         | R IOPUWR                                  | —                                      | _             | VREGSF                | —                 | CM               | VREGS         |

| bit 15        |                                           |                                        |               |                       |                   |                  | bit 8         |

|               |                                           | DANIO                                  | DAA/ O        | DAMA                  | DAMO              |                  |               |

| R/W-0         |                                           | R/W-0                                  | R/W-0         | R/W-0                 | R/W-0             | R/W-1            | R/W-1         |

| EXTR<br>bit 7 | SWR                                       | SWDTEN <sup>(2)</sup>                  | WDTO          | SLEEP                 | IDLE              | BOR              | POR           |

|               |                                           |                                        |               |                       |                   |                  | bit (         |

| Legend:       |                                           |                                        |               |                       |                   |                  |               |

| R = Reada     | able bit                                  | W = Writable I                         | oit           | U = Unimpler          | mented bit, read  | d as '0'         |               |

| -n = Value    | at POR                                    | '1' = Bit is set                       |               | '0' = Bit is cle      | ared              | x = Bit is unkı  | nown          |

|               |                                           |                                        |               |                       |                   |                  |               |

| bit 15        | •                                         | Reset Flag bit                         |               |                       |                   |                  |               |

|               |                                           | onflict Reset ha<br>onflict Reset ha   |               | d                     |                   |                  |               |

| bit 14        | •                                         | gal Opcode or                          |               |                       | et Flag bit       |                  |               |

|               |                                           | I opcode detec                         |               |                       | •                 | lized W registe  | er used as ar |

|               |                                           | Pointer caused                         |               |                       |                   |                  |               |

|               | -                                         | l opcode or Uni                        |               | egister Reset h       | as not occurred   | d                |               |

| bit 13-12     | -                                         | ted: Read as '                         |               |                       | . 1.9             |                  |               |

| bit 11        |                                           | ash Voltage Reg<br>Itage regulator i   |               |                       | p bit             |                  |               |

|               |                                           | ltage regulator (                      |               | •                     | ing Sleep         |                  |               |

| bit 10        |                                           | ted: Read as '                         | -             | ,,                    | 5                 |                  |               |

| bit 9         | CM: Configur                              | ation Mismatch                         | Flag bit      |                       |                   |                  |               |

|               | 1 = A Configu                             | uration Mismatc<br>uration Mismatc     | h Reset has   |                       |                   |                  |               |

| bit 8         | VREGS: Volta                              | age Regulator S                        | Standby Durir | ng Sleep bit          |                   |                  |               |

|               | •                                         | egulator is active<br>egulator goes in | •             | •                     | еер               |                  |               |

| bit 7         | EXTR: Extern                              | nal Reset (MCL                         | R) Pin bit    |                       |                   |                  |               |

|               |                                           | Clear (pin) Res<br>Clear (pin) Res     |               |                       |                   |                  |               |

| bit 6         | SWR: Softwa                               | re RESET (Instr                        | uction) Flag  | bit                   |                   |                  |               |

|               |                                           | instruction has instruction has        |               |                       |                   |                  |               |

| bit 5         | SWDTEN: So                                | oftware Enable/                        | Disable of W  | DT bit <sup>(2)</sup> |                   |                  |               |

|               | 1 = WDT is e<br>0 = WDT is di             |                                        |               |                       |                   |                  |               |

| bit 4         | WDTO: Watc                                | hdog Timer Tim                         | e-out Flag bi | it                    |                   |                  |               |

|               |                                           | e-out has occur<br>e-out has not oc    |               |                       |                   |                  |               |

| Note 1:       | All of the Reset sta<br>cause a device Re |                                        | set or cleare | d in software. S      | Setting one of th | ese bits in soft | ware does not |

| 2:            | If the FWDTEN Co<br>SWDTEN bit settir     | onfiguration bit i                     | s '1' (unprog | rammed), the V        | VDT is always e   | enabled, regard  | lless of the  |

# REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup>

# 9.3 Oscillator Control Registers

# REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1)</sup>

| U-0            | R-0                                                                | R-0                                                                                                                                  | R-0                                | U-0                                | R/W-y                              | R/W-y                | R/W-y                |  |  |  |  |

|----------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|------------------------------------|------------------------------------|----------------------|----------------------|--|--|--|--|

| _              | COSC2                                                              | COSC1                                                                                                                                | COSC0                              | —                                  | NOSC2 <sup>(2)</sup>               | NOSC1 <sup>(2)</sup> | NOSCO <sup>(2)</sup> |  |  |  |  |

| bit 15         |                                                                    |                                                                                                                                      |                                    |                                    |                                    |                      | bit 8                |  |  |  |  |

| R/W-0          | R/W-0                                                              | R-0                                                                                                                                  | U-0                                | R/W-0                              | U-0                                | U-0                  | R/W-0                |  |  |  |  |

| CLKLOC         | CK IOLOCK                                                          | LOCK                                                                                                                                 |                                    | CF <sup>(3)</sup>                  |                                    |                      | OSWEN                |  |  |  |  |

| bit 7          |                                                                    |                                                                                                                                      |                                    |                                    |                                    |                      | bit (                |  |  |  |  |

| Legend:        |                                                                    | y = Value set                                                                                                                        | from Configur                      | ation bits on F                    | POR                                |                      |                      |  |  |  |  |

| R = Reada      | able bit                                                           | W = Writable                                                                                                                         | -                                  |                                    | mented bit, read                   | l as '0'             |                      |  |  |  |  |

| -n = Value     | at POR                                                             | '1' = Bit is se                                                                                                                      | t                                  | '0' = Bit is cle                   | eared                              | x = Bit is unkr      | nown                 |  |  |  |  |

| hit 1 <i>5</i> | Unimplemen                                                         | ted. Dood oo                                                                                                                         | 0'                                 |                                    |                                    |                      |                      |  |  |  |  |

| bit 15         | -                                                                  | ted: Read as                                                                                                                         |                                    |                                    |                                    |                      |                      |  |  |  |  |

| bit 14-12      |                                                                    | Current Oscill                                                                                                                       |                                    |                                    | /)                                 |                      |                      |  |  |  |  |

|                |                                                                    | C Oscillator (F<br>C Oscillator (F                                                                                                   |                                    |                                    |                                    |                      |                      |  |  |  |  |

|                |                                                                    |                                                                                                                                      |                                    |                                    |                                    |                      |                      |  |  |  |  |

|                |                                                                    | 101 = Low-Power RC Oscillator (LPRC)<br>100 = Reserved                                                                               |                                    |                                    |                                    |                      |                      |  |  |  |  |

|                |                                                                    | 011 = Primary Oscillator (XT, HS, EC) with PLL                                                                                       |                                    |                                    |                                    |                      |                      |  |  |  |  |

|                |                                                                    | 010 = Primary Oscillator (XT, HS, EC)<br>001 = Fast RC Oscillator (FRC) with Divide-by-N and PLL (FRCPLL)                            |                                    |                                    |                                    |                      |                      |  |  |  |  |

|                |                                                                    | C Oscillator (F<br>C Oscillator (F                                                                                                   |                                    | le-by-N and Pl                     | LL (FRCPLL)                        |                      |                      |  |  |  |  |

| bit 11         |                                                                    | ted: Read as                                                                                                                         | ,                                  |                                    |                                    |                      |                      |  |  |  |  |

| bit 10-8       | NOSC<2:0>:                                                         | New Oscillato                                                                                                                        | r Selection bits                   | <sub>S</sub> (2)                   |                                    |                      |                      |  |  |  |  |

|                | 111 = Fast R                                                       | C Oscillator (F                                                                                                                      | RC) with Divid                     | le-by-n                            |                                    |                      |                      |  |  |  |  |

|                |                                                                    | C Oscillator (F                                                                                                                      |                                    | le-by-16                           |                                    |                      |                      |  |  |  |  |

|                |                                                                    | ower RC Oscil                                                                                                                        | ator (LPRC)                        |                                    |                                    |                      |                      |  |  |  |  |

|                | 100 = Reserv                                                       | /ed<br>y Oscillator (X                                                                                                               |                                    |                                    |                                    |                      |                      |  |  |  |  |

|                |                                                                    | y Oscillator (X                                                                                                                      |                                    | IFLL                               |                                    |                      |                      |  |  |  |  |

|                |                                                                    | C Oscillator (F                                                                                                                      |                                    | le-by-N and Pl                     | LL (FRCPLL)                        |                      |                      |  |  |  |  |

|                |                                                                    | C Oscillator (F                                                                                                                      |                                    | ,                                  | ,                                  |                      |                      |  |  |  |  |

| bit 7          |                                                                    | Clock Lock Ena                                                                                                                       |                                    |                                    |                                    |                      |                      |  |  |  |  |

|                |                                                                    |                                                                                                                                      |                                    | configurations                     | are locked; if (F                  | =CKSM0 = 0), t       | then clock and       |  |  |  |  |

|                |                                                                    | figurations may<br>d PLL selectio                                                                                                    |                                    | ked, configurat                    | ions may be mo                     | odified              |                      |  |  |  |  |

| bit 6          |                                                                    | <ul> <li>0 = Clock and PLL selections are not locked, configurations may be modified</li> <li>IOLOCK: I/O Lock Enable bit</li> </ul> |                                    |                                    |                                    |                      |                      |  |  |  |  |

|                | 1 = I/O lock is                                                    | s active                                                                                                                             |                                    |                                    |                                    |                      |                      |  |  |  |  |

|                | 0 = I/O lock is                                                    | s not active                                                                                                                         |                                    |                                    |                                    |                      |                      |  |  |  |  |

| bit 5          | LOCK: PLL L                                                        | ock Status bit                                                                                                                       | (read-only)                        |                                    |                                    |                      |                      |  |  |  |  |

|                |                                                                    | s that PLL is in<br>s that PLL is ou                                                                                                 |                                    |                                    | satisfied<br>progress or PLL       | is disabled          |                      |  |  |  |  |

| Note 1:        | Writes to this regis                                               |                                                                                                                                      |                                    |                                    |                                    |                      | ʻdsPIC33/            |  |  |  |  |

| 2:             | Direct clock switch<br>This applies to cloo<br>mode as a transitio | es between ar<br>ck switches in                                                                                                      | y primary osci<br>either directior | llator mode wi<br>n. In these inst | th PLL and FRC<br>ances, the appli | PLL mode are         |                      |  |  |  |  |

| 0              | This bit should only                                               |                                                                                                                                      |                                    |                                    |                                    |                      |                      |  |  |  |  |

**3:** This bit should only be cleared in software. Setting the bit in software (= 1) will have the same effect as an actual oscillator failure and trigger an oscillator failure trap.

- g) The TRISx registers control only the digital I/O output buffer. Any other dedicated or remappable active "output" will automatically override the TRIS setting. The TRISx register does not control the digital logic "input" buffer. Remappable digital "inputs" do not automatically override TRIS settings, which means that the TRISx bit must be set to input for pins with only remappable input function(s) assigned

- h) All analog pins are enabled by default after any Reset and the corresponding digital input buffer on the pin has been disabled. Only the Analog Pin Select registers control the digital input buffer, *not* the TRISx register. The user must disable the analog function on a pin using the Analog Pin Select registers in order to use any "digital input(s)" on a corresponding pin, no exceptions.

### 11.6 I/O Ports Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

#### 11.6.1 KEY RESOURCES

- "I/O Ports" (DS70598) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

### REGISTER 17-1: QEI1CON: QEI1 CONTROL REGISTER (CONTINUED)

| bit 6-4 | <b>INTDIV&lt;2:0&gt;:</b> Timer Input Clock Prescale Select bits (interval timer, main timer (position counter), velocity counter and index counter internal clock divider select) <sup>(3)</sup>                                                                                                                            |  |  |  |  |  |  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|         | <pre>111 = 1:128 prescale value<br/>110 = 1:64 prescale value<br/>101 = 1:32 prescale value<br/>100 = 1:16 prescale value<br/>011 = 1:8 prescale value<br/>010 = 1:4 prescale value<br/>001 = 1:2 prescale value<br/>000 = 1:1 prescale value</pre>                                                                          |  |  |  |  |  |  |

| bit 3   | <b>CNTPOL:</b> Position and Index Counter/Timer Direction Select bit<br>1 = Counter direction is negative unless modified by external up/down signal                                                                                                                                                                         |  |  |  |  |  |  |

|         | <ul> <li>0 = Counter direction is positive unless modified by external up/down signal</li> </ul>                                                                                                                                                                                                                             |  |  |  |  |  |  |

| bit 2   | GATEN: External Count Gate Enable bit                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

|         | <ul> <li>1 = External gate signal controls position counter operation</li> <li>0 = External gate signal does not affect position counter/timer operation</li> </ul>                                                                                                                                                          |  |  |  |  |  |  |

| bit 1-0 | CCM<1:0>: Counter Control Mode Selection bits                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

|         | <ul> <li>11 = Internal Timer mode with optional external count is selected</li> <li>10 = External clock count with optional external count is selected</li> <li>01 = External clock count with external up/down direction is selected</li> <li>00 = Quadrature Encoder Interface (x4 mode) Count mode is selected</li> </ul> |  |  |  |  |  |  |

| Note 1: | When CCM<1:0> = 10 or 11, all of the QEI counters operate as timers and the PIMOD<2:0> bits are ignored.                                                                                                                                                                                                                     |  |  |  |  |  |  |

- 2: When CCM<1:0> = 00, and QEA and QEB values match the Index Match Value (IMV), the POSCNTH and POSCNTL registers are reset. QEA/QEB signals used for the index match have swap and polarity values applied, as determined by the SWPAB and QEAPOL/QEBPOL bits.

- 3: The selected clock rate should be at least twice the expected maximum quadrature count rate.

| R-0                                                    | R-0 | R-0                          | R-0                                                | R-0                                                                                            | R-0                                                                                       | R-0                                                                                                                  |  |

|--------------------------------------------------------|-----|------------------------------|----------------------------------------------------|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--|

|                                                        |     | TERR                         | CNT<7:0>                                           |                                                                                                |                                                                                           |                                                                                                                      |  |

|                                                        |     |                              |                                                    |                                                                                                |                                                                                           | bit 8                                                                                                                |  |

|                                                        |     |                              |                                                    |                                                                                                |                                                                                           |                                                                                                                      |  |

| R-0                                                    | R-0 | R-0                          | R-0                                                | R-0                                                                                            | R-0                                                                                       | R-0                                                                                                                  |  |

|                                                        |     | RERR                         | CNT<7:0>                                           |                                                                                                |                                                                                           |                                                                                                                      |  |

|                                                        |     |                              |                                                    |                                                                                                |                                                                                           | bit 0                                                                                                                |  |

|                                                        |     |                              |                                                    |                                                                                                |                                                                                           |                                                                                                                      |  |

|                                                        |     |                              |                                                    |                                                                                                |                                                                                           |                                                                                                                      |  |

| R = Readable bit W = Writable bit                      |     |                              | U = Unimplemented bit, read as '0'                 |                                                                                                |                                                                                           |                                                                                                                      |  |

| = Value at POR '1' = Bit is set '0' = Bit is cleared x |     |                              |                                                    | x = Bit is unkr                                                                                | nown                                                                                      |                                                                                                                      |  |

|                                                        | R-0 | R-0 R-0<br>it W = Writable b | TERR<br>R-0 R-0 R-0<br>RERR<br>it W = Writable bit | TERRCNT<7:0>           R-0         R-0         R-0           RERRCNT<7:0>         RERRCNT<7:0> | TERRCNT<7:0>           R-0         R-0         R-0           RERRCNT<7:0>         RERRCNT | TERRCNT<7:0>         R-0       R-0       R-0       R-0         RERRCNT<7:0>       U = Unimplemented bit, read as '0' |  |

bit 7-0 **RERRCNT<7:0>:** Receive Error Count bits

#### REGISTER 21-9: CxCFG1: ECANx BAUD RATE CONFIGURATION REGISTER 1

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | _   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| SJW1  | SJW0  | BRP5  | BRP4  | BRP3  | BRP2  | BRP1  | BRP0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                                                                  |                      |                    |  |

|-------------------|------------------------------------------------------------------|----------------------|--------------------|--|

| R = Readable bit  | Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |

| -n = Value at POR | '1' = Bit is set                                                 | '0' = Bit is cleared | x = Bit is unknown |  |

| bit 15-8 | Unimplemented: Read as '0' |

|----------|----------------------------|

|----------|----------------------------|

| bit 7-6 | SJW<1:0>: Synchronization Jump Width bits    |

|---------|----------------------------------------------|

|         | 11 = Length is 4 x TQ                        |

|         | $10 = \text{Length is } 3 \times \text{Tq}$  |

|         | $01 = \text{Length is } 2 \times \text{T} Q$ |

|         | $00 = \text{Length is } 1 \times \text{Tq}$  |

```

bit 5-0 BRP<5:0>: Baud Rate Prescaler bits

```

```

11 1111 = TQ = 2 x 64 x 1/FCAN

```

•

- 00 0010 = TQ = 2 x 3 x 1/FCAN 00 0001 = TQ = 2 x 2 x 1/FCAN

- 00 0000 = Tq = 2 x 1 x 1/FCAN

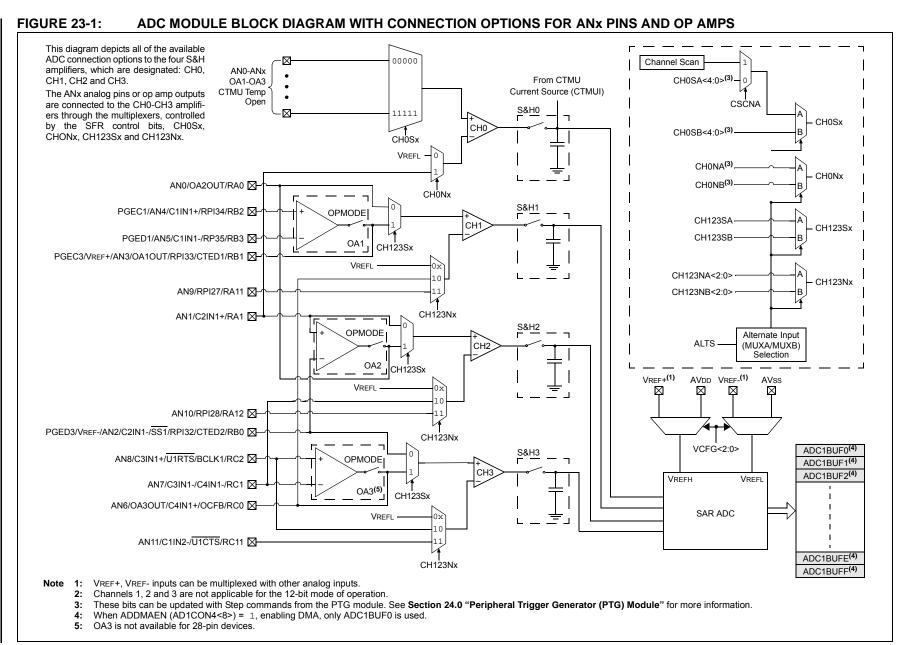

# 23.0 10-BIT/12-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

- **Note 1:** This data sheet summarizes the features of the dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. То complement the information in this data sheet. refer to "Analog-to-Digital Converter (ADC)" (DS70621) in the "dsPIC33/PIC24 Family Reference Manual', which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices have one ADC module. The ADC module supports up to 16 analog input channels.

On ADC1, the AD12B bit (AD1CON1<10>) allows the ADC module to be configured by the user as either a 10-bit, 4 Sample-and-Hold (S&H) ADC (default configuration) or a 12-bit, 1 S&H ADC.

Note: The ADC module needs to be disabled before modifying the AD12B bit.

# 23.1 Key Features

#### 23.1.1 10-BIT ADC CONFIGURATION

The 10-bit ADC configuration has the following key features:

- Successive Approximation (SAR) conversion

- · Conversion speeds of up to 1.1 Msps

- · Up to 16 analog input pins

- Connections to three internal op amps

- Connections to the Charge Time Measurement Unit (CTMU) and temperature measurement diode

- Channel selection and triggering can be controlled by the Peripheral Trigger Generator (PTG)

- External voltage reference input pins

- · Simultaneous sampling of:

- Up to four analog input pins

- Three op amp outputs

- Combinations of analog inputs and op amp outputs

- Automatic Channel Scan mode

- Selectable conversion Trigger source

- · Selectable Buffer Fill modes

- Four result alignment options (signed/unsigned, fractional/integer)

- Operation during CPU Sleep and Idle modes

#### 23.1.2 12-BIT ADC CONFIGURATION

The 12-bit ADC configuration supports all the features listed above, with the exception of the following:

- In the 12-bit configuration, conversion speeds of up to 500 ksps are supported

- There is only one S&H amplifier in the 12-bit configuration; therefore, simultaneous sampling of multiple channels is not supported.

Depending on the particular device pinout, the ADC can have up to 16 analog input pins, designated AN0 through AN15. These analog inputs are shared with op amp inputs and outputs, comparator inputs, and external voltage references. When op amp/comparator functionality is enabled, or an external voltage reference is used, the analog input that shares that pin is no longer available. The actual number of analog input pins, op amps and external voltage reference input configuration depends on the specific device.

A block diagram of the ADC module is shown in Figure 23-1. Figure 23-2 provides a diagram of the ADC conversion clock period.

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

# 23.2 ADC Helpful Tips

- 1. The SMPIx control bits in the AD1CON2 register:

- a) Determine when the ADC interrupt flag is set and an interrupt is generated, if enabled.

- b) When the CSCNA bit in the AD1CON2 registers is set to '1', this determines when the ADC analog scan channel list, defined in the AD1CSSL/AD1CSSH registers, starts over from the beginning.

- c) When the DMA peripheral is not used (ADDMAEN = 0), this determines when the ADC Result Buffer Pointer to ADC1BUF0-ADC1BUFF gets reset back to the beginning at ADC1BUF0.

- d) When the DMA peripheral is used (ADDMAEN = 1), this determines when the DMA Address Pointer is incremented after a sample/conversion operation. ADC1BUF0 is the only ADC buffer used in this mode. The ADC Result Buffer Pointer to ADC1BUF0-ADC1BUFF gets reset back to the beginning at ADC1BUF0. The DMA address is incremented after completion of every 32nd sample/conversion operation. Conversion results are stored in the ADC1BUF0 register for transfer to RAM using DMA.

- 2. When the DMA module is disabled (ADDMAEN = 0), the ADC has 16 result buffers. ADC conversion results are stored sequentially in ADC1BUF0-ADC1BUFF, regardless of which analog inputs are being used subject to the SMPIx bits and the condition described in 1c) above. There is no relationship between the ANx input being measured and which ADC buffer (ADC1BUF0-ADC1BUFF) that the conversion results will be placed in.

- 3. When the DMA module is enabled (ADDMAEN = 1), the ADC module has only 1 ADC result buffer (i.e., ADC1BUF0) per ADC peripheral and the ADC conversion result must be read, either by the CPU or DMA Controller, before the next ADC conversion is complete to avoid overwriting the previous value.

- 4. The DONE bit (AD1CON1<0>) is only cleared at the start of each conversion and is set at the completion of the conversion, but remains set indefinitely, even through the next sample phase until the next conversion begins. If application code is monitoring the DONE bit in any kind of software loop, the user must consider this behavior because the CPU code execution is faster than the ADC. As a result, in Manual Sample mode, particularly where the user's code is setting the SAMP bit (AD1CON1<1>), the DONE bit should also be cleared by the user application just before setting the SAMP bit.

5. Enabling op amps, comparator inputs and external voltage references can limit the availability of analog inputs (ANx pins). For example, when Op Amp 2 is enabled, the pins for ANO, AN1 and AN2 are used by the op amp's inputs and output. This negates the usefulness of Alternate Input mode since the MUXA selections use AN0-AN2. Carefully study the ADC block diagram to determine the configuration that will best suit your application. Configuration examples are available in the "Analog-to-Digital Converter (ADC)" (DS70621) section in the "dsPIC33/ PIC24 Family Reference Manual".

#### 23.3 ADC Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser:<br>http://www.microchip.com/wwwproducts/ |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | Devices.aspx?dDocName=en555464                                                                                                                          |

#### 23.3.1 KEY RESOURCES

- "Analog-to-Digital Converter (ADC)" (DS70621) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

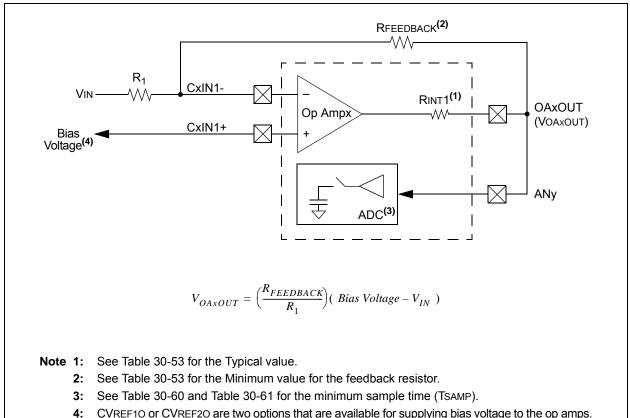

#### 25.1.2 OP AMP CONFIGURATION B

Figure 25-7 shows a typical inverting amplifier circuit with the output of the op amp (OAxOUT) externally routed to a separate analog input pin (ANy) on the device. This op amp configuration is slightly different in terms of the op amp output and the ADC input connection, therefore, RINT1 is not included in the transfer function. However, this configuration requires the designer to externally route the op amp output (OAxOUT) to another analog input pin (ANy). See Table 30-53 in **Section 30.0 "Electrical Characteristics"** for the typical value of RINT1. Table 30-60 and Table 30-61 in **Section 30.0 "Electrical Characteristics"** describe the minimum sample time (TSAMP) requirements for the ADC module in this configuration.

Figure 25-7 also defines the equation to be used to calculate the expected voltage at point VOAxOUT. This is the typical inverting amplifier equation.

## 25.2 Op Amp/Comparator Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 25.2.1 KEY RESOURCES

- "Op Amp/Comparator" (DS70357) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- · Application Notes

- Software Libraries

- · Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

#### FIGURE 25-7: OP AMP CONFIGURATION B

| Base<br>Instr<br># | Assembly<br>Mnemonic |           | Assembly Syntax                                  | Description                                 | # of<br>Words | # of<br>Cycles <sup>(2)</sup> | Status Flags<br>Affected |  |

|--------------------|----------------------|-----------|--------------------------------------------------|---------------------------------------------|---------------|-------------------------------|--------------------------|--|

| 25                 | DAW                  | DAW Wn Wn |                                                  | Wn = decimal adjust Wn                      | 1             | 1                             | С                        |  |

| 26                 | DEC                  | DEC       | f                                                | f = f - 1                                   | 1             | 1                             | C,DC,N,OV,Z              |  |

|                    |                      | DEC       | f,WREG                                           | WREG = f – 1                                | 1             | 1                             | C,DC,N,OV,Z              |  |

|                    |                      | DEC       | Ws,Wd                                            | Wd = Ws - 1                                 | 1             | 1                             | C,DC,N,OV,Z              |  |

| 27                 | DEC2                 | DEC2      | f                                                | f = f - 2                                   | 1             | 1                             | C,DC,N,OV,Z              |  |

|                    |                      | DEC2      | f,WREG                                           | WREG = f – 2                                | 1             | 1                             | C,DC,N,OV,Z              |  |

|                    |                      | DEC2      | Ws,Wd                                            | Wd = Ws - 2                                 | 1             | 1                             | C,DC,N,OV,Z              |  |

| 28                 | DISI                 | DISI      | #lit14                                           | Disable Interrupts for k instruction cycles | 1             | 1                             | None                     |  |

| 29                 | DIV                  | DIV.S     | Wm,Wn                                            | Signed 16/16-bit Integer Divide             | 1             | 18                            | N,Z,C,OV                 |  |

|                    |                      | DIV.SD    | Wm,Wn                                            | Signed 32/16-bit Integer Divide             | 1             | 18                            | N,Z,C,OV                 |  |

|                    |                      | DIV.U     | Wm,Wn                                            | Unsigned 16/16-bit Integer Divide           | 1             | 18                            | N,Z,C,OV                 |  |

|                    |                      | DIV.UD    | Wm,Wn                                            | Unsigned 32/16-bit Integer Divide           | 1             | 18                            | N,Z,C,OV                 |  |

| 30                 | DIVF                 | DIVF      | Wm , Wn <sup>(1)</sup>                           | Signed 16/16-bit Fractional Divide          | 1             | 18                            | N,Z,C,OV                 |  |

| 31                 | DO                   | DO        | #lit15,Expr <sup>(1)</sup>                       | Do code to PC + Expr, lit15 + 1 times       | 2             | 2                             | None                     |  |

|                    |                      | DO        | Wn, Expr(1)                                      | Do code to PC + Expr, (Wn) + 1 times        | 2             | 2                             | None                     |  |

| 32                 | ED                   | ED        | Wm*Wm,Acc,Wx,Wy,Wxd <sup>(1)</sup>               | Euclidean Distance (no accumulate)          | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |  |

| 33                 | EDAC                 | EDAC      | Wm*Wm,Acc,Wx,Wy,Wxd <sup>(1)</sup>               | Euclidean Distance                          | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |  |

| 34                 | EXCH                 | EXCH      | Wns,Wnd                                          | Swap Wns with Wnd                           | 1             | 1                             | None                     |  |

| 35                 | FBCL                 | FBCL      | Ws,Wnd                                           | Find Bit Change from Left (MSb) Side        | 1             | 1                             | С                        |  |

| 36                 | FF1L                 | FF1L      | Ws,Wnd                                           | Find First One from Left (MSb) Side         | 1             | 1                             | С                        |  |

| 37                 | FF1R                 | FF1R      | Ws,Wnd                                           | Find First One from Right (LSb) Side        | 1             | 1                             | С                        |  |

| 38                 | GOTO                 | GOTO      | Expr                                             | Go to address                               | 2             | 4                             | None                     |  |

|                    |                      | GOTO      | Wn                                               | Go to indirect                              | 1             | 4                             | None                     |  |

|                    |                      | GOTO.L    | Wn                                               | Go to indirect (long address)               | 1             | 4                             | None                     |  |

| 39                 | INC                  | INC       | f                                                | f = f + 1                                   | 1             | 1                             | C,DC,N,OV,Z              |  |

|                    |                      | INC       | f,WREG                                           | WREG = f + 1                                | 1             | 1                             | C,DC,N,OV,Z              |  |

|                    |                      | INC       | Ws,Wd                                            | Wd = Ws + 1                                 | 1             | 1                             | C,DC,N,OV,Z              |  |

| 40                 | INC2                 | INC2      | f                                                | f = f + 2                                   | 1             | 1                             | C,DC,N,OV,Z              |  |

|                    |                      | INC2      | f,WREG                                           | WREG = f + 2                                | 1             | 1                             | C,DC,N,OV,Z              |  |

|                    |                      | INC2      | Ws,Wd                                            | Wd = Ws + 2                                 | 1             | 1                             | C,DC,N,OV,Z              |  |

| 41                 | IOR                  | IOR       | f                                                | f = f .IOR. WREG                            | 1             | 1                             | N,Z                      |  |

|                    |                      | IOR       | f,WREG                                           | WREG = f .IOR. WREG                         | 1             | 1                             | N,Z                      |  |

|                    |                      | IOR       | #lit10,Wn                                        | Wd = lit10 .IOR. Wd                         | 1             | 1                             | N,Z                      |  |

|                    |                      | IOR       | Wb,Ws,Wd                                         | Wd = Wb .IOR. Ws                            | 1             | 1                             | N,Z                      |  |

|                    |                      | IOR       | Wb,#lit5,Wd                                      | Wd = Wb .IOR. lit5                          | 1             | 1                             | N,Z                      |  |

| 42                 | LAC                  | LAC       | Wso,#Slit4,Acc                                   | Load Accumulator                            | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |  |

| 43                 | LNK                  | LNK       | #lit14                                           | Link Frame Pointer                          | 1             | 1                             | SFA                      |  |

| 44                 | LSR                  | LSR       | f                                                | f = Logical Right Shift f                   | 1             | 1                             | C,N,OV,Z                 |  |

|                    |                      | LSR       | f,WREG                                           | WREG = Logical Right Shift f                | 1             | 1                             | C,N,OV,Z                 |  |

|                    |                      | LSR       | Ws,Wd                                            | Wd = Logical Right Shift Ws                 | 1             | 1                             | C,N,OV,Z                 |  |

|                    |                      | LSR       | Wb,Wns,Wnd                                       | Wnd = Logical Right Shift Wb by Wns         | 1             | 1                             | N,Z                      |  |

|                    |                      | LSR       | Wb,#lit5,Wnd                                     | Wnd = Logical Right Shift Wb by lit5        | 1             | 1                             | N,Z                      |  |

| 45                 | MAC                  | MAC       | Wm*Wn, Acc, Wx, Wxd, Wy, Wyd, AWB <sup>(1)</sup> | Multiply and Accumulate                     | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |  |

|                    |                      | MAC       | Wm*Wm,Acc,Wx,Wxd,Wy,Wyd(1)                       | Square and Accumulate                       | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |  |

#### TABLE 28-2: INSTRUCTION SET OVERVIEW (CONTINUED)

Note 1: These instructions are available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| DC CHARACTERISTICS                     |      |      | (unless othe | •          | <b>s: 3.0V to 3.6V</b><br>≤ Ta ≤ +85°C for Indi<br>≤ Ta ≤ +125°C for Ex |           |  |  |

|----------------------------------------|------|------|--------------|------------|-------------------------------------------------------------------------|-----------|--|--|

| Parameter<br>No.                       | Тур. | Max. | Units        | Conditions |                                                                         |           |  |  |

| Operating Current (IDD) <sup>(1)</sup> |      |      |              |            |                                                                         |           |  |  |

| DC20d                                  | 9    | 15   | mA           | -40°C      |                                                                         |           |  |  |

| DC20a                                  | 9    | 15   | mA           | +25°C      | 3.3V                                                                    | 10 MIPS   |  |  |

| DC20b                                  | 9    | 15   | mA           | +85°C      | 3.3V                                                                    | 10 1011-5 |  |  |

| DC20c                                  | 9    | 15   | mA           | +125°C     |                                                                         |           |  |  |

| DC22d                                  | 16   | 25   | mA           | -40°C      |                                                                         | 20 MIPS   |  |  |

| DC22a                                  | 16   | 25   | mA           | +25°C      | 3.3∨                                                                    |           |  |  |

| DC22b                                  | 16   | 25   | mA           | +85°C      | 3.3V                                                                    |           |  |  |

| DC22c                                  | 16   | 25   | mA           | +125°C     |                                                                         |           |  |  |

| DC24d                                  | 27   | 40   | mA           | -40°C      |                                                                         |           |  |  |

| DC24a                                  | 27   | 40   | mA           | +25°C      | 3.3V                                                                    | 40 MIPS   |  |  |

| DC24b                                  | 27   | 40   | mA           | +85°C      | 3.3V                                                                    |           |  |  |

| DC24c                                  | 27   | 40   | mA           | +125°C     |                                                                         |           |  |  |

| DC25d                                  | 36   | 55   | mA           | -40°C      |                                                                         |           |  |  |

| DC25a                                  | 36   | 55   | mA           | +25°C      | 3.3V                                                                    | 60 MIPS   |  |  |

| DC25b                                  | 36   | 55   | mA           | +85°C      | 3.3V                                                                    | OU IVIIPS |  |  |

| DC25c                                  | 36   | 55   | mA           | +125°C     | 7                                                                       |           |  |  |

| DC26d                                  | 41   | 60   | mA           | -40°C      |                                                                         |           |  |  |

| DC26a                                  | 41   | 60   | mA           | +25°C      | 3.3V                                                                    | 70 MIPS   |  |  |

| DC26b                                  | 41   | 60   | mA           | +85°C      |                                                                         |           |  |  |

#### TABLE 30-6: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

**Note 1:** IDD is primarily a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDD measurements are as follows:

• Oscillator is configured in EC mode with PLL, OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)

- · CLKO is configured as an I/O input pin in the Configuration Word

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- CPU, SRAM, program memory and data memory are operational

- No peripheral modules are operating; however, every peripheral is being clocked (all PMDx bits are zeroed)

- CPU is executing while(1) {NOP(); } statement

- · JTAG is disabled

| DC CHARACTERISTICS |        |                                                             | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |                                                             |       |                                                                                                                                                                        |   |

|--------------------|--------|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------------------------------------------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Param.             | Symbol | Characteristic                                              | Min.                                                                                                                                                                                                                                                                                  | Тур. | Max.                                                        | Units | Conditions                                                                                                                                                             |   |

| DO10               | Vol    | Output Low Voltage<br>4x Sink Driver Pins <sup>(2)</sup>    |                                                                                                                                                                                                                                                                                       |      | 0.4                                                         | V     | VDD = 3.3V,<br>$IOL \le 6 \text{ mA}, -40^{\circ}\text{C} \le Ta \le +85^{\circ}\text{C}$<br>$IOL \le 5 \text{ mA}, +85^{\circ}\text{C} < Ta \le +125^{\circ}\text{C}$ |   |

|                    |        | Output Low Voltage<br>8x Sink Driver Pins <sup>(3)</sup>    | _                                                                                                                                                                                                                                                                                     |      | 0.4                                                         | V     |                                                                                                                                                                        |   |

| DO20               | Vон    | Output High Voltage<br>4x Source Driver Pins <sup>(2)</sup> | 2.4                                                                                                                                                                                                                                                                                   |      | _                                                           | V     | $IOH \ge -10 \text{ mA}, \text{ VDD} = 3.3 \text{ V}$                                                                                                                  |   |

|                    |        |                                                             |                                                                                                                                                                                                                                                                                       |      | Output High Voltage<br>8x Source Driver Pins <sup>(3)</sup> | 2.4   | _                                                                                                                                                                      | — |

| DO20A              | Von1   | Output High Voltage                                         | 1.5(1)                                                                                                                                                                                                                                                                                | _    |                                                             | V     | $IOH \ge -14 \text{ mA}, \text{ VDD} = 3.3 \text{V}$                                                                                                                   |   |