Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Betano                     |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                      |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 60 MIPs                                                                       |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                 |

| Number of I/O              | 35                                                                            |

| Program Memory Size        | 32KB (10.7K x 24)                                                             |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 2K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 9x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 44-VFTLA Exposed Pad                                                          |

| Supplier Device Package    | 44-VTLA (6x6)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep32mc204-h-tl |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

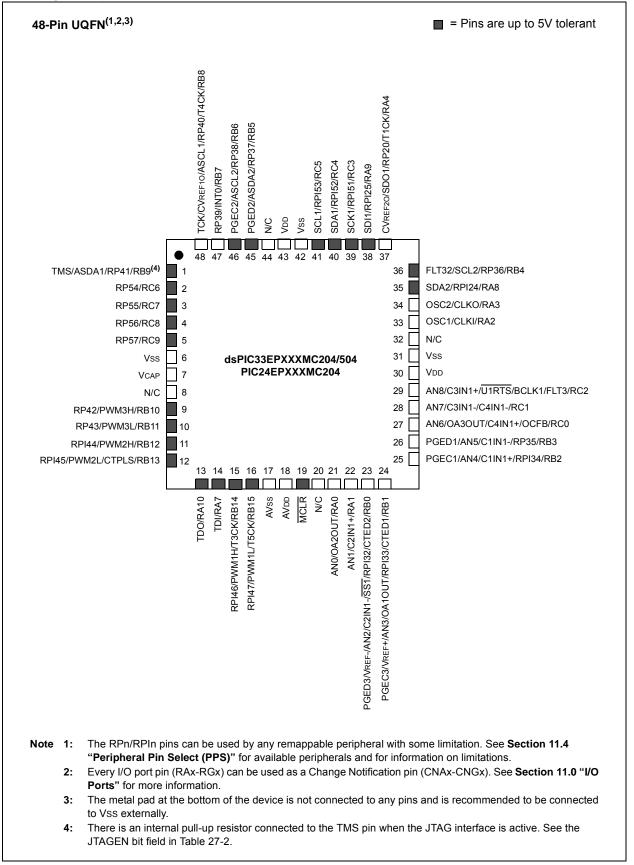

### Pin Diagrams (Continued)

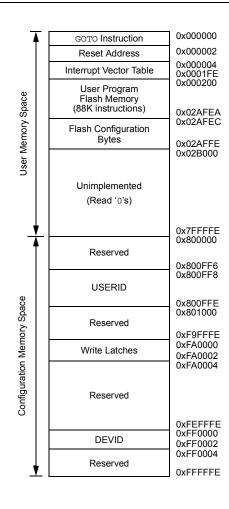

#### FIGURE 4-4: PROGRAM MEMORY MAP FOR dsPIC33EP256GP50X, dsPIC33EP256MC20X/50X AND PIC24EP256GP/MC20X DEVICES

Note: Memory areas are not shown to scale.

## 5.0 FLASH PROGRAM MEMORY

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXGP/MC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Flash Programming" (DS70609) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices contain internal Flash program memory for storing and executing application code. The memory is readable, writable and erasable during normal operation over the entire VDD range.

Flash memory can be programmed in two ways:

- In-Circuit Serial Programming™ (ICSP™) programming capability

- Run-Time Self-Programming (RTSP)

ICSP allows for a dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X device to be serially programmed while in the end application circuit. This is done with two lines for programming clock and programming data (one of the alternate programming pin pairs: PGECx/PGEDx), and three other lines for power (VDD), ground (VSS) and Master Clear (MCLR). This allows customers to manufacture boards with unprogrammed devices and then program the device just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

RTSP is accomplished using TBLRD (Table Read) and TBLWT (Table Write) instructions. With RTSP, the user application can write program memory data a single program memory word, and erase program memory in blocks or 'pages' of 1024 instructions (3072 bytes) at a time.

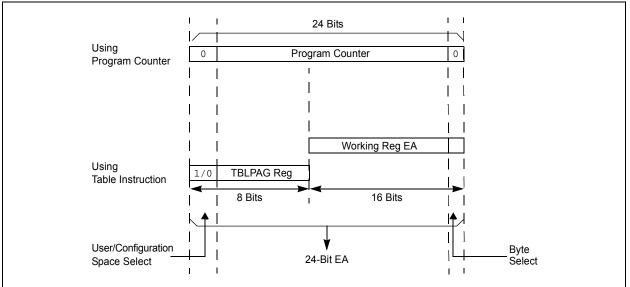

## 5.1 Table Instructions and Flash Programming

Regardless of the method used, all programming of Flash memory is done with the Table Read and Table Write instructions. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using bits<7:0> of the TBLPAG register and the Effective Address (EA) from a W register, specified in the table instruction, as shown in Figure 5-1.

The TBLRDL and the TBLWTL instructions are used to read or write to bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes.

The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

#### FIGURE 5-1: ADDRESSING FOR TABLE REGISTERS

| R/W-0  | U-0   | R/W-0 | R/W-0  | R/W-0               | R-0 | R-0   | R-0   |

|--------|-------|-------|--------|---------------------|-----|-------|-------|

| VAR    | —     | US1   | US0    | EDT                 | DL2 | DL1   | DL0   |

| bit 15 |       | •     |        |                     |     |       | bit 8 |

|        |       |       |        |                     |     |       |       |

| R/W-0  | R/W-0 | R/W-1 | R/W-0  | R/C-0               | R-0 | R/W-0 | R/W-0 |

| SATA   | SATB  | SATDW | ACCSAT | IPL3 <sup>(2)</sup> | SFA | RND   | IF    |

| bit 7  |       | •     |        |                     |     |       | bit 0 |

|        |       |       |        |                     |     |       |       |

|        |       |       |        |                     |     |       |       |

## **REGISTER 7-2:** CORCON: CORE CONTROL REGISTER<sup>(1)</sup>

| Legend:           | C = Clearable bit |                      |                                    |  |  |  |

|-------------------|-------------------|----------------------|------------------------------------|--|--|--|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bi | U = Unimplemented bit, read as '0' |  |  |  |

| -n = Value at POR | '1'= Bit is set   | '0' = Bit is cleared | x = Bit is unknown                 |  |  |  |

bit

| VAR: Variable Exception Processing Latency Control                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------|

| <ol> <li>1 = Variable exception processing is enabled</li> </ol>                                                              |

| 0 = Fixed exception processing is enabled                                                                                     |

| IPL3: CPU Interrupt Priority Level Status bit 3 <sup>(2)</sup>                                                                |

| <ul> <li>1 = CPU Interrupt Priority Level is greater than 7</li> <li>0 = CPU Interrupt Priority Level is 7 or less</li> </ul> |

|                                                                                                                               |

**Note 1:** For complete register details, see Register 3-2.

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

| U-0    | U-0 | U-0 | U-0 | U-0   | U-0   | U-0   | U-0   |

|--------|-----|-----|-----|-------|-------|-------|-------|

| _      |     |     |     | _     | —     |       | —     |

| bit 15 |     |     |     |       |       |       | bit 8 |

|        |     |     |     |       |       |       |       |

| U-0    | U-0 | U-0 | U-0 | R-0   | R-0   | R-0   | R-0   |

| —      | —   | —   | _   | PPST3 | PPST2 | PPST1 | PPST0 |

| bit 7  |     |     |     |       |       |       | bit 0 |

#### REGISTER 8-14: DMAPPS: DMA PING-PONG STATUS REGISTER

| Legend:          |                                                                                   |                                                                                       |                       |                    |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-----------------------|--------------------|--|--|--|--|--|

| R = Readable bit |                                                                                   | W = Writable bit                                                                      | U = Unimplemented bit | , read as '0'      |  |  |  |  |  |

| -n = Value a     | at POR                                                                            | '1' = Bit is set                                                                      | '0' = Bit is cleared  | x = Bit is unknown |  |  |  |  |  |

| bit 15-4         | Unimplo                                                                           | montod: Dood os 'o'                                                                   |                       |                    |  |  |  |  |  |

| bit 3            | Unimplemented: Read as '0'<br>PPST3: DMA Channel 3 Ping-Pong Mode Status Flag bit |                                                                                       |                       |                    |  |  |  |  |  |

| bit 5            | 1 = DMA                                                                           | ASTB3 register is selected<br>ASTA3 register is selected                              | vioue Status Flag bit |                    |  |  |  |  |  |

| bit 2            | 1 = DMA                                                                           | DMA Channel 2 Ping-Pong I<br>ASTB2 register is selected<br>ASTA2 register is selected | Mode Status Flag bit  |                    |  |  |  |  |  |

| bit 1            | PPST1:                                                                            | DMA Channel 1 Ping-Pong I                                                             | Mode Status Flag bit  |                    |  |  |  |  |  |

|                  |                                                                                   | CTD1 register is calested                                                             |                       |                    |  |  |  |  |  |

- 1 = DMASTB1 register is selected0 = DMASTA1 register is selected

- bit 0 PPST0: DMA Channel 0 Ping-Pong Mode Status Flag bit

- 1 = DMASTB0 register is selected

- 0 = DMASTA0 register is selected

| REGISTER     | <u>R 10-2: PMD</u> 2                                                                                           | 2: PERIPHER                                         | AL MODULE       | DISABLE C         | ONTROL RE       | GISTER 2        |       |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-----------------|-------------------|-----------------|-----------------|-------|--|--|--|

| U-0          | U-0                                                                                                            | U-0                                                 | U-0             | R/W-0             | R/W-0           | R/W-0           | R/W-0 |  |  |  |

| _            |                                                                                                                | —                                                   |                 | IC4MD             | IC3MD           | IC2MD           | IC1MD |  |  |  |

| bit 15       |                                                                                                                |                                                     |                 |                   |                 |                 | bit   |  |  |  |

| U-0          | U-0                                                                                                            | U-0                                                 | U-0             | R/W-0             | R/W-0           | R/W-0           | R/W-0 |  |  |  |

|              |                                                                                                                |                                                     |                 | OC4MD             | OC3MD           | OC2MD           | OC1MD |  |  |  |

| bit 7        |                                                                                                                |                                                     |                 |                   |                 |                 | bit   |  |  |  |

|              |                                                                                                                |                                                     |                 |                   |                 |                 |       |  |  |  |

| Legend:      | 1.1.1                                                                                                          |                                                     |                 |                   |                 |                 |       |  |  |  |

| R = Readab   |                                                                                                                | W = Writable b                                      | Dit             | •                 | nented bit, rea |                 |       |  |  |  |

| -n = Value a | at POR                                                                                                         | '1' = Bit is set                                    |                 | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |  |  |  |

| bit 15-12    | Unimplemen                                                                                                     | ted: Read as '0                                     | ,               |                   |                 |                 |       |  |  |  |

| bit 11       | -                                                                                                              | t Capture 4 Mod                                     |                 |                   |                 |                 |       |  |  |  |

|              | •                                                                                                              | ture 4 module is                                    |                 |                   |                 |                 |       |  |  |  |

|              | 0 = Input Cap                                                                                                  | oture 4 module is                                   | s enabled       |                   |                 |                 |       |  |  |  |

| bit 10       | IC3MD: Input                                                                                                   | t Capture 3 Mod                                     | ule Disable bit |                   |                 |                 |       |  |  |  |

|              |                                                                                                                | oture 3 module is                                   |                 |                   |                 |                 |       |  |  |  |

|              |                                                                                                                | 0 = Input Capture 3 module is enabled               |                 |                   |                 |                 |       |  |  |  |

| bit 9        |                                                                                                                | Capture 2 Mod                                       |                 |                   |                 |                 |       |  |  |  |

|              |                                                                                                                | oture 2 module is<br>oture 2 module is              |                 |                   |                 |                 |       |  |  |  |

| bit 8        | IC1MD: Input                                                                                                   | t Capture 1 Mod                                     | ule Disable bit |                   |                 |                 |       |  |  |  |

|              | 1 = Input Cap                                                                                                  | oture 1 module is<br>oture 1 module is              | s disabled      |                   |                 |                 |       |  |  |  |

| bit 7-4      |                                                                                                                | ted: Read as '0                                     |                 |                   |                 |                 |       |  |  |  |

| bit 3        | OC4MD: Out                                                                                                     | put Compare 4                                       | Module Disable  | e bit             |                 |                 |       |  |  |  |

|              | 1 = Output Compare 4 module is disabled                                                                        |                                                     |                 |                   |                 |                 |       |  |  |  |

|              | -                                                                                                              | ompare 4 modu                                       |                 |                   |                 |                 |       |  |  |  |

| bit 2        | OC3MD: Output Compare 3 Module Disable bit                                                                     |                                                     |                 |                   |                 |                 |       |  |  |  |

|              | 1 = Output Compare 3 module is disabled                                                                        |                                                     |                 |                   |                 |                 |       |  |  |  |

| L:1 4        | <ul> <li>0 = Output Compare 3 module is enabled</li> <li>OC2MD: Output Compare 2 Module Disable bit</li> </ul> |                                                     |                 |                   |                 |                 |       |  |  |  |

| bit 1        |                                                                                                                |                                                     |                 |                   |                 |                 |       |  |  |  |

|              | $\perp$ – Output Co                                                                                            | ompare 2 modu                                       |                 |                   |                 |                 |       |  |  |  |

|              | 0 = Output Co                                                                                                  | ompare 2 modul                                      | le is enabled   |                   |                 |                 |       |  |  |  |

| bit 0        |                                                                                                                | ompare 2 modul<br>put Compare 1                     |                 | e bit             |                 |                 |       |  |  |  |

| bit 0        | OC1MD: Out                                                                                                     | ompare 2 modul<br>put Compare 1 l<br>ompare 1 modul | Module Disable  | e bit             |                 |                 |       |  |  |  |

#### ~

| R/W-0                        | R/W-0                                                                                                                                                                  | R/W-0                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W-0                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                              |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          | IC2R<6:0>                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                     |

| ·                            |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 8                                                                                                                                                                                                                                                                                                                                                                                               |

| R/W-0                        | R/W-0                                                                                                                                                                  | R/W-0                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W-0                                                                                                                                                                                                                                                                                                                                                                                               |

|                              |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          | IC1R<6:0>                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                     |

|                              |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit C                                                                                                                                                                                                                                                                                                                                                                                               |

|                              |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                     |

| e bit                        | W = Writable b                                                                                                                                                         | it                                                                                                                                                                                                                                                                                                                                       | U = Unimplem                                                                                                                                                                                             | nented bit, rea                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | d as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                     |

| POR                          | '1' = Bit is set                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                          | '0' = Bit is clea                                                                                                                                                                                        | ared                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | x = Bit is unkr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | nown                                                                                                                                                                                                                                                                                                                                                                                                |

| •                            |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          | nbers)                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                     |

|                              |                                                                                                                                                                        | 1                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                     |

| Unimplemer                   | nted: Read as '0                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                     |

| (see Table 11<br>1111001 = I | I-2 for input pin's nput tied to RPI1                                                                                                                                  | election num<br>21                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                          | onding RPn Pi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | n bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                     |

|                              | e bit<br>POR<br>Unimplemen<br>IC2R<6:0>: /<br>(see Table 11<br>1111001 = I<br>0000001 = I<br>0000000 = I<br>Unimplemen<br>IC1R<6:0>: /<br>(see Table 11<br>1111001 = I | e bit W = Writable b<br>POR '1' = Bit is set<br>Unimplemented: Read as '0<br>IC2R<6:0>: Assign Input Cap<br>(see Table 11-2 for input pin s<br>1111001 = Input tied to RPI1<br>0000001 = Input tied to CMP<br>0000000 = Input tied to Vss<br>Unimplemented: Read as '0<br>IC1R<6:0>: Assign Input Cap<br>(see Table 11-2 for input pin s | e bit W = Writable bit<br>POR '1' = Bit is set<br>Unimplemented: Read as '0'<br>IC2R<6:0>: Assign Input Capture 2 (IC2)<br>(see Table 11-2 for input pin selection num<br>1111001 = Input tied to RPI121 | R/W-0       R/W-0       R/W-0       R/W-0         IC1R<6:0>       IC1R<6:0>         e bit       W = Writable bit       U = Unimplem         POR       '1' = Bit is set       '0' = Bit is clear         Unimplemented:       Read as '0'         IC2R<6:0>:       Assign Input Capture 2 (IC2) to the Correspond (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121         .         .         0000001 = Input tied to CMP1         0000000 = Input tied to Vss         Unimplemented:         Read as '0'         IC1R<6:0>:         Assign Input Capture 1 (IC1) to the Correspond (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         . | R/W-0       R/W-0       R/W-0       R/W-0         IC1R<6:0>         e bit       W = Writable bit       U = Unimplemented bit, real         POR       '1' = Bit is set       '0' = Bit is cleared         Unimplemented:       Read as '0'         IC2R<6:0>:       Assign Input Capture 2 (IC2) to the Corresponding RPn Pi (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121       .         .       .         0000001 = Input tied to CMP1         0000000 = Input tied to Vss         Unimplemented:         Read as '0'         IC1R<6:0>:         Assign Input Capture 1 (IC1) to the Corresponding RPn Pi (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         . | R/W-0       R/W-0       R/W-0       R/W-0       R/W-0         IC1R<6:0>    e bit W = Writable bit U = Unimplemented bit, read as '0' POR '1' = Bit is set '0' = Bit is cleared x = Bit is unkr Unimplemented: Read as '0' IC2R<6:0>: Assign Input Capture 2 (IC2) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) 1111001 = Input tied to RPI121 <p< td=""></p<> |

#### REGISTER 11-4: RPINR7: PERIPHERAL PIN SELECT INPUT REGISTER 7

| U-0          | R/W-0        | R/W-0                                                    | R/W-0         | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|--------------|--------------|----------------------------------------------------------|---------------|-------------------|-----------------|-----------------|-------|

| —            |              |                                                          |               | IC4R<6:0>         |                 |                 |       |

| bit 15       |              |                                                          |               |                   |                 |                 | bit 8 |

|              |              |                                                          |               |                   |                 |                 |       |

| U-0          | R/W-0        | R/W-0                                                    | R/W-0         | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

| —            |              |                                                          |               | IC3R<6:0>         |                 |                 |       |

| bit 7        |              |                                                          |               |                   |                 |                 | bit C |

|              |              |                                                          |               |                   |                 |                 |       |

| Legend:      |              |                                                          |               |                   |                 |                 |       |

| R = Readab   | ole bit      | W = Writable I                                           | bit           | U = Unimplem      | nented bit, rea | d as '0'        |       |

| -n = Value a | at POR       | '1' = Bit is set                                         |               | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

|              | 0000001 =    | nput tied to RPI<br>nput tied to CMI<br>nput tied to Vss | ⊃1            |                   |                 |                 |       |

| bit 7        | Unimpleme    | nted: Read as 'o                                         | )'            |                   |                 |                 |       |

| bit 6-0      | (see Table 1 | Assign Input Ca<br>1-2 for input pin<br>nput tied to RPI | selection nun |                   | onding RPn Pi   | n bits          |       |

### REGISTER 11-5: RPINR8: PERIPHERAL PIN SELECT INPUT REGISTER 8

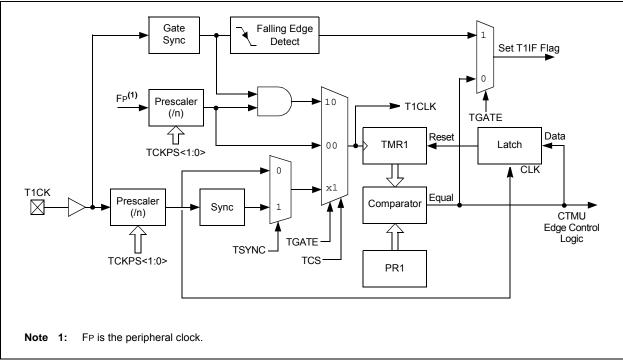

## 12.0 TIMER1

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Timer1 module is a 16-bit timer that can operate as a free-running interval timer/counter.

The Timer1 module has the following unique features over other timers:

- Can be operated in Asynchronous Counter mode from an external clock source

- The external clock input (T1CK) can optionally be synchronized to the internal device clock and the clock synchronization is performed after the prescaler

- A block diagram of Timer1 is shown in Figure 12-1.

The Timer1 module can operate in one of the following modes:

- Timer mode

- · Gated Timer mode

- Synchronous Counter mode

- · Asynchronous Counter mode

In Timer and Gated Timer modes, the input clock is derived from the internal instruction cycle clock (FCY). In Synchronous and Asynchronous Counter modes, the input clock is derived from the external clock input at the T1CK pin.

The Timer modes are determined by the following bits:

- Timer Clock Source Control bit (TCS): T1CON<1>

- Timer Synchronization Control bit (TSYNC): T1CON<2>

- Timer Gate Control bit (TGATE): T1CON<6>

Timer control bit setting for different operating modes are given in the Table 12-1.

| Mode                    | TCS | TGATE | TSYNC |  |  |  |  |

|-------------------------|-----|-------|-------|--|--|--|--|

| Timer                   | 0   | 0     | х     |  |  |  |  |

| Gated Timer             | 0   | 1     | x     |  |  |  |  |

| Synchronous<br>Counter  | 1   | х     | 1     |  |  |  |  |

| Asynchronous<br>Counter | 1   | x     | 0     |  |  |  |  |

#### TABLE 12-1: TIMER MODE SETTINGS

#### FIGURE 12-1: 16-BIT TIMER1 MODULE BLOCK DIAGRAM

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| RXOVF15 | RXOVF14 | RXOVF13 | RXOVF12 | RXOVF11 | RXOVF10 | RXOVF9 | RXOVF8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

|         |         |         |         |         |         |        |        |

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

#### REGISTER 21-24: CxRXOVF1: ECANx RECEIVE BUFFER OVERFLOW REGISTER 1

| RXOVF7  | RXOVF6                                                                | RXOVF5 | RXOVF4 | RXOVF3 | RXOVF2 | RXOVF1 | RXOVF0 |  |

|---------|-----------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|--|

| bit 7   |                                                                       |        |        |        |        |        | bit 0  |  |

|         |                                                                       |        |        |        |        |        |        |  |

| Legend: | egend: C = Writable bit, but only '0' can be written to clear the bit |        |        |        |        |        |        |  |

| Legend:           | C = Writable bit, but only '0' can be written to clear the bit |                             |                    |  |  |

|-------------------|----------------------------------------------------------------|-----------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                                               | U = Unimplemented bit, read | l as '0'           |  |  |

| -n = Value at POR | '1' = Bit is set                                               | '0' = Bit is cleared        | x = Bit is unknown |  |  |

bit 15-0 RXOVF<15:0>: Receive Buffer n Overflow bits

1 = Module attempted to write to a full buffer (set by module)

0 = No overflow condition (cleared by user software)

#### REGISTER 21-25: CxRXOVF2: ECANx RECEIVE BUFFER OVERFLOW REGISTER 2

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXOVF31 | RXOVF30 | RXOVF29 | RXOVF28 | RXOVF27 | RXOVF26 | RXOVF25 | RXOVF24 |

| bit 15  |         |         |         |         |         |         | bit 8   |

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXOVF23 | RXOVF22 | RXOVF21 | RXOVF20 | RXOVF19 | RXOVF18 | RXOVF17 | RXOVF16 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           | C = Writable bit, but or | C = Writable bit, but only '0' can be written to clear the bit |                                    |  |  |  |

|-------------------|--------------------------|----------------------------------------------------------------|------------------------------------|--|--|--|

| R = Readable bit  | W = Writable bit         | U = Unimplemented bit                                          | U = Unimplemented bit, read as '0' |  |  |  |

| -n = Value at POR | '1' = Bit is set         | '0' = Bit is cleared                                           | x = Bit is unknown                 |  |  |  |

bit 15-0 RXOVF<31:16>: Receive Buffer n Overflow bits

1 = Module attempted to write to a full buffer (set by module)

0 = No overflow condition (cleared by user software)

#### REGISTER 24-1: PTGCST: PTG CONTROL/STATUS REGISTER (CONTINUED)

- PTGITM<1:0>: PTG Input Trigger Command Operating Mode bits<sup>(1)</sup>

- 11 = Single level detect with Step delay not executed on exit of command (regardless of the PTGCTRL command)

- 10 = Single level detect with Step delay executed on exit of command

- 01 = Continuous edge detect with Step delay not executed on exit of command (regardless of the PTGCTRL command)

- 00 = Continuous edge detect with Step delay executed on exit of command

- Note 1: These bits apply to the PTGWHI and PTGWLO commands only.

bit 1-0

- **2:** This bit is only used with the PTGCTRL step command software trigger option.

- **3:** Use of the PTG Single-Step mode is reserved for debugging tools only.

| REGISTER      | 25-3: CM40                                              | CON: COMPA                             | RATOR 4 CO        | ONTROL RE        | GISTER             |                                            |                     |  |

|---------------|---------------------------------------------------------|----------------------------------------|-------------------|------------------|--------------------|--------------------------------------------|---------------------|--|

| R/W-0         | R/W-0                                                   | R/W-0                                  | U-0               | U-0              | U-0                | R/W-0                                      | R/W-0               |  |

| CON           | COE                                                     | CPOL                                   | —                 | —                | _                  | CEVT                                       | COUT                |  |

| bit 15        |                                                         |                                        |                   |                  |                    |                                            | bit 8               |  |

| R/W-0         | DAALO                                                   | U-0                                    |                   | U-0              | U-0                |                                            | R/W-0               |  |

|               | R/W-0                                                   | 0-0                                    | R/W-0             | 0-0              | 0-0                | R/W-0                                      |                     |  |

| EVPOL1        | EVPOL0                                                  | —                                      | CREF              | —                | _                  | CCH1 <sup>(1)</sup>                        | CCH0 <sup>(1)</sup> |  |

| bit 7         |                                                         |                                        |                   |                  |                    |                                            | bit (               |  |

| Legend:       |                                                         |                                        |                   |                  |                    |                                            |                     |  |

| R = Readable  | e bit                                                   | W = Writable                           | bit               | U = Unimple      | mented bit, rea    | d as '0'                                   |                     |  |

| -n = Value at |                                                         | '1' = Bit is se                        |                   | '0' = Bit is cle |                    | x = Bit is unkr                            | iown                |  |