Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                        |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 70 MIPs                                                                       |

| Connectivity               | I²C, IrDA, LINbus, QEI, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                 |

| Number of I/O              | 35                                                                            |

| Program Memory Size        | 32KB (10.7K x 24)                                                             |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 2K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 9x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 44-VFTLA Exposed Pad                                                          |

| Supplier Device Package    | 44-VTLA (6x6)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep32mc204-i-tl |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.6 CPU Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter |

|-------|--------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                            |

|       | http://www.microchip.com/wwwproducts/                                                |

|       | Devices.aspx?dDocName=en555464                                                       |

## 3.6.1 KEY RESOURCES

- "CPU" (DS70359) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

## 8.1 DMA Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

## 8.1.1 KEY RESOURCES

- Section 22. "Direct Memory Access (DMA)" (DS70348) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- · Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

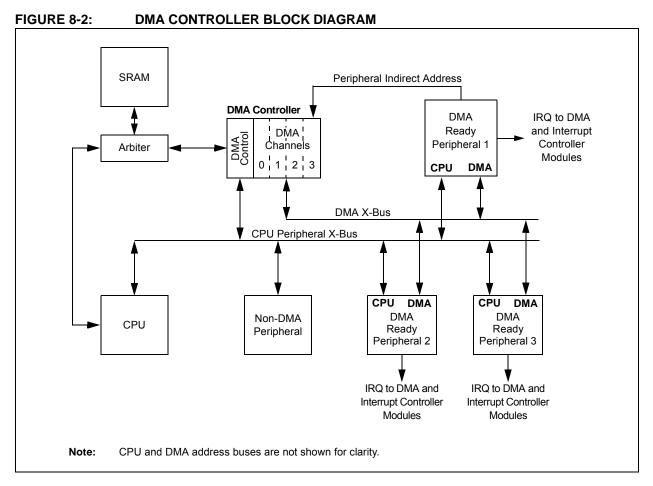

## 8.2 DMAC Registers

Each DMAC Channel x (where x = 0 through 3) contains the following registers:

- 16-Bit DMA Channel Control register (DMAxCON)

- 16-Bit DMA Channel IRQ Select register (DMAxREQ)

- 32-Bit DMA RAM Primary Start Address register (DMAxSTA)

- 32-Bit DMA RAM Secondary Start Address register (DMAxSTB)

- 16-Bit DMA Peripheral Address register (DMAxPAD)

- 14-Bit DMA Transfer Count register (DMAxCNT)

Additional status registers (DMAPWC, DMARQC, DMAPPS, DMALCA and DSADR) are common to all DMAC channels. These status registers provide information on write and request collisions, as well as on last address and channel access information.

The interrupt flags (DMAxIF) are located in an IFSx register in the interrupt controller. The corresponding interrupt enable control bits (DMAxIE) are located in an IECx register in the interrupt controller, and the corresponding interrupt priority control bits (DMAxIP) are located in an IPCx register in the interrupt controller.

## REGISTER 9-2: CLKDIV: CLOCK DIVISOR REGISTER (CONTINUED)

- **Note 1:** The DOZE<2:0> bits can only be written to when the DOZEN bit is clear. If DOZEN = 1, any writes to DOZE<2:0> are ignored.

- $\label{eq:constraint} \textbf{2:} \quad \text{This bit is cleared when the ROI bit is set and an interrupt occurs.}$

- **3:** The DOZEN bit cannot be set if DOZE<2:0> = 000. If DOZE<2:0> = 000, any attempt by user software to set the DOZEN bit is ignored.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| REGISTER     | REGISTER 10-5: PMD6: PERIPHERAL MODULE DISABLE CONTROL REGISTER 6 |                  |                           |                                    |                       |                       |                       |  |

|--------------|-------------------------------------------------------------------|------------------|---------------------------|------------------------------------|-----------------------|-----------------------|-----------------------|--|

| U-0          | U-0                                                               | U-0              | U-0                       | U-0                                | R/W-0                 | R/W-0                 | R/W-0                 |  |

| —            | —                                                                 | —                | —                         | —                                  | PWM3MD <sup>(1)</sup> | PWM2MD <sup>(1)</sup> | PWM1MD <sup>(1)</sup> |  |

| bit 15       |                                                                   |                  |                           |                                    |                       |                       | bit 8                 |  |

|              |                                                                   |                  |                           |                                    |                       |                       |                       |  |

| U-0          | U-0                                                               | U-0              | U-0                       | U-0                                | U-0                   | U-0                   | U-0                   |  |

|              |                                                                   |                  |                           |                                    |                       |                       |                       |  |

| bit 7        |                                                                   |                  |                           |                                    |                       |                       | bit 0                 |  |

|              |                                                                   |                  |                           |                                    |                       |                       |                       |  |

| Legend:      |                                                                   |                  |                           |                                    |                       |                       |                       |  |

| R = Readab   | le bit                                                            | W = Writable     | bit                       | U = Unimplemented bit, read as '0' |                       |                       |                       |  |

| -n = Value a | t POR                                                             | '1' = Bit is set |                           | '0' = Bit is clea                  | ared                  | x = Bit is unknown    |                       |  |

|              |                                                                   |                  |                           |                                    |                       |                       |                       |  |

| bit 15-11    | Unimplement                                                       | ted: Read as '   | כ'                        |                                    |                       |                       |                       |  |

| bit 10       | PWM3MD: P\                                                        | NM3 Module D     | isable bit <sup>(1)</sup> |                                    |                       |                       |                       |  |

|              | 1 = PWM3 mo                                                       | odule is disable | ed                        |                                    |                       |                       |                       |  |

|              | 0 = PWM3 mo                                                       | odule is enable  | d                         |                                    |                       |                       |                       |  |

| bit 9        | PWM2MD: P\                                                        | NM2 Module D     | isable bit <sup>(1)</sup> |                                    |                       |                       |                       |  |

|              | 1 = PWM2 mo                                                       | odule is disable | ed                        |                                    |                       |                       |                       |  |

|              | 0 = PWM2 mo                                                       | odule is enable  | d                         |                                    |                       |                       |                       |  |

| bit 8        | PWM1MD: P\                                                        | NM1 Module D     | isable bit <sup>(1)</sup> |                                    |                       |                       |                       |  |

|              |                                                                   | odule is disable |                           |                                    |                       |                       |                       |  |

|              | 0 = PWM1 mo                                                       | odule is enable  | d                         |                                    |                       |                       |                       |  |

| bit 7-0      | Unimplement                                                       | ted: Read as '   | כ'                        |                                    |                       |                       |                       |  |

## REGISTER 10-5: PMD6: PERIPHERAL MODULE DISABLE CONTROL REGISTER 6

Note 1: This bit is available on dsPIC33EPXXXMC50X/20X and PIC24EPXXXMC20X devices only.

## REGISTER 11-9: RPINR15: PERIPHERAL PIN SELECT INPUT REGISTER 15 (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

| U-0          | R/W-0        | R/W-0                                                  | R/W-0         | R/W-0            | R/W-0           | R/W-0           | R/W-0  |

|--------------|--------------|--------------------------------------------------------|---------------|------------------|-----------------|-----------------|--------|

| _            |              |                                                        |               | HOME1R<6:0       | >               |                 |        |

| bit 15       |              |                                                        |               |                  |                 |                 | bit 8  |

|              |              | <b>D</b> # 4 4 0                                       | 54446         | 5444.0           | 5444.0          |                 | 5444.6 |

| U-0          | R/W-0        | R/W-0                                                  | R/W-0         | R/W-0            | R/W-0           | R/W-0           | R/W-0  |

|              |              |                                                        |               | INDX1R<6:0>      | >               |                 |        |

| bit 7        |              |                                                        |               |                  |                 |                 | bit C  |

| Legend:      |              |                                                        |               |                  |                 |                 |        |

| R = Readab   | le bit       | W = Writable                                           | bit           | U = Unimplen     | nented bit, rea | ad as '0'       |        |

| -n = Value a | t POR        | '1' = Bit is set                                       |               | '0' = Bit is cle | ared            | x = Bit is unkr | nown   |

|              |              | nput tied to RPI                                       |               |                  |                 |                 |        |

|              |              | nput tied to CM<br>nput tied to Vss                    |               |                  |                 |                 |        |

| bit 7        |              | nted: Read as '                                        |               |                  |                 |                 |        |

| bit 6-0      | (see Table 1 | : Assign QEI1<br>1-2 for input pin<br>nput tied to RPI | selection nun | ,                | responding RI   | Pn Pin bits     |        |

|              |              | nput tied to CM                                        |               |                  |                 |                 |        |

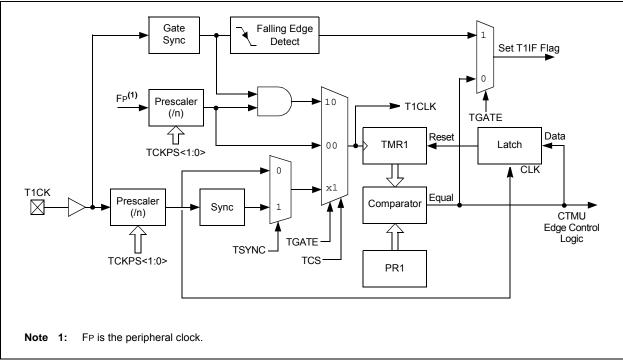

## 12.0 TIMER1

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Timer1 module is a 16-bit timer that can operate as a free-running interval timer/counter.

The Timer1 module has the following unique features over other timers:

- Can be operated in Asynchronous Counter mode from an external clock source

- The external clock input (T1CK) can optionally be synchronized to the internal device clock and the clock synchronization is performed after the prescaler

- A block diagram of Timer1 is shown in Figure 12-1.

The Timer1 module can operate in one of the following modes:

- Timer mode

- · Gated Timer mode

- Synchronous Counter mode

- · Asynchronous Counter mode

In Timer and Gated Timer modes, the input clock is derived from the internal instruction cycle clock (FCY). In Synchronous and Asynchronous Counter modes, the input clock is derived from the external clock input at the T1CK pin.

The Timer modes are determined by the following bits:

- Timer Clock Source Control bit (TCS): T1CON<1>

- Timer Synchronization Control bit (TSYNC): T1CON<2>

- Timer Gate Control bit (TGATE): T1CON<6>

Timer control bit setting for different operating modes are given in the Table 12-1.

| Mode                    | TCS | TGATE | TSYNC |

|-------------------------|-----|-------|-------|

| Timer                   | 0   | 0     | x     |

| Gated Timer             | 0   | 1     | x     |

| Synchronous<br>Counter  | 1   | х     | 1     |

| Asynchronous<br>Counter | 1   | x     | 0     |

#### TABLE 12-1: TIMER MODE SETTINGS

## FIGURE 12-1: 16-BIT TIMER1 MODULE BLOCK DIAGRAM

NOTES:

## 16.2 PWM Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

#### 16.2.1 KEY RESOURCES

- "High-Speed PWM" (DS70645) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

#### REGISTER 21-19: CxFMSKSEL2: ECANx FILTER 15-8 MASK SELECTION REGISTER 2

| R/W-0                                          | R/W-0                                                                                                                | R/W-0                                                                                                                 | R/W-0                                                                                                                                                | R/W-0                                                                                                                     | R/W-0                                                                   | R/W-0                        | R/W-0  |

|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|------------------------------|--------|

| F15MSK<1:0>                                    |                                                                                                                      | F14MS                                                                                                                 | F14MSK<1:0>                                                                                                                                          |                                                                                                                           | F13MSK<1:0>                                                             |                              | K<1:0> |

| bit 15                                         |                                                                                                                      |                                                                                                                       |                                                                                                                                                      |                                                                                                                           |                                                                         |                              | bit 8  |

|                                                |                                                                                                                      | 54446                                                                                                                 | 5444                                                                                                                                                 |                                                                                                                           |                                                                         | 5444.0                       |        |

| R/W-0                                          | R/W-0                                                                                                                | R/W-0                                                                                                                 | R/W-0                                                                                                                                                | R/W-0                                                                                                                     | R/W-0                                                                   | R/W-0                        | R/W-0  |

| F11M                                           | ISK<1:0>                                                                                                             | F10MS                                                                                                                 | K<1:0>                                                                                                                                               | F9MS                                                                                                                      | K<1:0>                                                                  | F8MSI                        | <<1:0> |

| bit 7                                          |                                                                                                                      |                                                                                                                       |                                                                                                                                                      |                                                                                                                           |                                                                         |                              | bit C  |

|                                                |                                                                                                                      |                                                                                                                       |                                                                                                                                                      |                                                                                                                           |                                                                         |                              |        |

| Legend:                                        |                                                                                                                      |                                                                                                                       |                                                                                                                                                      |                                                                                                                           |                                                                         |                              |        |

| R = Readable                                   | e bit                                                                                                                | W = Writable                                                                                                          | bit                                                                                                                                                  | U = Unimplem                                                                                                              | nented bit, read                                                        | l as '0'                     |        |

| -n = Value at                                  | POR                                                                                                                  | '1' = Bit is set                                                                                                      |                                                                                                                                                      | '0' = Bit is clea                                                                                                         | ared                                                                    | x = Bit is unkr              | nown   |

| bit 15 14                                      | ELEMOK A                                                                                                             | n. Maak Saura                                                                                                         | o for Filtor 15                                                                                                                                      | hita                                                                                                                      |                                                                         |                              |        |

|                                                | 11 = Reserv<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta                                                          | ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg                                                                 | gisters contair<br>gisters contair<br>gisters contair                                                                                                | n mask<br>n mask<br>n mask                                                                                                |                                                                         |                              |        |

|                                                | 11 = Reserv<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta                                                          | ed<br>ance Mask 2 reg<br>ance Mask 1 reg                                                                              | gisters contair<br>gisters contair<br>gisters contair                                                                                                | n mask<br>n mask<br>n mask                                                                                                | ies as bits<15:                                                         | 14>)                         |        |

| bit 13-12                                      | 11 = Reserv<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta<br>F14MSK<1:0                                            | ed<br>ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg                                                           | gisters contair<br>gisters contair<br>gisters contair<br>gisters contair<br>e for Filter 14                                                          | n mask<br>n mask<br>n mask<br>n mask<br>bits (same valu                                                                   |                                                                         |                              |        |

| bit 15-14<br>bit 13-12<br>bit 11-10<br>bit 9-8 | 11 = Reserve<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta<br>F14MSK<1:0<br>F13MSK<1:0                             | ed<br>ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg<br><b>0&gt;:</b> Mask Source                              | gisters contair<br>gisters contair<br>gisters contair<br>gisters contair<br>e for Filter 14<br>e for Filter 13                                       | n mask<br>n mask<br>n mask<br>n mask<br>bits (same valu<br>bits (same valu                                                | ies as bits<15:                                                         | 14>)                         |        |

| bit 13-12<br>bit 11-10                         | 11 = Reserv<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta<br>F14MSK<1:0<br>F13MSK<1:0<br>F12MSK<1:0                | ed<br>ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg<br><b>0&gt;:</b> Mask Source<br><b>0&gt;:</b> Mask Source | gisters contair<br>gisters contair<br>gisters contair<br>e for Filter 14<br>e for Filter 13<br>e for Filter 12                                       | n mask<br>n mask<br>n mask<br>bits (same valu<br>bits (same valu<br>bits (same valu                                       | ies as bits<15:<br>ies as bits<15:                                      | 14>)<br>14>)                 |        |

| bit 13-12<br>bit 11-10<br>bit 9-8              | 11 = Reserv<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta<br>F14MSK<1:0<br>F13MSK<1:0<br>F12MSK<1:0<br>F11MSK<1:0  | ed<br>ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg<br>0>: Mask Source<br>0>: Mask Source<br>0>: Mask Source  | gisters contair<br>gisters contair<br>gisters contair<br>e for Filter 14<br>e for Filter 13<br>e for Filter 12<br>e for Filter 11                    | n mask<br>n mask<br>n mask<br>bits (same valu<br>bits (same valu<br>bits (same valu<br>bits (same valu                    | ies as bits<15:<br>ies as bits<15:<br>es as bits<15:′                   | 14>)<br>14>)<br>14>)         |        |

| bit 13-12<br>bit 11-10<br>bit 9-8<br>bit 7-6   | 11 = Reserve<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta<br>F14MSK<1:0<br>F13MSK<1:0<br>F11MSK<1:0<br>F11MSK<1:0 | ed<br>ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg<br>0>: Mask Source<br>0>: Mask Source<br>0>: Mask Source  | gisters contair<br>gisters contair<br>gisters contair<br>e for Filter 14<br>e for Filter 13<br>e for Filter 12<br>e for Filter 11<br>e for Filter 10 | n mask<br>n mask<br>n mask<br>bits (same valu<br>bits (same valu<br>bits (same valu<br>bits (same valu<br>bits (same valu | ies as bits<15:<br>ies as bits<15:<br>es as bits<15:<br>ies as bits<15: | 14>)<br>14>)<br>14>)<br>14>) |        |

## 21.5 ECAN Message Buffers

ECAN Message Buffers are part of RAM memory. They are not ECAN Special Function Registers. The user application must directly write into the RAM area that is configured for ECAN Message Buffers. The location and size of the buffer area is defined by the user application.

#### BUFFER 21-1: ECAN™ MESSAGE BUFFER WORD 0

| U-0           | U-0                       | U-0               | R/W-x         | R/W-x                                  | R/W-x            | R/W-x    | R/W-x |  |

|---------------|---------------------------|-------------------|---------------|----------------------------------------|------------------|----------|-------|--|

|               | —                         | _                 | SID10         | SID9                                   | SID8             | SID7     | SID6  |  |

| bit 15        |                           |                   |               |                                        |                  |          | bit 8 |  |

| R/W-x         | R/W-x                     | R/W-x             | R/W-x         | R/W-x                                  | R/W-x            | R/W-x    | R/W-x |  |

| SID5          | SID4                      | SID3              | SID2          | SID1                                   | SID0             | SRR      | IDE   |  |

| bit 7         |                           |                   |               |                                        | •                |          | bit 0 |  |

| Legend:       |                           |                   |               |                                        |                  |          |       |  |

| R = Readabl   | e bit                     | W = Writable      | bit           | U = Unimpler                           | mented bit, read | l as '0' |       |  |

| -n = Value at | POR                       | '1' = Bit is set  |               | 0' = Bit is cleared x = Bit is unknown |                  |          |       |  |

|               |                           |                   |               |                                        |                  |          |       |  |

| bit 15-13     | Unimplemen                | ted: Read as '    | כי            |                                        |                  |          |       |  |

| bit 12-2      | <b>SID&lt;10:0&gt;:</b> S | Standard Identifi | ier bits      |                                        |                  |          |       |  |

| bit 1         | SRR: Substitu             | ute Remote Re     | quest bit     |                                        |                  |          |       |  |

|               | When IDE =                | 0:                |               |                                        |                  |          |       |  |

|               | 1 = Message               | will request rer  | note transmis | ssion                                  |                  |          |       |  |

|               | 0 = Normal m              | nessage           |               |                                        |                  |          |       |  |

|               | When IDE = 1              | <u>1:</u>         |               |                                        |                  |          |       |  |

|               | The SRR bit r             | must be set to '  | 1'.           |                                        |                  |          |       |  |

| bit 0         | IDE: Extende              | d Identifier bit  |               |                                        |                  |          |       |  |

|               | 1 = Message               | will transmit Ex  | tended Ident  | ifier                                  |                  |          |       |  |

|               | 0 = Message               | will transmit St  | andard Identi | fier                                   |                  |          |       |  |

|               |                           |                   |               |                                        |                  |          |       |  |

#### BUFFER 21-2: ECAN™ MESSAGE BUFFER WORD 1

| U-0             | U-0                               | U-0   | U-0   | R/W-x                                   | R/W-x | R/W-x | R/W-x |  |

|-----------------|-----------------------------------|-------|-------|-----------------------------------------|-------|-------|-------|--|

| —               | —                                 | —     | _     | EID17                                   | EID16 | EID15 | EID14 |  |

| bit 15          |                                   |       |       |                                         |       |       | bit 8 |  |

|                 |                                   |       |       |                                         |       |       |       |  |

| R/W-x           | R/W-x                             | R/W-x | R/W-x | R/W-x                                   | R/W-x | R/W-x | R/W-x |  |

| EID13           | EID12                             | EID11 | EID10 | EID9                                    | EID8  | EID7  | EID6  |  |

| bit 7           |                                   |       |       |                                         |       |       | bit 0 |  |

|                 |                                   |       |       |                                         |       |       |       |  |

| Legend:         |                                   |       |       |                                         |       |       |       |  |

| R = Readable    | ble bit W = Writable bit          |       |       | U = Unimplemented bit, read as '0'      |       |       |       |  |

| -n = Value at P | n = Value at POR '1' = Bit is set |       |       | '0' = Bit is cleared x = Bit is unknown |       |       |       |  |

|                 |                                   |       |       |                                         |       |       |       |  |

bit 15-12 Unimplemented: Read as '0'

bit 11-0 EID<17:6>: Extended Identifier bits

#### REGISTER 23-5: AD1CHS123: ADC1 INPUT CHANNEL 1, 2, 3 SELECT REGISTER (CONTINUED)

bit 0

**CH123SA:** Channel 1, 2, 3 Positive Input Select for Sample MUXA bit In 12-bit mode (AD21B = 1), CH123SA is Unimplemented and is Read as '0':

| Value          | ADC Channel |         |         |  |  |  |  |

|----------------|-------------|---------|---------|--|--|--|--|

| value          | CH1 CH2 CH3 |         |         |  |  |  |  |

| 1 <b>(2)</b>   | OA1/AN3     | OA2/AN0 | OA3/AN6 |  |  |  |  |

| 0 <b>(1,2)</b> | OA2/AN0     | AN1     | AN2     |  |  |  |  |

**Note 1:** AN0 through AN7 are repurposed when comparator and op amp functionality is enabled. See Figure 23-1 to determine how enabling a particular op amp or comparator affects selection choices for Channels 1, 2 and 3.

2: The OAx input is used if the corresponding op amp is selected (OPMODE (CMxCON<10>) = 1); otherwise, the ANx input is used.

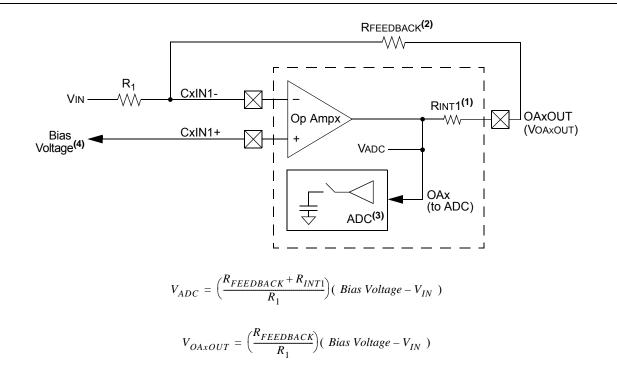

#### 25.1 Op Amp Application Considerations

There are two configurations to take into consideration when designing with the op amp modules that available in the dsPIC33EPXXXGP50X. are dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X devices. Configuration A (see Figure 25-6) takes advantage of the internal connection to the ADC module to route the output of the op amp directly to the ADC for measurement. Configuration B (see Figure 25-7) requires that the designer externally route the output of the op amp (OAxOUT) to a separate analog input pin (ANy) on the device. Table 30-55 in Section 30.0 "Electrical Characteristics" describes the performance characteristics for the op amps, distinguishing between the two configuration types where applicable.

#### 25.1.1 OP AMP CONFIGURATION A

Figure 25-6 shows a typical inverting amplifier circuit taking advantage of the internal connections from the op amp output to the input of the ADC. The advantage of this configuration is that the user does not need to consume another analog input (ANy) on the device, and allows the user to simultaneously sample all three op amps with the ADC module, if needed. However, the presence of the internal resistance, RINT1, adds an error in the feedback path. Since RINT1 is an internal resistance, in relation to the op amp output (VOAXOUT) and ADC internal connection (VADC), RINT1 must be included in the numerator term of the transfer function. See Table 30-53 in Section 30.0 "Electrical Characteristics" for the typical value of RINT1. Table 30-60 and Table 30-61 in Section 30.0 "Electrical Characteristics" describe the minimum sample time (TSAMP) requirements for the ADC module in this configuration. Figure 25-6 also defines the equations that should be used when calculating the expected voltages at points, VADC and VOAXOUT.

#### FIGURE 25-6: OP AMP CONFIGURATION A

Note 1: See Table 30-53 for the Typical value.

- 2: See Table 30-53 for the Minimum value for the feedback resistor.

- 3: See Table 30-60 and Table 30-61 for the minimum sample time (TSAMP).

- 4: CVREF10 or CVREF20 are two options that are available for supplying bias voltage to the op amps.

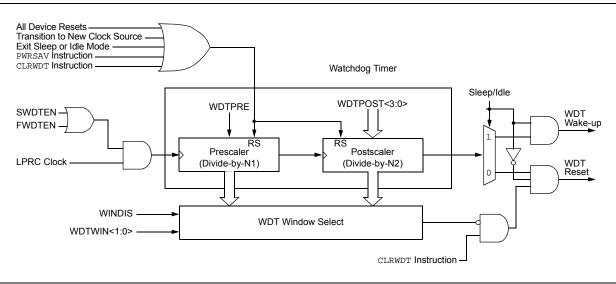

## 27.5 Watchdog Timer (WDT)

For dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices, the WDT is driven by the LPRC oscillator. When the WDT is enabled, the clock source is also enabled.

#### 27.5.1 PRESCALER/POSTSCALER

The nominal WDT clock source from LPRC is 32 kHz. This feeds a prescaler that can be configured for either 5-bit (divide-by-32) or 7-bit (divide-by-128) operation. The prescaler is set by the WDTPRE Configuration bit. With a 32 kHz input, the prescaler yields a WDT Timeout period (TWDT), as shown in Parameter SY12 in Table 30-22.

A variable postscaler divides down the WDT prescaler output and allows for a wide range of time-out periods. The postscaler is controlled by the WDTPOST<3:0> Configuration bits (FWDT<3:0>), which allow the selection of 16 settings, from 1:1 to 1:32,768. Using the prescaler and postscaler, time-out periods ranging from 1 ms to 131 seconds can be achieved.

The WDT, prescaler and postscaler are reset:

- · On any device Reset

- On the completion of a clock switch, whether invoked by software (i.e., setting the OSWEN bit after changing the NOSCx bits) or by hardware (i.e., Fail-Safe Clock Monitor)

- When a PWRSAV instruction is executed (i.e., Sleep or Idle mode is entered)

- When the device exits Sleep or Idle mode to resume normal operation

- By a CLRWDT instruction during normal execution

- Note: The CLRWDT and PWRSAV instructions clear the prescaler and postscaler counts when executed.

## FIGURE 27-2: WDT BLOCK DIAGRAM

## 27.5.2 SLEEP AND IDLE MODES

If the WDT is enabled, it continues to run during Sleep or Idle modes. When the WDT time-out occurs, the device wakes the device and code execution continues from where the PWRSAV instruction was executed. The corresponding SLEEP or IDLE bit (RCON<3,2>) needs to be cleared in software after the device wakes up.

## 27.5.3 ENABLING WDT

The WDT is enabled or disabled by the FWDTEN Configuration bit in the FWDT Configuration register. When the FWDTEN Configuration bit is set, the WDT is always enabled.

The WDT can be optionally controlled in software when the FWDTEN Configuration bit has been programmed to '0'. The WDT is enabled in software by setting the SWDTEN control bit (RCON<5>). The SWDTEN control bit is cleared on any device Reset. The software WDT option allows the user application to enable the WDT for critical code segments and disable the WDT during non-critical segments for maximum power savings.

The WDT flag bit, WDTO (RCON<4>), is not automatically cleared following a WDT time-out. To detect subsequent WDT events, the flag must be cleared in software.

#### 27.5.4 WDT WINDOW

The Watchdog Timer has an optional Windowed mode, enabled by programming the WINDIS bit in the WDT Configuration register (FWDT<6>). In the Windowed mode (WINDIS = 0), the WDT should be cleared based on the settings in the programmable Watchdog Timer Window select bits (WDTWIN<1:0>).

| DC CHARACTER  | ISTICS |      | (unless otherw | perature $-40^{\circ}C \le TA \le +8$ |       |  |

|---------------|--------|------|----------------|---------------------------------------|-------|--|

| Parameter No. | Тур.   | Max. | Units          | Conditions                            |       |  |

| DC61d         | 8      |      | μΑ             | -40°C                                 |       |  |

| DC61a         | 10     | —    | μA             | +25°C                                 | 2.21/ |  |

| DC61b         | 12     | —    | μA             | +85°C                                 | 3.3V  |  |

| DC61c         | 13     | —    | μA             | +125°C                                |       |  |

## TABLE 30-9: DC CHARACTERISTICS: WATCHDOG TIMER DELTA CURRENT ( $\Delta$ Iwdt)<sup>(1)</sup>

**Note 1:** The  $\triangle$ IwDT current is the additional current consumed when the module is enabled. This current should be added to the base IPD current. All parameters are characterized but not tested during manufacturing.

#### TABLE 30-10: DC CHARACTERISTICS: DOZE CURRENT (IDOZE)

| DC CHARACTER                        | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |      |               |       |            |      |                |

|-------------------------------------|-------------------------------------------------------|------|---------------|-------|------------|------|----------------|

| Parameter No.                       | Тур.                                                  | Max. | Doze<br>Ratio | Units | Conditions |      |                |

| Doze Current (IDOZE) <sup>(1)</sup> |                                                       |      |               |       |            |      |                |

| DC73a <sup>(2)</sup>                | 35                                                    |      | 1:2           | mA    | -40°C      | 3.3V | Fosc = 140 MHz |

| DC73g                               | 20                                                    | 30   | 1:128         | mA    |            |      |                |

| DC70a <sup>(2)</sup>                | 35                                                    | _    | 1:2           | mA    | 12500      | 3.3V | Fosc = 140 MHz |

| DC70g                               | 20                                                    | 30   | 1:128         | mA    | +25°C      |      |                |

| DC71a <sup>(2)</sup>                | 35                                                    | —    | 1:2           | mA    | .05%0      | 3.3V | Fosc = 140 MHz |

| DC71g                               | 20                                                    | 30   | 1:128         | mA    | +85°C      |      |                |

| DC72a <sup>(2)</sup>                | 28                                                    | —    | 1:2           | mA    | +125°C     | 3.3V | Fosc = 120 MHz |

| DC72g                               | 15                                                    | 30   | 1:128         | mA    | +125 C     |      |                |

**Note 1:** IDOZE is primarily a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDOZE measurements are as follows:

- Oscillator is configured in EC mode and external clock is active, OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)</li>

- CLKO is configured as an I/O input pin in the Configuration Word

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- CPU, SRAM, program memory and data memory are operational

- No peripheral modules are operating; however, every peripheral is being clocked (all PMDx bits are zeroed)

- CPU is executing while(1) statement

- · JTAG is disabled

- 2: Parameter is characterized but not tested in manufacturing.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

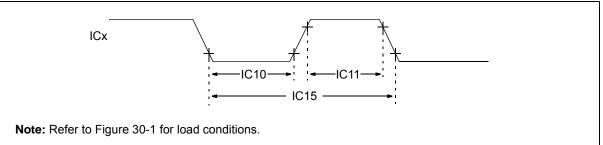

## FIGURE 30-6: INPUT CAPTURE x (ICx) TIMING CHARACTERISTICS

#### TABLE 30-26: INPUT CAPTURE x MODULE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                                                |      |       |                                  |                                  |

|--------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|------|-------|----------------------------------|----------------------------------|

| Param.<br>No.      | Symbol | Characteristics <sup>(1)</sup>                                                                                                                                                                                                                                                          | Min.                                           | Max. | Units | Conditions                       |                                  |

| IC10               | TccL   | ICx Input Low Time                                                                                                                                                                                                                                                                      | Greater of<br>12.5 + 25 or<br>(0.5 Tcy/N) + 25 |      | ns    | Must also meet<br>Parameter IC15 |                                  |

| IC11               | ТссН   | ICx Input High Time                                                                                                                                                                                                                                                                     | Greater of<br>12.5 + 25 or<br>(0.5 Tcy/N) + 25 | —    | ns    | Must also meet<br>Parameter IC15 | N = prescale value<br>(1, 4, 16) |

| IC15               | TccP   | ICx Input Period                                                                                                                                                                                                                                                                        | Greater of<br>25 + 50<br>or<br>(1 Tcy/N) + 50  | _    | ns    |                                  |                                  |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

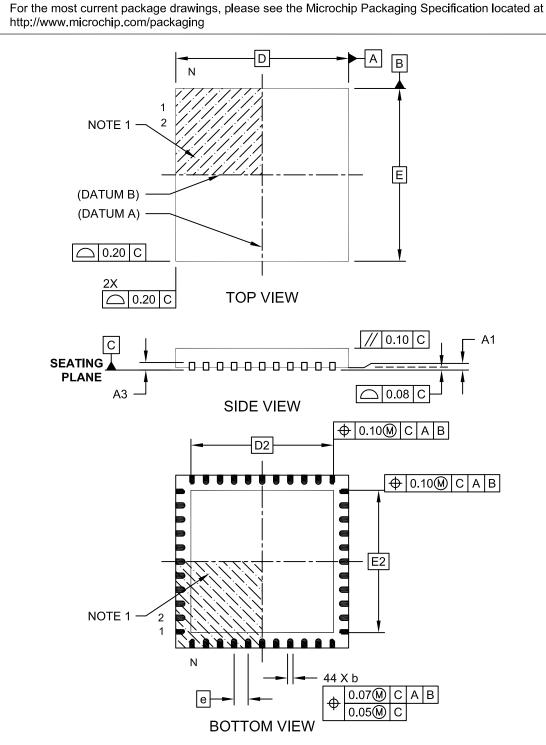

## 44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN]

Note:

Microchip Technology Drawing C04-103C Sheet 1 of 2

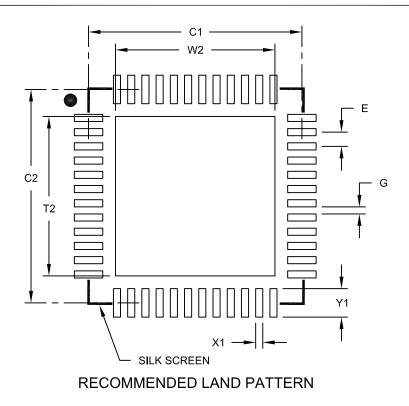

48-Lead Ultra Thin Plastic Quad Flat, No Lead Package (MV) - 6x6 mm Body [UQFN] With 0.40 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | MILLIMETERS |          |      |      |  |

|----------------------------|-------------|----------|------|------|--|

| Dimension Limits           |             | MIN      | NOM  | MAX  |  |

| Contact Pitch              | E           | 0.40 BSC |      |      |  |

| Optional Center Pad Width  | W2          |          |      | 4.45 |  |

| Optional Center Pad Length | T2          |          |      | 4.45 |  |

| Contact Pad Spacing        | C1          |          | 6.00 |      |  |

| Contact Pad Spacing        | C2          |          | 6.00 |      |  |

| Contact Pad Width (X28)    | X1          |          |      | 0.20 |  |

| Contact Pad Length (X28)   | Y1          |          |      | 0.80 |  |

| Distance Between Pads      | G           | 0.20     |      |      |  |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2153A

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV == ISO/TS 16949 ==

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, FlashFlex, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MTP, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

Analog-for-the-Digital Age, Application Maestro, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, SQI, Serial Quad I/O, Total Endurance, TSHARC, UniWinDriver, WiperLock, ZENA and Z-Scale are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

GestIC and ULPP are registered trademarks of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2011-2013, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

ISBN: 9781620773949

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEEL0Q® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and mulfacture of development systems is ISO 9001:2000 certified.