Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 60 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                  |

| Number of I/O              | 35                                                                             |

| Program Memory Size        | 32KB (10.7K x 24)                                                              |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 2K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 9x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 44-QFN (8x8)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep32mc204t-e-ml |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

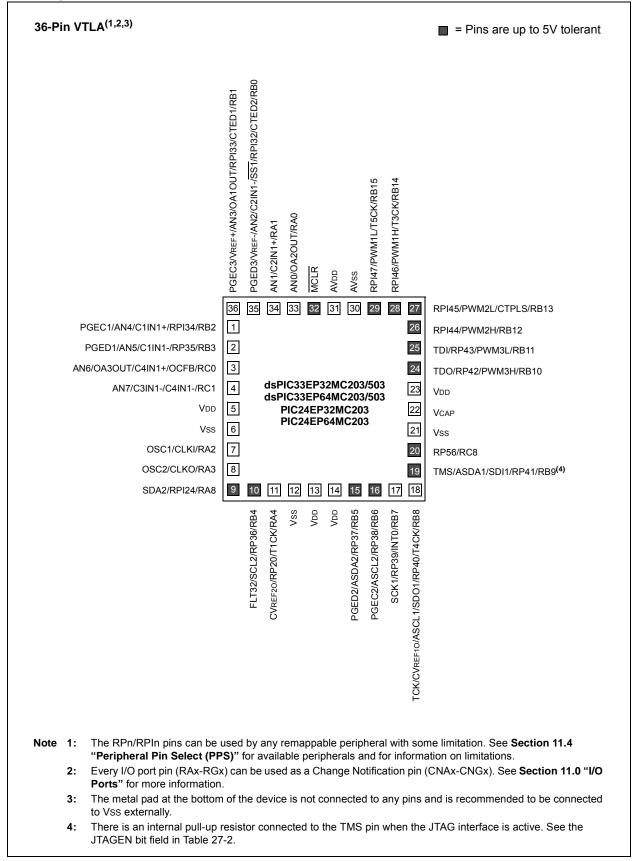

# Pin Diagrams (Continued)

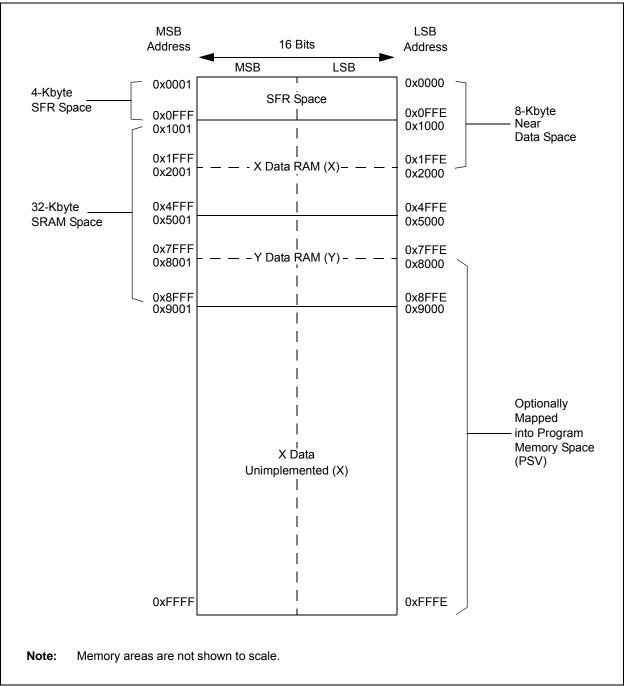

# 4.2 Data Address Space

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X CPU has a separate 16-bit-wide data memory space. The Data Space is accessed using separate Address Generation Units (AGUs) for read and write operations. The data memory maps, which are presented by device family and memory size, are shown in Figure 4-7 through Figure 4-16.

All Effective Addresses (EAs) in the data memory space are 16 bits wide and point to bytes within the Data Space. This arrangement gives a base Data Space address range of 64 Kbytes (32K words).

The base Data Space address is used in conjunction with a Read or Write Page register (DSRPAG or DSWPAG) to form an Extended Data Space, which has a total address range of 16 Mbytes.

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices implement up to 52 Kbytes of data memory (4 Kbytes of data memory for Special Function Registers and up to 48 Kbytes of data memory for RAM). If an EA points to a location outside of this area, an all-zero word or byte is returned.

# 4.2.1 DATA SPACE WIDTH

The data memory space is organized in byteaddressable, 16-bit-wide blocks. Data is aligned in data memory and registers as 16-bit words, but all Data Space EAs resolve to bytes. The Least Significant Bytes (LSBs) of each word have even addresses, while the Most Significant Bytes (MSBs) have odd addresses.

#### 4.2.2 DATA MEMORY ORGANIZATION AND ALIGNMENT

To maintain backward compatibility with PIC<sup>®</sup> MCU devices and improve Data Space memory usage efficiency, the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X instruction set supports both word and byte operations. As a consequence of byte accessibility, all Effective Address calculations are internally scaled to step through word-aligned memory. For example, the core recognizes that Post-Modified Register Indirect Addressing mode [Ws++] results in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

A data byte read, reads the complete word that contains the byte, using the LSb of any EA to determine which byte to select. The selected byte is placed onto the LSB of the data path. That is, data memory and registers are organized as two parallel, byte-wide entities with shared (word) address decode but separate write lines. Data byte writes only write to the corresponding side of the array or register that matches the byte address. All word accesses must be aligned to an even address. Misaligned word data fetches are not supported, so care must be taken when mixing byte and word operations, or translating from 8-bit MCU code. If a misaligned read or write is attempted, an address error trap is generated. If the error occurred on a read, the instruction underway is completed. If the error occurred on a write, the instruction is executed but the write does not occur. In either case, a trap is then executed, allowing the system and/or user application to examine the machine state prior to execution of the address Fault.

All byte loads into any W register are loaded into the LSB. The MSB is not modified.

A Sign-Extend (SE) instruction is provided to allow user applications to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, user applications can clear the MSB of any W register by executing a Zero-Extend (ZE) instruction on the appropriate address.

# 4.2.3 SFR SPACE

The first 4 Kbytes of the Near Data Space, from 0x0000 to 0x0FFF, is primarily occupied by Special Function Registers (SFRs). These are used by the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X core and peripheral modules for controlling the operation of the device.

SFRs are distributed among the modules that they control and are generally grouped together by module. Much of the SFR space contains unused addresses; these are read as '0'.

**Note:** The actual set of peripheral features and interrupts varies by the device. Refer to the corresponding device tables and pinout diagrams for device-specific information.

# 4.2.4 NEAR DATA SPACE

The 8-Kbyte area, between 0x0000 and 0x1FFF, is referred to as the Near Data Space. Locations in this space are directly addressable through a 13-bit absolute address field within all memory direct instructions. Additionally, the whole Data Space is addressable using MOV instructions, which support Memory Direct Addressing mode with a 16-bit address field, or by using Indirect Addressing mode using a working register as an Address Pointer.

# FIGURE 4-10: DATA MEMORY MAP FOR dsPIC33EP256MC20X/50X AND dsPIC33EP256GP50X DEVICES

# TABLE 4-17: I2C1 AND I2C2 REGISTER MAP

| File<br>Name | Addr. | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9                    | Bit 8                      | Bit 7 | Bit 6 | Bit 5     | Bit 4        | Bit 3        | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|---------|--------|---------|--------|--------|--------|--------------------------|----------------------------|-------|-------|-----------|--------------|--------------|-------|-------|-------|---------------|

| I2C1RCV      | 0200  | —       | —      | —       | —      | —      | —      | —                        | – – I2C1 Receive Register  |       |       |           |              |              |       | 0000  |       |               |

| I2C1TRN      | 0202  | _       | _      | _       | _      | —      | _      | —                        | – – I2C1 Transmit Register |       |       |           |              |              |       | OOFF  |       |               |

| I2C1BRG      | 0204  | _       | _      | _       | _      | _      | _      | _                        | - Baud Rate Generator      |       |       |           |              |              |       | 0000  |       |               |

| I2C1CON      | 0206  | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW                   | SMEN                       | GCEN  | STREN | ACKDT     | ACKEN        | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C1STAT     | 0208  | ACKSTAT | TRSTAT | _       | _      | _      | BCL    | GCSTAT                   | ADD10                      | IWCOL | I2COV | D_A       | Р            | S            | R_W   | RBF   | TBF   | 0000          |

| I2C1ADD      | 020A  | _       | _      | _       | _      | _      | _      |                          |                            |       |       | I2C1 Addr | ess Register | r            |       |       |       | 0000          |

| I2C1MSK      | 020C  | _       | _      | _       | _      | _      | _      |                          |                            |       |       | I2C1 Add  | dress Mask   |              |       |       |       | 0000          |

| I2C2RCV      | 0210  | _       | _      | _       | _      | _      | _      | _                        | _                          |       |       |           | I2C2 Recei   | ve Register  |       |       |       | 0000          |

| I2C2TRN      | 0212  | _       | _      | _       | _      | _      | _      | _                        | _                          |       |       |           | I2C2 Transi  | mit Register |       |       |       | OOFF          |

| I2C2BRG      | 0214  | _       | _      | _       | _      | _      | _      | _                        |                            |       |       | Bau       | d Rate Gene  | erator       |       |       |       | 0000          |

| I2C2CON      | 0216  | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW                   | SMEN                       | GCEN  | STREN | ACKDT     | ACKEN        | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C2STAT     | 0218  | ACKSTAT | TRSTAT | _       | _      | —      | BCL    | GCSTAT                   | ADD10                      | IWCOL | I2COV | D_A       | Р            | S            | R_W   | RBF   | TBF   | 0000          |

| I2C2ADD      | 021A  | _       | _      | _       | _      | —      | _      | I2C2 Address Register 00 |                            |       |       |           |              | 0000         |       |       |       |               |

| I2C2MSK      | 021C  | _       | _      | _       | _      | _      | -      | - I2C2 Address Mask 00   |                            |       |       |           |              | 0000         |       |       |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-18: UART1 AND UART2 REGISTER MAP

| SFR<br>Name | Addr. | Bit 15   | Bit 14 | Bit 13                      | Bit 12 | Bit 11 | Bit 10                        | Bit 9 | Bit 8    | Bit 7      | Bit 6    | Bit 5 | Bit 4      | Bit 3    | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|-------------|-------|----------|--------|-----------------------------|--------|--------|-------------------------------|-------|----------|------------|----------|-------|------------|----------|-------|--------|-------|---------------|

| U1MODE      | 0220  | UARTEN   | —      | USIDL                       | IREN   | RTSMD  | _                             | UEN<  | :1:0>    | WAKE       | LPBACK   | ABAUD | URXINV     | BRGH     | PDSE  | L<1:0> | STSEL | 0000          |

| U1STA       | 0222  | UTXISEL1 | UTXINV | UTXISEL0                    | _      | UTXBRK | UTXEN                         | UTXBF | TRMT     | URXIS      | SEL<1:0> | ADDEN | RIDLE      | PERR     | FERR  | OERR   | URXDA | 0110          |

| U1TXREG     | 0224  | _        | _      | _                           | _      | _      | _                             | _     |          |            |          | UART1 | Transmit F | Register |       |        |       | xxxx          |

| U1RXREG     | 0226  | _        | _      | _                           | _      | _      | _                             | _     |          |            |          | UART  | Receive R  | legister |       |        |       | 0000          |

| U1BRG       | 0228  |          |        |                             |        |        | Baud Rate Generator Prescaler |       |          |            |          |       | 0000       |          |       |        |       |               |

| U2MODE      | 0230  | UARTEN   | _      | USIDL                       | IREN   | RTSMD  | _                             | UEN<  | :1:0>    | WAKE       | LPBACK   | ABAUD | URXINV     | BRGH     | PDSE  | L<1:0> | STSEL | 0000          |

| U2STA       | 0232  | UTXISEL1 | UTXINV | UTXISEL0                    | _      | UTXBRK | UTXEN                         | UTXBF | TRMT     | URXIS      | SEL<1:0> | ADDEN | RIDLE      | PERR     | FERR  | OERR   | URXDA | 0110          |

| U2TXREG     | 0234  | _        | _      | _                           | _      | _      | _                             | _     |          |            |          | UART2 | Transmit F | Register |       |        |       | xxxx          |

| U2RXREG     | 0236  | _        | _      | UART2 Receive Register 0000 |        |        |                               |       |          |            | 0000     |       |            |          |       |        |       |               |

| U2BRG       | 0238  |          |        |                             |        |        |                               | Baud  | Rate Gen | erator Pre | scaler   |       |            |          |       |        |       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| TABLE 4 | 4-31: | PER | IPHERA | L PIN S | ELECT | INPUT F | REGISTI | ER MAP | FOR ds | sPIC33E | EPXXXG | P50X D | EVICES | SONLY |  |

|---------|-------|-----|--------|---------|-------|---------|---------|--------|--------|---------|--------|--------|--------|-------|--|

|         |       |     |        |         |       |         |         |        |        |         |        |        |        |       |  |

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13       | Bit 12 | Bit 11     | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6      | Bit 5 | Bit 4      | Bit 3     | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------------|--------|------------|--------|-------|-------|-------|------------|-------|------------|-----------|-------|-------|-------|---------------|

| RPINR0       | 06A0  | —      |        |              |        | INT1R<6:0> |        |       |       | _     |            |       |            |           |       |       | _     | 0000          |

| RPINR1       | 06A2  |        | _      | _            | _      | _          | _      | _     | _     | _     | INT2R<6:0> |       |            |           |       |       |       | 0000          |

| RPINR3       | 06A6  |        | _      |              |        |            |        |       | _     | _     |            |       | ٦          | [2CKR<6:0 | >     |       |       | 0000          |

| RPINR7       | 06AE  |        |        |              |        | IC2R<6:0>  |        |       |       | _     |            |       |            | IC1R<6:0> |       |       |       | 0000          |

| RPINR8       | 06B0  |        |        | IC4R<6:0>    |        |            |        |       |       | _     | IC3R<6:0>  |       |            |           |       |       |       | 0000          |

| RPINR11      | 06B6  |        | _      | _            | _      | _          | _      | _     | _     | _     | OCFAR<6:0> |       |            |           |       |       |       | 0000          |

| RPINR18      | 06C4  |        | _      | _            | _      | _          | _      | _     | _     | _     | U1RXR<6:0> |       |            |           |       |       |       | 0000          |

| RPINR19      | 06C6  |        | _      | _            | _      | _          | _      | _     | _     | _     |            |       | ι          | J2RXR<6:0 | >     |       |       | 0000          |

| RPINR22      | 06CC  |        |        | SCK2INR<6:0> |        |            |        |       | _     |       |            | :     | SDI2R<6:0> | •         |       |       | 0000  |               |

| RPINR23      | 06CE  | _      | _      |              |        |            |        | —     | —     |       |            |       | SS2R<6:0>  |           |       |       | 0000  |               |

| RPINR26      | 06D4  | —      | _      | _            | -      | _          | _      | —     |       | —     |            |       | (          | C1RXR<6:0 | >     |       |       | 0000          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### **TABLE 4-32:** PERIPHERAL PIN SELECT INPUT REGISTER MAP FOR dsPIC33EPXXXMC50X DEVICES ONLY

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13       | Bit 12 | Bit 11     | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6      | Bit 5 | Bit 4 | Bit 3      | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------|--------|--------|--------------|--------|------------|--------|-------|-------|-------|------------|-------|-------|------------|-------|-------|-------|---------------|

| RPINR0    | 06A0  | _      |        |              |        | INT1R<6:0> |        |       |       | —     |            |       |       |            |       |       | _     | 0000          |

| RPINR1    | 06A2  |        | _      | _            | _      | _          | _      | _     | _     | _     | INT2R<6:0> |       |       |            |       |       | 0000  |               |

| RPINR3    | 06A6  |        | _      | _            | _      | _          | _      | _     | _     | _     | T2CKR<6:0> |       |       |            |       |       | 0000  |               |

| RPINR7    | 06AE  |        |        |              |        | IC2R<6:0>  |        |       |       | _     |            |       |       | IC1R<6:0>  |       |       |       | 0000          |

| RPINR8    | 06B0  |        |        | IC4R<6:0>    |        |            |        |       |       | _     |            |       |       | IC3R<6:0>  |       |       |       | 0000          |

| RPINR11   | 06B6  |        | _      |              |        |            |        |       | _     | _     |            |       | (     | DCFAR<6:0  | >     |       |       | 0000          |

| RPINR12   | 06B8  |        |        | FLT2R<6:0>   |        |            |        |       |       | _     | FLT1R<6:0> |       |       |            |       |       | 0000  |               |

| RPINR14   | 06BC  |        |        |              | (      | QEB1R<6:0  | >      |       |       | _     |            |       | (     | QEA1R<6:0  | >     |       |       | 0000          |

| RPINR15   | 06BE  |        |        |              | Н      | OME1R<6:0  | )>     |       |       | _     |            |       | I     | NDX1R<6:0  | >     |       |       | 0000          |

| RPINR18   | 06C4  |        | _      | _            | _      | _          | _      | _     | _     | _     | U1RXR<6:0> |       |       |            |       |       | 0000  |               |

| RPINR19   | 06C6  |        | _      | _            | _      | _          | _      | _     | _     | _     |            |       | ι     | J2RXR<6:0  | >     |       |       | 0000          |

| RPINR22   | 06CC  | _      |        |              | S      | CK2INR<6:( | )>     |       |       | —     |            |       |       | SDI2R<6:0> | •     |       |       | 0000          |

| RPINR23   | 06CE  | _      | —      | —            |        | —          | —      |       | —     | —     |            |       |       | SS2R<6:0>  |       |       |       | 0000          |

| RPINR26   | 06D4  | _      | —      |              |        |            |        |       | —     | —     |            |       | (     | C1RXR<6:0  | >     |       |       | 0000          |

| RPINR37   | 06EA  | _      |        | SYNCI1R<6:0> |        |            |        |       |       | —     | —          | —     | —     | —          |       |       |       | 0000          |

| RPINR38   | 06EC  | _      |        | DTCMP1R<6:0> |        |            |        |       |       | —     | —          | —     | —     | _          |       |       |       | 0000          |

| RPINR39   | 06EE  | _      |        | DTCMP3R<6:0> |        |            |        |       |       | _     |            |       | D     | CMP2R<6:   | 0>    |       |       | 0000          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

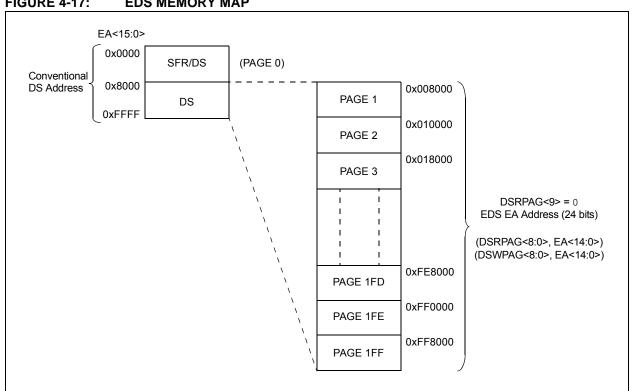

#### 4.4.2 EXTENDED X DATA SPACE

The lower portion of the base address space range, between 0x0000 and 0x7FFF, is always accessible regardless of the contents of the Data Space Page registers. It is indirectly addressable through the register indirect instructions. It can be regarded as being located in the default EDS Page 0 (i.e., EDS address range of 0x000000 to 0x007FFF with the base address bit, EA<15> = 0, for this address range). However, Page 0 cannot be accessed through the upper 32 Kbytes, 0x8000 to 0xFFFF, of base Data Space, in combination with DSRPAG = 0x000 or DSWPAG = 0x000. Consequently, DSRPAG and DSWPAG are initialized to 0x001 at Reset.

- Note 1: DSxPAG should not be used to access Page 0. An EDS access with DSxPAG set to 0x000 will generate an address error trap.

- 2: Clearing the DSxPAG in software has no effect.

The remaining pages, including both EDS and PSV pages, are only accessible using the DSRPAG or DSWPAG registers in combination with the upper 32 Kbytes, 0x8000 to 0xFFFF, of the base address, where base address bit, EA<15> = 1.

For example, when DSRPAG = 0x001 or DSWPAG = 0x001, accesses to the upper 32 Kbytes, 0x8000 to 0xFFFF, of the Data Space will map to the EDS address range of 0x008000 to 0x00FFFF. When DSRPAG = 0x002 or DSWPAG = 0x002, accesses to the upper 32 Kbytes of the Data Space will map to the EDS address range of 0x010000 to 0x017FFF and so on, as shown in the EDS memory map in Figure 4-17.

For more information on the PSV page access using Data Space Page registers, refer to the "**Program Space Visibility from Data Space**" section in "**Program Memory**" (DS70613) of the "*dsPIC33/ PIC24 Family Reference Manual*".

#### FIGURE 4-17: EDS MEMORY MAP

| R/W-0                | R/W-0                   | R/W-0                | R/W-0 | R/C-0 | R/C-0 | R-0   | R/W-0 |

|----------------------|-------------------------|----------------------|-------|-------|-------|-------|-------|

| OA                   | OB                      | SA                   | SB    | OAB   | SAB   | DA    | DC    |

| bit 15               |                         |                      |       |       |       |       | bit 8 |

|                      |                         |                      |       |       |       |       |       |

| R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup>    | R/W-0 <sup>(3)</sup> | R-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|                      | IPL<2:0> <sup>(2)</sup> |                      | RA    | Ν     | OV    | Z     | С     |

| bit 7                |                         |                      |       |       |       |       | bit 0 |

|                      |                         |                      |       |       |       |       |       |

# REGISTER 7-1: SR: CPU STATUS REGISTER<sup>(1)</sup>

| Legend:           | C = Clearable bit |                       |                    |

|-------------------|-------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1'= Bit is set   | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7-5 | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2,3)</sup>        |

|---------|----------------------------------------------------------------------------|

|         | 111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled |

|         | 110 = CPU Interrupt Priority Level is 6 (14)                               |

|         | 101 = CPU Interrupt Priority Level is 5 (13)                               |

|         | 100 = CPU Interrupt Priority Level is 4 (12)                               |

|         | 011 = CPU Interrupt Priority Level is 3 (11)                               |

|         | 010 = CPU Interrupt Priority Level is 2 (10)                               |

|         | 001 = CPU Interrupt Priority Level is 1 (9)                                |

|         | 000 = CPU Interrupt Priority Level is 0 (8)                                |

- **Note 1:** For complete register details, see Register 3-1.

- 2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL, if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- **3:** The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0    | U-0 | U-0 | U-0 | U-0   | U-0   | U-0   | U-0   |

|--------|-----|-----|-----|-------|-------|-------|-------|

| _      |     |     |     | _     | —     |       | —     |

| bit 15 |     |     |     |       |       |       | bit 8 |

|        |     |     |     |       |       |       |       |

| U-0    | U-0 | U-0 | U-0 | R-0   | R-0   | R-0   | R-0   |

| —      | —   | —   | _   | PPST3 | PPST2 | PPST1 | PPST0 |

| bit 7  |     |     |     |       |       |       | bit 0 |

#### REGISTER 8-14: DMAPPS: DMA PING-PONG STATUS REGISTER

| Legend:      |         |                                                                                       |                       |                    |  |  |  |  |

|--------------|---------|---------------------------------------------------------------------------------------|-----------------------|--------------------|--|--|--|--|

| R = Readat   | ole bit | W = Writable bit                                                                      | U = Unimplemented bit | , read as '0'      |  |  |  |  |

| -n = Value a | at POR  | '1' = Bit is set                                                                      | '0' = Bit is cleared  | x = Bit is unknown |  |  |  |  |

| bit 15 1     | Unimplo | mented: Read as '0'                                                                   |                       |                    |  |  |  |  |

| •            |         | DMA Channel 3 Ping-Pong I                                                             | Modo Status Elag bit  |                    |  |  |  |  |

| 1 = DMA      |         | ASTB3 register is selected<br>ASTA3 register is selected                              | vioue Status Flag bit |                    |  |  |  |  |

| bit 2        | 1 = DMA | DMA Channel 2 Ping-Pong I<br>ASTB2 register is selected<br>ASTA2 register is selected | Mode Status Flag bit  |                    |  |  |  |  |

| bit 1        | PPST1:  | MA Channel 1 Ping-Pong Mode Status Flag bit                                           |                       |                    |  |  |  |  |

|              |         | CTD1 register is calested                                                             |                       |                    |  |  |  |  |

- 1 = DMASTB1 register is selected0 = DMASTA1 register is selected

- bit 0 PPST0: DMA Channel 0 Ping-Pong Mode Status Flag bit

- 1 = DMASTB0 register is selected

- 0 = DMASTA0 register is selected

- g) The TRISx registers control only the digital I/O output buffer. Any other dedicated or remappable active "output" will automatically override the TRIS setting. The TRISx register does not control the digital logic "input" buffer. Remappable digital "inputs" do not automatically override TRIS settings, which means that the TRISx bit must be set to input for pins with only remappable input function(s) assigned

- h) All analog pins are enabled by default after any Reset and the corresponding digital input buffer on the pin has been disabled. Only the Analog Pin Select registers control the digital input buffer, *not* the TRISx register. The user must disable the analog function on a pin using the Analog Pin Select registers in order to use any "digital input(s)" on a corresponding pin, no exceptions.

## 11.6 I/O Ports Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

#### 11.6.1 KEY RESOURCES

- "I/O Ports" (DS70598) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

| R/W-0                          | U-0                                                                       | U-0                                                                                                                        | U-0                                                              | U-0                  | U-0               | R/W-0              | R/W-0   |

|--------------------------------|---------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|----------------------|-------------------|--------------------|---------|

| CHPCLKEN                       | —                                                                         | —                                                                                                                          | —                                                                | —                    | —                 | CHOPC              | LK<9:8> |

| bit 15                         |                                                                           |                                                                                                                            |                                                                  |                      |                   |                    | bit 8   |

|                                |                                                                           |                                                                                                                            |                                                                  |                      |                   |                    |         |

| R/W-0                          | R/W-0                                                                     | R/W-0                                                                                                                      | R/W-0                                                            | R/W-0                | R/W-0             | R/W-0              | R/W-0   |

|                                |                                                                           |                                                                                                                            | CHOPC                                                            | LK<7:0>              |                   |                    |         |

| bit 7                          |                                                                           |                                                                                                                            |                                                                  |                      |                   |                    | bit 0   |

|                                |                                                                           |                                                                                                                            |                                                                  |                      |                   |                    |         |

| Legend:                        |                                                                           |                                                                                                                            |                                                                  |                      |                   |                    |         |

| R = Readable I                 | bit                                                                       | W = Writable                                                                                                               | bit                                                              | U = Unimplei         | mented bit, read  | as '0'             |         |

| -n = Value at P                | OR                                                                        | '1' = Bit is set                                                                                                           |                                                                  | '0' = Bit is cleared |                   | x = Bit is unknown |         |

| bit 15<br>bit 14-10<br>bit 9-0 | 1 = Chop cloo<br>0 = Chop cloo<br>Unimplemen<br>CHOPCLK<9<br>The frequenc | Enable Chop<br>ck generator is<br>ck generator is<br>ted: Read as '<br>):0>: Chop Clo<br>y of the chop c<br>ncy = (FP/PCL) | enabled<br>disabled<br>0'<br>ck Divider bits<br>lock signal is g | given by the fo      | ollowing expressi | on:                |         |

# REGISTER 16-5: CHOP: PWMx CHOP CLOCK GENERATOR REGISTER

#### REGISTER 16-6: MDC: PWMx MASTER DUTY CYCLE REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

|                 |       |                  | MDC   | <15:8>           |                 |                 |       |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

|                 |       |                  |       |                  |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | MD    | C<7:0>           |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

|                 |       |                  |       |                  |                 |                 |       |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable    | bit   | W = Writable b   | bit   | U = Unimpler     | mented bit, rea | ad as '0'       |       |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

bit 15-0 MDC<15:0>: PWMx Master Duty Cycle Value bits

| REGISTE    | R 16-7: PWMC                            | CONX: PWMX (                                                                           | CONTROL R               | EGISTER          |                      |                      |                     |

|------------|-----------------------------------------|----------------------------------------------------------------------------------------|-------------------------|------------------|----------------------|----------------------|---------------------|

| HS/HC-     | 0 HS/HC-0                               | HS/HC-0                                                                                | R/W-0                   | R/W-0            | R/W-0                | R/W-0                | R/W-0               |

| FLTSTAT    | -(1) CLSTAT <sup>(1)</sup>              | TRGSTAT                                                                                | FLTIEN                  | CLIEN            | TRGIEN               | ITB <sup>(2)</sup>   | MDCS <sup>(2)</sup> |

| bit 15     | ·                                       |                                                                                        |                         | ÷                |                      |                      | bit                 |

| R/W-0      | R/W-0                                   | R/W-0                                                                                  | U-0                     | R/W-0            | R/W-0                | R/W-0                | R/W-0               |

| DTC1       | DTC0                                    | DTCP <sup>(3)</sup>                                                                    | 0-0                     | MTBS             | CAM <sup>(2,4)</sup> | XPRES <sup>(5)</sup> | IUE <sup>(2)</sup>  |

| bit 7      | БТСО                                    | DIGLO                                                                                  |                         | INT DO           | CANIC                | XI KLOV              | bit                 |

|            |                                         |                                                                                        |                         |                  |                      |                      |                     |

| Legend:    |                                         | HC = Hardware                                                                          | Clearable bit           | HS = Hardwa      | are Settable bit     |                      |                     |

| R = Reada  | able bit                                | W = Writable bi                                                                        | t                       | U = Unimple      | mented bit, rea      | id as '0'            |                     |

| -n = Value | at POR                                  | '1' = Bit is set                                                                       |                         | '0' = Bit is cle | eared                | x = Bit is unk       | nown                |

| bit 15     | ELTSTAT: Ea                             | ult Interrupt Statu                                                                    | us hit(1)               |                  |                      |                      |                     |

| bit 15     |                                         | rrupt is pending                                                                       |                         |                  |                      |                      |                     |

|            | 0 = No Fault                            | interrupt is pendi                                                                     |                         |                  |                      |                      |                     |

|            |                                         | ared by setting F                                                                      |                         |                  |                      |                      |                     |

| bit 14     |                                         | rent-Limit Interru                                                                     | •                       |                  |                      |                      |                     |

|            |                                         | 1 = Current-limit interrupt is pending                                                 |                         |                  |                      |                      |                     |

|            |                                         | 0 = No current-limit interrupt is pending<br>This bit is cleared by setting CLIEN = 0. |                         |                  |                      |                      |                     |

| bit 13     |                                         | igger Interrupt S                                                                      |                         |                  |                      |                      |                     |

|            |                                         | terrupt is pending                                                                     |                         |                  |                      |                      |                     |

|            |                                         | r interrupt is pene<br>ared by setting T                                               |                         |                  |                      |                      |                     |

| bit 12     |                                         | t Interrupt Enabl                                                                      |                         |                  |                      |                      |                     |

|            |                                         | rrupt is enabled                                                                       |                         |                  |                      |                      |                     |

|            |                                         | rrupt is disabled                                                                      | and the FLTS            | TAT bit is clear | ed                   |                      |                     |

| bit 11     | CLIEN: Curre                            | ent-Limit Interrup                                                                     | t Enable bit            |                  |                      |                      |                     |

|            |                                         | mit interrupt is er                                                                    |                         |                  |                      |                      |                     |

| bit 10     |                                         | mit interrupt is di<br>Iger Interrupt Ena                                              |                         |                  | scieared             |                      |                     |

|            | -                                       | event generates                                                                        |                         | auest            |                      |                      |                     |

|            |                                         | vent interrupts ar                                                                     |                         |                  | T bit is cleared     |                      |                     |

| bit 9      | ITB: Indepen                            | dent Time Base                                                                         | Mode bit <sup>(2)</sup> |                  |                      |                      |                     |

|            |                                         | register provides<br>egister provides f                                                | •                       |                  | •                    |                      |                     |

| bit 8      |                                         | er Duty Cycle Re                                                                       |                         |                  |                      |                      |                     |

|            |                                         | ster provides du                                                                       | •                       |                  | WM generator         |                      |                     |

|            |                                         | ister provides du                                                                      |                         |                  |                      | r                    |                     |

| Note 1:    | Software must clea                      | ar the interrupt st                                                                    | atus here and           | in the corresp   | onding IFSx bit      | in the interrup      | t controller.       |

| 2:         | These bits should                       | not be changed                                                                         | after the PWM           | x is enabled (F  | PTEN = 1).           |                      |                     |

| 3:         | DTC<1:0> = 11 fo                        |                                                                                        |                         | •                |                      |                      |                     |

| 4:         | The Independent T<br>CAM bit is ignored | •                                                                                      | 1) mode mus             | t be enabled to  | o use Center-Al      | igned mode. If       | ITB = 0, the        |

| 5:         | To operate in Exte                      |                                                                                        | t mode, the IT          | B bit must be '  | 1' and the CLM       | 10D bit in the I     | FCLCONx             |

# REGISTER 16-7: PWMCONx: PWMx CONTROL REGISTER

5: To operate in External Period Reset mode, the ITB bit must be '1' and the CLMOD bit in the FCLCONx register must be '0'.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-0      | U-0                                                        | U-0                                                             | R/W-0                           | R/W-0                 | R/W-0                    | R/W-0                 | R/W-0                 |

|------------|------------------------------------------------------------|-----------------------------------------------------------------|---------------------------------|-----------------------|--------------------------|-----------------------|-----------------------|

| CH0NB      |                                                            | _                                                               | CH0SB4 <sup>(1)</sup>           | CH0SB3 <sup>(1)</sup> | CH0SB2 <sup>(1)</sup>    | CH0SB1 <sup>(1)</sup> | CH0SB0 <sup>(1)</sup> |

| bit 15     |                                                            | -                                                               |                                 |                       |                          |                       | bit 8                 |

|            |                                                            |                                                                 |                                 |                       |                          |                       |                       |

| R/W-0      | U-0                                                        | U-0                                                             | R/W-0                           | R/W-0                 | R/W-0                    | R/W-0                 | R/W-0                 |

| CH0NA      |                                                            | _                                                               | CH0SA4 <sup>(1)</sup>           | CH0SA3 <sup>(1)</sup> | CH0SA2 <sup>(1)</sup>    | CH0SA1 <sup>(1)</sup> | CH0SA0 <sup>(1)</sup> |

| bit 7      |                                                            |                                                                 |                                 |                       |                          |                       | bit C                 |

|            |                                                            |                                                                 |                                 |                       |                          |                       |                       |

| Legend:    |                                                            |                                                                 |                                 |                       |                          |                       |                       |

| R = Reada  |                                                            | W = Writable                                                    |                                 |                       | nented bit, read         |                       |                       |

| -n = Value | e at POR                                                   | '1' = Bit is set                                                |                                 | '0' = Bit is clea     | ared                     | x = Bit is unkn       | own                   |

| hit 15     |                                                            | annal O Nagativa                                                | Input Coloct for                | r Comple MUX          |                          |                       |                       |

| bit 15     |                                                            | nannel 0 Negative<br>el 0 negative input                        |                                 |                       |                          |                       |                       |

|            |                                                            | el 0 negative input                                             |                                 |                       |                          |                       |                       |

| bit 14-13  | Unimpleme                                                  | ented: Read as '0                                               | )'                              |                       |                          |                       |                       |

| bit 12-8   | CH0SB<4:0                                                  | 0>: Channel 0 Po:                                               | sitive Input Sele               | ect for Sample I      | MUXB bits <sup>(1)</sup> |                       |                       |

|            |                                                            | pen; use this sele                                              |                                 |                       |                          | ement                 |                       |

|            | 11110 <b>= Ch</b>                                          | nannel 0 positive in                                            | put is connected                | to the CTMU te        | mperature meas           | surement diode        | (CTMU TEMP            |

|            | 11101 <b>= R</b> e                                         |                                                                 |                                 |                       |                          |                       |                       |

|            | 11100 <b>= Re</b><br>11011 <b>= Re</b>                     |                                                                 |                                 |                       |                          |                       |                       |

|            |                                                            | nannel 0 positive i                                             | input is the outp               | out of OA3/AN6        | (2,3)                    |                       |                       |

|            |                                                            | nannel 0 positive i                                             |                                 |                       |                          |                       |                       |

|            |                                                            | nannel 0 positive i                                             | input is the outp               | out of OA1/AN3        | (2)                      |                       |                       |

|            | 10111 <b>= Re</b>                                          | served                                                          |                                 |                       |                          |                       |                       |

|            | •                                                          |                                                                 |                                 |                       |                          |                       |                       |

|            | •                                                          |                                                                 |                                 |                       |                          |                       |                       |

|            | 10000 <b>= Re</b>                                          |                                                                 |                                 |                       |                          |                       |                       |

|            | 01111 = Ch                                                 | nannel 0 positive i                                             | input is AN15 <sup>(3)</sup>    |                       |                          |                       |                       |

|            | 01110 = Cr                                                 | nannel 0 positive i<br>nannel 0 positive i                      | input is AN14 <sup>(3)</sup>    |                       |                          |                       |                       |

|            | •                                                          |                                                                 |                                 |                       |                          |                       |                       |

|            | •                                                          |                                                                 |                                 |                       |                          |                       |                       |

|            | •                                                          |                                                                 | (2)                             |                       |                          |                       |                       |

|            | 00010 = Ch                                                 | nannel 0 positive i<br>nannel 0 positive i                      | input is AN2 <sup>(3)</sup>     |                       |                          |                       |                       |

|            |                                                            | nannel 0 positive i                                             |                                 |                       |                          |                       |                       |

| bit 7      |                                                            | •                                                               | •                               | r Samnle MI IX        | Δ hit                    |                       |                       |

|            | CHONA: Channel 0 Negative Input Select for Sample MUXA bit |                                                                 |                                 |                       |                          |                       |                       |

|            | 1 = Channell                                               | 1 0 negative input                                              | is AN1(1)                       |                       |                          |                       |                       |

|            |                                                            | el 0 negative input<br>el 0 negative input                      |                                 |                       |                          |                       |                       |

| bit 6-5    | 0 = Channe                                                 | el 0 negative input<br>el 0 negative input<br>ented: Read as '0 | is Vrefl                        |                       |                          |                       |                       |

|            | 0 = Channe<br>Unimpleme<br>AN0 through A                   | el 0 negative input                                             | is VREFL<br>,'<br>ed when compa |                       |                          |                       |                       |

#### REGISTER 23-6: AD1CHS0: ADC1 INPUT CHANNEL 0 SELECT REGISTER

3: See the "**Pin Diagrams**" section for the available analog channels for each device.

otherwise, the ANx input is used.

#### REGISTER 24-1: PTGCST: PTG CONTROL/STATUS REGISTER (CONTINUED)

- PTGITM<1:0>: PTG Input Trigger Command Operating Mode bits<sup>(1)</sup>

- 11 = Single level detect with Step delay not executed on exit of command (regardless of the PTGCTRL command)

- 10 = Single level detect with Step delay executed on exit of command

- 01 = Continuous edge detect with Step delay not executed on exit of command (regardless of the PTGCTRL command)

- 00 = Continuous edge detect with Step delay executed on exit of command

- Note 1: These bits apply to the PTGWHI and PTGWLO commands only.

bit 1-0

- **2:** This bit is only used with the PTGCTRL step command software trigger option.

- **3:** Use of the PTG Single-Step mode is reserved for debugging tools only.

#### REGISTER 25-3: CM4CON: COMPARATOR 4 CONTROL REGISTER (CONTINUED)

- bit 5 Unimplemented: Read as '0'

- bit 4 **CREF:** Comparator Reference Select bit (VIN+ input)<sup>(1)</sup>

- 1 = VIN+ input connects to internal CVREFIN voltage

- 0 = VIN+ input connects to C4IN1+ pin

- bit 3-2 Unimplemented: Read as '0'

- bit 1-0 CCH<1:0>: Comparator Channel Select bits<sup>(1)</sup>

- 11 = VIN- input of comparator connects to OA3/AN6

- 10 = VIN- input of comparator connects to OA2/AN0

- 01 = VIN- input of comparator connects to OA1/AN3

- 00 = VIN- input of comparator connects to C4IN1-

- Note 1: Inputs that are selected and not available will be tied to Vss. See the "Pin Diagrams" section for available inputs for each package.

# 29.11 Demonstration/Development Boards, Evaluation Kits and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

# 29.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

#### TABLE 30-18: PLL CLOCK TIMING SPECIFICATIONS

| AC CHARACTERISTICS |        |                                                                  | (unless | d Operati<br>otherwis | <b>e stated)</b><br>ature -4 | 0°C ≤ TA | <b>.0V to 3.6V</b><br>A $\leq$ +85°C for Industrial<br>A $\leq$ +125°C for Extended |

|--------------------|--------|------------------------------------------------------------------|---------|-----------------------|------------------------------|----------|-------------------------------------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic                                                   | Min.    | Typ. <sup>(1)</sup>   | Max.                         | Units    | Conditions                                                                          |

| OS50               | Fplli  | PLL Voltage Controlled Oscillator<br>(VCO) Input Frequency Range | 0.8     | —                     | 8.0                          | MHz      | ECPLL, XTPLL modes                                                                  |

| OS51               | Fvco   | On-Chip VCO System Frequency                                     | 120     | —                     | 340                          | MHz      |                                                                                     |

| OS52               | TLOCK  | PLL Start-up Time (Lock Time)                                    | 0.9     | 1.5                   | 3.1                          | ms       |                                                                                     |

| OS53               | DCLK   | CLKO Stability (Jitter) <sup>(2)</sup>                           | -3      | 0.5                   | 3                            | %        |                                                                                     |

**Note 1:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: This jitter specification is based on clock cycle-by-clock cycle measurements. To get the effective jitter for individual time bases, or communication clocks used by the application, use the following formula:

$$Effective Jitter = \frac{DCLK}{\sqrt{\frac{FOSC}{Time Base or Communication Clock}}}$$

For example, if Fosc = 120 MHz and the SPIx bit rate = 10 MHz, the effective jitter is as follows:

Effective Jitter =

$$\frac{DCLK}{\sqrt{\frac{120}{10}}} = \frac{DCLK}{\sqrt{12}} = \frac{DCLK}{3.464}$$

#### TABLE 30-19: INTERNAL FRC ACCURACY

| AC CHARACTERISTICS Standard Operating Operating temperature |                                                                 |      |      | ture -40° | $^{\circ}C \le TA \le -$ | to 3.6V (unless otherw<br>⊦85°C for Industrial<br>⊦125°C for Extended | vise stated)   |  |

|-------------------------------------------------------------|-----------------------------------------------------------------|------|------|-----------|--------------------------|-----------------------------------------------------------------------|----------------|--|

| Param<br>No.                                                | Characteristic                                                  | Min. | Тур. | Max.      | Units                    | Conditions                                                            |                |  |

| Internal                                                    | Internal FRC Accuracy @ FRC Frequency = 7.37 MHz <sup>(1)</sup> |      |      |           |                          |                                                                       |                |  |

| F20a                                                        | FRC                                                             | -1.5 | 0.5  | +1.5      | %                        | $-40^{\circ}C \le TA \le -10^{\circ}C$                                | VDD = 3.0-3.6V |  |

|                                                             |                                                                 | -1   | 0.5  | +1        | %                        | $-10^{\circ}C \le TA \le +85^{\circ}C$                                | VDD = 3.0-3.6V |  |

| F20b                                                        | FRC                                                             | -2   | 1    | +2        | %                        | $+85^{\circ}C \le TA \le +125^{\circ}C$                               | VDD = 3.0-3.6V |  |

Note 1: Frequency is calibrated at +25°C and 3.3V. TUNx bits can be used to compensate for temperature drift.

#### TABLE 30-20: INTERNAL LPRC ACCURACY

| AC CH        | ARACTERISTICS               |      | l <b>Operating</b><br>g temperati | ure -40° | $C \le TA \le +$ | to 3.6V (unless otherw<br>85°C for Industrial<br>125°C for Extended | ise stated)    |  |

|--------------|-----------------------------|------|-----------------------------------|----------|------------------|---------------------------------------------------------------------|----------------|--|

| Param<br>No. | Characteristic              | Min. | Тур.                              | Max.     | Units            | Conditions                                                          |                |  |

| LPRC (       | @ 32.768 kHz <sup>(1)</sup> |      |                                   |          |                  |                                                                     |                |  |

| F21a         | LPRC                        | -30  | —                                 | +30      | %                | $-40^\circ C \le T A \le -10^\circ C$                               | VDD = 3.0-3.6V |  |

|              |                             | -20  |                                   | +20      | %                | $-10^{\circ}C \leq TA \leq +85^{\circ}C$                            | VDD = 3.0-3.6V |  |

| F21b         | LPRC                        | -30  | _                                 | +30      | %                | $+85^{\circ}C \leq TA \leq +125^{\circ}C$                           | VDD = 3.0-3.6V |  |

**Note 1:** The change of LPRC frequency as VDD changes.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

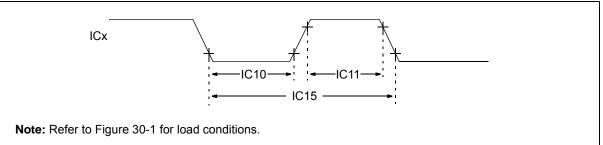

#### FIGURE 30-6: INPUT CAPTURE x (ICx) TIMING CHARACTERISTICS

#### TABLE 30-26: INPUT CAPTURE x MODULE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                | Standard Operati<br>(unless otherwise<br>Operating tempera | e stated | )<br>∙40°C ≤ <sup>-</sup> | <b>3.0V to 3.6V</b><br>「A ≤ +85°C for Indu<br>「A ≤ +125°C for Ext |                                  |  |

|--------------------|--------|--------------------------------|------------------------------------------------------------|----------|---------------------------|-------------------------------------------------------------------|----------------------------------|--|

| Param.<br>No.      | Symbol | Characteristics <sup>(1)</sup> | Min.                                                       | Max.     | Units                     | Conditions                                                        |                                  |  |

| IC10               | TccL   | ICx Input Low Time             | Greater of<br>12.5 + 25 or<br>(0.5 Tcy/N) + 25             |          | ns                        | Must also meet<br>Parameter IC15                                  |                                  |  |

| IC11               | ТссН   | ICx Input High Time            | Greater of<br>12.5 + 25 or<br>(0.5 Tcy/N) + 25             | —        | ns                        | Must also meet<br>Parameter IC15                                  | N = prescale value<br>(1, 4, 16) |  |

| IC15               | TccP   | ICx Input Period               | Greater of<br>25 + 50<br>or<br>(1 Tcy/N) + 50              | _        | ns                        |                                                                   |                                  |  |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

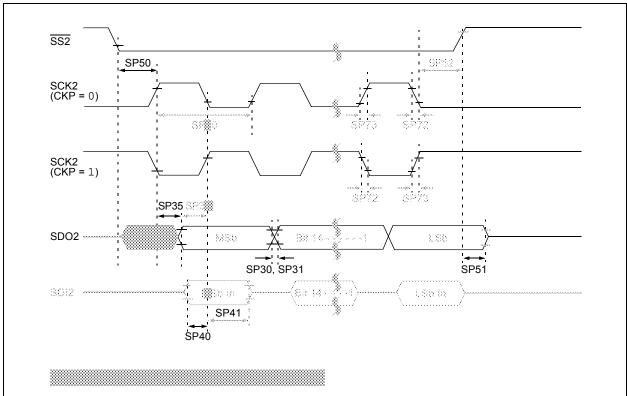

#### FIGURE 30-20: SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0) TIMING CHARACTERISTICS

# APPENDIX A: REVISION HISTORY

# **Revision A (April 2011)**

This is the initial released version of the document.

# Revision B (July 2011)

This revision includes minor typographical and formatting changes throughout the data sheet text.

All other major changes are referenced by their respective section in Table A-1.

#### TABLE A-1: MAJOR SECTION UPDATES

| Section Name                                                                     | Update Description                                                                                                                                                                                                                                                                                                      |

|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "High-Performance, 16-bit<br>Digital Signal Controllers<br>and Microcontrollers" | Changed all pin diagrams references of VLAP to TLA.                                                                                                                                                                                                                                                                     |

| Section 4.0 "Memory<br>Organization"                                             | Updated the All Resets values for CLKDIV and PLLFBD in the System Control Register Map (see Table 4-35).                                                                                                                                                                                                                |

| Section 5.0 "Flash Program<br>Memory"                                            | Updated "one word" to "two words" in the first paragraph of <b>Section 5.2 "RTSP Operation"</b> .                                                                                                                                                                                                                       |

| Section 9.0 "Oscillator<br>Configuration"                                        | Updated the PLL Block Diagram (see Figure 9-2).<br>Updated the Oscillator Mode, Fast RC Oscillator (FRC) with divide-by-N and PLL<br>(FRCPLL), by changing (FRCDIVN + PLL) to (FRCPLL).                                                                                                                                 |

|                                                                                  | Changed (FRCDIVN + PLL) to (FRCPLL) for COSC<2:0> = 001 and NOSC<2:0> = 001 in the Oscillator Control Register (see Register 9-1).                                                                                                                                                                                      |

|                                                                                  | Changed the POR value from 0 to 1 for the DOZE<1:0> bits, from 1 to 0 for the FRCDIV<0> bit, and from 0 to 1 for the PLLPOST<0> bit; Updated the default definitions for the DOZE<2:0> and FRCDIV<2:0> bits and updated all bit definitions for the PLLPOST<1:0> bits in the Clock Divisor Register (see Register 9-2). |

|                                                                                  | Changed the POR value from 0 to 1 for the PLLDIV<5:4> bits and updated the default definitions for all PLLDIV<8:0> bits in the PLL Feedback Division Register (see Register 9-2).                                                                                                                                       |

| Section 22.0 "Charge Time<br>Measurement Unit (CTMU)"                            | Updated the bit definitions for the IRNG<1:0> bits in the CTMU Current Control Register (see Register 22-3).                                                                                                                                                                                                            |

| Section 25.0 "Op amp/<br>Comparator Module"                                      | Updated the voltage reference block diagrams (see Figure 25-1 and Figure 25-2).                                                                                                                                                                                                                                         |

# Revision E (April 2012)

This revision includes typographical and formatting changes throughout the data sheet text.

All other major changes are referenced by their respective section in Table A-3.

| TABLE A-4: | MAJOR SECTION UPDATES |

|------------|-----------------------|

|------------|-----------------------|

| Section Name                                   | Update Description                                                                              |

|------------------------------------------------|-------------------------------------------------------------------------------------------------|

| "16-bit Microcontrollers<br>and Digital Signal | The following 512-Kbyte devices were added to the General Purpose Families table (see Table 1): |

| Controllers (up to                             | <ul> <li>PIC24EP512GP202</li> </ul>                                                             |

| 512-Kbyte Flash and                            | • PIC24EP512GP204                                                                               |

| 48-Kbyte SRAM) with High-                      | • PIC24EP512GP206                                                                               |

| Speed PWM, Op amps, and Advanced Analog"       | • dsPIC33EP512GP502                                                                             |

| Advanced Analog                                | • dsPIC33EP512GP504                                                                             |

|                                                | • dsPIC33EP512GP506                                                                             |

|                                                | The following 512-Kbyte devices were added to the Motor Control Families table (see Table 2):   |

|                                                | • PIC24EP512MC202                                                                               |

|                                                | • PIC24EP512MC204                                                                               |