Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 70 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                  |

| Number of I/O              | 35                                                                             |

| Program Memory Size        | 32KB (10.7K x 24)                                                              |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 2K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 9x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

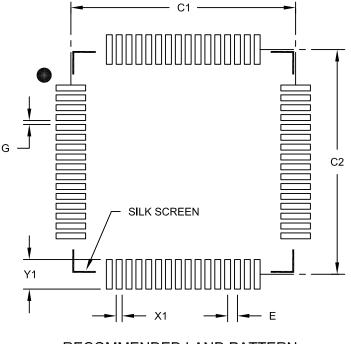

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-VFTLA Exposed Pad                                                           |

| Supplier Device Package    | 44-VTLA (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep32mc204t-i-tl |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

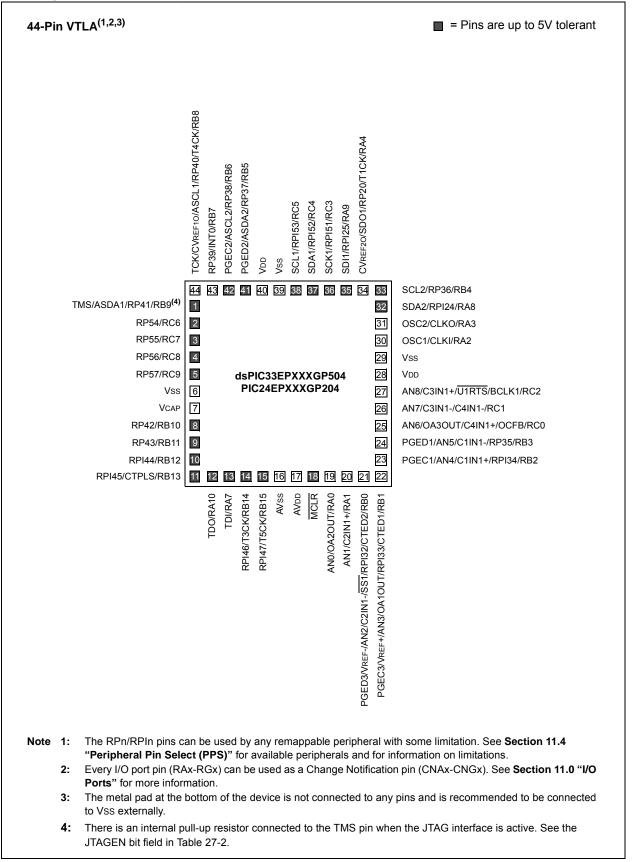

### **Pin Diagrams (Continued)**

| Pin Name <sup>(4)</sup>                        | Pin<br>Type         | Buffer<br>Type          | PPS              | Description                                                                                                                                                                        |

|------------------------------------------------|---------------------|-------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AN0-AN15                                       | I                   | Analog                  | No               | Analog input channels.                                                                                                                                                             |

| CLKI                                           | I                   | ST/<br>CMOS             | No               | External clock source input. Always associated with OSC1 pin function                                                                                                              |

| CLKO                                           | 0                   | —                       | No               | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes. Always associated with OSC2 pin function. |

| OSC1                                           | I                   | ST/                     | No               | Oscillator crystal input. ST buffer when configured in RC mode; CMOS                                                                                                               |

| OSC2                                           | I/O                 | CMOS<br>—               | No               | otherwise.<br>Oscillator crystal output. Connects to crystal or resonator in Crystal<br>Oscillator mode. Optionally functions as CLKO in RC and EC modes.                          |

| REFCLKO                                        | 0                   |                         | Yes              | Reference clock output.                                                                                                                                                            |

| IC1-IC4                                        | Ι                   | ST                      | Yes              | Capture Inputs 1 through 4.                                                                                                                                                        |

| OCFA<br>OCFB<br>OC1-OC4                        | <br> <br> <br>0     | ST<br>ST                | Yes<br>No<br>Yes | Compare Fault A input (for Compare channels).<br>Compare Fault B input (for Compare channels).<br>Compare Outputs 1 through 4.                                                     |

| INT0                                           | I                   | ST                      | No               | External Interrupt 0.                                                                                                                                                              |

| INT1<br>INT2                                   |                     | ST<br>ST                | Yes<br>Yes       | External Interrupt 1.<br>External Interrupt 2.                                                                                                                                     |

| RA0-RA4, RA7-RA12                              | I/O                 | ST                      | No               | PORTA is a bidirectional I/O port.                                                                                                                                                 |

| RB0-RB15                                       | I/O                 | ST                      | No               | PORTB is a bidirectional I/O port.                                                                                                                                                 |

| RC0-RC13, RC15                                 | I/O                 | ST                      | No               | PORTC is a bidirectional I/O port.                                                                                                                                                 |

| RD5, RD6, RD8                                  | I/O                 | ST                      | No               | PORTD is a bidirectional I/O port.                                                                                                                                                 |

| RE12-RE15                                      | I/O                 | ST                      | No               | PORTE is a bidirectional I/O port.                                                                                                                                                 |

| RF0, RF1                                       | I/O                 | ST                      | No               | PORTF is a bidirectional I/O port.                                                                                                                                                 |

| RG6-RG9                                        | I/O                 | ST                      | No               | PORTG is a bidirectional I/O port.                                                                                                                                                 |

| T1CK                                           | Ι                   | ST                      | No               | Timer1 external clock input.                                                                                                                                                       |

| T2CK<br>T3CK                                   |                     | ST<br>ST                | Yes              | Timer2 external clock input.                                                                                                                                                       |

| T4CK                                           |                     | ST                      | No<br>No         | Timer3 external clock input.<br>Timer4 external clock input.                                                                                                                       |

| T5CK                                           | i                   | ST                      | No               | Timer5 external clock input.                                                                                                                                                       |

| CTPLS                                          | 0                   | ST                      | No               | CTMU pulse output.                                                                                                                                                                 |

| CTED1                                          | Ι                   | ST                      | No               | CTMU External Edge Input 1.                                                                                                                                                        |

| CTED2                                          | Ι                   | ST                      | No               | CTMU External Edge Input 2.                                                                                                                                                        |

| U1CTS                                          | Ι                   | ST                      | No               | UART1 Clear-To-Send.                                                                                                                                                               |

| U1RTS                                          | 0                   |                         | No               | UART1 Ready-To-Send.                                                                                                                                                               |

| U1RX                                           |                     | ST                      | Yes              | UART1 receive.<br>UART1 transmit.                                                                                                                                                  |

| U1TX<br>BCLK1                                  | 0                   | ST                      | Yes<br>No        | UART1 Iransmit.<br>UART1 IrDA <sup>®</sup> baud clock output.                                                                                                                      |

| Legend: CMOS = CM<br>ST = Schmi<br>PPS = Perip | MOS co<br>itt Trigg | ompatible<br>er input v | input<br>with CN | or output Analog = Analog input P = Power                                                                                                                                          |

### TABLE 1-1:PINOUT I/O DESCRIPTIONS

Note 1: This pin is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This pin is available on dsPIC33EPXXXGP/MC50X devices only.

3: This is the default Fault on Reset for dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices. See Section 16.0 "High-Speed PWM Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)" for more information.

4: Not all pins are available in all packages variants. See the "Pin Diagrams" section for pin availability.

**5:** There is an internal pull-up resistor connected to the TMS pin when the JTAG interface is active. See the JTAGEN bit field in Table 27-2.

| Pin Name <sup>(4)</sup>       | Pin<br>Type | Buffer<br>Type | PPS     | Description                                                                                     |  |  |  |

|-------------------------------|-------------|----------------|---------|-------------------------------------------------------------------------------------------------|--|--|--|

| C1IN1-                        | I           | Analog         | No      | Op Amp/Comparator 1 Negative Input 1.                                                           |  |  |  |

| C1IN2-                        | I           | Analog         | No      | Comparator 1 Negative Input 2.                                                                  |  |  |  |

| C1IN1+                        | I           | Analog         | No      | Op Amp/Comparator 1 Positive Input 1.                                                           |  |  |  |

| OA1OUT                        | 0           | Analog         | No      | Op Amp 1 output.                                                                                |  |  |  |

| C1OUT                         | 0           | —              | Yes     | Comparator 1 output.                                                                            |  |  |  |

| C2IN1-                        | I           | Analog         | No      | Op Amp/Comparator 2 Negative Input 1.                                                           |  |  |  |

| C2IN2-                        | I           | Analog         | No      | Comparator 2 Negative Input 2.                                                                  |  |  |  |

| C2IN1+                        | I           | Analog         | No      | Op Amp/Comparator 2 Positive Input 1.                                                           |  |  |  |

| OA2OUT                        | 0           | Analog         | No      | Op Amp 2 output.                                                                                |  |  |  |

| C2OUT                         | 0           |                | Yes     | Comparator 2 output.                                                                            |  |  |  |

| C3IN1-                        | I           | Analog         | No      | Op Amp/Comparator 3 Negative Input 1.                                                           |  |  |  |

| C3IN2-                        | I           | Analog         | No      | Comparator 3 Negative Input 2.                                                                  |  |  |  |

| C3IN1+                        | I           | Analog         | No      | Op Amp/Comparator 3 Positive Input 1.                                                           |  |  |  |

| OA3OUT                        | 0           | Analog         | No      | Op Amp 3 output.                                                                                |  |  |  |

| C3OUT                         | 0           |                | Yes     | Comparator 3 output.                                                                            |  |  |  |

| C4IN1-                        | I.          | Analog         | No      | Comparator 4 Negative Input 1.                                                                  |  |  |  |

| C4IN1+                        | I.          | Analog         | No      | Comparator 4 Positive Input 1.                                                                  |  |  |  |

| C4OUT                         | 0           |                | Yes     | Comparator 4 output.                                                                            |  |  |  |

| CVREF10                       | 0           | Analog         | No      | Op amp/comparator voltage reference output.                                                     |  |  |  |

| CVREF20                       | 0           | Analog         | No      | Op amp/comparator voltage reference divided by 2 output.                                        |  |  |  |

| PGED1                         | I/O         | ST             | No      | Data I/O pin for Programming/Debugging Communication Channel 1.                                 |  |  |  |

| PGEC1                         | I           | ST             | No      | Clock input pin for Programming/Debugging Communication Channel 1.                              |  |  |  |

| PGED2                         | I/O         | ST             | No      | Data I/O pin for Programming/Debugging Communication Channel 2.                                 |  |  |  |

| PGEC2                         | I           | ST             | No      | Clock input pin for Programming/Debugging Communication Channel 2.                              |  |  |  |

| PGED3                         | I/O         | ST             | No      | Data I/O pin for Programming/Debugging Communication Channel 3.                                 |  |  |  |

| PGEC3                         | I           | ST             | No      | Clock input pin for Programming/Debugging Communication Channel 3.                              |  |  |  |

| MCLR                          | I/P         | ST             | No      | Master Clear (Reset) input. This pin is an active-low Reset to the device.                      |  |  |  |

| AVDD                          | Р           | Р              | No      | Positive supply for analog modules. This pin must be connected at all times.                    |  |  |  |

| AVss                          | Р           | Р              | No      | Ground reference for analog modules. This pin must be connected at all times.                   |  |  |  |

| Vdd                           | Р           |                | No      | Positive supply for peripheral logic and I/O pins.                                              |  |  |  |

| VCAP                          | Р           |                | No      | CPU logic filter capacitor connection.                                                          |  |  |  |

| Vss                           | Р           |                | No      | Ground reference for logic and I/O pins.                                                        |  |  |  |

| VREF+                         | I           | Analog         | No      | Analog voltage reference (high) input.                                                          |  |  |  |

| VREF-                         | Ι           | Analog         | No      | Analog voltage reference (low) input.                                                           |  |  |  |

| Legend: CMOS = C<br>ST = Schn | nitt Trigg  | jer input v    | with CI | or output     Analog = Analog input     P = Power       MOS levels     O = Output     I = Input |  |  |  |

Note 1: This pin is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This pin is available on dsPIC33EPXXXGP/MC50X devices only.

PPS = Peripheral Pin Select

3: This is the default Fault on Reset for dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices. See Section 16.0 "High-Speed PWM Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)" for more information.

TTL = TTL input buffer

4: Not all pins are available in all packages variants. See the "Pin Diagrams" section for pin availability.

**5:** There is an internal pull-up resistor connected to the TMS pin when the JTAG interface is active. See the JTAGEN bit field in Table 27-2.

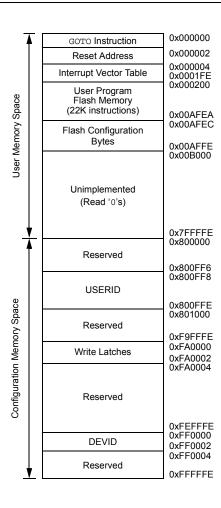

### FIGURE 4-2: PROGRAM MEMORY MAP FOR dsPIC33EP64GP50X, dsPIC33EP64MC20X/50X AND PIC24EP64GP/MC20X DEVICES

Note: Memory areas are not shown to scale.

# 7.0 INTERRUPT CONTROLLER

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXGP/MC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Interrupts" (DS70600) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X interrupt controller reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X CPU.

The interrupt controller has the following features:

- Up to eight processor exceptions and software traps

- Eight user-selectable priority levels

- Interrupt Vector Table (IVT) with a unique vector for each interrupt or exception source

- Fixed priority within a specified user priority level

- Fixed interrupt entry and return latencies

# 7.1 Interrupt Vector Table

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X Interrupt Vector Table (IVT), shown in Figure 7-1, resides in program memory starting at location, 000004h. The IVT contains seven non-maskable trap vectors and up to 246 sources of interrupt. In general, each interrupt source has its own vector. Each interrupt vector contains a 24-bit-wide address. The value programmed into each interrupt vector location is the starting address of the associated Interrupt Service Routine (ISR).

Interrupt vectors are prioritized in terms of their natural priority. This priority is linked to their position in the vector table. Lower addresses generally have a higher natural priority. For example, the interrupt associated with Vector 0 takes priority over interrupts at any other vector address.

# 7.2 Reset Sequence

A device Reset is not a true exception because the interrupt controller is not involved in the Reset process. The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices clear their registers in response to a Reset, which forces the PC to zero. The device then begins program execution at location, 0x000000. A GOTO instruction at the Reset address can redirect program execution to the appropriate start-up routine.

**Note:** Any unimplemented or unused vector locations in the IVT should be programmed with the address of a default interrupt handler routine that contains a RESET instruction.

| R/W-0         | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R/W-0                                                             | R/W-0           | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |  |  |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-----------------|-----------------------|-----------------------|-----------------------|-----------------------|--|--|--|

| ROON          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ROSSLP                                                            | ROSEL           | RODIV3 <sup>(1)</sup> | RODIV2 <sup>(1)</sup> | RODIV1 <sup>(1)</sup> | RODIV0 <sup>(1)</sup> |  |  |  |

| bit 15        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                   |                 |                       |                       | •                     | bit                   |  |  |  |

| U-0           | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | U-0                                                               | U-0             | U-0                   | U-0                   | U-0                   | U-0                   |  |  |  |

|               | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _                                                                 |                 | _                     |                       | _                     |                       |  |  |  |

| bit 7         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                   |                 |                       |                       |                       | bit                   |  |  |  |

| Legend:       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                   |                 |                       |                       |                       |                       |  |  |  |

| R = Readable  | e bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | W = Writable                                                      | bit             | U = Unimpler          | nented bit, read      | l as '0'              |                       |  |  |  |

| -n = Value at |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | '1' = Bit is set                                                  |                 | '0' = Bit is cle      |                       | x = Bit is unkr       | iown                  |  |  |  |

| bit 14        | 0 = Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | e oscillator outp<br>e oscillator outp<br>i <b>ted:</b> Read as ' | out is disabled |                       | .K pin <sup>(2)</sup> |                       |                       |  |  |  |

| bit 13        | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ference Oscilla                                                   |                 | en hit                |                       |                       |                       |  |  |  |

|               | 1 = Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | e oscillator out<br>e oscillator out                              | out continues   | to run in Sleep       |                       |                       |                       |  |  |  |

| bit 12        | 1 = Oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | erence Oscillato<br>crystal is used<br>lock is used as            | as the refere   | nce clock             |                       |                       |                       |  |  |  |

| bit 11-8      | 0 = System clock is used as the reference clock<br><b>RODIV&lt;3:0&gt;:</b> Reference Oscillator Divider bits <sup>(1)</sup><br>1111 = Reference clock divided by 32,768<br>1100 = Reference clock divided by 16,384<br>1101 = Reference clock divided by 4,096<br>1011 = Reference clock divided by 2,048<br>1010 = Reference clock divided by 1,024<br>1001 = Reference clock divided by 512<br>1000 = Reference clock divided by 256<br>0111 = Reference clock divided by 128<br>0110 = Reference clock divided by 4096<br>1011 = Reference clock divided by 128<br>0110 = Reference clock divided by 32<br>0100 = Reference clock divided by 32<br>0100 = Reference clock divided by 40<br>001 = Reference cloc |                                                                   |                 |                       |                       |                       |                       |  |  |  |

|               | 0000 = Refer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ence clock                                                        | -               |                       |                       |                       |                       |  |  |  |

### REGISTER 9-5: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

- **Note 1:** The reference oscillator output must be disabled (ROON = 0) before writing to these bits.

- 2: This pin is remappable. See Section 11.4 "Peripheral Pin Select (PPS)" for more information.

### 15.1 Output Compare Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

### 15.1.1 KEY RESOURCES

- "Output Compare" (DS70358) in the "dsPIC33/ PIC24 Family Reference Manual"

- · Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

### REGISTER 17-1: QEI1CON: QEI1 CONTROL REGISTER (CONTINUED)

| bit 6-4 | <b>INTDIV&lt;2:0&gt;:</b> Timer Input Clock Prescale Select bits (interval timer, main timer (position counter), velocity counter and index counter internal clock divider select) <sup>(3)</sup>                                                                                                                            |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <pre>111 = 1:128 prescale value<br/>110 = 1:64 prescale value<br/>101 = 1:32 prescale value<br/>100 = 1:16 prescale value<br/>011 = 1:8 prescale value<br/>010 = 1:4 prescale value<br/>001 = 1:2 prescale value<br/>000 = 1:1 prescale value</pre>                                                                          |

| bit 3   | <b>CNTPOL:</b> Position and Index Counter/Timer Direction Select bit<br>1 = Counter direction is negative unless modified by external up/down signal                                                                                                                                                                         |

|         | <ul> <li>0 = Counter direction is positive unless modified by external up/down signal</li> </ul>                                                                                                                                                                                                                             |

| bit 2   | GATEN: External Count Gate Enable bit                                                                                                                                                                                                                                                                                        |

|         | <ul> <li>1 = External gate signal controls position counter operation</li> <li>0 = External gate signal does not affect position counter/timer operation</li> </ul>                                                                                                                                                          |

| bit 1-0 | CCM<1:0>: Counter Control Mode Selection bits                                                                                                                                                                                                                                                                                |

|         | <ul> <li>11 = Internal Timer mode with optional external count is selected</li> <li>10 = External clock count with optional external count is selected</li> <li>01 = External clock count with external up/down direction is selected</li> <li>00 = Quadrature Encoder Interface (x4 mode) Count mode is selected</li> </ul> |

| Note 1: | When CCM<1:0> = 10 or 11, all of the QEI counters operate as timers and the PIMOD<2:0> bits are ignored.                                                                                                                                                                                                                     |

- 2: When CCM<1:0> = 00, and QEA and QEB values match the Index Match Value (IMV), the POSCNTH and POSCNTL registers are reset. QEA/QEB signals used for the index match have swap and polarity values applied, as determined by the SWPAB and QEAPOL/QEBPOL bits.

- 3: The selected clock rate should be at least twice the expected maximum quadrature count rate.

# 21.0 ENHANCED CAN (ECAN™) MODULE (dsPIC33EPXXXGP/ MC50X DEVICES ONLY)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Enhanced Controller Area Network (ECAN™)" (DS70353) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

# 21.1 Overview

The Enhanced Controller Area Network (ECAN) module is a serial interface, useful for communicating with other CAN modules or microcontroller devices. This interface/protocol was designed to allow communications within noisy environments. The dsPIC33EPXXXGP/MC50X devices contain one ECAN module.

The ECAN module is a communication controller implementing the CAN 2.0 A/B protocol, as defined in the BOSCH CAN specification. The module supports CAN 1.2, CAN 2.0A, CAN 2.0B Passive and CAN 2.0B Active versions of the protocol. The module implementation is a full CAN system. The CAN specification is not covered within this data sheet. The reader can refer to the BOSCH CAN specification for further details.

The ECAN module features are as follows:

- Implementation of the CAN protocol, CAN 1.2, CAN 2.0A and CAN 2.0B

- · Standard and extended data frames

- 0-8 bytes data length

- Programmable bit rate up to 1 Mbit/sec

- Automatic response to remote transmission requests

- Up to eight transmit buffers with application specified prioritization and abort capability (each buffer can contain up to 8 bytes of data)

- Up to 32 receive buffers (each buffer can contain up to 8 bytes of data)

- Up to 16 full (Standard/Extended Identifier) acceptance filters

- Three full acceptance filter masks

- DeviceNet<sup>™</sup> addressing support

- Programmable wake-up functionality with integrated low-pass filter

- Programmable Loopback mode supports self-test operation

- Signaling via interrupt capabilities for all CAN receiver and transmitter error states

- · Programmable clock source

- Programmable link to Input Capture (IC2) module for time-stamping and network synchronization

- · Low-power Sleep and Idle mode

The CAN bus module consists of a protocol engine and message buffering/control. The CAN protocol engine handles all functions for receiving and transmitting messages on the CAN bus. Messages are transmitted by first loading the appropriate data registers. Status and errors can be checked by reading the appropriate registers. Any message detected on the CAN bus is checked for errors and then matched against filters to see if it should be received and stored in one of the receive registers.

#### 22.2 **CTMU Control Registers**

| REGISTER      | 22-1: CTM                    | UCON1: CTM                                  | J CONTROI                    | - REGISTER                              | 1                |                        |        |  |

|---------------|------------------------------|---------------------------------------------|------------------------------|-----------------------------------------|------------------|------------------------|--------|--|

| R/W-0         | U-0                          | R/W-0                                       | R/W-0                        | R/W-0                                   | R/W-0            | R/W-0                  | R/W-0  |  |

| CTMUEN        | _                            | CTMUSIDL                                    | TGEN                         | EDGEN                                   | EDGSEQEN         | IDISSEN <sup>(1)</sup> | CTTRIG |  |

| bit 15        |                              |                                             |                              |                                         |                  |                        | bit 8  |  |

|               |                              |                                             |                              |                                         |                  |                        |        |  |

| U-0           | U-0                          | U-0                                         | U-0                          | U-0                                     | U-0              | U-0                    | U-0    |  |

|               | _                            |                                             | _                            | <u> </u>                                | <u> </u>         |                        | _      |  |

| bit 7         |                              |                                             |                              |                                         |                  |                        | bit 0  |  |

|               |                              |                                             |                              |                                         |                  |                        |        |  |

| Legend:       |                              |                                             |                              |                                         |                  |                        |        |  |

| R = Readable  | e bit                        | W = Writable b                              | bit                          | U = Unimplen                            | nented bit, read | as '0'                 |        |  |

| -n = Value at | POR                          | '1' = Bit is set                            |                              | '0' = Bit is cleared x = Bit is unknown |                  |                        | own    |  |

| bit 15        |                              | TMU Enable bit<br>is enabled<br>is disabled |                              |                                         |                  |                        |        |  |

| bit 14        | Unimplemented: Read as '0'   |                                             |                              |                                         |                  |                        |        |  |

| bit 13        | 1 = Disconti<br>0 = Continue | CTMU Stop in lo<br>nues module opera        | eration when tion in Idle mo |                                         | lle mode         |                        |        |  |

| bit 12        | TGEN: Time                   | Generation Ena                              | ble bit                      |                                         |                  |                        |        |  |

#### DECISTED

| bit 9 | IDISSEN: Analog Current Source Control bit <sup>(1)</sup>                                                               |

|-------|-------------------------------------------------------------------------------------------------------------------------|

|       | <ul><li>1 = Analog current source output is grounded</li><li>0 = Analog current source output is not grounded</li></ul> |

| bit 8 | CTTRIG: ADC Trigger Control bit                                                                                         |

|       | <ul><li>1 = CTMU triggers ADC start of conversion</li><li>0 = CTMU does not trigger ADC start of conversion</li></ul>   |

EDGSEQEN: Edge Sequence Enable bit

0 = No edge sequence is needed

1 = Enables edge delay generation 0 = Disables edge delay generation

EDGEN: Edge Enable bit

bit 7-0 Unimplemented: Read as '0'

bit 11

bit 10

Note 1: The ADC module Sample-and-Hold capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitance measurement must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

1 = Hardware modules are used to trigger edges (TMRx, CTEDx, etc.) 0 = Software is used to trigger edges (manual set of EDGxSTAT)

1 = Edge 1 event must occur before Edge 2 event can occur

# 23.4 ADC Control Registers

### REGISTER 23-1: AD1CON1: ADC1 CONTROL REGISTER 1

| R/W-0         | U-0                                                                                                                                                                                    | R/W-0                                           | R/W-0               | U-0               | R/W-0            | R/W-0             | R/W-0               |  |  |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|---------------------|-------------------|------------------|-------------------|---------------------|--|--|--|

| ADON          | —                                                                                                                                                                                      | ADSIDL                                          | ADDMABM             |                   | AD12B            | FORM1             | FORM0               |  |  |  |

| bit 15        | •                                                                                                                                                                                      |                                                 |                     |                   |                  |                   | bit 8               |  |  |  |

| R/W-0         | R/W-0                                                                                                                                                                                  | R/W-0                                           | R/W-0               | R/W-0             | R/W-0            | R/W-0, HC, HS     | R/C-0. HC. HS       |  |  |  |

| SSRC2         | SSRC1                                                                                                                                                                                  | SSRC0                                           | SSRCG               | SIMSAM            | ASAM             | SAMP              | DONE <sup>(3)</sup> |  |  |  |

| bit 7         |                                                                                                                                                                                        |                                                 |                     |                   |                  |                   | bit (               |  |  |  |

| Legend:       |                                                                                                                                                                                        | HC - Hardwar                                    | e Clearable bit     | HS - Hardwa       | re Settable bit  | C = Clearable bi  | +                   |  |  |  |

| R = Readable  | a hit                                                                                                                                                                                  | W = Writable b                                  |                     |                   | nented bit, read |                   | L                   |  |  |  |

| -n = Value at |                                                                                                                                                                                        | '1' = Bit is set                                | nt -                | '0' = Bit is clea |                  | x = Bit is unknov | vp.                 |  |  |  |

|               | FUR                                                                                                                                                                                    | I - DILIS SEL                                   |                     |                   | aieu             |                   |                     |  |  |  |

| bit 15        | ADON: ADO                                                                                                                                                                              | C1 Operating M                                  | ode bit             |                   |                  |                   |                     |  |  |  |

|               | 1 = ADC mo<br>0 = ADC is 0                                                                                                                                                             | odule is operatir<br>off                        | ng                  |                   |                  |                   |                     |  |  |  |

| bit 14        | Unimpleme                                                                                                                                                                              | nted: Read as                                   | <b>'</b> 0 <b>'</b> |                   |                  |                   |                     |  |  |  |