Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 60 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 512KB (170K x 24)                                                              |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | ·                                                                              |

| RAM Size                   | 24K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 6x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                 |

| Supplier Device Package    | 28-SOIC                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep512gp202-e-so |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

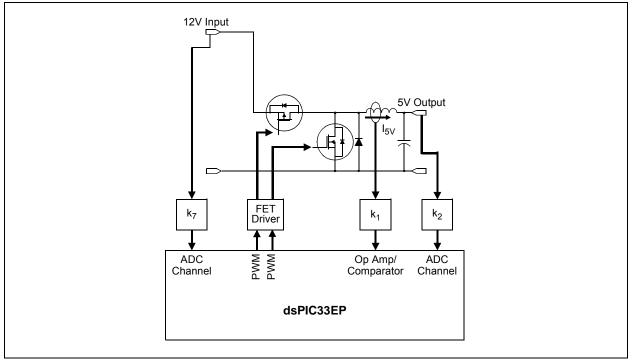

#### FIGURE 2-5: SINGLE-PHASE SYNCHRONOUS BUCK CONVERTER

### TABLE 4-19: SPI1 AND SPI2 REGISTER MAP

| SFR Name | Addr. | Bit 15 | Bit 14                             | Bit 13  | Bit 12 | Bit 11                                                      | Bit 10                                                | Bit 9      | Bit 8        | Bit 7       | Bit 6      | Bit 5  | Bit 4 | Bit 3      | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|----------|-------|--------|------------------------------------|---------|--------|-------------------------------------------------------------|-------------------------------------------------------|------------|--------------|-------------|------------|--------|-------|------------|-------|--------|--------|---------------|

| SPI1STAT | 0240  | SPIEN  | _                                  | SPISIDL | _      | _                                                           | 5                                                     | SPIBEC<2:0 | >            | SRMPT       | SPIROV     | SRXMPT |       | SISEL<2:0> |       | SPITBF | SPIRBF | 0000          |

| SPI1CON1 | 0242  | _      | _                                  | _       | DISSCK | DISSDO                                                      | SDO MODE16 SMP CKE SSEN CKP MSTEN SPRE<2:0> PPRE<1:0> |            |              |             | <1:0>      | 0000   |       |            |       |        |        |               |

| SPI1CON2 | 0244  | FRMEN  | SPIFSD                             | FRMPOL  | _      | _                                                           |                                                       | _          | _            | —           | _          | _      | _     | _          | _     | FRMDLY | SPIBEN | 0000          |

| SPI1BUF  | 0248  |        |                                    |         |        |                                                             |                                                       | SPI1 Tra   | insmit and R | eceive Buff | er Registe | r      |       |            |       |        |        | 0000          |

| SPI2STAT | 0260  | SPIEN  | _                                  | SPISIDL | _      | _                                                           | ŝ                                                     | SPIBEC<2:0 | >            | SRMPT       | SPIROV     | SRXMPT |       | SISEL<2:0> |       | SPITBF | SPIRBF | 0000          |

| SPI2CON1 | 0262  | _      | _                                  | _       | DISSCK | DISSDO MODE16 SMP CKE SSEN CKP MSTEN SPRE<2:0> PPRE<1:0> 00 |                                                       |            |              |             |            | 0000   |       |            |       |        |        |               |

| SPI2CON2 | 0264  | FRMEN  | RMEN SPIFSD FRMPOL FRMDLY SPIBEN ( |         |        |                                                             |                                                       |            |              |             |            | 0000   |       |            |       |        |        |               |

| SPI2BUF  | 0268  |        |                                    |         |        |                                                             |                                                       | SPI2 Tra   | insmit and R | eceive Buff | er Registe | r      |       |            |       |        |        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| Input Name <sup>(1)</sup>                   | Function Name | Register | Configuration Bits |  |  |

|---------------------------------------------|---------------|----------|--------------------|--|--|

| External Interrupt 1                        | INT1          | RPINR0   | INT1R<6:0>         |  |  |

| External Interrupt 2                        | INT2          | RPINR1   | INT2R<6:0>         |  |  |

| Timer2 External Clock                       | T2CK          | RPINR3   | T2CKR<6:0>         |  |  |

| Input Capture 1                             | IC1           | RPINR7   | IC1R<6:0>          |  |  |

| Input Capture 2                             | IC2           | RPINR7   | IC2R<6:0>          |  |  |

| Input Capture 3                             | IC3           | RPINR8   | IC3R<6:0>          |  |  |

| Input Capture 4                             | IC4           | RPINR8   | IC4R<6:0>          |  |  |

| Output Compare Fault A                      | OCFA          | RPINR11  | OCFAR<6:0>         |  |  |

| PWM Fault 1 <sup>(3)</sup>                  | FLT1          | RPINR12  | FLT1R<6:0>         |  |  |

| PWM Fault 2 <sup>(3)</sup>                  | FLT2          | RPINR12  | FLT2R<6:0>         |  |  |

| QEI1 Phase A <sup>(3)</sup>                 | QEA1          | RPINR14  | QEA1R<6:0>         |  |  |

| QEI1 Phase B <sup>(3)</sup>                 | QEB1          | RPINR14  | QEB1R<6:0>         |  |  |

| QEI1 Index <sup>(3)</sup>                   | INDX1         | RPINR15  | INDX1R<6:0>        |  |  |

| QEI1 Home <sup>(3)</sup>                    | HOME1         | RPINR15  | HOM1R<6:0>         |  |  |

| UART1 Receive                               | U1RX          | RPINR18  | U1RXR<6:0>         |  |  |

| UART2 Receive                               | U2RX          | RPINR19  | U2RXR<6:0>         |  |  |

| SPI2 Data Input                             | SDI2          | RPINR22  | SDI2R<6:0>         |  |  |

| SPI2 Clock Input                            | SCK2          | RPINR22  | SCK2R<6:0>         |  |  |

| SPI2 Slave Select                           | SS2           | RPINR23  | SS2R<6:0>          |  |  |

| CAN1 Receive <sup>(2)</sup>                 | C1RX          | RPINR26  | C1RXR<6:0>         |  |  |

| PWM Sync Input 1 <sup>(3)</sup>             | SYNCI1        | RPINR37  | SYNCI1R<6:0>       |  |  |

| PWM Dead-Time Compensation 1 <sup>(3)</sup> | DTCMP1        | RPINR38  | DTCMP1R<6:0>       |  |  |

| PWM Dead-Time Compensation 2 <sup>(3)</sup> | DTCMP2        | RPINR39  | DTCMP2R<6:0>       |  |  |

| PWM Dead-Time Compensation 3 <sup>(3)</sup> | DTCMP3        | RPINR39  | DTCMP3R<6:0>       |  |  |

#### TABLE 11-1: SELECTABLE INPUT SOURCES (MAPS INPUT TO FUNCTION)

**Note 1:** Unless otherwise noted, all inputs use the Schmitt Trigger input buffers.

2: This input source is available on dsPIC33EPXXXGP/MC50X devices only.

3: This input source is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

## 12.0 TIMER1

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Timer1 module is a 16-bit timer that can operate as a free-running interval timer/counter.

The Timer1 module has the following unique features over other timers:

- Can be operated in Asynchronous Counter mode from an external clock source

- The external clock input (T1CK) can optionally be synchronized to the internal device clock and the clock synchronization is performed after the prescaler

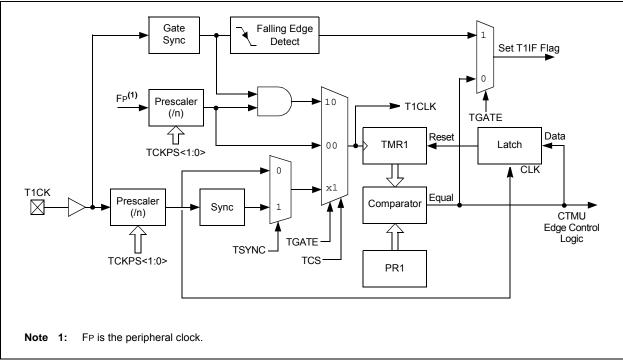

- A block diagram of Timer1 is shown in Figure 12-1.

The Timer1 module can operate in one of the following modes:

- Timer mode

- · Gated Timer mode

- Synchronous Counter mode

- · Asynchronous Counter mode

In Timer and Gated Timer modes, the input clock is derived from the internal instruction cycle clock (FCY). In Synchronous and Asynchronous Counter modes, the input clock is derived from the external clock input at the T1CK pin.

The Timer modes are determined by the following bits:

- Timer Clock Source Control bit (TCS): T1CON<1>

- Timer Synchronization Control bit (TSYNC): T1CON<2>

- Timer Gate Control bit (TGATE): T1CON<6>

Timer control bit setting for different operating modes are given in the Table 12-1.

| Mode                    | TCS | TGATE | TSYNC |  |  |  |  |

|-------------------------|-----|-------|-------|--|--|--|--|

| Timer                   | 0   | 0     | х     |  |  |  |  |

| Gated Timer             | 0   | 1     | x     |  |  |  |  |

| Synchronous<br>Counter  | 1   | х     | 1     |  |  |  |  |

| Asynchronous<br>Counter | 1   | x     | 0     |  |  |  |  |

#### TABLE 12-1: TIMER MODE SETTINGS

#### FIGURE 12-1: 16-BIT TIMER1 MODULE BLOCK DIAGRAM

| R/W-0              | U-0                  | R/W-0                 | U-0                   | U-0 | U-0 | U-0                  | U-0   |

|--------------------|----------------------|-----------------------|-----------------------|-----|-----|----------------------|-------|

| TON <sup>(1)</sup> | —                    | TSIDL <sup>(2)</sup>  | —                     | —   | —   | —                    | —     |

| bit 15             |                      |                       |                       |     |     |                      | bit 8 |

|                    |                      |                       |                       |     |     |                      |       |

| U-0                | R/W-0                | R/W-0                 | R/W-0                 | U-0 | U-0 | R/W-0                | U-0   |

| —                  | TGATE <sup>(1)</sup> | TCKPS1 <sup>(1)</sup> | TCKPS0 <sup>(1)</sup> |     | —   | TCS <sup>(1,3)</sup> | —     |

| bit 7              |                      |                       |                       |     |     |                      | bit 0 |

|                    |                      |                       |                       |     |     |                      |       |

#### REGISTER 13-2: TyCON: (TIMER3 AND TIMER5) CONTROL REGISTER

| Legend:      |                                                                        |                                                                               |                                          |                                   |  |  |  |  |  |  |

|--------------|------------------------------------------------------------------------|-------------------------------------------------------------------------------|------------------------------------------|-----------------------------------|--|--|--|--|--|--|

| R = Readal   | ole bit                                                                | W = Writable bit                                                              | U = Unimplemented bit                    | , read as '0'                     |  |  |  |  |  |  |

| -n = Value a | at POR                                                                 | '1' = Bit is set                                                              | '0' = Bit is cleared                     | x = Bit is unknown                |  |  |  |  |  |  |

| bit 15       | TON: Tin                                                               | nery On bit <sup>(1)</sup>                                                    |                                          |                                   |  |  |  |  |  |  |

|              |                                                                        | s 16-bit Timery<br>s 16-bit Timery                                            |                                          |                                   |  |  |  |  |  |  |

| bit 14       | •                                                                      | mented: Read as '0'                                                           |                                          |                                   |  |  |  |  |  |  |

| bit 13       | -                                                                      | imery Stop in Idle Mode bit <sup>(2</sup>                                     | 2)                                       |                                   |  |  |  |  |  |  |

|              |                                                                        | ontinues module operation winues module operation in Id                       | when device enters Idle mode<br>lle mode |                                   |  |  |  |  |  |  |

| bit 12-7     | Unimple                                                                | Unimplemented: Read as '0'                                                    |                                          |                                   |  |  |  |  |  |  |

| bit 6        | <b>TGATE:</b> Timery Gated Time Accumulation Enable bit <sup>(1)</sup> |                                                                               |                                          |                                   |  |  |  |  |  |  |

|              | When TC<br>This bit is                                                 | <u>CS = 1:</u><br>s ignored.                                                  |                                          |                                   |  |  |  |  |  |  |

|              |                                                                        | <u>CS = 0:</u><br>d time accumulation is enab<br>d time accumulation is disab |                                          |                                   |  |  |  |  |  |  |

| bit 5-4      | TCKPS<                                                                 | 1:0>: Timery Input Clock Pre                                                  | escale Select bits <sup>(1)</sup>        |                                   |  |  |  |  |  |  |

|              | 11 <b>= 1:2</b> 5                                                      |                                                                               |                                          |                                   |  |  |  |  |  |  |

|              | 10 = 1:64<br>01 = 1:8                                                  | 1                                                                             |                                          |                                   |  |  |  |  |  |  |

|              | 01 = 1.8                                                               |                                                                               |                                          |                                   |  |  |  |  |  |  |

| bit 3-2      | Unimple                                                                | mented: Read as '0'                                                           |                                          |                                   |  |  |  |  |  |  |

| bit 1        | -                                                                      | nery Clock Source Select bit                                                  | (1,3)                                    |                                   |  |  |  |  |  |  |

|              |                                                                        | nal clock is from pin, TyCK (<br>nal clock (FP)                               | (on the rising edge)                     |                                   |  |  |  |  |  |  |

| bit 0        | Unimple                                                                | mented: Read as '0'                                                           |                                          |                                   |  |  |  |  |  |  |

|              |                                                                        | peration is enabled (T2CON<br>set through TxCON.                              | <3> = 1), these bits have no e           | ffect on Timery operation; all ti |  |  |  |  |  |  |

|              |                                                                        |                                                                               |                                          |                                   |  |  |  |  |  |  |

2: When 32-bit timer operation is enabled (T32 = 1) in the Timerx Control register (TxCON<3>), the TSIDL bit must be cleared to operate the 32-bit timer in Idle mode.

3: The TyCK pin is not available on all timers. See the "Pin Diagrams" section for the available pins.

| U-0                   | U-0                                | HS, R/C-0                          | R/W-0            | HS, R/C-0        | R/W-0            | HS, R/C-0             | R/W-0    |

|-----------------------|------------------------------------|------------------------------------|------------------|------------------|------------------|-----------------------|----------|

| _                     | —                                  | PCHEQIRQ                           | PCHEQIEN         | PCLEQIRQ         | PCLEQIEN         | POSOVIRQ              | POSOVIEN |

| bit 15                |                                    |                                    |                  |                  |                  |                       | bit 8    |

|                       |                                    |                                    |                  |                  |                  |                       |          |

| HS, R/C-0             | R/W-0                              | HS, R/C-0                          | R/W-0            | HS, R/C-0        | R/W-0            | HS, R/C-0             | R/W-0    |

| PCIIRQ <sup>(1)</sup> | PCIIEN                             | VELOVIRQ                           | VELOVIEN         | HOMIRQ           | HOMIEN           | IDXIRQ                | IDXIEN   |

| bit 7                 |                                    |                                    |                  |                  |                  |                       | bit 0    |

| r                     |                                    |                                    |                  |                  |                  |                       |          |

| Legend:               |                                    | HS = Hardware                      |                  | C = Clearable    |                  |                       |          |

| R = Readable I        |                                    | W = Writable b                     | bit              | •                | nented bit, rea  |                       |          |

| -n = Value at P       | OR                                 | '1' = Bit is set                   |                  | '0' = Bit is cle | ared             | x = Bit is unkr       | iown     |

|                       |                                    |                                    |                  |                  |                  |                       |          |

| bit 15-14             | -                                  | ted: Read as '0                    |                  |                  |                  | .,                    |          |

| bit 13                |                                    | Position Counte                    | er Greater Tha   | n or Equal Cor   | npare Status b   | it                    |          |

|                       |                                    | T ≥ QEI1GEC<br>T < QEI1GEC         |                  |                  |                  |                       |          |

| bit 12                |                                    | Position Counte                    | r Greater Tha    | n or Equal Con   | npare Interrupt  | Enable bit            |          |

|                       | 1 = Interrupt i                    |                                    |                  |                  |                  |                       |          |

|                       | 0 = Interrupt i                    | s disabled                         |                  |                  |                  |                       |          |

| bit 11                |                                    | Position Counte                    | r Less Than o    | r Equal Compa    | are Status bit   |                       |          |

|                       | 1 = POS1CN                         |                                    |                  |                  |                  |                       |          |

| bit 10                |                                    | Position Counte                    | r Less Than or   | - Equal Compa    | ire Interrunt En | ahla hit              |          |

|                       | 1 = Interrupt i                    |                                    |                  |                  |                  |                       |          |

|                       | 0 = Interrupt i                    |                                    |                  |                  |                  |                       |          |

| bit 9                 | POSOVIRQ:                          | Position Counte                    | er Overflow Sta  | itus bit         |                  |                       |          |

|                       | 1 = Overflow                       |                                    |                  |                  |                  |                       |          |

|                       |                                    | ow has occurred                    |                  |                  |                  |                       |          |

| bit 8                 |                                    | Position Counte                    | r Overflow Inte  | errupt Enable b  | Dit              |                       |          |

|                       | 1 = Interrupt i<br>0 = Interrupt i |                                    |                  |                  |                  |                       |          |

| bit 7                 | •                                  | tion Counter (H                    | oming) Initializ | ation Process    | Complete Stat    | us bit <sup>(1)</sup> |          |

|                       |                                    | T was reinitialize                 | •                |                  | · · · · · · · ·  |                       |          |

|                       | 0 = POS1CN                         | T was not reiniti                  | alized           |                  |                  |                       |          |

| bit 6                 | PCIIEN: Posi                       | tion Counter (He                   | oming) Initializ | ation Process    | Complete inter   | rupt Enable bit       |          |

|                       | 1 = Interrupt i                    |                                    |                  |                  |                  |                       |          |

| bit 5                 | 0 = Interrupt i                    |                                    | r Overflow Sta   | tuo hit          |                  |                       |          |

| DIL 5                 | 1 = Overflow                       | Velocity Counter                   | I Overnow Sta    |                  |                  |                       |          |

|                       |                                    | ow has not occu                    | irred            |                  |                  |                       |          |

| bit 4                 | VELOVIEN:                          | /elocity Counter                   | Overflow Inte    | rrupt Enable bi  | it               |                       |          |

|                       | 1 = Interrupt i                    | s enabled                          |                  |                  |                  |                       |          |

|                       | 0 = Interrupt i                    |                                    |                  |                  |                  |                       |          |

| bit 3                 |                                    | atus Flag for Ho                   |                  | us bit           |                  |                       |          |

|                       |                                    | ent has occurred<br>event has occu |                  |                  |                  |                       |          |

|                       |                                    |                                    |                  |                  |                  |                       |          |

#### REGISTER 17-3: QEI1STAT: QEI1 STATUS REGISTER

**Note 1:** This status bit is only applicable to PIMOD<2:0> modes, '011' and '100'.

|                                    | R/W-0 | R/W-0           | R/W-0                                 | R/W-0                                                            | R/W-0                                                                                                | R/W-0                                                                                                    |  |  |

|------------------------------------|-------|-----------------|---------------------------------------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--|--|

|                                    |       | QEIG            | EC<31:24>                             |                                                                  |                                                                                                      |                                                                                                          |  |  |

|                                    |       |                 |                                       |                                                                  |                                                                                                      | bit 8                                                                                                    |  |  |

|                                    | DAMO  |                 |                                       |                                                                  | DAMO                                                                                                 |                                                                                                          |  |  |

| R/W-U                              | R/W-0 |                 |                                       | R/W-U                                                            | R/W-U                                                                                                | R/W-0                                                                                                    |  |  |

|                                    |       | QEIGE           | EC<23:16>                             |                                                                  |                                                                                                      |                                                                                                          |  |  |

|                                    |       |                 |                                       |                                                                  |                                                                                                      | bit (                                                                                                    |  |  |

|                                    |       |                 |                                       |                                                                  |                                                                                                      |                                                                                                          |  |  |

| R = Readable bit W = Writable bit  |       | t               | U = Unimplemented bit, read as '0'    |                                                                  |                                                                                                      |                                                                                                          |  |  |

| -n = Value at POR '1' = Bit is set |       |                 | '0' = Bit is clea                     | ared                                                             | x = Bit is unkn                                                                                      | x = Bit is unknown                                                                                       |  |  |

|                                    |       | W = Writable bi | R/W-0 R/W-0 QEIGI<br>W = Writable bit | R/W-0 R/W-0 R/W-0 QEIGEC<23:16><br>W = Writable bit U = Unimplem | R/W-0     R/W-0     R/W-0       QEIGEC<23:16>       W = Writable bit     U = Unimplemented bit, real | R/W-0       R/W-0       R/W-0       R/W-0         QEIGEC<23:16>       U = Unimplemented bit, read as '0' |  |  |

#### REGISTER 17-15: QEI1GECH: QEI1 GREATER THAN OR EQUAL COMPARE HIGH WORD REGISTER

bit 15-0 QEIGEC<31:16>: High Word Used to Form 32-Bit Greater Than or Equal Compare Register (QEI1GEC) bits

#### REGISTER 17-16: QEI1GECL: QEI1 GREATER THAN OR EQUAL COMPARE LOW WORD REGISTER

| R/W-0                             | R/W-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |  |

|-----------------------------------|-------|------------------|-------|-----------------------------------------|-------|-------|-------|--|--|

|                                   |       |                  | QEIGE | C<15:8>                                 |       |       |       |  |  |

| bit 15                            |       |                  |       |                                         |       |       | bit 8 |  |  |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |  |

|                                   |       |                  | QEIG  | EC<7:0>                                 |       |       |       |  |  |

| bit 7                             |       |                  |       |                                         |       |       | bit 0 |  |  |

| Legend:                           |       |                  |       |                                         |       |       |       |  |  |

| R = Readable bit W = Writable bit |       |                  |       | U = Unimplemented bit, read as '0'      |       |       |       |  |  |

| -n = Value at P                   | OR    | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |       |       | nown  |  |  |

bit 15-0 QEIGEC<15:0>: Low Word Used to Form 32-Bit Greater Than or Equal Compare Register (QEI1GEC) bits

#### REGISTER 21-16: CxRXFnSID: ECANx ACCEPTANCE FILTER n STANDARD IDENTIFIER REGISTER (n = 0-15)

| RW-x       R/W-x       R/W-x       R/W-x       R/W-x       R/W-x       R/W-x       R/W-x         SID10       SID9       SID8       SID7       SID6       SID5       SID4       SID3         bit 15       bit 15       bit 8       bit 8       bit 8       bit 8       bit 8         R/W-x       R/W-x       R/W-x       U-0       R/W-x       U-0       R/W-x       R/W-x         SID2       SID1       SID0       -       EXIDE       -       EID17       EID16         bit 7       5ID2       SID1       SID0       -       EXIDE       -       EID17       EID16         bit 7       -       -       EID17       EID16       bit 0       bit 0         Legend:       R       Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       - <th></th> <th></th> <th></th> <th></th> <th></th> <th></th> <th></th> <th></th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |               |                                                                          |                                |               |                                         |       |       |       |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------------------------------------------------------------------|--------------------------------|---------------|-----------------------------------------|-------|-------|-------|--|--|

| bit 15 bit 2 bit 3 bit 8 bit 8 bit 8 bit 7 bit 7 bit 9 bit 7 bit 0 bit 0 bit 7 bit 0 bit 0 bit 7 bit 0 bit 0 bit 0 bit 1 bit 9 bit 1 bit 9 bit 1 bit 1 bit 9 bit 1 | R/W-x         | R/W-x                                                                    | R/W-x                          | R/W-x         | R/W-x                                   | R/W-x | R/W-x | R/W-x |  |  |

| R/W-x       R/W-x       U-0       R/W-x       U-0       R/W-x       R/W-x         SID2       SID1       SID0       -       EXIDE       -       EID17       EID16         bit 7       bit 0         Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-5       SID<10:>: Standard Identifier bits       1 = Message address bit, SIDx, must be '1' to match filter       0 = Message address bit, SIDx, must be '0' to match filter         bit 4       Unimplemented: Read as '0'       bit 3       EXIDE: Extended Identifier Enable bit         If MIDE = 1:       1 = Matches only messages with Extended Identifier addresses       0 = Matches only messages with Standard Identifier addresses         0 = Matches only messages with Standard Identifier addresses       Ignores EXIDE bit.       Ignores EXIDE bit.         bit 2       Unimplemented: Read as '0'       bit 1-0       EID       EID         bit 1-0       EID       Extended Identifier bits       1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SID10         | SID9                                                                     | SID8                           | SID7          | SID6                                    | SID5  | SID4  | SID3  |  |  |

| SID2       SID1       SID0       —       EXIDE       —       EID17       EID16         bit 7       bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | bit 15        | ÷                                                                        |                                |               |                                         |       |       | bit 8 |  |  |

| SID2       SID1       SID0       —       EXIDE       —       EID17       EID16         bit 7       bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |               |                                                                          |                                |               |                                         |       |       |       |  |  |

| bit 7       bit 0         Legend:       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-5       SID<10:0>: Standard Identifier bits       1 = Message address bit, SIDx, must be '1' to match filter       x = Bit is unknown         bit 15-5       SID<10:0>: Standard Identifier bits       1 = Message address bit, SIDx, must be '1' to match filter       x = Bit is unknown         bit 4       Unimplemented: Read as '0'       bit 3       EXIDE: Extended Identifier Enable bit       If MIDE = 1:         1 = Matches only messages with Extended Identifier addresses       0 = Matches only messages with Standard Identifier addresses         0 = Matches only messages with Standard Identifier addresses       If MIDE = 0:       Ignores EXIDE bit.         bit 2       Unimplemented: Read as '0'       bit 1-0       EID<17:16>: Extended Identifier bits         1 = Message address bit, EIDx, must be '1' to match filter       1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R/W-x         | R/W-x                                                                    | R/W-x                          | U-0           | R/W-x                                   | U-0   | R/W-x | R/W-x |  |  |

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-5       SID<10:0>: Standard Identifier bits       1 = Message address bit, SIDx, must be '1' to match filter         0 = Message address bit, SIDx, must be '1' to match filter       0 = Message address bit, SIDx, must be '0' to match filter         bit 4       Unimplemented: Read as '0'         bit 3       EXIDE: Extended Identifier Enable bit         If MIDE = 1:       1 = Matches only messages with Extended Identifier addresses         0 = Matches only messages with Standard Identifier addresses         If MIDE = 0:       Ignores EXIDE bit.         bit 2       Unimplemented: Read as '0'         bit 1-0       EID<17:16>: Extended Identifier bits         1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SID2          | SID1                                                                     | SID0                           | _             | EXIDE                                   |       | EID17 | EID16 |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-5       SID<10:0>: Standard Identifier bits       1 = Message address bit, SIDx, must be '1' to match filter         0 = Message address bit, SIDx, must be '1' to match filter       0 = Message address bit, SIDx, must be '0' to match filter         bit 4       Unimplemented: Read as '0'         bit 3       EXIDE: Extended Identifier Enable bit         If MIDE = 1:       1 = Matches only messages with Extended Identifier addresses         0 = Matches only messages with Standard Identifier addresses       0 = Matches only messages with Standard Identifier addresses         1f MIDE = 0:       Ignores EXIDE bit.         bit 2       Unimplemented: Read as '0'         bit 1-0       EID         a Matches bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | bit 7         |                                                                          |                                |               |                                         |       |       | bit 0 |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-5       SID<10:0>: Standard Identifier bits       1 = Message address bit, SIDx, must be '1' to match filter         0 = Message address bit, SIDx, must be '1' to match filter       0 = Message address bit, SIDx, must be '0' to match filter         bit 4       Unimplemented: Read as '0'         bit 3       EXIDE: Extended Identifier Enable bit         If MIDE = 1:       1 = Matches only messages with Extended Identifier addresses         0 = Message Sit, SIDE       5         bit 2       Unimplemented: Read as '0'         bit 2       Unimplemented: Read as '0'         bit 4       Unimplemented: Read as '0'         bit 1-0       EID         if MIDE = 0:       Ignores EXIDE bit.         bit 2       Unimplemented: Read as '0'         bit 1-0       EID         a Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |               |                                                                          |                                |               |                                         |       |       |       |  |  |

| -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-5       SID<10:0>: Standard Identifier bits       1 = Message address bit, SIDx, must be '1' to match filter         o = Message address bit, SIDx, must be '1' to match filter       0' = Bit is cleared       x = Bit is unknown         bit 4       Unimplemented: Read as '0'       bit 3       EXIDE: Extended Identifier Enable bit         If MIDE = 1:       1 = Matches only messages with Extended Identifier addresses       0 = Matches only messages with Standard Identifier addresses         If MIDE = 0:       Ignores EXIDE bit.       If MIDE = 0:       Ignores EXIDE bit.         bit 2       Unimplemented: Read as '0'       EID<17:16>: Extended Identifier bits         1 = Message address bit, EIDx, must be '1' to match filter       1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Legend:       |                                                                          |                                |               |                                         |       |       |       |  |  |

| bit 15-5       SID<10:0>: Standard Identifier bits         1 = Message address bit, SIDx, must be '1' to match filter         0 = Message address bit, SIDx, must be '0' to match filter         bit 4       Unimplemented: Read as '0'         bit 3       EXIDE: Extended Identifier Enable bit         If MIDE = 1:       1 = Matches only messages with Extended Identifier addresses         0 = Matches only messages with Standard Identifier addresses         0 = Matches only messages with Standard Identifier addresses         1 f MIDE = 0:         Ignores EXIDE bit.         bit 2       Unimplemented: Read as '0'         bit 1-0       EID<17:16>: Extended Identifier bits         1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R = Readable  | R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'     |                                |               |                                         |       |       |       |  |  |

| 1 = Message address bit, SIDx, must be '1' to match filter         0 = Message address bit, SIDx, must be '0' to match filter         bit 4       Unimplemented: Read as '0'         bit 3       EXIDE: Extended Identifier Enable bit         If MIDE = 1:       1 = Matches only messages with Extended Identifier addresses         0 = Matches only messages with Standard Identifier addresses       0 = Matches only messages with Standard Identifier addresses         If MIDE = 0:       Ignores EXIDE bit.         bit 2       Unimplemented: Read as '0'         bit 1-0       EID         I= Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -n = Value at | POR                                                                      | '1' = Bit is set               |               | '0' = Bit is cleared x = Bit is unknown |       |       |       |  |  |

| If MIDE = 1:         1 = Matches only messages with Extended Identifier addresses         0 = Matches only messages with Standard Identifier addresses         If MIDE = 0:         Ignores EXIDE bit.         bit 2       Unimplemented: Read as '0'         bit 1-0       EID<17:16>: Extended Identifier bits         1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | bit 4         | 0 = Message                                                              | address bit, SI                | Dx, must be ' |                                         |       |       |       |  |  |

| bit 1-0 EID<17:16>: Extended Identifier bits<br>1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 3         | <u>If MIDE = 1:</u><br>1 = Matches<br>0 = Matches<br><u>If MIDE = 0:</u> | only messages<br>only messages | with Extende  |                                         |       |       |       |  |  |

| 1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 2         | Unimplemen                                                               | ted: Read as '                 | כ'            |                                         |       |       |       |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | bit 1-0       | EID<17:16>:                                                              | Extended Iden                  | tifier bits   |                                         |       |       |       |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               | •                                                                        |                                |               |                                         |       |       |       |  |  |

### 23.2 ADC Helpful Tips

- 1. The SMPIx control bits in the AD1CON2 register:

- a) Determine when the ADC interrupt flag is set and an interrupt is generated, if enabled.

- b) When the CSCNA bit in the AD1CON2 registers is set to '1', this determines when the ADC analog scan channel list, defined in the AD1CSSL/AD1CSSH registers, starts over from the beginning.

- c) When the DMA peripheral is not used (ADDMAEN = 0), this determines when the ADC Result Buffer Pointer to ADC1BUF0-ADC1BUFF gets reset back to the beginning at ADC1BUF0.

- d) When the DMA peripheral is used (ADDMAEN = 1), this determines when the DMA Address Pointer is incremented after a sample/conversion operation. ADC1BUF0 is the only ADC buffer used in this mode. The ADC Result Buffer Pointer to ADC1BUF0-ADC1BUFF gets reset back to the beginning at ADC1BUF0. The DMA address is incremented after completion of every 32nd sample/conversion operation. Conversion results are stored in the ADC1BUF0 register for transfer to RAM using DMA.

- 2. When the DMA module is disabled (ADDMAEN = 0), the ADC has 16 result buffers. ADC conversion results are stored sequentially in ADC1BUF0-ADC1BUFF, regardless of which analog inputs are being used subject to the SMPIx bits and the condition described in 1c) above. There is no relationship between the ANx input being measured and which ADC buffer (ADC1BUF0-ADC1BUFF) that the conversion results will be placed in.

- 3. When the DMA module is enabled (ADDMAEN = 1), the ADC module has only 1 ADC result buffer (i.e., ADC1BUF0) per ADC peripheral and the ADC conversion result must be read, either by the CPU or DMA Controller, before the next ADC conversion is complete to avoid overwriting the previous value.

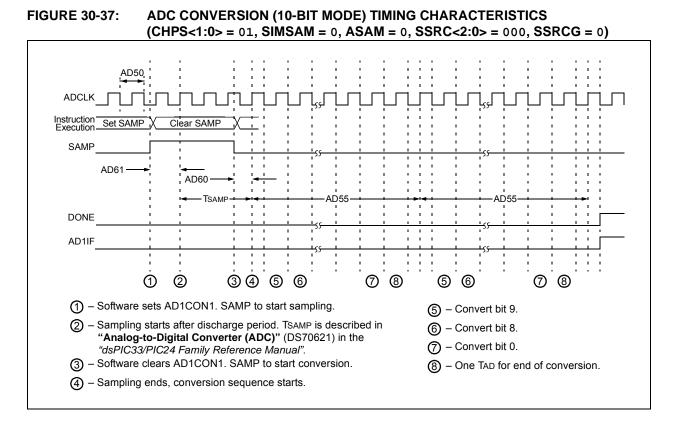

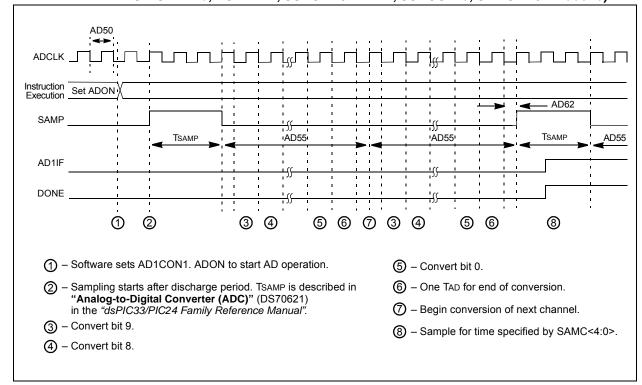

- 4. The DONE bit (AD1CON1<0>) is only cleared at the start of each conversion and is set at the completion of the conversion, but remains set indefinitely, even through the next sample phase until the next conversion begins. If application code is monitoring the DONE bit in any kind of software loop, the user must consider this behavior because the CPU code execution is faster than the ADC. As a result, in Manual Sample mode, particularly where the user's code is setting the SAMP bit (AD1CON1<1>), the DONE bit should also be cleared by the user application just before setting the SAMP bit.

5. Enabling op amps, comparator inputs and external voltage references can limit the availability of analog inputs (ANx pins). For example, when Op Amp 2 is enabled, the pins for ANO, AN1 and AN2 are used by the op amp's inputs and output. This negates the usefulness of Alternate Input mode since the MUXA selections use AN0-AN2. Carefully study the ADC block diagram to determine the configuration that will best suit your application. Configuration examples are available in the "Analog-to-Digital Converter (ADC)" (DS70621) section in the "dsPIC33/ PIC24 Family Reference Manual".

#### 23.3 ADC Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser:<br>http://www.microchip.com/wwwproducts/ |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | Devices.aspx?dDocName=en555464                                                                                                                          |

#### 23.3.1 KEY RESOURCES

- "Analog-to-Digital Converter (ADC)" (DS70621) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

## REGISTER 24-10: PTGADJ: PTG ADJUST REGISTER<sup>(1)</sup>

| R/W-0           | R/W-0                                                           | R/W-0          | R/W-0 | R/W-0        | R/W-0           | R/W-0    | R/W-0 |

|-----------------|-----------------------------------------------------------------|----------------|-------|--------------|-----------------|----------|-------|

|                 |                                                                 |                | PTGA  | DJ<15:8>     |                 |          |       |

| bit 15          |                                                                 |                |       |              |                 |          | bit 8 |

|                 |                                                                 |                |       |              |                 |          |       |

| R/W-0           | R/W-0                                                           | R/W-0          | R/W-0 | R/W-0        | R/W-0           | R/W-0    | R/W-0 |