#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 512KB (170K x 24)                                                               |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 24K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 6x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                  |

| Supplier Device Package    | 28-SOIC                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep512gp202t-e-so |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

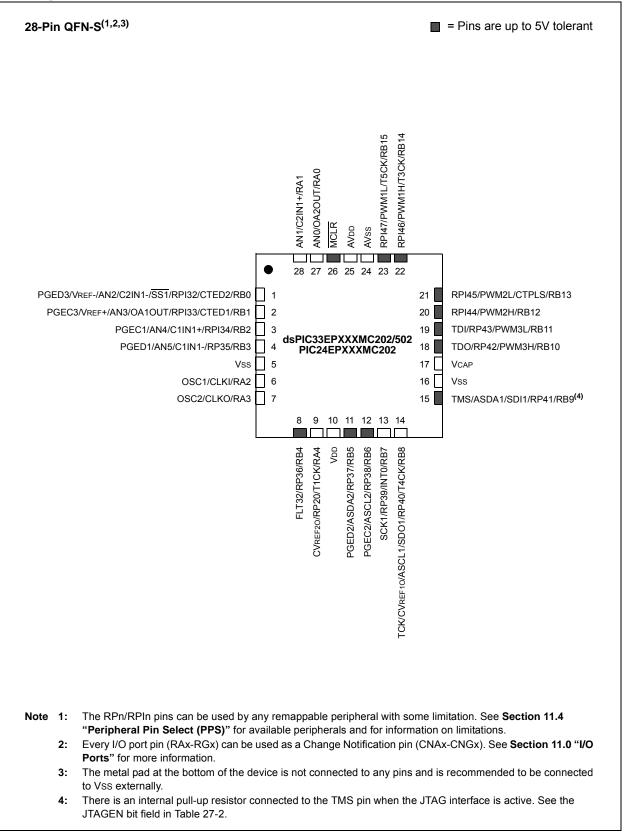

# Pin Diagrams (Continued)

# 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT DIGITAL SIGNAL CONTROLLERS AND MICROCONTROLLERS

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section of the "dsPIC33/PIC24 Familv Reference Manual", which is available from the Microchip web site (www.microchip.com)

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

# 2.1 Basic Connection Requirements

Getting started with the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins (regardless if ADC module is not used)

(see Section 2.2 "Decoupling Capacitors")

• VCAP

(see Section 2.3 "CPU Logic Filter Capacitor Connection (VCAP)")

- MCLR pin (see Section 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.5 "ICSP Pins**")

- OSC1 and OSC2 pins when external oscillator source is used

(see Section 2.6 "External Oscillator Pins")

Additionally, the following pins may be required:

• VREF+/VREF- pins are used when external voltage reference for the ADC module is implemented

Note: The AVDD and AVSS pins must be connected, independent of the ADC voltage reference source.

# 2.2 Decoupling Capacitors

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: Recommendation of 0.1  $\mu$ F (100 nF), 10-20V. This capacitor should be a low-ESR and have resonance frequency in the range of 20 MHz and higher. It is recommended to use ceramic capacitors.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high-frequency noise: If the board is experiencing high-frequency noise, above tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of  $0.01 \ \mu\text{F}$  to  $0.001 \ \mu\text{F}$ . Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example,  $0.1 \ \mu\text{F}$  in parallel with  $0.001 \ \mu\text{F}$ .

- **Maximizing performance:** On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB track inductance.

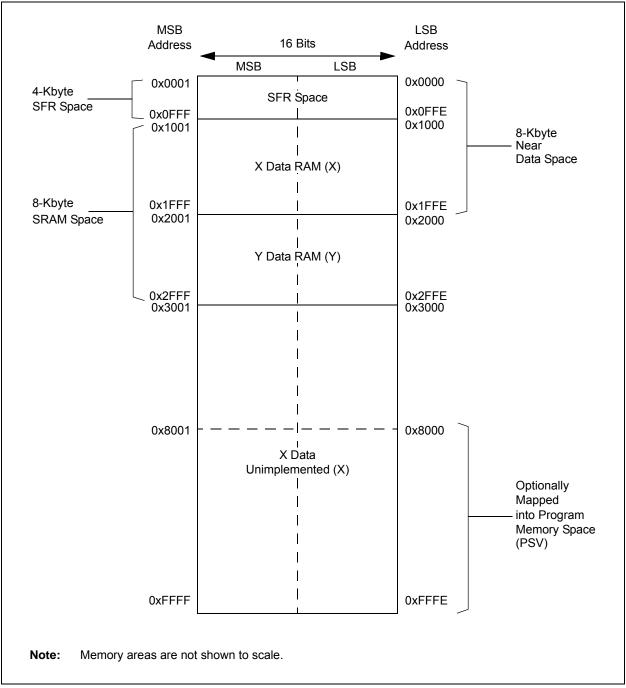

# FIGURE 4-8: DATA MEMORY MAP FOR dsPIC33EP64MC20X/50X AND dsPIC33EP64GP50X DEVICES

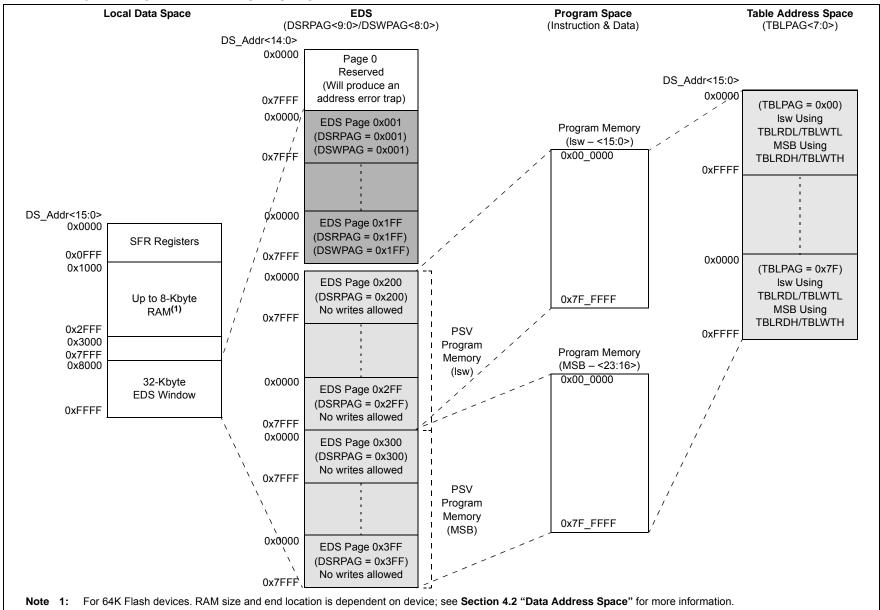

# EXAMPLE 4-3: PAGED DATA MEMORY SPACE

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

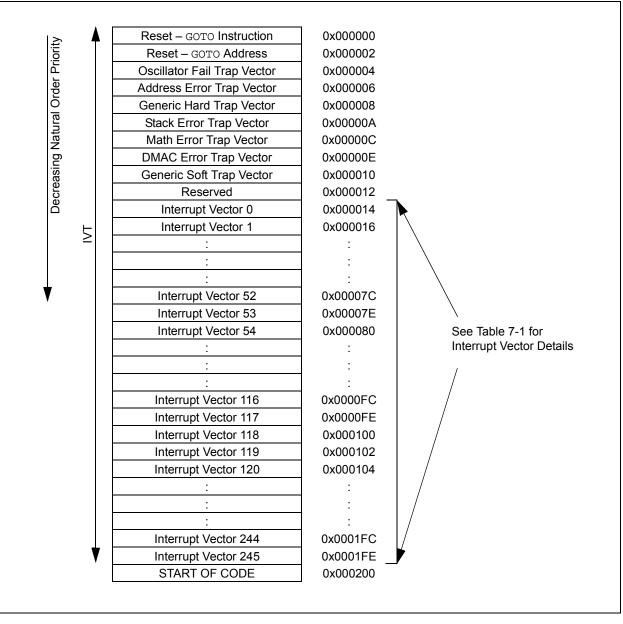

# FIGURE 7-1: dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X INTERRUPT VECTOR TABLE

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0                                                                  | U-0   | U-0              | U-0   | U-0              | U-0   | U-0             | U-0   |

|----------------------------------------------------------------------|-------|------------------|-------|------------------|-------|-----------------|-------|

| —                                                                    | —     | —                | —     | —                | —     | _               | —     |

| bit 15                                                               |       |                  |       |                  | •     |                 | bit 8 |

|                                                                      |       |                  |       |                  |       |                 |       |

| R/W-0                                                                | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0 | R/W-0           | R/W-0 |

|                                                                      |       |                  | STB<  | 23:16>           |       |                 |       |

| bit 7                                                                |       |                  |       |                  |       |                 | bit 0 |

|                                                                      |       |                  |       |                  |       |                 |       |

| Legend:                                                              |       |                  |       |                  |       |                 |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |       |                  |       |                  |       |                 |       |

| -n = Value at P                                                      | POR   | '1' = Bit is set |       | '0' = Bit is cle | eared | x = Bit is unkr | nown  |

|                                                                      |       |                  |       |                  |       |                 |       |

# REGISTER 8-5: DMAXSTBH: DMA CHANNEL X START ADDRESS REGISTER B (HIGH)

bit 15-8 Unimplemented: Read as '0'

bit 7-0 STB<23:16>: Secondary Start Address bits (source or destination)

# REGISTER 8-6: DMAXSTBL: DMA CHANNEL X START ADDRESS REGISTER B (LOW)

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|-----------------|-----------------|-------|

|                 |       |                  | STB   | <15:8>            |                 |                 |       |

| bit 15          |       |                  |       |                   |                 |                 | bit 8 |

|                 |       |                  |       |                   |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | STE   | 3<7:0>            |                 |                 |       |

| bit 7           |       |                  |       |                   |                 |                 | bit 0 |

| Legend:         |       |                  |       |                   |                 |                 |       |

| R = Readable    | bit   | W = Writable b   | bit   | U = Unimplen      | nented bit, rea | ad as '0'       |       |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is clea | ared            | x = Bit is unkı | nown  |

bit 15-0 **STB<15:0>:** Secondary Start Address bits (source or destination)

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

## REGISTER 8-9: DSADRH: DMA MOST RECENT RAM HIGH ADDRESS REGISTER

| U-0            | U-0 | U-0             | U-0   | U-0          | U-0              | U-0    | U-0   |

|----------------|-----|-----------------|-------|--------------|------------------|--------|-------|

| —              | —   | —               | —     | —            | —                | -      | —     |

| bit 15         |     |                 |       |              |                  |        | bit 8 |

|                |     |                 |       |              |                  |        |       |

| R-0            | R-0 | R-0             | R-0   | R-0          | R-0              | R-0    | R-0   |

|                |     |                 | DSADR | <23:16>      |                  |        |       |

| bit 7          |     |                 |       |              |                  |        | bit 0 |

|                |     |                 |       |              |                  |        |       |

| Legend:        |     |                 |       |              |                  |        |       |

| R = Readable b | it  | W = Writable bi | t     | U = Unimpler | nented bit, read | as '0' |       |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |  |

|-------------------|------------------|------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |  |

#### bit 15-8 Unimplemented: Read as '0'

bit 7-0 DSADR<23:16>: Most Recent DMA Address Accessed by DMA bits

#### REGISTER 8-10: DSADRL: DMA MOST RECENT RAM LOW ADDRESS REGISTER

| R-0              | R-0 | R-0              | R-0  | R-0                  | R-0         | R-0             | R-0   |

|------------------|-----|------------------|------|----------------------|-------------|-----------------|-------|

|                  |     |                  | DSAD | DR<15:8>             |             |                 |       |

| bit 15           |     |                  |      |                      |             |                 | bit 8 |

|                  |     |                  |      |                      |             |                 |       |

| R-0              | R-0 | R-0              | R-0  | R-0                  | R-0         | R-0             | R-0   |

|                  |     |                  | DSA  | DR<7:0>              |             |                 |       |

| bit 7            |     |                  |      |                      |             |                 | bit 0 |

|                  |     |                  |      |                      |             |                 |       |

| Legend:          |     |                  |      |                      |             |                 |       |

| R = Readable b   | it  | W = Writable bit |      | U = Unimplemen       | ted bit, re | ad as '0'       |       |

| -n = Value at PC | OR  | '1' = Bit is set |      | '0' = Bit is cleared | d           | x = Bit is unkn | own   |

bit 15-0 DSADR<15:0>: Most Recent DMA Address Accessed by DMA bits

| U-0          | R/W-0                                    | R/W-0                                                                        | R/W-0         | R/W-0             | R/W-0         | R/W-0           | R/W-0  |

|--------------|------------------------------------------|------------------------------------------------------------------------------|---------------|-------------------|---------------|-----------------|--------|

| —            |                                          |                                                                              |               | SCK2INR<6:0       | >             |                 |        |

| bit 15       |                                          |                                                                              |               |                   |               |                 | bit 8  |

|              |                                          |                                                                              |               |                   | 5444.6        | <b>D</b> 444 A  | 5444.6 |

| U-0          | R/W-0                                    | R/W-0                                                                        | R/W-0         | R/W-0             | R/W-0         | R/W-0           | R/W-0  |

|              |                                          |                                                                              |               | SDI2R<6:0>        |               |                 |        |

| bit 7        |                                          |                                                                              |               |                   |               |                 | bit 0  |

|              |                                          |                                                                              |               |                   |               |                 |        |

| Legend:      |                                          |                                                                              |               |                   |               |                 |        |

| R = Readab   |                                          | W = Writable                                                                 |               | U = Unimplen      |               |                 |        |

| -n = Value a | t POR                                    | '1' = Bit is set                                                             |               | '0' = Bit is clea | ared          | x = Bit is unkr | nown   |

|              |                                          | nput tied to RPI<br>nput tied to CMI<br>nput tied to Vss                     | P1            |                   |               |                 |        |

| bit 7        | Unimpleme                                | nted: Read as 'o                                                             | כי            |                   |               |                 |        |

| bit 6-0      | (see Table 1 <sup>^</sup><br>1111001 = I | : Assign SPI2 D<br>1-2 for input pin<br>nput tied to RPI<br>nput tied to CMI | selection num | ,                 | esponding RPi | ר Pin bits      |        |

# REGISTER 11-12: RPINR22: PERIPHERAL PIN SELECT INPUT REGISTER 22

NOTES:

| R/W-0              | U-0                  | R/W-0                 | U-0                   | U-0 | U-0 | U-0                  | U-0   |

|--------------------|----------------------|-----------------------|-----------------------|-----|-----|----------------------|-------|

| TON <sup>(1)</sup> | —                    | TSIDL <sup>(2)</sup>  | —                     | —   | —   | —                    | —     |

| bit 15             |                      |                       |                       |     |     |                      | bit 8 |

|                    |                      |                       |                       |     |     |                      |       |

| U-0                | R/W-0                | R/W-0                 | R/W-0                 | U-0 | U-0 | R/W-0                | U-0   |

| —                  | TGATE <sup>(1)</sup> | TCKPS1 <sup>(1)</sup> | TCKPS0 <sup>(1)</sup> |     | —   | TCS <sup>(1,3)</sup> | —     |

| bit 7              |                      |                       |                       |     |     |                      | bit 0 |

|                    |                      |                       |                       |     |     |                      |       |

# REGISTER 13-2: TyCON: (TIMER3 AND TIMER5) CONTROL REGISTER

| Legend:      |                                                                                                                                         |                                                                               |                                    |                                   |  |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|------------------------------------|-----------------------------------|--|--|--|

| R = Readal   | R = Readable bit W = Writable bit                                                                                                       |                                                                               | U = Unimplemented bit, read as '0' |                                   |  |  |  |

| -n = Value a | at POR                                                                                                                                  | '1' = Bit is set                                                              | '0' = Bit is cleared               | x = Bit is unknown                |  |  |  |

| bit 15       | TON: Tin                                                                                                                                | nery On bit <sup>(1)</sup>                                                    |                                    |                                   |  |  |  |

|              |                                                                                                                                         | s 16-bit Timery<br>s 16-bit Timery                                            |                                    |                                   |  |  |  |

| bit 14       | •                                                                                                                                       | mented: Read as '0'                                                           |                                    |                                   |  |  |  |

| bit 13       | -                                                                                                                                       | <b>TSIDL</b> : Timery Stop in Idle Mode bit <sup>(2)</sup>                    |                                    |                                   |  |  |  |

|              | <ul> <li>1 = Discontinues module operation when device enters Idle mode</li> <li>0 = Continues module operation in Idle mode</li> </ul> |                                                                               |                                    |                                   |  |  |  |

| bit 12-7     | Unimplemented: Read as '0'                                                                                                              |                                                                               |                                    |                                   |  |  |  |

| bit 6        | <b>TGATE:</b> Timery Gated Time Accumulation Enable bit <sup>(1)</sup>                                                                  |                                                                               |                                    |                                   |  |  |  |

|              | When TC<br>This bit is                                                                                                                  | <u>CS = 1:</u><br>s ignored.                                                  |                                    |                                   |  |  |  |

|              |                                                                                                                                         | <u>CS = 0:</u><br>d time accumulation is enab<br>d time accumulation is disab |                                    |                                   |  |  |  |

| bit 5-4      | TCKPS<                                                                                                                                  | 1:0>: Timery Input Clock Pre                                                  | escale Select bits <sup>(1)</sup>  |                                   |  |  |  |

|              | 11 <b>= 1:2</b> 5                                                                                                                       |                                                                               |                                    |                                   |  |  |  |

|              | 10 = 1:64<br>01 = 1:8                                                                                                                   | 1                                                                             |                                    |                                   |  |  |  |

|              | 01 = 1.8                                                                                                                                |                                                                               |                                    |                                   |  |  |  |

| bit 3-2      | Unimple                                                                                                                                 | mented: Read as '0'                                                           |                                    |                                   |  |  |  |

| bit 1        | -                                                                                                                                       | nery Clock Source Select bit                                                  | (1,3)                              |                                   |  |  |  |

|              |                                                                                                                                         | nal clock is from pin, TyCK (<br>nal clock (FP)                               | (on the rising edge)               |                                   |  |  |  |

| bit 0        | Unimple                                                                                                                                 | mented: Read as '0'                                                           |                                    |                                   |  |  |  |

|              |                                                                                                                                         | peration is enabled (T2CON<br>set through TxCON.                              | <3> = 1), these bits have no e     | ffect on Timery operation; all ti |  |  |  |

|              |                                                                                                                                         |                                                                               |                                    |                                   |  |  |  |

2: When 32-bit timer operation is enabled (T32 = 1) in the Timerx Control register (TxCON<3>), the TSIDL bit must be cleared to operate the 32-bit timer in Idle mode.

3: The TyCK pin is not available on all timers. See the "Pin Diagrams" section for the available pins.

# 16.0 HIGH-SPEED PWM MODULE (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "High-Speed PWM" (DS70645) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices support a dedicated Pulse-Width Modulation (PWM) module with up to 6 outputs.

The high-speed PWMx module consists of the following major features:

- Three PWM generators

- Two PWM outputs per PWM generator

- Individual period and duty cycle for each PWM pair

- Duty cycle, dead time, phase shift and frequency resolution of Tcy/2 (7.14 ns at Fcy = 70MHz)

- Independent Fault and current-limit inputs for six PWM outputs

- · Redundant output

- Center-Aligned PWM mode

- Output override control

- Chop mode (also known as Gated mode)

- Special Event Trigger

- Prescaler for input clock

- PWMxL and PWMxH output pin swapping

- Independent PWM frequency, duty cycle and phase-shift changes for each PWM generator

- Dead-time compensation

- Enhanced Leading-Edge Blanking (LEB) functionality

- Frequency resolution enhancement

- PWM capture functionality

**Note:** In Edge-Aligned PWM mode, the duty cycle, dead time, phase shift and frequency resolution are 8.32 ns.

The high-speed PWMx module contains up to three PWM generators. Each PWM generator provides two PWM outputs: PWMxH and PWMxL. The master time base generator provides a synchronous signal as a common time base to synchronize the various PWM outputs. The individual PWM outputs are available on the output pins of the device. The input Fault signals and current-limit signals, when enabled, can monitor and protect the system by placing the PWM outputs into a known "safe" state.

Each PWMx can generate a trigger to the ADC module to sample the analog signal at a specific instance during the PWM period. In addition, the high-speed PWMx module also generates a Special Event Trigger to the ADC module based on either of the two master time bases.

The high-speed PWMx module can synchronize itself with an external signal or can act as a synchronizing source to any external device. The SYNCI1 input pin that utilizes PPS, can synchronize the high-speed PWMx module with an external signal. The SYNC01 pin is an output pin that provides a synchronous signal to an external device.

Figure 16-1 illustrates an architectural overview of the high-speed PWMx module and its interconnection with the CPU and other peripherals.

# 16.1 PWM Faults

The PWMx module incorporates multiple external Fault inputs to include FLT1 and FLT2 which are remappable using the PPS feature, FLT3 and FLT4 which are available only on the larger 44-pin and 64-pin packages, and FLT32 which has been implemented with Class B safety features, and is available on a fixed pin on all dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

These Faults provide a safe and reliable way to safely shut down the PWM outputs when the Fault input is asserted.

# 16.1.1 PWM FAULTS AT RESET

During any Reset event, the PWMx module maintains ownership of the Class B Fault, FLT32. At Reset, this Fault is enabled in Latched mode to ensure the fail-safe power-up of the application. The application software must clear the PWM Fault before enabling the highspeed motor control PWMx module. To clear the Fault condition, the FLT32 pin must first be pulled low externally or the internal pull-down resistor in the CNPDx register can be enabled.

Note: The Fault mode may be changed using the FLTMOD<1:0> bits (FCLCON<1:0>), regardless of the state of FLT32.

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| RXOVF15 | RXOVF14 | RXOVF13 | RXOVF12 | RXOVF11 | RXOVF10 | RXOVF9 | RXOVF8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

|         |         |         |         |         |         |        |        |

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

# REGISTER 21-24: CxRXOVF1: ECANx RECEIVE BUFFER OVERFLOW REGISTER 1

RXOVF4

| bit 7            |                          |                                         | bit 0 |

|------------------|--------------------------|-----------------------------------------|-------|

|                  |                          |                                         |       |

| Legend:          | C = Writable bit, but or | nly '0' can be written to clear the bit |       |

| R = Readable bit | W = Writable bit         | U = Unimplemented bit, read as '0'      |       |

RXOVF3

RXOVF2

| R = Readable bit  | vv = vvritable bit | U = Unimplemented bit, read | d as 0             |

|-------------------|--------------------|-----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set   | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-0 RXOVF<15:0>: Receive Buffer n Overflow bits

RXOVF6

RXOVF7

1 = Module attempted to write to a full buffer (set by module)

0 = No overflow condition (cleared by user software)

RXOVF5

#### REGISTER 21-25: CxRXOVF2: ECANx RECEIVE BUFFER OVERFLOW REGISTER 2

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXOVF31 | RXOVF30 | RXOVF29 | RXOVF28 | RXOVF27 | RXOVF26 | RXOVF25 | RXOVF24 |

| bit 15  |         |         |         |         |         |         | bit 8   |

| R/C-0       | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   |  |

|-------------|---------|---------|---------|---------|---------|---------|---------|--|

| RXOVF23     | RXOVF22 | RXOVF21 | RXOVF20 | RXOVF19 | RXOVF18 | RXOVF17 | RXOVF16 |  |

| bit 7 bit 0 |         |         |         |         |         |         |         |  |

| Legend:                           | C = Writable bit, but or | C = Writable bit, but only '0' can be written to clear the bit |                    |  |  |  |  |

|-----------------------------------|--------------------------|----------------------------------------------------------------|--------------------|--|--|--|--|

| R = Readable bit W = Writable bit |                          | U = Unimplemented bit, read as '0'                             |                    |  |  |  |  |

| -n = Value at POR                 | '1' = Bit is set         | '0' = Bit is cleared                                           | x = Bit is unknown |  |  |  |  |

bit 15-0 RXOVF<31:16>: Receive Buffer n Overflow bits

1 = Module attempted to write to a full buffer (set by module)

0 = No overflow condition (cleared by user software)

RXOVF0

RXOVF1

# 23.2 ADC Helpful Tips

- 1. The SMPIx control bits in the AD1CON2 register:

- a) Determine when the ADC interrupt flag is set and an interrupt is generated, if enabled.

- b) When the CSCNA bit in the AD1CON2 registers is set to '1', this determines when the ADC analog scan channel list, defined in the AD1CSSL/AD1CSSH registers, starts over from the beginning.

- c) When the DMA peripheral is not used (ADDMAEN = 0), this determines when the ADC Result Buffer Pointer to ADC1BUF0-ADC1BUFF gets reset back to the beginning at ADC1BUF0.

- d) When the DMA peripheral is used (ADDMAEN = 1), this determines when the DMA Address Pointer is incremented after a sample/conversion operation. ADC1BUF0 is the only ADC buffer used in this mode. The ADC Result Buffer Pointer to ADC1BUF0-ADC1BUFF gets reset back to the beginning at ADC1BUF0. The DMA address is incremented after completion of every 32nd sample/conversion operation. Conversion results are stored in the ADC1BUF0 register for transfer to RAM using DMA.

- 2. When the DMA module is disabled (ADDMAEN = 0), the ADC has 16 result buffers. ADC conversion results are stored sequentially in ADC1BUF0-ADC1BUFF, regardless of which analog inputs are being used subject to the SMPIx bits and the condition described in 1c) above. There is no relationship between the ANx input being measured and which ADC buffer (ADC1BUF0-ADC1BUFF) that the conversion results will be placed in.

- 3. When the DMA module is enabled (ADDMAEN = 1), the ADC module has only 1 ADC result buffer (i.e., ADC1BUF0) per ADC peripheral and the ADC conversion result must be read, either by the CPU or DMA Controller, before the next ADC conversion is complete to avoid overwriting the previous value.

- 4. The DONE bit (AD1CON1<0>) is only cleared at the start of each conversion and is set at the completion of the conversion, but remains set indefinitely, even through the next sample phase until the next conversion begins. If application code is monitoring the DONE bit in any kind of software loop, the user must consider this behavior because the CPU code execution is faster than the ADC. As a result, in Manual Sample mode, particularly where the user's code is setting the SAMP bit (AD1CON1<1>), the DONE bit should also be cleared by the user application just before setting the SAMP bit.

5. Enabling op amps, comparator inputs and external voltage references can limit the availability of analog inputs (ANx pins). For example, when Op Amp 2 is enabled, the pins for ANO, AN1 and AN2 are used by the op amp's inputs and output. This negates the usefulness of Alternate Input mode since the MUXA selections use AN0-AN2. Carefully study the ADC block diagram to determine the configuration that will best suit your application. Configuration examples are available in the "Analog-to-Digital Converter (ADC)" (DS70621) section in the "dsPIC33/ PIC24 Family Reference Manual".

# 23.3 ADC Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser:<br>http://www.microchip.com/wwwproducts/ |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | Devices.aspx?dDocName=en555464                                                                                                                          |

# 23.3.1 KEY RESOURCES

- "Analog-to-Digital Converter (ADC)" (DS70621) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

| bit 3-0 | Step<br>Command        | OPTION<3:0> | Option Description                                          |  |  |  |  |

|---------|------------------------|-------------|-------------------------------------------------------------|--|--|--|--|

|         | PTGWHI(1)              | 0000        | PWM Special Event Trigger. <sup>(3)</sup>                   |  |  |  |  |

|         | or (1)                 | 0001        | PWM master time base synchronization output. <sup>(3)</sup> |  |  |  |  |

|         | PTGWLO(1)              | 0010        | PWM1 interrupt. <sup>(3)</sup>                              |  |  |  |  |

|         |                        | 0011        | PWM2 interrupt. <sup>(3)</sup>                              |  |  |  |  |

|         |                        | 0100        | PWM3 interrupt. <sup>(3)</sup>                              |  |  |  |  |

|         |                        | 0101        | Reserved.                                                   |  |  |  |  |

|         |                        | 0110        | Reserved.                                                   |  |  |  |  |

|         |                        | 0111        | OC1 Trigger event.                                          |  |  |  |  |

|         |                        | 1000        | OC2 Trigger event.                                          |  |  |  |  |

|         |                        | 1001        | IC1 Trigger event.                                          |  |  |  |  |

|         |                        | 1010        | CMP1 Trigger event.                                         |  |  |  |  |

|         |                        | 1011        | CMP2 Trigger event.                                         |  |  |  |  |

|         |                        | 1100        | CMP3 Trigger event.                                         |  |  |  |  |

|         |                        | 1101        | CMP4 Trigger event.                                         |  |  |  |  |

|         |                        | 1110        | ADC conversion done interrupt.                              |  |  |  |  |

|         |                        | 1111        | INT2 external interrupt.                                    |  |  |  |  |

|         | PTGIRQ(1)              | 0000        | Generate PTG Interrupt 0.                                   |  |  |  |  |

|         |                        | 0001        | Generate PTG Interrupt 1.                                   |  |  |  |  |

|         |                        | 0010        | Generate PTG Interrupt 2.                                   |  |  |  |  |

|         |                        | 0011        | Generate PTG Interrupt 3.                                   |  |  |  |  |

|         |                        | 0100        | Reserved.                                                   |  |  |  |  |

|         |                        | •           | •                                                           |  |  |  |  |

|         |                        | •           | •                                                           |  |  |  |  |

|         |                        | •           | •                                                           |  |  |  |  |

|         | (2)                    | 1111        | Reserved.                                                   |  |  |  |  |

|         | PTGTRIG <sup>(2)</sup> | 00000       | PTGO0.                                                      |  |  |  |  |

|         |                        | 00001       | PTGO1.                                                      |  |  |  |  |

|         |                        | •           | •                                                           |  |  |  |  |

|         |                        | •           | •                                                           |  |  |  |  |

|         |                        | •           | •                                                           |  |  |  |  |

|         |                        | 11110       | PTGO30.                                                     |  |  |  |  |

|         |                        | 11111       | PTGO31.                                                     |  |  |  |  |

TABLE 24-1: PTG STEP COMMAND FORMAT (CONTINUED)

Note 1: All reserved commands or options will execute but have no effect (i.e., execute as a NOP instruction).

2: Refer to Table 24-2 for the trigger output descriptions.

3: This feature is only available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

# **30.0 ELECTRICAL CHARACTERISTICS**

This section provides an overview of dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X electrical characteristics. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X family are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these or any other conditions above the parameters indicated in the operation listings of this specification is not implied.

# Absolute Maximum Ratings<sup>(1)</sup>

| Ambient temperature under bias                                                    | 40°C to +125°C       |

|-----------------------------------------------------------------------------------|----------------------|

| Storage temperature                                                               | 65°C to +150°C       |

| Voltage on VDD with respect to Vss                                                | -0.3V to +4.0V       |

| Voltage on any pin that is not 5V tolerant, with respect to Vss <sup>(3)</sup>    | 0.3V to (VDD + 0.3V) |

| Voltage on any 5V tolerant pin with respect to Vss when $VDD \ge 3.0V^{(3)}$      | 0.3V to +5.5V        |

| Voltage on any 5V tolerant pin with respect to Vss when VDD < 3.0V <sup>(3)</sup> | -0.3V to +3.6V       |

| Maximum current out of Vss pin                                                    |                      |

| Maximum current into Vod pin <sup>(2)</sup>                                       |                      |

| Maximum current sunk/sourced by any 4x I/O pin                                    | 15 mA                |

| Maximum current sunk/sourced by any 8x I/O pin                                    | 25 mA                |

| Maximum current sunk by all ports <sup>(2,4)</sup>                                | 200 mA               |

- **Note 1:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

- 2: Maximum allowable current is a function of device maximum power dissipation (see Table 30-2).

- 3: See the "Pin Diagrams" section for the 5V tolerant pins.

- 4: Exceptions are: dsPIC33EPXXXGP502, dsPIC33EPXXXMC202/502 and PIC24EPXXXGP/MC202 devices, which have a maximum sink/source capability of 130 mA.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| TABLE 30-23: TIME | 1 EXTERNAL CLOCK TIMING REQUI | REMENTS <sup>(1)</sup> |

|-------------------|-------------------------------|------------------------|

|-------------------|-------------------------------|------------------------|

| AC CHARACTERISTICS |           |                                                                                                    | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                                        |      |               |       |                                                                             |

|--------------------|-----------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|------|---------------|-------|-----------------------------------------------------------------------------|

| Param<br>No.       | Symbol    | Characteristic <sup>(2)</sup>                                                                      |                                                                                                                                                                                                                                                                                         | Min.                                   | Тур. | Max.          | Units | Conditions                                                                  |

| TA10               | ТтхН      | T1CK High<br>Time                                                                                  | Synchronous<br>mode                                                                                                                                                                                                                                                                     | Greater of:<br>20 or<br>(Tcy + 20)/N   |      | _             | ns    | Must also meet<br>Parameter TA15,<br>N = prescaler value<br>(1, 8, 64, 256) |

|                    |           |                                                                                                    | Asynchronous                                                                                                                                                                                                                                                                            | 35                                     | _    | —             | ns    |                                                                             |

| TA11               | ΤτχL      | T1CK Low<br>Time                                                                                   | Synchronous<br>mode                                                                                                                                                                                                                                                                     | Greater of:<br>20 or<br>(Tcy + 20)/N   |      | _             | ns    | Must also meet<br>Parameter TA15,<br>N = prescaler value<br>(1, 8, 64, 256) |

|                    |           |                                                                                                    | Asynchronous                                                                                                                                                                                                                                                                            | 10                                     | _    | _             | ns    |                                                                             |

| TA15               | ΤτχΡ      | T1CK Input<br>Period                                                                               | Synchronous mode                                                                                                                                                                                                                                                                        | Greater of:<br>40 or<br>(2 Tcy + 40)/N | _    | _             | ns    | N = prescale value<br>(1, 8, 64, 256)                                       |

| OS60               | Ft1       | T1CK Oscillator Input<br>Frequency Range (oscillator<br>enabled by setting bit, TCS<br>(T1CON<1>)) |                                                                                                                                                                                                                                                                                         | DC                                     |      | 50            | kHz   |                                                                             |

| TA20               | TCKEXTMRL | Delay from External T1CK<br>Clock Edge to Timer<br>Increment                                       |                                                                                                                                                                                                                                                                                         | 0.75 Tcy + 40                          | —    | 1.75 Tcy + 40 | ns    |                                                                             |

**Note 1:** Timer1 is a Type A.

2: These parameters are characterized, but are not tested in manufacturing.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

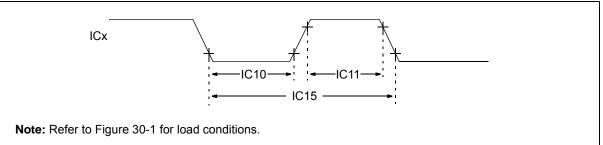

# FIGURE 30-6: INPUT CAPTURE x (ICx) TIMING CHARACTERISTICS

# TABLE 30-26: INPUT CAPTURE x MODULE TIMING REQUIREMENTS

| AC CHARACTERISTICS                                  |      |                     | $\begin{array}{ll} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |       |                                  |                                  |  |

|-----------------------------------------------------|------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|----------------------------------|----------------------------------|--|

| Param.<br>No. Symbol Characteristics <sup>(1)</sup> |      |                     | Min.                                                                                                                                                                                                                                                                                     | Max. | Units | Conditions                       |                                  |  |

| IC10                                                | TccL | ICx Input Low Time  | Greater of<br>12.5 + 25 or<br>(0.5 Tcy/N) + 25                                                                                                                                                                                                                                           |      | ns    | Must also meet<br>Parameter IC15 |                                  |  |

| IC11                                                | ТссН | ICx Input High Time | Greater of<br>12.5 + 25 or<br>(0.5 Tcy/N) + 25                                                                                                                                                                                                                                           | —    | ns    | Must also meet<br>Parameter IC15 | N = prescale value<br>(1, 4, 16) |  |

| IC15                                                | TccP | ICx Input Period    | Greater of<br>25 + 50<br>or<br>(1 Tcy/N) + 50                                                                                                                                                                                                                                            | _    | ns    |                                  |                                  |  |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

# TABLE 30-54: OP AMP/COMPARATOR VOLTAGE REFERENCE SETTLING TIME SPECIFICATIONS

| AC CHARACTERISTICS |        |                | $\begin{array}{l} \mbox{Standard Operating Conditions (see Note 2): 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |      |       |            |

|--------------------|--------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|------------|

| Param.             | Symbol | Characteristic | Min.                                                                                                                                                                                                                                                                                                 | Тур. | Max. | Units | Conditions |

| VR310              | TSET   | Settling Time  | —                                                                                                                                                                                                                                                                                                    | 1    | 10   | μS    | (Note 1)   |

**Note 1:** Settling time is measured while CVRR = 1 and CVR<3:0> bits transition from '0000' to '1111'.

2: Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

#### TABLE 30-55: OP AMP/COMPARATOR VOLTAGE REFERENCE SPECIFICATIONS

| DC CHARACTERISTICS |        |                                            | $\begin{array}{l} \mbox{Standard Operating Conditions (see Note 1): 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |            |     |               |  |  |

|--------------------|--------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------|-----|---------------|--|--|

| Param<br>No.       | Symbol | Characteristics                            | Min. Typ. Max. Units Condition                                                                                                                                                                                                                                                                     |      |            |     |               |  |  |

| VRD310             | CVRES  | Resolution                                 | CVRSRC/24                                                                                                                                                                                                                                                                                          | _    | CVRSRC/32  | LSb |               |  |  |

| VRD311             | CVRAA  | Absolute Accuracy <sup>(2)</sup>           | —                                                                                                                                                                                                                                                                                                  | ±25  | _          | mV  | CVRSRC = 3.3V |  |  |

| VRD313             | CVRSRC | Input Reference Voltage                    | 0                                                                                                                                                                                                                                                                                                  | _    | AVDD + 0.3 | V   |               |  |  |

| VRD314             | CVRout | Buffer Output<br>Resistance <sup>(2)</sup> | _                                                                                                                                                                                                                                                                                                  | 1.5k | _          | Ω   |               |  |  |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

2: Parameter is characterized but not tested in manufacturing.

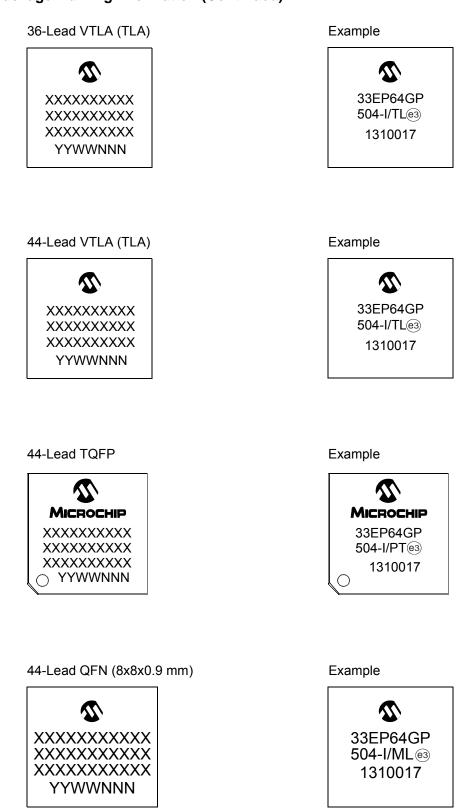

## 33.1 Package Marking Information (Continued)

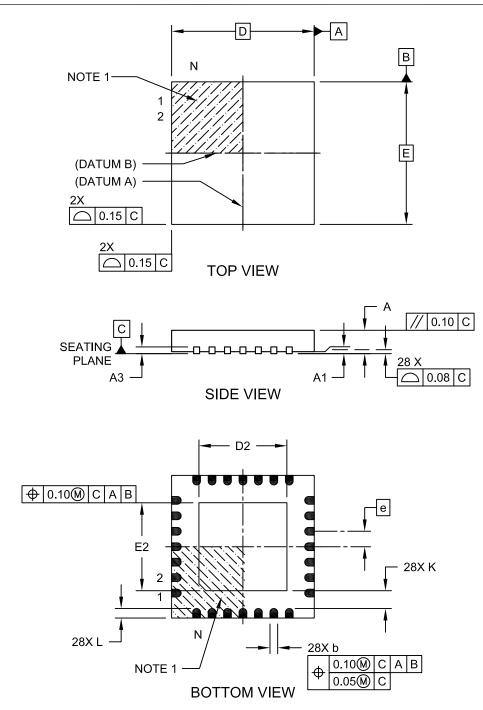

# 28-Lead Plastic Quad Flat, No Lead Package (MM) - 6x6x0.9mm Body [QFN-S] With 0.40 mm Terminal Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-124C Sheet 1 of 2