#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 512KB (170K x 24)                                                               |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | ·                                                                               |

| RAM Size                   | 24K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 6x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                  |

| Supplier Device Package    | 28-SOIC                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep512gp202t-i-so |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

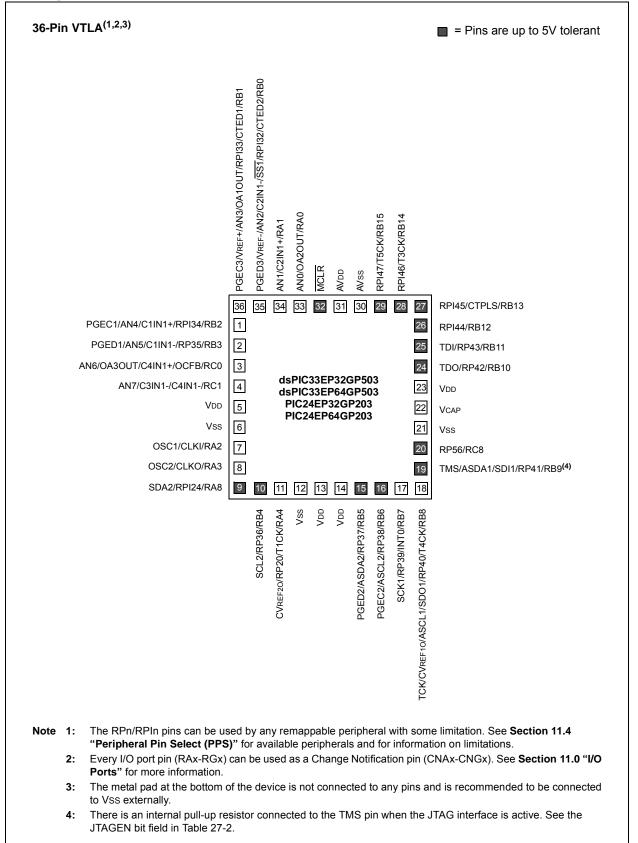

#### **Pin Diagrams (Continued)**

| TABLE 1-1: PINC                           |             | O DESC         | RIPT | IONS (CONTINUED)                                                                 |

|-------------------------------------------|-------------|----------------|------|----------------------------------------------------------------------------------|

| Pin Name <sup>(4)</sup>                   | Pin<br>Type | Buffer<br>Type | PPS  | Description                                                                      |

| U2CTS                                     | Ι           | ST             | No   | UART2 Clear-To-Send.                                                             |

| U2RTS                                     | 0           | —              | No   | UART2 Ready-To-Send.                                                             |

| U2RX                                      | Ι           | ST             | Yes  | UART2 receive.                                                                   |

| U2TX                                      | 0           | —              | Yes  | UART2 transmit.                                                                  |

| BCLK2                                     | 0           | ST             | No   | UART2 IrDA <sup>®</sup> baud clock output.                                       |

| SCK1                                      | I/O         | ST             | No   | Synchronous serial clock input/output for SPI1.                                  |

| SDI1                                      | I           | ST             | No   | SPI1 data in.                                                                    |

| SDO1                                      | 0           | —              | No   | SPI1 data out.                                                                   |

| SS1                                       | I/O         | ST             | No   | SPI1 slave synchronization or frame pulse I/O.                                   |

| SCK2                                      | I/O         | ST             | Yes  | Synchronous serial clock input/output for SPI2.                                  |

| SDI2                                      | I           | ST             | Yes  | SPI2 data in.                                                                    |

| SDO2                                      | 0           | _              | Yes  | SPI2 data out.                                                                   |

| SS2                                       | I/O         | ST             | Yes  | SPI2 slave synchronization or frame pulse I/O.                                   |

| SCL1                                      | I/O         | ST             | No   | Synchronous serial clock input/output for I2C1.                                  |

| SDA1                                      | I/O         | ST             | No   | Synchronous serial data input/output for I2C1.                                   |

| ASCL1                                     | I/O         | ST             | No   | Alternate synchronous serial clock input/output for I2C1.                        |

| ASDA1                                     | I/O         | ST             | No   | Alternate synchronous serial data input/output for I2C1.                         |

| SCL2                                      | I/O         | ST             | No   | Synchronous serial clock input/output for I2C2.                                  |

| SDA2                                      | I/O         | ST             | No   | Synchronous serial data input/output for I2C2.                                   |

| ASCL2                                     | I/O         | ST             | No   | Alternate synchronous serial clock input/output for I2C2.                        |

| ASDA2                                     | I/O         | ST             | No   | Alternate synchronous serial data input/output for I2C2.                         |

| TMS <sup>(5)</sup>                        | Ι           | ST             | No   | JTAG Test mode select pin.                                                       |

| TCK                                       | Ι           | ST             | No   | JTAG test clock input pin.                                                       |

| TDI                                       | I           | ST             | No   | JTAG test data input pin.                                                        |

| TDO                                       | 0           | _              | No   | JTAG test data output pin.                                                       |

| C1RX <sup>(2)</sup>                       | Ι           | ST             | Yes  | ECAN1 bus receive pin.                                                           |

| C1TX <sup>(2)</sup>                       | 0           | _              | Yes  | ECAN1 bus transmit pin.                                                          |

| FLT1 <sup>(1)</sup> , FLT2 <sup>(1)</sup> | Ι           | ST             | Yes  | PWM Fault Inputs 1 and 2.                                                        |

| FLT3 <sup>(1)</sup> , FLT4 <sup>(1)</sup> | Ι           | ST             | No   | PWM Fault Inputs 3 and 4.                                                        |

| FLT32 <sup>(1,3)</sup>                    | Ι           | ST             | No   | PWM Fault Input 32 (Class B Fault).                                              |

| DTCMP1-DTCMP3 <sup>(1)</sup>              | Ι           | ST             | Yes  | PWM Dead-Time Compensation Inputs 1 through 3.                                   |

| PWM1L-PWM3L <sup>(1)</sup>                | 0           | —              | No   | PWM Low Outputs 1 through 3.                                                     |

| PWM1H-PWM3H <sup>(1)</sup>                | 0           | —              | No   | PWM High Outputs 1 through 3.                                                    |

| SYNCI1 <sup>(1)</sup>                     | Ι           | ST             |      | PWM Synchronization Input 1.                                                     |

| SYNCO1 <sup>(1)</sup>                     | 0           |                | Yes  | PWM Synchronization Output 1.                                                    |

| INDX1 <sup>(1)</sup>                      | Ι           | ST             | Yes  | Quadrature Encoder Index1 pulse input.                                           |

| HOME1 <sup>(1)</sup>                      | Ι           | ST             | Yes  | Quadrature Encoder Home1 pulse input.                                            |

| QEA1 <sup>(1)</sup>                       | Ι           | ST             | Yes  | Quadrature Encoder Phase A input in QEI1 mode. Auxiliary timer                   |

| QEB1 <sup>(1)</sup>                       | ,           | ст             | Vee  | external clock/gate input in Timer mode.                                         |

|                                           | Ι           | ST             | Yes  | Quadrature Encoder Phase B input in QEI1 mode. Auxiliary timer                   |

| CNTCMP1 <sup>(1)</sup>                    | 0           |                | Yes  | external clock/gate input in Timer mode.<br>Quadrature Encoder Compare Output 1. |

|                                           | 0           | <br>ompatible  | 162  |                                                                                  |

# TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

Legend:

CMOS = CMOS compatible input or output

Analog = Analog input

ST = Schmitt Trigger input with CMOS levels

O = Output

PPS = Peripheral Pin Select

TTL = TTL input buffer

P = Power I = Input

Note 1: This pin is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This pin is available on dsPIC33EPXXXGP/MC50X devices only.

3: This is the default Fault on Reset for dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices. See Section 16.0 "High-Speed PWM Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)" for more information.

4: Not all pins are available in all packages variants. See the "Pin Diagrams" section for pin availability.

5: There is an internal pull-up resistor connected to the TMS pin when the JTAG interface is active. See the JTAGEN bit field in Table 27-2.

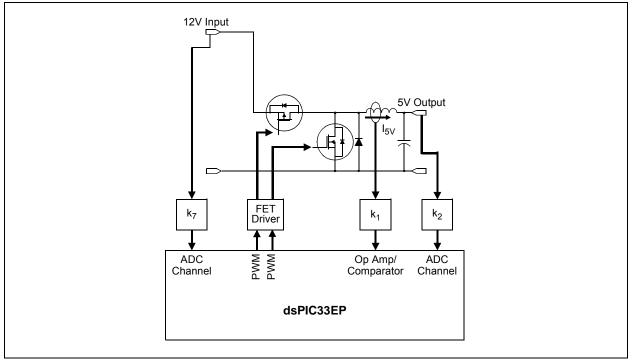

#### FIGURE 2-5: SINGLE-PHASE SYNCHRONOUS BUCK CONVERTER

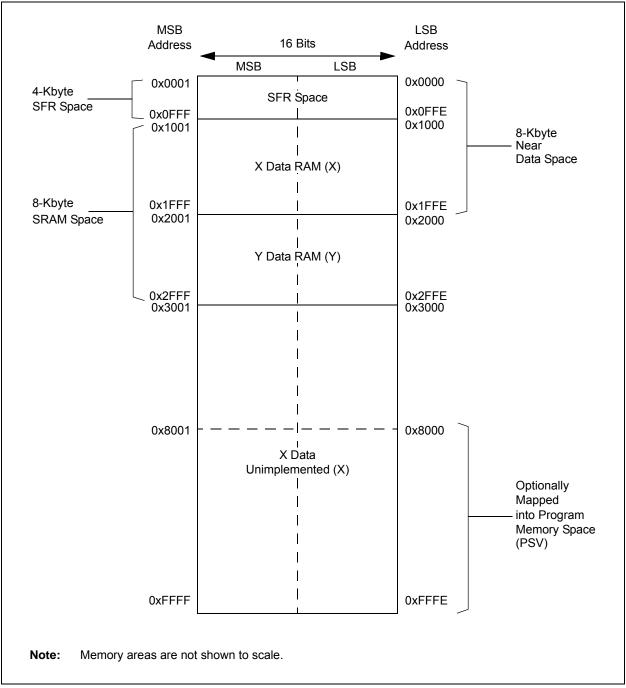

# FIGURE 4-8: DATA MEMORY MAP FOR dsPIC33EP64MC20X/50X AND dsPIC33EP64GP50X DEVICES

|             |       |                   |                                                            |        |        |        |        | •            |             |               |              |       |        |       |       |       |       |               |

|-------------|-------|-------------------|------------------------------------------------------------|--------|--------|--------|--------|--------------|-------------|---------------|--------------|-------|--------|-------|-------|-------|-------|---------------|

| SFR<br>Name | Addr. | Bit 15            | Bit 14                                                     | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9        | Bit 8       | Bit 7         | Bit 6        | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| TMR1        | 0100  |                   |                                                            |        |        |        |        |              | Timer1      | Register      |              |       |        |       |       |       |       | xxxx          |

| PR1         | 0102  |                   |                                                            |        |        |        |        |              | Period F    | Register 1    |              |       |        |       |       |       |       | FFFF          |

| T1CON       | 0104  | TON               | _                                                          | TSIDL  | _      | _      | _      | _            | _           | _             | TGATE        | TCKP  | S<1:0> | —     | TSYNC | TCS   |       | 0000          |

| TMR2        | 0106  |                   | Timer2 Register                                            |        |        |        |        |              |             |               |              |       | xxxx   |       |       |       |       |               |

| TMR3HLD     | 0108  |                   | Timer3 Holding Register (for 32-bit timer operations only) |        |        |        |        |              |             |               |              | xxxx  |        |       |       |       |       |               |

| TMR3        | 010A  |                   | Timer3 Register                                            |        |        |        |        |              |             |               |              | xxxx  |        |       |       |       |       |               |

| PR2         | 010C  |                   | Period Register 2                                          |        |        |        |        |              |             |               |              | FFFF  |        |       |       |       |       |               |

| PR3         | 010E  |                   | Period Register 3                                          |        |        |        |        |              |             |               |              | FFFF  |        |       |       |       |       |               |

| T2CON       | 0110  | TON               | —                                                          | TSIDL  | —      | —      | —      | _            | —           | —             | TGATE        | TCKP  | S<1:0> | T32   | _     | TCS   |       | 0000          |

| T3CON       | 0112  | TON               | -                                                          | TSIDL  | _      | _      | _      | _            | _           | _             | TGATE        | TCKP  | S<1:0> | _     | _     | TCS   |       | 0000          |

| TMR4        | 0114  |                   |                                                            | •      | •      | •      | •      | •            | Timer4      | Register      |              |       |        | •     |       | •     | •     | xxxx          |

| TMR5HLD     | 0116  |                   |                                                            |        |        |        | Т      | imer5 Holdir | ng Register | (for 32-bit o | perations on | ly)   |        |       |       |       |       | xxxx          |

| TMR5        | 0118  |                   | Timer5 Register                                            |        |        |        |        |              |             |               | xxxx         |       |        |       |       |       |       |               |

| PR4         | 011A  |                   | Period Register 4                                          |        |        |        |        |              |             |               | FFFF         |       |        |       |       |       |       |               |

| PR5         | 011C  | Period Register 5 |                                                            |        |        |        |        |              |             |               | FFFF         |       |        |       |       |       |       |               |

| T4CON       | 011E  | TON               | —                                                          | TSIDL  | —      | —      | —      | _            | _           | —             | TGATE        | TCKP  | S<1:0> | T32   | —     | TCS   | —     | 0000          |

| T5CON       | 0120  | TON               | _                                                          | TSIDL  | _      | _      | _      | _            | _           | _             | TGATE        | TCKP  | S<1:0> | _     | _     | TCS   | _     | 0000          |

## TABLE 4-8: TIMER1 THROUGH TIMER5 REGISTER MAP

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| IABLE 4   | -14:  | PVVIVI G | ENERA  | IUR Z R | EGIST                                                 |                                             | FOR as  | PIC33EP |            | 202/202  |         | 16246   | PXXX    |       |          | CES ONL | _ T   |               |

|-----------|-------|----------|--------|---------|-------------------------------------------------------|---------------------------------------------|---------|---------|------------|----------|---------|---------|---------|-------|----------|---------|-------|---------------|

| File Name | Addr. | Bit 15   | Bit 14 | Bit 13  | Bit 12                                                | Bit 11                                      | Bit 10  | Bit 9   | Bit 8      | Bit 7    | Bit 6   | Bit 5   | Bit 4   | Bit 3 | Bit 2    | Bit 1   | Bit 0 | All<br>Resets |

| PWMCON2   | 0C40  | FLTSTAT  | CLSTAT | TRGSTAT | FLTIEN                                                | CLIEN                                       | TRGIEN  | ITB     | MDCS       | DTC      | <1:0>   | DTCP    | _       | MTBS  | CAM      | XPRES   | IUE   | 0000          |

| IOCON2    | 0C42  | PENH     | PENL   | POLH    | POLL                                                  | PMOD                                        | 0<1:0>  | OVRENH  | OVRENL     | OVRDA    | \T<1:0> | FLTD    | \T<1:0> | CLDA  | AT<1:0>  | SWAP    | OSYNC | C000          |

| FCLCON2   | 0C44  | _        |        | (       | CLSRC<4:0> CLPOL CLMOD FLTSRC<4:0> FLTPOL FLTMOD<1:0> |                                             |         |         |            |          |         |         | D<1:0>  | 00F8  |          |         |       |               |

| PDC2      | 0C46  |          |        |         | PDC2<15:0> 0                                          |                                             |         |         |            |          |         |         |         |       | 0000     |         |       |               |

| PHASE2    | 0C48  |          |        |         | PHASE2<15:0> 0                                        |                                             |         |         |            |          |         |         |         |       |          | 0000    |       |               |

| DTR2      | 0C4A  | _        | _      |         | DTR2<13:0> 00                                         |                                             |         |         |            |          |         |         |         |       | 0000     |         |       |               |

| ALTDTR2   | 0C4C  | _        | _      |         |                                                       |                                             |         |         | AL         | TDTR2<13 | :0>     |         |         |       |          |         |       | 0000          |

| TRIG2     | 0C52  |          |        |         |                                                       |                                             |         | TI      | RGCMP<15:0 | )>       |         |         |         |       |          |         |       | 0000          |

| TRGCON2   | 0C54  |          | TRGDI  | V<3:0>  |                                                       | _                                           | —       | _       | _          | _        | -       |         |         | TRO   | GSTRT<5: | 0>      |       | 0000          |

| LEBCON2   | 0C5A  | PHR      | PHF    | PLR     | PLF                                                   | FLTLEBEN                                    | CLLEBEN | _       | _          | _        | -       | BCH     | BCL     | BPHH  | BPHL     | BPLH    | BPLL  | 0000          |

| LEBDLY2   | 0C5C  | _        | _      | _       | _                                                     | LEB<11:0>                                   |         |         |            |          |         |         |         | 0000  |          |         |       |               |

| AUXCON2   | 0C5E  | _        | _      | —       | —                                                     | BLANKSEL<3:0> — — CHOPSEL<3:0> CHOPHEN CHOF |         |         |            |          |         | CHOPLEN | 0000    |       |          |         |       |               |

I- DIGGOEDV/VMOGOV/EGV AND DIGGAEDV/VMOGOV DEVICED ONLY

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-15: PWM GENERATOR 3 REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY

| File Name | Addr. | Bit 15  | Bit 14 | Bit 13       | Bit 12         | Bit 11                                         | Bit 10                                     | Bit 9  | Bit 8     | Bit 7    | Bit 6  | Bit 5 | Bit 4   | Bit 3 | Bit 2    | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------|---------|--------|--------------|----------------|------------------------------------------------|--------------------------------------------|--------|-----------|----------|--------|-------|---------|-------|----------|-------|-------|---------------|

| PWMCON3   | 0C60  | FLTSTAT | CLSTAT | TRGSTAT      | FLTIEN         | CLIEN                                          | TRGIEN                                     | ITB    | MDCS      | DTC<     | <1:0>  | DTCP  | —       | MTBS  | CAM      | XPRES | IUE   | 0000          |

| IOCON3    | 0C62  | PENH    | PENL   | POLH         | POLL           | PMOD                                           | )<1:0>                                     | OVRENH | OVRENL    | OVRDA    | T<1:0> | FLTD  | AT<1:0> | CLD   | AT<1:0>  | SWAP  | OSYNC | C000          |

| FCLCON3   | 0C64  |         |        | (            | CLSRC<4:0      | )>                                             | CLPOL CLMOD FLTSRC<4:0> FLTPOL FLTMOD<1:0> |        |           |          |        |       | D<1:0>  | 00F8  |          |       |       |               |

| PDC3      | 0C66  |         |        |              | PDC3<15:0> 00  |                                                |                                            |        |           |          |        |       |         |       |          | 0000  |       |               |

| PHASE3    | 0C68  |         |        | PHASE3<15:0> |                |                                                |                                            |        |           |          |        |       |         |       |          | 0000  |       |               |

| DTR3      | 0C6A  |         | —      |              | DTR3<13:0> 000 |                                                |                                            |        |           |          |        |       |         |       | 0000     |       |       |               |

| ALTDTR3   | 0C6C  |         | —      |              |                |                                                |                                            |        | AL        | TDTR3<13 | :0>    |       |         |       |          |       |       | 0000          |

| TRIG3     | 0C72  |         |        |              |                |                                                |                                            | Т      | RGCMP<15: | 0>       |        |       |         |       |          |       |       | 0000          |

| TRGCON3   | 0C74  |         | TRGDI  | V<3:0>       |                | _                                              | _                                          | _      | _         | _        | _      |       |         | TR    | GSTRT<5: | 0>    |       | 0000          |

| LEBCON3   | 0C7A  | PHR     | PHF    | PLR          | PLF            | FLTLEBEN                                       | CLLEBEN                                    | —      | —         |          | —      | BCH   | BCL     | BPHH  | BPHL     | BPLH  | BPLL  | 0000          |

| LEBDLY3   | 0C7C  |         | —      | _            | _              | LEB<11:0> 0                                    |                                            |        |           |          |        |       |         | 0000  |          |       |       |               |

| AUXCON3   | 0C7E  |         | —      | —            | —              | BLANKSEL<3:0> — — CHOPSEL<3:0> CHOPHEN CHOPLEN |                                            |        |           |          |        | 0000  |         |       |          |       |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

.

----

.

### TABLE 4-41: PMD REGISTER MAP FOR dsPIC33EPXXXMC20X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | QEI1MD | PWMMD  | —      | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | _      | _      | AD1MD | 0000          |

| PMD2         | 0762  | _      | _      | _      | _      | IC4MD  | IC3MD  | IC2MD  | IC1MD  | _      | _     | _     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  | _      | _      | —      | —      | _      | CMPMD  | _      | _      | CRCMD  | _     | —     | _      | —      | —      | I2C2MD | _     | 0000          |

| PMD4         | 0766  | _      |        | _      | _      | _      | _      | _      | _      | _      | _     | _     | _      | REFOMD | CTMUMD | _      | _     | 0000          |

| PMD6         | 076A  | _      |        | _      | _      | _      | PWM3MD | PWM2MD | PWM1MD | _      | _     | _     | _      | _      | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  |        |        |        |        |        |        |        |        |        |       |       | DMA1MD | PTGMD  |        |        |       | 0000          |

| PIVID7       | 0760  | _      | _      | _      | _      | _      | _      | _      | _      | _      | _     | _     | DMA2MD | FIGMD  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA3MD |        |        |        |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

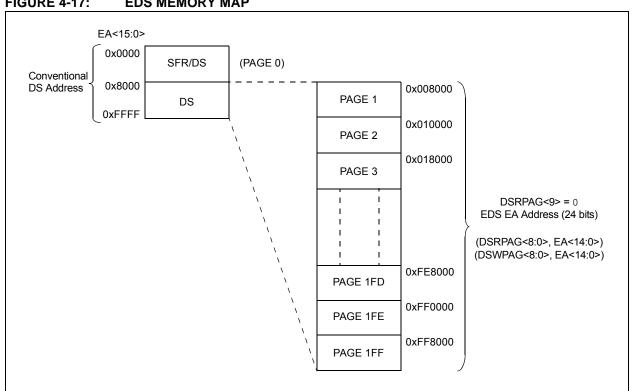

#### 4.4.2 EXTENDED X DATA SPACE

The lower portion of the base address space range, between 0x0000 and 0x7FFF, is always accessible regardless of the contents of the Data Space Page registers. It is indirectly addressable through the register indirect instructions. It can be regarded as being located in the default EDS Page 0 (i.e., EDS address range of 0x000000 to 0x007FFF with the base address bit, EA<15> = 0, for this address range). However, Page 0 cannot be accessed through the upper 32 Kbytes, 0x8000 to 0xFFFF, of base Data Space, in combination with DSRPAG = 0x000 or DSWPAG = 0x000. Consequently, DSRPAG and DSWPAG are initialized to 0x001 at Reset.

- Note 1: DSxPAG should not be used to access Page 0. An EDS access with DSxPAG set to 0x000 will generate an address error trap.

- 2: Clearing the DSxPAG in software has no effect.

The remaining pages, including both EDS and PSV pages, are only accessible using the DSRPAG or DSWPAG registers in combination with the upper 32 Kbytes, 0x8000 to 0xFFFF, of the base address, where base address bit, EA<15> = 1.

For example, when DSRPAG = 0x001 or DSWPAG = 0x001, accesses to the upper 32 Kbytes, 0x8000 to 0xFFFF, of the Data Space will map to the EDS address range of 0x008000 to 0x00FFFF. When DSRPAG = 0x002 or DSWPAG = 0x002, accesses to the upper 32 Kbytes of the Data Space will map to the EDS address range of 0x010000 to 0x017FFF and so on, as shown in the EDS memory map in Figure 4-17.

For more information on the PSV page access using Data Space Page registers, refer to the "**Program Space Visibility from Data Space**" section in "**Program Memory**" (DS70613) of the "*dsPIC33/ PIC24 Family Reference Manual*".

#### FIGURE 4-17: EDS MEMORY MAP

# 5.0 FLASH PROGRAM MEMORY

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXGP/MC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Flash Programming" (DS70609) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices contain internal Flash program memory for storing and executing application code. The memory is readable, writable and erasable during normal operation over the entire VDD range.

Flash memory can be programmed in two ways:

- In-Circuit Serial Programming™ (ICSP™) programming capability

- Run-Time Self-Programming (RTSP)

ICSP allows for a dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X device to be serially programmed while in the end application circuit. This is done with two lines for programming clock and programming data (one of the alternate programming pin pairs: PGECx/PGEDx), and three other lines for power (VDD), ground (VSS) and Master Clear (MCLR). This allows customers to manufacture boards with unprogrammed devices and then program the device just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

RTSP is accomplished using TBLRD (Table Read) and TBLWT (Table Write) instructions. With RTSP, the user application can write program memory data a single program memory word, and erase program memory in blocks or 'pages' of 1024 instructions (3072 bytes) at a time.

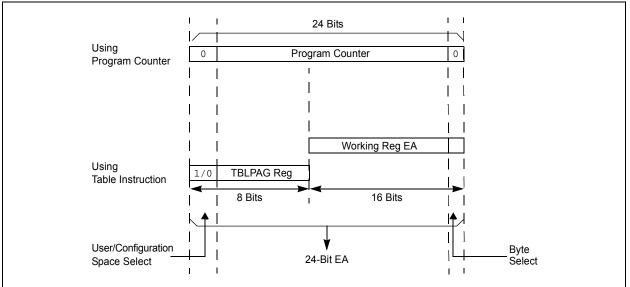

# 5.1 Table Instructions and Flash Programming

Regardless of the method used, all programming of Flash memory is done with the Table Read and Table Write instructions. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using bits<7:0> of the TBLPAG register and the Effective Address (EA) from a W register, specified in the table instruction, as shown in Figure 5-1.

The TBLRDL and the TBLWTL instructions are used to read or write to bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes.

The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

#### FIGURE 5-1: ADDRESSING FOR TABLE REGISTERS

### 7.3 Interrupt Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

#### 7.3.1 KEY RESOURCES

- "Interrupts" (DS70600) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- Development Tools

#### 7.4 Interrupt Control and Status Registers

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices implement the following registers for the interrupt controller:

- INTCON1

- INTCON2

- INTCON3

- INTCON4

- INTTREG

#### 7.4.1 INTCON1 THROUGH INTCON4

Global interrupt control functions are controlled from INTCON1, INTCON2, INTCON3 and INTCON4.

INTCON1 contains the Interrupt Nesting Disable bit (NSTDIS), as well as the control and status flags for the processor trap sources.

The INTCON2 register controls external interrupt request signal behavior and also contains the Global Interrupt Enable bit (GIE).

INTCON3 contains the status flags for the DMA and DO stack overflow status trap sources.

The INTCON4 register contains the software generated hard trap status bit (SGHT).

### 7.4.2 IFSx

The IFSx registers maintain all of the interrupt request flags. Each source of interrupt has a status bit, which is set by the respective peripherals or external signal and is cleared via software.

#### 7.4.3 IECx

The IECx registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

#### 7.4.4 IPCx

The IPCx registers are used to set the Interrupt Priority Level (IPL) for each source of interrupt. Each user interrupt source can be assigned to one of eight priority levels.

#### 7.4.5 INTTREG

The INTTREG register contains the associated interrupt vector number and the new CPU Interrupt Priority Level, which are latched into the Vector Number bits (VECNUM<7:0>) and Interrupt Priority Level bits (ILR<3:0>) fields in the INTTREG register. The new Interrupt Priority Level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the same sequence as they are listed in Table 7-1. For example, the INT0 (External Interrupt 0) is shown as having Vector Number 8 and a natural order priority of 0. Thus, the INT0IF bit is found in IFS0<0>, the INT0IE bit in IEC0<0> and the INT0IP bits in the first position of IPC0 (IPC0<2:0>).

#### 7.4.6 STATUS/CONTROL REGISTERS

Although these registers are not specifically part of the interrupt control hardware, two of the CPU Control registers contain bits that control interrupt functionality. For more information on these registers refer to "**CPU**" (DS70359) in the "dsPIC33/PIC24 Family Reference Manual".

- The CPU STATUS Register, SR, contains the IPL<2:0> bits (SR<7:5>). These bits indicate the current CPU Interrupt Priority Level. The user software can change the current CPU Interrupt Priority Level by writing to the IPLx bits.

- The CORCON register contains the IPL3 bit which, together with IPL<2:0>, also indicates the current CPU priority level. IPL3 is a read-only bit so that trap events cannot be masked by the user software.

All Interrupt registers are described in Register 7-3 through Register 7-7 in the following pages.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0           | U-0        | R/W-0            | R/W-0          | R/W-0             | R/W-0            | R/W-0    | R/W-0 |

|---------------|------------|------------------|----------------|-------------------|------------------|----------|-------|

| _             | —          |                  |                | RP39              | R<5:0>           |          |       |

| bit 15        |            |                  |                |                   |                  |          | bit 8 |

|               |            |                  |                |                   |                  |          |       |

| U-0           | U-0        | R/W-0            | R/W-0          | R/W-0             | R/W-0            | R/W-0    | R/W-0 |

| —             | —          |                  |                | RP38              | R<5:0>           |          |       |

| bit 7         |            |                  |                |                   |                  |          | bit 0 |

|               |            |                  |                |                   |                  |          |       |

| Legend:       |            |                  |                |                   |                  |          |       |

| R = Readable  | e bit      | W = Writable     | bit            | U = Unimplen      | nented bit, read | d as '0' |       |

| -n = Value at | POR        | '1' = Bit is set |                | '0' = Bit is clea | x = Bit is unkr  | nown     |       |

|               |            |                  |                |                   |                  |          |       |

| bit 15-14     | Unimplemer | nted: Read as '  | 0'             |                   |                  |          |       |

| bit 13-8      | RP39R<5:0> | : Peripheral Ou  | Itput Function | n is Assigned to  | RP39 Output F    | Pin bits |       |

#### REGISTER 11-20: RPOR2: PERIPHERAL PIN SELECT OUTPUT REGISTER 2

|         | (see Table 11-3 for peripheral function numbers)                           |

|---------|----------------------------------------------------------------------------|

| bit 7-6 | Unimplemented: Read as '0'                                                 |

| bit 5-0 | RP38R<5:0>: Peripheral Output Function is Assigned to RP38 Output Pin bits |

|         | (see Table 11-3 for peripheral function numbers)                           |

#### REGISTER 11-21: RPOR3: PERIPHERAL PIN SELECT OUTPUT REGISTER 3

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| —      | —   |       |       | RP41  | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|--------|-------|-------|

| —     | —   |       |       | RP40  | R<5:0> |       |       |

| bit 7 |     |       |       |       |        |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

- bit 13-8 **RP41R<5:0>:** Peripheral Output Function is Assigned to RP41 Output Pin bits (see Table 11-3 for peripheral function numbers)

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 **RP40R<5:0>:** Peripheral Output Function is Assigned to RP40 Output Pin bits (see Table 11-3 for peripheral function numbers)

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| REGISTER 21-26: | CxTRmnCON: ECANx TX/RX BUFFER mn CONTROL REGISTER |

|-----------------|---------------------------------------------------|

|                 | (m = 0,2,4,6; n = 1,3,5,7)                        |

|              | ( •                                        | ,_, ., ., .,                     | -,-,-,                         |                  |                  |                 |                 |  |  |  |

|--------------|--------------------------------------------|----------------------------------|--------------------------------|------------------|------------------|-----------------|-----------------|--|--|--|

| R/W-0        | R-0                                        | R-0                              | R-0                            | R/W-0            | R/W-0            | R/W-0           | R/W-0           |  |  |  |

| TXENn        | TXABTn                                     | TXLARBn                          | TXERRn                         | TXREQn           | RTRENn           | TXnPRI1         | TXnPRI0         |  |  |  |

| bit 15       |                                            |                                  |                                |                  |                  |                 | bit 8           |  |  |  |

| R/W-0        | R-0                                        | R-0                              | R-0                            | R/W-0            | R/W-0            | R/W-0           | R/W-0           |  |  |  |

| TXENm        | TXABTm <sup>(1)</sup>                      | TXLARBm <sup>(1)</sup>           | TXERRm <sup>(1)</sup>          | TXREQm           | RTRENm           | TXmPRI1         | TXmPRI0         |  |  |  |

| bit 7        |                                            |                                  | •                              |                  |                  |                 | bit 0           |  |  |  |

| Legend:      |                                            |                                  |                                |                  |                  |                 |                 |  |  |  |

| R = Readab   | le bit                                     | W = Writable                     | bit                            | U = Unimpler     | mented bit, read | d as '0'        |                 |  |  |  |

| -n = Value a | t POR                                      | '1' = Bit is set                 |                                | '0' = Bit is cle | ared             | x = Bit is unki | nown            |  |  |  |

| bit 15-8     | See Definitio                              | n for bits<7:0>,                 | Controls Buffe                 | ar n             |                  |                 |                 |  |  |  |

| bit 7        |                                            | RX Buffer Sele                   |                                | 51 11            |                  |                 |                 |  |  |  |

|              |                                            | Ren is a transm                  |                                |                  |                  |                 |                 |  |  |  |

|              |                                            | RBn is a receive                 |                                |                  |                  |                 |                 |  |  |  |

| bit 6        | TXABTm: Message Aborted bit <sup>(1)</sup> |                                  |                                |                  |                  |                 |                 |  |  |  |

|              |                                            | 1 = Message was aborted          |                                |                  |                  |                 |                 |  |  |  |

|              | 0 = Message                                | completed tran                   | nsmission succ                 | cessfully        |                  |                 |                 |  |  |  |

| bit 5        | TXLARBm: N                                 | Message Lost A                   | Arbitration bit <sup>(1)</sup> | )                |                  |                 |                 |  |  |  |

|              |                                            | lost arbitration did not lose ar |                                |                  |                  |                 |                 |  |  |  |

| bit 4        | •                                          | ror Detected D                   |                                | •                |                  |                 |                 |  |  |  |

|              |                                            | or occurred wh                   |                                |                  | ent              |                 |                 |  |  |  |

|              | 0 = A bus err                              | or did not occu                  | r while the me                 | ssage was bei    | ing sent         |                 |                 |  |  |  |

| bit 3        | TXREQm: M                                  | essage Send R                    | Request bit                    |                  |                  |                 |                 |  |  |  |

|              | sent                                       |                                  | -                              |                  | ally clears wher | n the message   | is successfully |  |  |  |

|              | •                                          | the bit to '0' wh                | •                              | •                | abort            |                 |                 |  |  |  |

| bit 2        |                                            | uto-Remote Tra                   |                                |                  |                  |                 |                 |  |  |  |

|              |                                            | emote transmit<br>emote transmit |                                |                  |                  |                 |                 |  |  |  |

| bit 1-0      | TXmPRI<1:0                                 | >: Message Tra                   | ansmission Pri                 | iority bits      |                  |                 |                 |  |  |  |

|              | -                                          | message prior                    | •                              |                  |                  |                 |                 |  |  |  |

|              | 0                                          | ermediate mes                    |                                |                  |                  |                 |                 |  |  |  |

|              |                                            | ermediate mess<br>message priori |                                |                  |                  |                 |                 |  |  |  |

| <b>.</b> –   |                                            |                                  | -                              |                  |                  |                 |                 |  |  |  |

| Note 1: ⊤    | his bit is cleared                         | when IXREQ                       | s set.                         |                  |                  |                 |                 |  |  |  |

Note: The buffers, SID, EID, DLC, Data Field, and Receive Status registers are located in DMA RAM.

# 23.0 10-BIT/12-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

- **Note 1:** This data sheet summarizes the features of the dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. То complement the information in this data sheet. refer to "Analog-to-Digital Converter (ADC)" (DS70621) in the "dsPIC33/PIC24 Family Reference Manual', which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices have one ADC module. The ADC module supports up to 16 analog input channels.

On ADC1, the AD12B bit (AD1CON1<10>) allows the ADC module to be configured by the user as either a 10-bit, 4 Sample-and-Hold (S&H) ADC (default configuration) or a 12-bit, 1 S&H ADC.

Note: The ADC module needs to be disabled before modifying the AD12B bit.

# 23.1 Key Features

#### 23.1.1 10-BIT ADC CONFIGURATION

The 10-bit ADC configuration has the following key features:

- Successive Approximation (SAR) conversion

- · Conversion speeds of up to 1.1 Msps

- · Up to 16 analog input pins

- Connections to three internal op amps

- Connections to the Charge Time Measurement Unit (CTMU) and temperature measurement diode

- Channel selection and triggering can be controlled by the Peripheral Trigger Generator (PTG)

- External voltage reference input pins

- · Simultaneous sampling of:

- Up to four analog input pins

- Three op amp outputs

- Combinations of analog inputs and op amp outputs

- Automatic Channel Scan mode

- Selectable conversion Trigger source

- · Selectable Buffer Fill modes

- Four result alignment options (signed/unsigned, fractional/integer)

- Operation during CPU Sleep and Idle modes

#### 23.1.2 12-BIT ADC CONFIGURATION

The 12-bit ADC configuration supports all the features listed above, with the exception of the following:

- In the 12-bit configuration, conversion speeds of up to 500 ksps are supported

- There is only one S&H amplifier in the 12-bit configuration; therefore, simultaneous sampling of multiple channels is not supported.

Depending on the particular device pinout, the ADC can have up to 16 analog input pins, designated AN0 through AN15. These analog inputs are shared with op amp inputs and outputs, comparator inputs, and external voltage references. When op amp/comparator functionality is enabled, or an external voltage reference is used, the analog input that shares that pin is no longer available. The actual number of analog input pins, op amps and external voltage reference input configuration depends on the specific device.

A block diagram of the ADC module is shown in Figure 23-1. Figure 23-2 provides a diagram of the ADC conversion clock period.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| REGISTER      | 25-3: CM40       | CON: COMPA                                  | RATOR 4 CO          | ONTROL RE        | GISTER             |                                           |                     |  |  |  |

|---------------|------------------|---------------------------------------------|---------------------|------------------|--------------------|-------------------------------------------|---------------------|--|--|--|

| R/W-0         | R/W-0            | R/W-0                                       | U-0                 | U-0              | U-0                | R/W-0                                     | R/W-0               |  |  |  |

| CON           | COE              | CPOL                                        | —                   | —                | —                  | CEVT                                      | COUT                |  |  |  |

| bit 15        |                  |                                             |                     |                  |                    |                                           | bit 8               |  |  |  |

| R/W-0         | DAM 0            | U-0                                         | DAM 0               | U-0              | U-0                |                                           | R/W-0               |  |  |  |

|               | R/W-0            | 0-0                                         | R/W-0               | 0-0              | 0-0                | R/W-0                                     |                     |  |  |  |

| EVPOL1        | EVPOL0           | —                                           | CREF <sup>(1)</sup> | —                | _                  | CCH1 <sup>(1)</sup>                       | CCH0 <sup>(1)</sup> |  |  |  |

| bit 7         |                  |                                             |                     |                  |                    |                                           | bit (               |  |  |  |

| Legend:       |                  |                                             |                     |                  |                    |                                           |                     |  |  |  |

| R = Readable  | e bit            | W = Writable                                | bit                 | U = Unimple      | mented bit, rea    | d as '0'                                  |                     |  |  |  |

| -n = Value at |                  | '1' = Bit is se                             |                     | '0' = Bit is cle |                    | x = Bit is unkr                           | iown                |  |  |  |

|               |                  |                                             |                     | 0 200000         |                    |                                           |                     |  |  |  |

| bit 15        | CON: Comp        | arator Enable b                             | oit                 |                  |                    |                                           |                     |  |  |  |

|               |                  | ator is enabled                             |                     |                  |                    |                                           |                     |  |  |  |

|               |                  | ator is disabled                            |                     |                  |                    |                                           |                     |  |  |  |

| bit 14        | COE: Comp        | arator Output E                             | nable bit           |                  |                    |                                           |                     |  |  |  |

|               |                  | ator output is pr<br>ator output is in      |                     | xOUT pin         |                    |                                           |                     |  |  |  |

| bit 13        | CPOL: Com        | parator Output                              | Polarity Select     | bit              |                    |                                           |                     |  |  |  |

|               | 1 = Compara      | ator output is in                           | verted              |                  |                    |                                           |                     |  |  |  |

|               | 0 = Compara      | ator output is no                           | ot inverted         |                  |                    |                                           |                     |  |  |  |

| bit 12-10     | Unimpleme        | nted: Read as                               | '0'                 |                  |                    |                                           |                     |  |  |  |

| bit 9         | CEVT: Com        | parator Event b                             | it                  |                  |                    |                                           |                     |  |  |  |

|               | interrup         | ts until the bit is                         | cleared             | POL<1:0> set     | tings occurred;    | disables future                           | e triggers and      |  |  |  |

|               | •                | ator event did r                            |                     |                  |                    |                                           |                     |  |  |  |

| bit 8         |                  | parator Output                              |                     |                  |                    |                                           |                     |  |  |  |

|               |                  | <u>. = 0 (non-inver</u>                     | ted polarity):      |                  |                    |                                           |                     |  |  |  |

|               |                  | 1 = VIN+ > VIN-<br>0 = VIN+ < VIN-          |                     |                  |                    |                                           |                     |  |  |  |

|               |                  | When CPOL = 1 (inverted polarity):          |                     |                  |                    |                                           |                     |  |  |  |

|               |                  | 1 = VIN+ < VIN-                             |                     |                  |                    |                                           |                     |  |  |  |

|               | 0 = VIN+ > V     | 'IN-                                        |                     |                  |                    |                                           |                     |  |  |  |

| bit 7-6       | EVPOL<1:0        | >: Trigger/Ever                             | t/Interrupt Pola    | arity Select bit | S                  |                                           |                     |  |  |  |

|               | 10 = Trigger     |                                             | generated only      |                  |                    | or output (while (<br>e polarity selected |                     |  |  |  |

|               | If CPO           | L = <u>1</u> (inverted)<br>-high transition | polarity):          | ator output.     |                    |                                           |                     |  |  |  |

|               |                  | L = 0 (non-inve                             |                     | ator output.     |                    |                                           |                     |  |  |  |

|               |                  | /event/interrupt<br>(while CEVT =           |                     | v on low-to-higl | n transition of th | e polarity selecte                        | ed comparato        |  |  |  |

|               |                  | L = 1 (inverted                             |                     | ator output.     |                    |                                           |                     |  |  |  |

|               |                  | <u>L = 0 (non-inve</u><br>-high transition  |                     | ator output.     |                    |                                           |                     |  |  |  |

|               | 00 = Trigger     | /event/interrupt                            | generation is       | disabled         |                    |                                           |                     |  |  |  |

| Note 1: In    | puts that are se | lected and not a                            | available will be   | e tied to Vss. S | See the "Pin Dia   | agrams" sectior                           | n for available     |  |  |  |

Note 1: Inputs that are selected and not available will be tied to Vss. See the "Pin Diagrams" section for available inputs for each package.

#### REGISTER 25-4: CMxMSKSRC: COMPARATOR x MASK SOURCE SELECT CONTROL REGISTER (CONTINUED)

- bit 3-0 SELSRCA<3:0>: Mask A Input Select bits

- 1111 = FLT4 1110 = FLT2 1101 = PTGO19 1100 = PTGO18 1011 = Reserved 1010 = Reserved 1001 = Reserved 1000 = Reserved 0111 = Reserved 0110 = Reserved 0101 = PWM3H 0100 = PWM3L 0011 = PWM2H 0010 = PWM2L 0001 = PWM1H 0000 = PWM1L

NOTES:

| U-0                                                          | U-0   | U-0          | R/W-0   | R/W-0           | R/W-0            | R/W-0    | R/W-0   |  |

|--------------------------------------------------------------|-------|--------------|---------|-----------------|------------------|----------|---------|--|

| _                                                            | —     | —            | DWIDTH4 | DWIDTH3         | DWIDTH2          | DWIDTH1  | DWIDTH0 |  |

| bit 15                                                       |       |              |         |                 |                  |          | bit 8   |  |

|                                                              |       |              |         |                 |                  |          |         |  |

| U-0                                                          | U-0   | U-0          | R/W-0   | R/W-0           | R/W-0            | R/W-0    | R/W-0   |  |

| —                                                            | —     | —            | PLEN4   | PLEN3           | PLEN2            | PLEN1    | PLEN0   |  |

| bit 7                                                        |       |              |         |                 |                  |          | bit 0   |  |

|                                                              |       |              |         |                 |                  |          |         |  |

| Legend:                                                      |       |              |         |                 |                  |          |         |  |

| R = Readable                                                 | e bit | W = Writable | bit     | U = Unimpler    | mented bit, read | l as '0' |         |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared      |       |              |         | x = Bit is unkr | nown             |          |         |  |

|                                                              |       |              |         |                 |                  |          |         |  |

| bit 15-13 Unimplemented: Read as '0'                         |       |              |         |                 |                  |          |         |  |

| bit 12-8 DWIDTH<4:0>: Data Width Select bits                 |       |              |         |                 |                  |          |         |  |

| These bits set the width of the data word (DWIDTH<4:0> + 1). |       |              |         |                 |                  |          |         |  |

| bit 7-5 Unimplemented: Read as '0'                           |       |              |         |                 |                  |          |         |  |

|                                                              |       |              |         |                 |                  |          |         |  |

#### REGISTER 26-2: CRCCON2: CRC CONTROL REGISTER 2

bit 4-0 **PLEN<4:0>:** Polynomial Length Select bits

These bits set the length of the polynomial (Polynomial Length = PLEN<4:0> + 1).

| DC CHARACTI       | ERISTICS            |      | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |            |        |         |  |  |

|-------------------|---------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------|---------|--|--|

| Parameter<br>No.  | Тур.                | Max. | Units                                                                                                                                                                                                                                                                                   | Conditions |        |         |  |  |

| Idle Current (III | dle) <sup>(1)</sup> |      |                                                                                                                                                                                                                                                                                         |            |        |         |  |  |

| DC40d             | 3                   | 8    | mA                                                                                                                                                                                                                                                                                      | -40°C      |        |         |  |  |

| DC40a             | 3                   | 8    | mA                                                                                                                                                                                                                                                                                      | +25°C      | - 3.3V |         |  |  |

| DC40b             | 3                   | 8    | mA                                                                                                                                                                                                                                                                                      | +85°C      | 3.3V   | 10 MIPS |  |  |

| DC40c             | 3                   | 8    | mA                                                                                                                                                                                                                                                                                      | +125°C     |        |         |  |  |

| DC42d             | 6                   | 12   | mA                                                                                                                                                                                                                                                                                      | -40°C      |        | 20 MIPS |  |  |

| DC42a             | 6                   | 12   | mA                                                                                                                                                                                                                                                                                      | +25°C      | 3.3V   |         |  |  |

| DC42b             | 6                   | 12   | mA                                                                                                                                                                                                                                                                                      | +85°C      |        |         |  |  |

| DC42c             | 6                   | 12   | mA                                                                                                                                                                                                                                                                                      | +125°C     |        |         |  |  |

| DC44d             | 11                  | 18   | mA                                                                                                                                                                                                                                                                                      | -40°C      |        | 40 MIPS |  |  |

| DC44a             | 11                  | 18   | mA                                                                                                                                                                                                                                                                                      | +25°C      | 3.3V   |         |  |  |

| DC44b             | 11                  | 18   | mA                                                                                                                                                                                                                                                                                      | +85°C      | 5.5 V  |         |  |  |

| DC44c             | 11                  | 18   | mA                                                                                                                                                                                                                                                                                      | +125°C     |        |         |  |  |

| DC45d             | 17                  | 27   | mA                                                                                                                                                                                                                                                                                      | -40°C      |        |         |  |  |

| DC45a             | 17                  | 27   | mA                                                                                                                                                                                                                                                                                      | +25°C      | 3.3V   | 60 MIPS |  |  |

| DC45b             | 17                  | 27   | mA                                                                                                                                                                                                                                                                                      | +85°C      |        |         |  |  |

| DC45c             | 17                  | 27   | mA                                                                                                                                                                                                                                                                                      | +125°C     |        |         |  |  |

| DC46d             | 20                  | 35   | mA                                                                                                                                                                                                                                                                                      | -40°C      |        |         |  |  |

| DC46a             | 20                  | 35   | mA                                                                                                                                                                                                                                                                                      | +25°C      | 3.3V   | 70 MIPS |  |  |

| DC46b             | 20                  | 35   | mA                                                                                                                                                                                                                                                                                      | +85°C      |        |         |  |  |

#### TABLE 30-7: DC CHARACTERISTICS: IDLE CURRENT (lidle)

**Note 1:** Base Idle current (IIDLE) is measured as follows:

• CPU core is off, oscillator is configured in EC mode and external clock is active; OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)

- CLKO is configured as an I/O input pin in the Configuration Word

- All I/O pins are configured as inputs and pulled to Vss

- $\overline{\text{MCLR}}$  = VDD, WDT and FSCM are disabled

- No peripheral modules are operating; however, every peripheral is being clocked (all PMDx bits are zeroed)

- The NVMSIDL bit (NVMCON<12>) = 1 (i.e., Flash regulator is set to standby while the device is in Idle mode)

- The VREGSF bit (RCON<11>) = 0 (i.e., Flash regulator is set to standby while the device is in Sleep mode)

- JTAG is disabled

# 33.0 PACKAGING INFORMATION

#### 33.1 Package Marking Information

#### 28-Lead SPDIP

#### 28-Lead SOIC (.300")

28-Lead SSOP

Example dsPIC33EP64GP 502-I/SP@3 1310017

### Example

#### Example

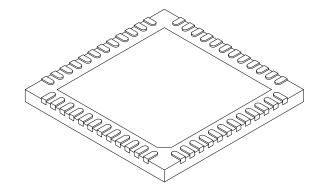

28-Lead QFN-S (6x6x0.9 mm)

Example

| Legend | : XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>* | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator ((e3))<br>can be found on the outer packaging for this package. |

|--------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | be carried                               | nt the full Microchip part number cannot be marked on one line, it will<br>d over to the next line, thus limiting the number of available<br>of or customer-specific information.                                                                                                                                                                                              |

48-Lead Plastic Ultra Thin Quad Flat, No Lead Package (MV) – 6x6x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | MILLIMETERS |           |          |      |

|------------------------|-------------|-----------|----------|------|

| Dimension              | Limits      | MIN       | NOM      | MAX  |

| Number of Pins         | N           |           | 48       |      |

| Pitch                  | е           |           | 0.40 BSC |      |

| Overall Height         | Α           | 0.45      | 0.50     | 0.55 |

| Standoff               | A1          | 0.00      | 0.02     | 0.05 |

| Contact Thickness      | A3          | 0.127 REF |          |      |

| Overall Width          | E           | 6.00 BSC  |          |      |

| Exposed Pad Width      | E2          | 4.45      | 4.60     | 4.75 |

| Overall Length         | D           | 6.00 BSC  |          |      |

| Exposed Pad Length     | D2          | 4.45      | 4.60     | 4.75 |

| Contact Width          | b           | 0.15      | 0.20     | 0.25 |

| Contact Length         | L           | 0.30      | 0.40     | 0.50 |

| Contact-to-Exposed Pad | K           | 0.20      | -        | -    |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-153A Sheet 2 of 2