Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 60 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 35                                                                             |

| Program Memory Size        | 512KB (170K x 24)                                                              |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 24K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 9x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

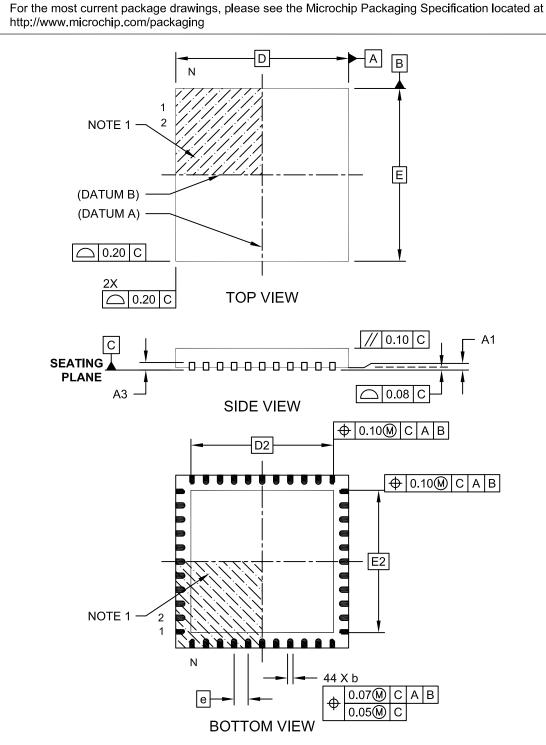

| Package / Case             | 44-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 44-QFN (8x8)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep512gp204-e-ml |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

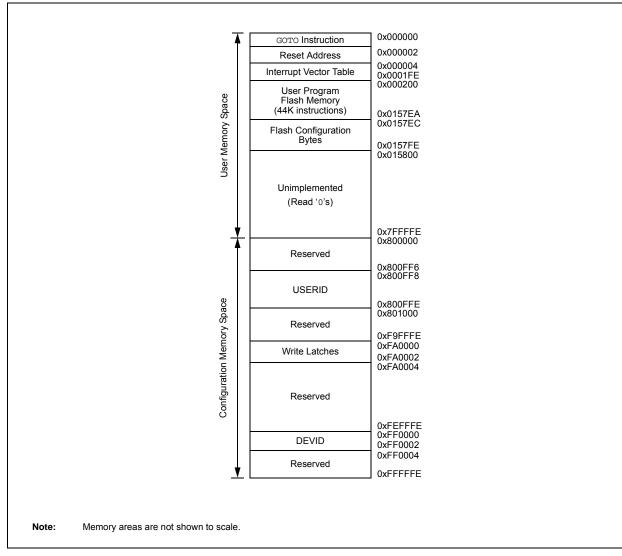

#### FIGURE 4-3: PROGRAM MEMORY MAP FOR dsPIC33EP128GP50X, dsPIC33EP128MC20X/50X AND PIC24EP128GP/MC20X DEVICES

| IABLE 4   | -14:  | PVVIVI G | ENERA  | IUR Z R | EGIST     |          | FOR as  | PIC33EP  |            | 202/202   |          | 16246   | PXXX    |          |          | CES ONL | _ T     |               |

|-----------|-------|----------|--------|---------|-----------|----------|---------|----------|------------|-----------|----------|---------|---------|----------|----------|---------|---------|---------------|

| File Name | Addr. | Bit 15   | Bit 14 | Bit 13  | Bit 12    | Bit 11   | Bit 10  | Bit 9    | Bit 8      | Bit 7     | Bit 6    | Bit 5   | Bit 4   | Bit 3    | Bit 2    | Bit 1   | Bit 0   | All<br>Resets |

| PWMCON2   | 0C40  | FLTSTAT  | CLSTAT | TRGSTAT | FLTIEN    | CLIEN    | TRGIEN  | ITB      | MDCS       | DTC       | <1:0>    | DTCP    | _       | MTBS     | CAM      | XPRES   | IUE     | 0000          |

| IOCON2    | 0C42  | PENH     | PENL   | POLH    | POLL      | PMOD     | 0<1:0>  | OVRENH   | OVRENL     | OVRDA     | \T<1:0>  | FLTD    | \T<1:0> | CLDA     | AT<1:0>  | SWAP    | OSYNC   | C000          |

| FCLCON2   | 0C44  | _        |        | (       | CLSRC<4:0 | )>       |         | CLPOL    | CLMOD      |           | FLT      | SRC<4:0 | >       |          | FLTPOL   | FLTMO   | D<1:0>  | 00F8          |

| PDC2      | 0C46  |          |        |         |           |          |         |          | PDC2<15:0> |           |          |         |         |          |          |         |         | 0000          |

| PHASE2    | 0C48  |          |        |         |           |          |         | Р        | HASE2<15:0 | )>        |          |         |         |          |          |         |         | 0000          |

| DTR2      | 0C4A  | _        | _      |         |           |          |         |          | [          | DTR2<13:0 | >        |         |         |          |          |         |         | 0000          |

| ALTDTR2   | 0C4C  | _        | _      |         |           |          |         |          | AL         | TDTR2<13  | :0>      |         |         |          |          |         |         | 0000          |

| TRIG2     | 0C52  |          |        |         |           |          |         | TI       | RGCMP<15:0 | )>        |          |         |         |          |          |         |         | 0000          |

| TRGCON2   | 0C54  |          | TRGDI  | V<3:0>  |           | _        | —       | _        | _          | _         | -        |         |         | TRO      | GSTRT<5: | 0>      |         | 0000          |

| LEBCON2   | 0C5A  | PHR      | PHF    | PLR     | PLF       | FLTLEBEN | CLLEBEN | _        | _          | _         | -        | BCH     | BCL     | BPHH     | BPHL     | BPLH    | BPLL    | 0000          |

| LEBDLY2   | 0C5C  | _        | _      | _       | _         |          |         |          |            |           | LEB<11:0 | )>      |         |          |          |         |         | 0000          |

| AUXCON2   | 0C5E  | _        | _      | —       | —         |          | BLANK   | SEL<3:0> |            | _         | —        |         | CHOPS   | SEL<3:0> |          | CHOPHEN | CHOPLEN | 0000          |

I- DIGGOEDV/VMOGOV/EGV AND DIGGAEDV/VMOGOV DEVICED ONLY

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-15: PWM GENERATOR 3 REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY

| File Name | Addr. | Bit 15  | Bit 14 | Bit 13  | Bit 12    | Bit 11   | Bit 10  | Bit 9    | Bit 8       | Bit 7     | Bit 6    | Bit 5   | Bit 4   | Bit 3    | Bit 2    | Bit 1   | Bit 0   | All<br>Resets |

|-----------|-------|---------|--------|---------|-----------|----------|---------|----------|-------------|-----------|----------|---------|---------|----------|----------|---------|---------|---------------|

| PWMCON3   | 0C60  | FLTSTAT | CLSTAT | TRGSTAT | FLTIEN    | CLIEN    | TRGIEN  | ITB      | MDCS        | DTC<      | <1:0>    | DTCP    | —       | MTBS     | CAM      | XPRES   | IUE     | 0000          |

| IOCON3    | 0C62  | PENH    | PENL   | POLH    | POLL      | PMOD     | )<1:0>  | OVRENH   | OVRENL      | OVRDA     | T<1:0>   | FLTD    | AT<1:0> | CLD      | AT<1:0>  | SWAP    | OSYNC   | C000          |

| FCLCON3   | 0C64  |         |        | (       | CLSRC<4:0 | )>       |         | CLPOL    | CLMOD       |           | FLT      | SRC<4:0 | >       |          | FLTPOL   | FLTMO   | D<1:0>  | 00F8          |

| PDC3      | 0C66  |         |        |         |           |          |         |          | PDC3<15:0>  | •         |          |         |         |          |          |         |         | 0000          |

| PHASE3    | 0C68  |         |        |         |           |          |         | F        | PHASE3<15:0 | )>        |          |         |         |          |          |         |         | 0000          |

| DTR3      | 0C6A  |         | —      |         |           |          |         |          | [           | DTR3<13:0 | >        |         |         |          |          |         |         | 0000          |

| ALTDTR3   | 0C6C  |         | —      |         |           |          |         |          | AL          | TDTR3<13  | :0>      |         |         |          |          |         |         | 0000          |

| TRIG3     | 0C72  |         |        |         |           |          |         | Т        | RGCMP<15:   | 0>        |          |         |         |          |          |         |         | 0000          |

| TRGCON3   | 0C74  |         | TRGDI  | V<3:0>  |           | _        | _       | _        | _           | _         | _        |         |         | TR       | GSTRT<5: | 0>      |         | 0000          |

| LEBCON3   | 0C7A  | PHR     | PHF    | PLR     | PLF       | FLTLEBEN | CLLEBEN | —        | —           |           | —        | BCH     | BCL     | BPHH     | BPHL     | BPLH    | BPLL    | 0000          |

| LEBDLY3   | 0C7C  |         | —      | _       | _         |          |         |          |             |           | LEB<11:0 | )>      |         |          |          |         |         | 0000          |

| AUXCON3   | 0C7E  |         | —      | —       | —         |          | BLANK   | SEL<3:0> |             |           | —        |         | CHOPS   | SEL<3:0> | •        | CHOPHEN | CHOPLEN | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

.

----

.

# 4.5.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions. which apply to dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices, and the DSP accumulator class of instructions, which apply to the dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices, provide a greater degree of addressing flexibility than other instructions. In addition to the addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

Note: For the MOV instructions, the addressing mode specified in the instruction can differ for the source and destination EA. However, the 4-bit Wb (Register Offset) field is shared by both source and destination (but typically only used by one).

In summary, the following addressing modes are supported by move and accumulator instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-modified

- Register Indirect Pre-modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-Bit Literal

- 16-Bit Literal

Note: Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

#### 4.5.4 MAC INSTRUCTIONS (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X DEVICES ONLY)

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY. N, MOVSAC and MSC), also referred to as MAC instructions, use a simplified set of addressing modes to allow the user application to effectively manipulate the Data Pointers through register indirect tables.

The Two-Source Operand Prefetch registers must be members of the set: {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU, and W10 and W11 are always directed to the Y AGU. The Effective Addresses generated (before and after modification) must therefore, be valid addresses within X Data Space for W8 and W9, and Y Data Space for W10 and W11.

Note: Register Indirect with Register Offset Addressing mode is available only for W9 (in X space) and W11 (in Y space).

In summary, the following addressing modes are supported by the  ${\tt MAC}$  class of instructions:

- · Register Indirect

- Register Indirect Post-Modified by 2

- · Register Indirect Post-Modified by 4

- Register Indirect Post-Modified by 6

- Register Indirect with Register Offset (Indexed)

#### 4.5.5 OTHER INSTRUCTIONS

Besides the addressing modes outlined previously, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ULNK, the source of an operand or result is implied by the opcode itself. Certain operations, such as a NOP, do not have any operands.

| U-0                                | U-0                                       | U-0            | U-0             | U-0              | U-0              | U-0             | R/W-0   |

|------------------------------------|-------------------------------------------|----------------|-----------------|------------------|------------------|-----------------|---------|

| _                                  | —                                         | —              |                 | —                | —                | —               | PLLDIV8 |

| bit 15                             |                                           |                |                 |                  |                  |                 | bit 8   |

|                                    |                                           |                |                 |                  |                  |                 |         |

| R/W-0                              | R/W-0                                     | R/W-1          | R/W-1           | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

| PLLDIV7                            | PLLDIV6                                   | PLLDIV5        | PLLDIV4         | PLLDIV3          | PLLDIV2          | PLLDIV1         | PLLDIV0 |

| bit 7                              |                                           |                |                 |                  |                  |                 | bit 0   |

|                                    |                                           |                |                 |                  |                  |                 |         |

| Legend:                            |                                           |                |                 |                  |                  |                 |         |

| R = Readable                       | bit                                       | W = Writable   | bit             | U = Unimpler     | mented bit, read | as '0'          |         |

| -n = Value at POR '1' = Bit is set |                                           |                |                 | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |

|                                    |                                           |                |                 |                  |                  |                 |         |

| bit 15-9                           | Unimplemen                                | ted: Read as ' | 0'              |                  |                  |                 |         |

| bit 8-0                            | PLLDIV<8:0>                               | : PLL Feedba   | ck Divisor bits | (also denoted    | as 'M', PLL mul  | tiplier)        |         |

|                                    | 111111111 =                               | = 513          |                 |                  |                  |                 |         |

|                                    | •                                         |                |                 |                  |                  |                 |         |

|                                    | •                                         |                |                 |                  |                  |                 |         |

|                                    | •                                         |                |                 |                  |                  |                 |         |

|                                    | 000110000 =                               | = 50 (default) |                 |                  |                  |                 |         |

|                                    |                                           |                |                 |                  |                  |                 |         |

|                                    | •                                         |                |                 |                  |                  |                 |         |

|                                    | 000000010 =<br>000000001 =<br>000000000 = | = 3            |                 |                  |                  |                 |         |

|                                    |                                           |                |                 |                  |                  |                 |         |

#### REGISTER 9-3: PLLFBD: PLL FEEDBACK DIVISOR REGISTER

| REGISTER     | <u>R 10-2: PMD</u> 2 | 2: PERIPHER                                         | AL MODULE       | DISABLE C         | ONTROL RE       | GISTER 2        |       |

|--------------|----------------------|-----------------------------------------------------|-----------------|-------------------|-----------------|-----------------|-------|

| U-0          | U-0                  | U-0                                                 | U-0             | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

| _            |                      | _                                                   |                 | IC4MD             | IC3MD           | IC2MD           | IC1MD |

| bit 15       |                      |                                                     |                 |                   |                 |                 | bit   |

| U-0          | U-0                  | U-0                                                 | U-0             | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|              |                      |                                                     |                 | OC4MD             | OC3MD           | OC2MD           | OC1MD |

| bit 7        |                      |                                                     |                 |                   |                 |                 | bit   |

|              |                      |                                                     |                 |                   |                 |                 |       |

| Legend:      | 1.1.1                |                                                     |                 |                   |                 |                 |       |

| R = Readab   |                      | W = Writable b                                      | Dit             | •                 | nented bit, rea |                 |       |

| -n = Value a | at POR               | '1' = Bit is set                                    |                 | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

| bit 15-12    | Unimplemen           | ted: Read as '0                                     | ,               |                   |                 |                 |       |

| bit 11       | -                    | t Capture 4 Mod                                     |                 |                   |                 |                 |       |

|              |                      | oture 4 module is                                   |                 |                   |                 |                 |       |

|              | 0 = Input Cap        | oture 4 module is                                   | s enabled       |                   |                 |                 |       |

| bit 10       | IC3MD: Input         | t Capture 3 Mod                                     | ule Disable bit |                   |                 |                 |       |

|              |                      | oture 3 module is                                   |                 |                   |                 |                 |       |

|              |                      | oture 3 module is                                   |                 |                   |                 |                 |       |

| bit 9        |                      | t Capture 2 Mod                                     |                 |                   |                 |                 |       |

|              |                      | oture 2 module is<br>oture 2 module is              |                 |                   |                 |                 |       |

| bit 8        | IC1MD: Input         | t Capture 1 Mod                                     | ule Disable bit |                   |                 |                 |       |

|              | 1 = Input Cap        | oture 1 module is<br>oture 1 module is              | s disabled      |                   |                 |                 |       |

| bit 7-4      |                      | ted: Read as '0                                     |                 |                   |                 |                 |       |

| bit 3        | OC4MD: Out           | put Compare 4                                       | Module Disable  | e bit             |                 |                 |       |

|              |                      | ompare 4 modul                                      |                 |                   |                 |                 |       |

|              | -                    | ompare 4 modu                                       |                 |                   |                 |                 |       |

| bit 2        |                      | put Compare 3                                       |                 | e bit             |                 |                 |       |

|              | •                    | ompare 3 modul                                      |                 |                   |                 |                 |       |

| L:1 4        | -                    | ompare 3 modul                                      |                 | . h.:4            |                 |                 |       |

| bit 1        |                      | put Compare 2                                       |                 |                   |                 |                 |       |

|              | $\perp$ – Output Co  | ompare 2 modu                                       |                 |                   |                 |                 |       |

|              | 0 = Output Co        | ompare 2 modul                                      | le is enabled   |                   |                 |                 |       |

| bit 0        |                      | ompare 2 modul<br>put Compare 1                     |                 | e bit             |                 |                 |       |

| bit 0        | OC1MD: Out           | ompare 2 modul<br>put Compare 1 l<br>ompare 1 modul | Module Disable  | e bit             |                 |                 |       |

#### ~

#### REGISTER 11-7: RPINR12: PERIPHERAL PIN SELECT INPUT REGISTER 12 (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

|                   | R/W-0                                      | R/W-0                                                                      | R/W-0                                        | R/W-0                      | R/W-0           | R/W-0           | R/W-0           |

|-------------------|--------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------|----------------------------|-----------------|-----------------|-----------------|

| _                 |                                            |                                                                            |                                              | FLT2R<6:0>                 |                 |                 |                 |

| bit 15            |                                            |                                                                            |                                              |                            |                 |                 | bit 8           |

|                   | <b>D</b> 444 A                             | <b>D</b> 444 0                                                             | <b>D</b> 444 A                               | Date                       | <b>D</b> 444 0  | DAVA            | <b>D</b> # 44 0 |

| U-0               | R/W-0                                      | R/W-0                                                                      | R/W-0                                        | R/W-0                      | R/W-0           | R/W-0           | R/W-0           |

|                   |                                            |                                                                            |                                              | FLT1R<6:0>                 |                 |                 |                 |

| bit 7             |                                            |                                                                            |                                              |                            |                 |                 | bit C           |

| Legend:           |                                            |                                                                            |                                              |                            |                 |                 |                 |

| R = Readabl       | le bit                                     | W = Writable                                                               | bit                                          | U = Unimplen               | nented bit, rea | ad as '0'       |                 |

| -n = Value at     | t POR                                      | '1' = Bit is set                                                           |                                              | '0' = Bit is clea          | ared            | x = Bit is unkr | nown            |

| bit 14-8          | <b>FLT2R&lt;6:0&gt;</b><br>(see Table 11   | -2 for input pin                                                           | Fault 2 (FLT2)                               | ) to the Corresp<br>nbers) | onding RPn F    | Pin bits        |                 |

| bit 14-8          | FLT2R<6:0><br>(see Table 11<br>1111001 = h | : Assign PWM I                                                             | Fault 2 (FLT2)<br>selection nur<br>121       |                            | onding RPn F    | Pin bits        |                 |

| bit 14-8          | FLT2R<6:0><br>(see Table 11<br>1111001 = h | : Assign PWM I<br>I-2 for input pin<br>nput tied to RPI                    | Fault 2 (FLT2)<br>selection nur<br>121<br>P1 |                            | onding RPn F    | Pin bits        |                 |

| bit 14-8<br>bit 7 | FLT2R<6:0><br>(see Table 11<br>1111001 = h | : Assign PWM I<br>I-2 for input pin<br>nput tied to RPI<br>nput tied to CM | Fault 2 (FLT2<br>selection nur<br>121<br>P1  |                            | onding RPn F    | Pin bits        |                 |

NOTES:

#### 13.2 Timer Control Registers

| R/W-0         | U-0                                   | R/W-0                              | U-0            | U-0              | U-0             | U-0             | U-0   |

|---------------|---------------------------------------|------------------------------------|----------------|------------------|-----------------|-----------------|-------|

| TON           |                                       | TSIDL                              | —              | _                |                 |                 | _     |

| bit 15        |                                       |                                    |                |                  |                 |                 | bit 8 |

|               |                                       |                                    |                |                  |                 |                 |       |

| U-0           | R/W-0                                 | R/W-0                              | R/W-0          | R/W-0            | U-0             | R/W-0           | U-0   |

| _             | TGATE                                 | TCKPS1                             | TCKPS0         | T32              | _               | TCS             | _     |

| bit 7         |                                       |                                    |                |                  |                 |                 | bit ( |

| <u> </u>      |                                       |                                    |                |                  |                 |                 |       |

| Legend:       | - 1-:4                                |                                    |                | II II.           |                 |                 |       |

| R = Readable  |                                       | W = Writable                       |                | -                | nented bit, rea |                 |       |

| -n = Value at | PUR                                   | '1' = Bit is set                   |                | '0' = Bit is cle | areo            | x = Bit is unkn | own   |

| bit 15        | TON: Timerx                           | On hit                             |                |                  |                 |                 |       |

|               | When T32 = 2                          |                                    |                |                  |                 |                 |       |

|               | 1 = Starts 32-                        | bit Timerx/y                       |                |                  |                 |                 |       |

|               | 0 = Stops 32-                         |                                    |                |                  |                 |                 |       |

|               | <u>When T32 = 0</u><br>1 = Starts 16- |                                    |                |                  |                 |                 |       |

|               | 0 = Stops 16-                         |                                    |                |                  |                 |                 |       |

| bit 14        | Unimplemen                            | ted: Read as '                     | )'             |                  |                 |                 |       |

| bit 13        | TSIDL: Timer                          | x Stop in Idle M                   | lode bit       |                  |                 |                 |       |

|               |                                       | ues module op                      |                |                  | dle mode        |                 |       |

|               |                                       | s module opera                     |                | ode              |                 |                 |       |

| bit 12-7      | -                                     | ted: Read as '                     |                |                  |                 |                 |       |

| bit 6         |                                       | erx Gated Time                     | Accumulation   | Enable bit       |                 |                 |       |

|               | When TCS =<br>This bit is igno        |                                    |                |                  |                 |                 |       |

|               | When TCS =                            |                                    |                |                  |                 |                 |       |

|               | 1 = Gated tim                         | e accumulatior                     |                |                  |                 |                 |       |

|               |                                       | e accumulation                     |                |                  |                 |                 |       |

| bit 5-4       |                                       | : Timerx Input                     | Clock Prescal  | e Select bits    |                 |                 |       |

|               | 11 = 1:256<br>10 = 1:64               |                                    |                |                  |                 |                 |       |

|               | 01 = 1:8                              |                                    |                |                  |                 |                 |       |

|               | 00 = 1:1                              |                                    |                |                  |                 |                 |       |

| bit 3         | T32: 32-Bit Ti                        | mer Mode Sele                      | ect bit        |                  |                 |                 |       |

|               |                                       | nd Timery form<br>nd Timery act as |                |                  |                 |                 |       |

| bit 2         | Unimplemen                            | ted: Read as '                     | )'             |                  |                 |                 |       |

| bit 1         | TCS: Timerx Clock Source Select bit   |                                    |                |                  |                 |                 |       |

|               | 1 = External c<br>0 = Internal cl     | clock is from pir<br>lock (FP)     | n, TxCK (on th | ne rising edge)  |                 |                 |       |

| bit 0         | Unimplomon                            | ted: Read as '                     | ı'             |                  |                 |                 |       |

### REGISTER 13-1: TxCON: (TIMER2 AND TIMER4) CONTROL REGISTER

| R/W-0      | R/W-0                                                                    | R/W-0                                                | R/W-0                           | U-0               | U-0              | U-0                    | R/W-0        |

|------------|--------------------------------------------------------------------------|------------------------------------------------------|---------------------------------|-------------------|------------------|------------------------|--------------|

| FLTMD      | FLTOUT                                                                   | FLTTRIEN                                             | OCINV                           | —                 | _                | —                      | OC32         |

| bit 15     | ·                                                                        |                                                      |                                 |                   | ·                |                        | bit          |

|            |                                                                          |                                                      |                                 |                   |                  |                        |              |

| R/W-0      | R/W-0, HS                                                                | R/W-0                                                | R/W-0                           | R/W-1             | R/W-1            | R/W-0                  | R/W-0        |

| OCTRIC     | G TRIGSTAT                                                               | OCTRIS                                               | SYNCSEL4                        | SYNCSEL3          | SYNCSEL2         | SYNCSEL1               | SYNCSEL      |

| bit 7      |                                                                          |                                                      |                                 |                   |                  |                        | bit          |

| Legend:    |                                                                          | HS = Hardwa                                          | re Settable bit                 |                   |                  |                        |              |

| R = Reada  | able bit                                                                 | W = Writable                                         | bit                             | U = Unimplem      | nented bit, read | l as '0'               |              |

| -n = Value | at POR                                                                   | '1' = Bit is set                                     |                                 | '0' = Bit is clea | ared             | x = Bit is unkn        | iown         |

|            |                                                                          |                                                      |                                 |                   |                  |                        |              |

| bit 15     | 1 = Fault mo<br>cleared i                                                | t Mode Select b<br>ode is maintain<br>n software and | ed until the Fa<br>a new PWM pe | eriod starts      |                  |                        |              |

|            |                                                                          | de is maintaine                                      | d until the Faul                | t source is rem   | loved and a ne   | w PWM period           | starts       |

| bit 14     | FLTOUT: Fau                                                              |                                                      | . –                             |                   |                  |                        |              |

|            |                                                                          | tput is driven hi<br>tput is driven lo               |                                 |                   |                  |                        |              |

| bit 13     |                                                                          | ault Output Sta                                      |                                 |                   |                  |                        |              |

|            |                                                                          | is tri-stated on                                     |                                 | 'n                |                  |                        |              |

|            | •                                                                        | I/O state is defi                                    |                                 |                   | ault condition   |                        |              |

| bit 12     | OCINV: Outp                                                              | ut Compare x I                                       | nvert bit                       |                   |                  |                        |              |

|            |                                                                          | out is inverted<br>out is not invert                 | ed                              |                   |                  |                        |              |

| bit 11-9   | Unimplemen                                                               | ted: Read as '                                       | כי                              |                   |                  |                        |              |

| bit 8      | OC32: Casca                                                              | ide Two OCx M                                        | odules Enable                   | bit (32-bit oper  | ration)          |                        |              |

|            |                                                                          | module operate module operate                        |                                 |                   |                  |                        |              |

| bit 7      |                                                                          | tput Compare x                                       |                                 | Select bit        |                  |                        |              |

|            |                                                                          | OCx from the s                                       |                                 |                   | CSELx bits       |                        |              |

|            |                                                                          | nizes OCx with                                       |                                 |                   |                  | S                      |              |

| bit 6      | TRIGSTAT: T                                                              | imer Trigger St                                      | atus bit                        |                   |                  |                        |              |

|            |                                                                          | urce has been <sup>.</sup><br>urce has not be        |                                 |                   | d clear          |                        |              |

| bit 5      |                                                                          | put Compare x                                        |                                 | •                 |                  |                        |              |

|            | 1 = OCx is tr                                                            | • •                                                  | ·                               |                   |                  |                        |              |

|            | 0 = Output C                                                             | ompare x mod                                         | ule drives the C                | OCx pin           |                  |                        |              |

| Note 1:    | Do not use the O                                                         | Cx module as i                                       | ts own Svnchro                  | nization or Tric  | aaer source.     |                        |              |

|            | When the OCy m                                                           |                                                      | -                               |                   |                  | module uses t          | he OCv       |

|            | module as a Trigg                                                        |                                                      |                                 |                   |                  |                        |              |

| 3:         | Each Output Con<br><b>"Peripheral Trig</b><br>PTGO0 = OC1<br>PTGO1 = OC2 |                                                      |                                 |                   |                  | n source. See <b>S</b> | Section 24.0 |

|            | PTGO2 = OC3 $PTGO3 = OC4$                                                |                                                      |                                 |                   |                  |                        |              |

#### REGISTER 15-2: OCxCON2: OUTPUT COMPARE x CONTROL REGISTER 2

#### REGISTER 16-8: PDCx: PWMx GENERATOR DUTY CYCLE REGISTER

| R/W-0                              | R/W-0 | R/W-0          | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|------------------------------------|-------|----------------|-------|------------------|-----------------|-----------------|-------|

|                                    |       |                | PDC   | <15:8>           |                 |                 |       |

| bit 15                             |       |                |       |                  |                 |                 | bit 8 |

|                                    |       |                |       |                  |                 |                 |       |

| R/W-0                              | R/W-0 | R/W-0          | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                                    |       |                | PDC   | x<7:0>           |                 |                 |       |

| bit 7                              |       |                |       |                  |                 |                 | bit 0 |

|                                    |       |                |       |                  |                 |                 |       |

| Legend:                            |       |                |       |                  |                 |                 |       |

| R = Readable                       | bit   | W = Writable b | oit   | U = Unimpler     | mented bit, rea | d as '0'        |       |

| -n = Value at POR '1' = Bit is set |       |                |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

bit 15-0 **PDCx<15:0>:** PWMx Generator # Duty Cycle Value bits

#### REGISTER 16-9: PHASEx: PWMx PRIMARY PHASE-SHIFT REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|-----------------|-----------------|-------|

|                 |       |                  | PHAS  | Ex<15:8>          |                 |                 |       |

| bit 15          |       |                  |       |                   |                 |                 | bit 8 |

|                 |       |                  |       |                   |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | PHAS  | SEx<7:0>          |                 |                 |       |

| bit 7           |       |                  |       |                   |                 |                 | bit 0 |

|                 |       |                  |       |                   |                 |                 |       |

| Legend:         |       |                  |       |                   |                 |                 |       |

| R = Readable    | bit   | W = Writable b   | pit   | U = Unimplen      | nented bit, rea | ad as '0'       |       |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

bit 15-0 PHASEx<15:0>: PWMx Phase-Shift Value or Independent Time Base Period for the PWM Generator bits

Note 1: If ITB (PWMCONx<9>) = 0, the following applies based on the mode of operation: Complementary, Redundant and Push-Pull Output mode (PMOD<1:0> (IOCON<11:10>) = 00, 01 or 10), PHASEx<15:0> = Phase-shift value for PWMxH and PWMxL outputs

If ITB (PWMCONx<9>) = 1, the following applies based on the mode of operation: Complementary, Redundant and Push-Pull Output mode (PMOD<1:0> (IOCONx<11:10>) = 00, 01 or 10), PHASEx<15:0> = Independent time base period value for PWMxH and PWMxL

#### REGISTER 18-1: SPIx STAT: SPIx STATUS AND CONTROL REGISTER (CONTINUED)

- bit 1 SPITBF: SPIx Transmit Buffer Full Status bit

- 1 = Transmit not yet started, SPIxTXB is full

- 0 = Transmit started, SPIxTXB is empty

#### Standard Buffer mode:

Automatically set in hardware when core writes to the SPIxBUF location, loading SPIxTXB. Automatically cleared in hardware when SPIx module transfers data from SPIxTXB to SPIxSR.

#### Enhanced Buffer mode:

Automatically set in hardware when the CPU writes to the SPIxBUF location, loading the last available buffer location. Automatically cleared in hardware when a buffer location is available for a CPU write operation.

#### bit 0 SPIRBF: SPIx Receive Buffer Full Status bit

1 = Receive is complete, SPIxRXB is full

0 = Receive is incomplete, SPIxRXB is empty

#### Standard Buffer mode:

Automatically set in hardware when SPIx transfers data from SPIxSR to SPIxRXB. Automatically cleared in hardware when the core reads the SPIxBUF location, reading SPIxRXB.

#### Enhanced Buffer mode:

Automatically set in hardware when SPIx transfers data from SPIxSR to the buffer, filling the last unread buffer location. Automatically cleared in hardware when a buffer location is available for a transfer from SPIxSR.

### REGISTER 19-1: I2CxCON: I2Cx CONTROL REGISTER (CONTINUED)

| bit 6         | <b>STREN:</b> SCLx Clock Stretch Enable bit (when operating as I <sup>2</sup> C slave)<br>Used in conjunction with the SCLREL bit.<br>1 = Enables software or receives clock stretching<br>0 = Disables software or receives clock stretching |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5         | ACKDT: Acknowledge Data bit (when operating as I <sup>2</sup> C master, applicable during master receive)                                                                                                                                     |

|               | Value that is transmitted when the software initiates an Acknowledge sequence.<br>1 = Sends NACK during Acknowledge<br>0 = Sends ACK during Acknowledge                                                                                       |

| bit 4         | <b>ACKEN:</b> Acknowledge Sequence Enable bit (when operating as I <sup>2</sup> C master, applicable during master receive)                                                                                                                   |

|               | <ul> <li>1 = Initiates Acknowledge sequence on SDAx and SCLx pins and transmits ACKDT data bit. Hardware is clear at the end of the master Acknowledge sequence.</li> <li>0 = Acknowledge sequence is not in progress</li> </ul>              |

| bit 3         | <b>RCEN:</b> Receive Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                                   |

|               | <ul> <li>1 = Enables Receive mode for I<sup>2</sup>C. Hardware is clear at the end of the eighth bit of the master receive data byte.</li> <li>0 = Receive sequence is not in progress</li> </ul>                                             |

| bit 2         | <b>PEN:</b> Stop Condition Enable bit (when operating as $I^2C$ master)                                                                                                                                                                       |

| 511 2         | 1 = Initiates Stop condition on SDAx and SCLx pins. Hardware is clear at the end of the master Stop sequence.                                                                                                                                 |

| <b>h</b> :+ 4 | 0 = Stop condition is not in progress                                                                                                                                                                                                         |

| bit 1         | <b>RSEN:</b> Repeated Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                  |

|               | <ul> <li>1 = Initiates Repeated Start condition on SDAx and SCLx pins. Hardware is clear at the end of the<br/>master Repeated Start sequence.</li> <li>0 = Repeated Start condition is not in progress</li> </ul>                            |

| bit 0         | <b>SEN:</b> Start Condition Enable bit (when operating as $l^2C$ master)                                                                                                                                                                      |

|               | <ul> <li>1 = Initiates Start condition on SDAx and SCLx pins. Hardware is clear at the end of the master Start sequence.</li> <li>0 = Start condition is not in progress</li> </ul>                                                           |

**Note 1:** When performing master operations, ensure that the IPMIEN bit is set to '0'.

#### REGISTER 20-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 5 | <ul> <li>ADDEN: Address Character Detect bit (bit 8 of received data = 1)</li> <li>1 = Address Detect mode is enabled; if 9-bit mode is not selected, this does not take effect</li> <li>0 = Address Detect mode is disabled</li> </ul>                                                          |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4 | RIDLE: Receiver Idle bit (read-only)<br>1 = Receiver is Idle<br>0 = Receiver is active                                                                                                                                                                                                           |

| bit 3 | <b>PERR:</b> Parity Error Status bit (read-only) 1 = Parity error has been detected for the current character (character at the top of the receive FIFO) 0 = Parity error has not been detected                                                                                                  |

| bit 2 | <pre>FERR: Framing Error Status bit (read-only) 1 = Framing error has been detected for the current character (character at the top of the receive FIFO) 0 = Framing error has not been detected</pre>                                                                                           |

| bit 1 | <ul> <li>OERR: Receive Buffer Overrun Error Status bit (clear/read-only)</li> <li>1 = Receive buffer has overflowed</li> <li>0 = Receive buffer has not overflowed; clearing a previously set OERR bit (1 → 0 transition) resets the receiver buffer and the UxRSR to the empty state</li> </ul> |

| bit 0 | <ul> <li>URXDA: UARTx Receive Buffer Data Available bit (read-only)</li> <li>1 = Receive buffer has data, at least one more character can be read</li> <li>0 = Receive buffer is empty</li> </ul>                                                                                                |

**Note 1:** Refer to the "**UART**" (DS70582) section in the "*dsPIC33/PIC24 Family Reference Manual*" for information on enabling the UARTx module for transmit operation.

| U-0           | U-0                                                                                       | U-0                              | U-0            | U-0                                | U-0    | U-0                | U-0    |  |  |

|---------------|-------------------------------------------------------------------------------------------|----------------------------------|----------------|------------------------------------|--------|--------------------|--------|--|--|

| _             | —                                                                                         | —                                | _              | —                                  | —      | —                  | —      |  |  |

| bit 15        |                                                                                           |                                  |                |                                    |        |                    | bit 8  |  |  |

|               |                                                                                           |                                  |                |                                    |        |                    |        |  |  |

| U-0           | U-0                                                                                       | U-0                              | R-0            | R-0                                | R-0    | R-0                | R-0    |  |  |

| —             | —                                                                                         | —                                | DNCNT4         | DNCNT3                             | DNCNT2 | DNCNT1             | DNCNT0 |  |  |

| bit 7         |                                                                                           |                                  |                |                                    |        |                    | bit 0  |  |  |

|               |                                                                                           |                                  |                |                                    |        |                    |        |  |  |

| Legend:       |                                                                                           |                                  |                |                                    |        |                    |        |  |  |

| R = Readabl   | e bit                                                                                     | W = Writable bit                 |                | U = Unimplemented bit, read as '0' |        |                    |        |  |  |

| -n = Value at | POR                                                                                       | '1' = Bit is set                 |                | '0' = Bit is cleared               |        | x = Bit is unknown |        |  |  |

|               |                                                                                           |                                  |                |                                    |        |                    |        |  |  |

| bit 15-5      | Unimplemen                                                                                | ted: Read as '                   | 0'             |                                    |        |                    |        |  |  |

| bit 4-0       | DNCNT<4:0>                                                                                | : DeviceNet™                     | Filter Bit Num | iber bits                          |        |                    |        |  |  |

|               | 10010-11111 = Invalid selection<br>10001 = Compares up to Data Byte 3, bit 6 with EID<17> |                                  |                |                                    |        |                    |        |  |  |

|               | •                                                                                         |                                  |                |                                    |        |                    |        |  |  |

|               | •                                                                                         |                                  |                |                                    |        |                    |        |  |  |

|               | •                                                                                         |                                  |                |                                    |        |                    |        |  |  |

|               |                                                                                           | npares up to Da<br>s not compare | •              | 7 with EID<0>                      |        |                    |        |  |  |

| U-0                     | U-0                                  | U-0                                | R-0     | R-0              | R-0             | R-0              | R-0     |  |  |

|-------------------------|--------------------------------------|------------------------------------|---------|------------------|-----------------|------------------|---------|--|--|

| _                       | _                                    |                                    | FILHIT4 | FILHIT3          | FILHIT2         | FILHIT1          | FILHIT0 |  |  |

| bit 15                  | <b>I</b>                             |                                    |         |                  |                 |                  | bit 8   |  |  |

|                         |                                      |                                    |         |                  |                 |                  |         |  |  |

| U-0                     | R-1                                  | R-0                                | R-0     | R-0              | R-0             | R-0              | R-0     |  |  |

| _                       | ICODE6                               | ICODE5                             | ICODE4  | ICODE3           | ICODE2          | ICODE1           | ICODE0  |  |  |

| bit 7                   |                                      |                                    |         |                  |                 |                  | bit     |  |  |

| Logondi                 |                                      |                                    |         |                  |                 |                  |         |  |  |

| Legend:<br>R = Readable | - hit                                | W = Writable                       | hit     | LI – Unimplor    | mented bit, rea | d as '0'         |         |  |  |

| -n = Value at           |                                      | '1' = Bit is set                   |         | '0' = Bit is cle |                 | x = Bit is unkr  |         |  |  |

|                         | FUR                                  |                                    |         |                  |                 | x – Dit is uliki |         |  |  |

| bit 15-13               | Unimplemen                           | ted: Read as '                     | 0'      |                  |                 |                  |         |  |  |

| bit 12-8                | =                                    | Filter Hit Num                     |         |                  |                 |                  |         |  |  |

|                         |                                      | 1 = Reserved                       |         |                  |                 |                  |         |  |  |

|                         | 01111 <b>= Filte</b>                 | er 15                              |         |                  |                 |                  |         |  |  |

|                         | •                                    |                                    |         |                  |                 |                  |         |  |  |

|                         | •                                    |                                    |         |                  |                 |                  |         |  |  |

|                         | •                                    |                                    |         |                  |                 |                  |         |  |  |

|                         | 00001 = Filter 1<br>00000 = Filter 0 |                                    |         |                  |                 |                  |         |  |  |

| bit 7                   |                                      | ted: Read as '                     | 0'      |                  |                 |                  |         |  |  |

| bit 6-0                 | ICODE<6:0>: Interrupt Flag Code bits |                                    |         |                  |                 |                  |         |  |  |

|                         | 1000101-1111111 = Reserved           |                                    |         |                  |                 |                  |         |  |  |

|                         |                                      | IFO almost full                    |         |                  |                 |                  |         |  |  |

|                         |                                      | leceiver overflo                   |         |                  |                 |                  |         |  |  |

|                         | 1000010 = K<br>1000001 = E           | Vake-up interru<br>rror interrupt  | μ       |                  |                 |                  |         |  |  |

|                         | 1000000 = N                          |                                    |         |                  |                 |                  |         |  |  |

|                         | •                                    |                                    |         |                  |                 |                  |         |  |  |

|                         | •                                    |                                    |         |                  |                 |                  |         |  |  |

|                         | •                                    |                                    |         |                  |                 |                  |         |  |  |

|                         |                                      | 11111 = Rese                       |         |                  |                 |                  |         |  |  |

|                         | •                                    | B15 buffer inte                    | inupt   |                  |                 |                  |         |  |  |

|                         | •                                    |                                    |         |                  |                 |                  |         |  |  |

|                         | •                                    |                                    |         |                  |                 |                  |         |  |  |

|                         | 0001001 <b>= R</b>                   | B9 buffer inter                    | rupt    |                  |                 |                  |         |  |  |

|                         |                                      | B8 buffer inter                    |         |                  |                 |                  |         |  |  |

|                         |                                      | RB7 buffer inte<br>RB6 buffer inte |         |                  |                 |                  |         |  |  |

|                         |                                      | RB5 buffer inte                    |         |                  |                 |                  |         |  |  |

|                         |                                      | RB4 buffer inte                    |         |                  |                 |                  |         |  |  |

|                         | 0000011 <b>= T</b>                   | RB3 buffer inte                    | errupt  |                  |                 |                  |         |  |  |

|                         |                                      |                                    |         |                  |                 |                  |         |  |  |

|                         |                                      | RB2 buffer inte<br>RB1 buffer inte |         |                  |                 |                  |         |  |  |

#### REGISTER 21-3: CxVEC: ECANx INTERRUPT CODE REGISTER

| R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1  | R/W-1  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| FLTEN15 | FLTEN14 | FLTEN13 | FLTEN12 | FLTEN11 | FLTEN10 | FLTEN9 | FLTEN8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

|         |         |         |         |         |         |        |        |

| R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1  | R/W-1  |

| FLTEN7  | FLTEN6  | FLTEN5  | FLTEN4  | FLTEN3  | FLTEN2  | FLTEN1 | FLTEN0 |

| bit 7   |         |         |         |         |         |        | bit 0  |

|         |         |         |         |         |         |        |        |

| Legend: |         |         |         |         |         |        |        |

#### REGISTER 21-11: CxFEN1: ECANx ACCEPTANCE FILTER ENABLE REGISTER 1

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-0

FLTEN<15:0>: Enable Filter n to Accept Messages bits

1 = Enables Filter n

0 = Disables Filter n

REGISTER 21-12: CxBUFPNT1: ECANx FILTER 0-3 BUFFER POINTER REGISTER 1

| R/W-0                                                                                                                                                                                                                                                   | R/W-0                                                                                     | R/W-0            | R/W-0            | R/W-0                                   | R/W-0          | R/W-0  | R/W-0 |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------------------|------------------|-----------------------------------------|----------------|--------|-------|--|--|

|                                                                                                                                                                                                                                                         | F3BP<3:0>                                                                                 |                  |                  |                                         | F2BP<3:0>      |        |       |  |  |

| bit 15                                                                                                                                                                                                                                                  |                                                                                           |                  |                  |                                         |                |        | bit 8 |  |  |

| R/W-0                                                                                                                                                                                                                                                   | R/W-0                                                                                     | R/W-0            | R/W-0            | R/W-0                                   | R/W-0          | R/W-0  | R/W-0 |  |  |

|                                                                                                                                                                                                                                                         | F1BI                                                                                      | P<3:0>           |                  |                                         | F0BI           | P<3:0> |       |  |  |

| bit 7                                                                                                                                                                                                                                                   |                                                                                           |                  |                  |                                         |                |        | bit ( |  |  |

| Legend:                                                                                                                                                                                                                                                 |                                                                                           |                  |                  |                                         |                |        |       |  |  |

| R = Readable                                                                                                                                                                                                                                            | e bit                                                                                     | W = Writable     | bit              | U = Unimplemented bit, read as '0'      |                |        |       |  |  |

| -n = Value at                                                                                                                                                                                                                                           | POR                                                                                       | '1' = Bit is set |                  | '0' = Bit is cleared x = Bit is unknown |                |        | nown  |  |  |

| bit 15-12 <b>F3BP&lt;3:0&gt;:</b> RX Buffer Mask for Filter 3 to<br>1111 = Filter hits received in RX FIFO bu<br>1110 = Filter hits received in RX Buffer 1<br>0001 = Filter hits received in RX Buffer 1<br>0000 = Filter hits received in RX Buffer 0 |                                                                                           |                  |                  | iffer                                   |                |        |       |  |  |

| bit 11-8                                                                                                                                                                                                                                                | F2BP<3:0>                                                                                 | : RX Buffer Mas  | k for Filter 2 b | oits (same value                        | s as bits<15:1 | 2>)    |       |  |  |

| bit 7-4                                                                                                                                                                                                                                                 | F1BP<3:0>                                                                                 | : RX Buffer Mas  | k for Filter 1 k | oits (same value                        | s as bits<15:1 | 2>)    |       |  |  |

|                                                                                                                                                                                                                                                         | 3-0 <b>F0BP&lt;3:0&gt;:</b> RX Buffer Mask for Filter 0 bits (same values as bits<15:12>) |                  |                  |                                         |                |        |       |  |  |

### 23.0 10-BIT/12-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

- **Note 1:** This data sheet summarizes the features of the dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. То complement the information in this data sheet. refer to "Analog-to-Digital Converter (ADC)" (DS70621) in the "dsPIC33/PIC24 Family Reference Manual', which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices have one ADC module. The ADC module supports up to 16 analog input channels.

On ADC1, the AD12B bit (AD1CON1<10>) allows the ADC module to be configured by the user as either a 10-bit, 4 Sample-and-Hold (S&H) ADC (default configuration) or a 12-bit, 1 S&H ADC.

Note: The ADC module needs to be disabled before modifying the AD12B bit.

### 23.1 Key Features

#### 23.1.1 10-BIT ADC CONFIGURATION

The 10-bit ADC configuration has the following key features:

- Successive Approximation (SAR) conversion

- · Conversion speeds of up to 1.1 Msps

- · Up to 16 analog input pins

- Connections to three internal op amps