Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 60 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 35                                                                             |

| Program Memory Size        | 512KB (170K x 24)                                                              |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | · ·                                                                            |

| RAM Size                   | 24K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 9x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 48-UFQFN Exposed Pad                                                           |

| Supplier Device Package    | 48-UQFN (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep512gp204-e-mv |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| IABLE 4   | -14:  | PVVIVI G | ENERA  | ATOR 2 REGISTER MAP FOR dSPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY |              |          |         |          |            |           |         |         |         |          |          |         |         |               |

|-----------|-------|----------|--------|--------------------------------------------------------------------------------|--------------|----------|---------|----------|------------|-----------|---------|---------|---------|----------|----------|---------|---------|---------------|

| File Name | Addr. | Bit 15   | Bit 14 | Bit 13                                                                         | Bit 12       | Bit 11   | Bit 10  | Bit 9    | Bit 8      | Bit 7     | Bit 6   | Bit 5   | Bit 4   | Bit 3    | Bit 2    | Bit 1   | Bit 0   | All<br>Resets |

| PWMCON2   | 0C40  | FLTSTAT  | CLSTAT | TRGSTAT                                                                        | FLTIEN       | CLIEN    | TRGIEN  | ITB      | MDCS       | DTC       | <1:0>   | DTCP    | _       | MTBS     | CAM      | XPRES   | IUE     | 0000          |

| IOCON2    | 0C42  | PENH     | PENL   | POLH                                                                           | POLL         | PMOD     | 0<1:0>  | OVRENH   | OVRENL     | OVRDA     | \T<1:0> | FLTD    | \T<1:0> | CLDA     | AT<1:0>  | SWAP    | OSYNC   | C000          |

| FCLCON2   | 0C44  | _        |        | (                                                                              | CLSRC<4:0    | )>       |         | CLPOL    | CLMOD      |           | FLT     | SRC<4:0 | >       |          | FLTPOL   | FLTMO   | D<1:0>  | 00F8          |

| PDC2      | 0C46  |          |        |                                                                                | PDC2<15:0>   |          |         |          |            |           |         |         | 0000    |          |          |         |         |               |

| PHASE2    | 0C48  |          |        |                                                                                | PHASE2<15:0> |          |         |          |            |           |         |         | 0000    |          |          |         |         |               |

| DTR2      | 0C4A  | _        | _      |                                                                                |              |          |         |          | [          | DTR2<13:0 | >       |         |         |          |          |         |         | 0000          |

| ALTDTR2   | 0C4C  | _        | _      |                                                                                |              |          |         |          | AL         | TDTR2<13  | :0>     |         |         |          |          |         |         | 0000          |

| TRIG2     | 0C52  |          |        |                                                                                |              |          |         | TI       | RGCMP<15:0 | )>        |         |         |         |          |          |         |         | 0000          |

| TRGCON2   | 0C54  |          | TRGDI  | V<3:0>                                                                         |              | _        | —       | _        | _          | _         | -       |         |         | TRO      | GSTRT<5: | 0>      |         | 0000          |

| LEBCON2   | 0C5A  | PHR      | PHF    | PLR                                                                            | PLF          | FLTLEBEN | CLLEBEN | _        | _          | _         | -       | BCH     | BCL     | BPHH     | BPHL     | BPLH    | BPLL    | 0000          |

| LEBDLY2   | 0C5C  | _        | _      | LEB<11:0>                                                                      |              |          |         |          |            |           | 0000    |         |         |          |          |         |         |               |

| AUXCON2   | 0C5E  | _        | _      | —                                                                              | —            |          | BLANK   | SEL<3:0> |            | _         | —       |         | CHOPS   | SEL<3:0> |          | CHOPHEN | CHOPLEN | 0000          |

I- DIGGOEDV/VMOGOV/EGV AND DIGGAEDV/VMOGOV DEVICED ONLY

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-15: PWM GENERATOR 3 REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY

| File Name | Addr. | Bit 15  | Bit 14 | Bit 13  | Bit 12                                                                   | Bit 11   | Bit 10  | Bit 9  | Bit 8     | Bit 7     | Bit 6    | Bit 5   | Bit 4   | Bit 3 | Bit 2    | Bit 1 | Bit 0  | All<br>Resets |

|-----------|-------|---------|--------|---------|--------------------------------------------------------------------------|----------|---------|--------|-----------|-----------|----------|---------|---------|-------|----------|-------|--------|---------------|

| PWMCON3   | 0C60  | FLTSTAT | CLSTAT | TRGSTAT | FLTIEN                                                                   | CLIEN    | TRGIEN  | ITB    | MDCS      | DTC<      | <1:0>    | DTCP    | —       | MTBS  | CAM      | XPRES | IUE    | 0000          |

| IOCON3    | 0C62  | PENH    | PENL   | POLH    | POLL                                                                     | PMOD     | )<1:0>  | OVRENH | OVRENL    | OVRDA     | T<1:0>   | FLTD    | AT<1:0> | CLD   | AT<1:0>  | SWAP  | OSYNC  | C000          |

| FCLCON3   | 0C64  |         |        | (       | CLSRC<4:0                                                                | )>       |         | CLPOL  | CLMOD     |           | FLT      | SRC<4:0 | >       |       | FLTPOL   | FLTMO | D<1:0> | 00F8          |

| PDC3      | 0C66  |         |        |         | PDC3<15:0>                                                               |          |         |        |           |           |          |         | 0000    |       |          |       |        |               |

| PHASE3    | 0C68  |         |        |         | PHASE3<15:0> 0000                                                        |          |         |        |           |           |          |         | 0000    |       |          |       |        |               |

| DTR3      | 0C6A  |         | —      |         |                                                                          |          |         |        | [         | DTR3<13:0 | >        |         |         |       |          |       |        | 0000          |

| ALTDTR3   | 0C6C  |         | —      |         |                                                                          |          |         |        | AL        | TDTR3<13  | :0>      |         |         |       |          |       |        | 0000          |

| TRIG3     | 0C72  |         |        |         |                                                                          |          |         | Т      | RGCMP<15: | 0>        |          |         |         |       |          |       |        | 0000          |

| TRGCON3   | 0C74  |         | TRGDI  | V<3:0>  |                                                                          | _        | _       | _      | _         | _         | _        |         |         | TR    | GSTRT<5: | 0>    |        | 0000          |

| LEBCON3   | 0C7A  | PHR     | PHF    | PLR     | PLF                                                                      | FLTLEBEN | CLLEBEN | —      | —         |           | —        | BCH     | BCL     | BPHH  | BPHL     | BPLH  | BPLL   | 0000          |

| LEBDLY3   | 0C7C  |         | —      | _       | _                                                                        |          |         |        |           |           | LEB<11:0 | )>      |         |       |          |       |        | 0000          |

| AUXCON3   | 0C7E  |         | —      | —       | —     BLANKSEL<3:0>     —     —     CHOPSEL<3:0>     CHOPHEN     CHOPLEN |          |         |        |           |           | 0000     |         |         |       |          |       |        |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

.

----

.

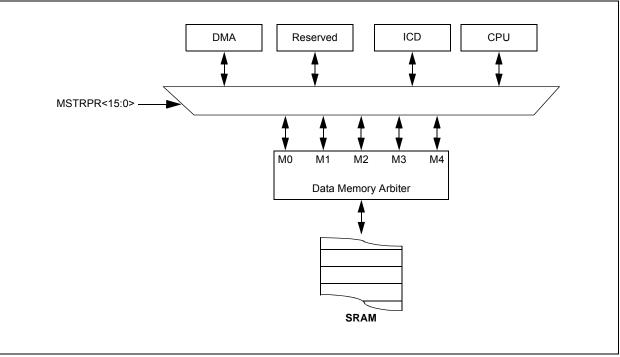

# 4.4.3 DATA MEMORY ARBITRATION AND BUS MASTER PRIORITY

EDS accesses from bus masters in the system are arbitrated.

The arbiter for data memory (including EDS) arbitrates between the CPU, the DMA and the ICD module. In the event of coincidental access to a bus by the bus masters, the arbiter determines which bus master access has the highest priority. The other bus masters are suspended and processed after the access of the bus by the bus master with the highest priority.

By default, the CPU is Bus Master 0 (M0) with the highest priority and the ICD is Bus Master 4 (M4) with the lowest priority. The remaining bus master (DMA Controller) is allocated to M3 (M1 and M2 are reserved and cannot be used). The user application may raise or lower the priority of the DMA Controller to be above that of the CPU by setting the appropriate bits in the EDS Bus Master Priority Control (MSTRPR) register. All bus masters with raised priorities will maintain the same priority relationship relative to each other (i.e., M1 being highest and M3 being lowest, with M2 in between). Also, all the bus masters with priorities below

### FIGURE 4-18: ARBITER ARCHITECTURE

that of the CPU maintain the same priority relationship relative to each other. The priority schemes for bus masters with different MSTRPR values are tabulated in Table 4-62.

This bus master priority control allows the user application to manipulate the real-time response of the system, either statically during initialization or dynamically in response to real-time events.

| TABLE 4-62: | DATA MEMORY BUS  |

|-------------|------------------|

|             | ARBITER PRIORITY |

| Drierity     | MSTRPR<15:0> Bit Setting <sup>(1)</sup> |          |  |  |  |  |

|--------------|-----------------------------------------|----------|--|--|--|--|

| Priority     | 0x0000                                  | 0x0020   |  |  |  |  |

| M0 (highest) | CPU                                     | DMA      |  |  |  |  |

| M1           | Reserved                                | CPU      |  |  |  |  |

| M2           | Reserved                                | Reserved |  |  |  |  |

| M3           | DMA                                     | Reserved |  |  |  |  |

| M4 (lowest)  | ICD                                     | ICD      |  |  |  |  |

**Note 1:** All other values of MSTRPR<15:0> are reserved.

| R/SO-0 <sup>(1</sup>         | ) R/W-0 <sup>(1)</sup>                                                                                                    | R/W-0 <sup>(1)</sup>                                                                                                                                                                   | R/W-0                         | U-0                     | U-0                     | U-0                     | U-0                    |  |  |  |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-------------------------|-------------------------|-------------------------|------------------------|--|--|--|

| WR                           | WREN                                                                                                                      | WRERR                                                                                                                                                                                  | NVMSIDL <sup>(2)</sup>        | _                       |                         | —                       |                        |  |  |  |

| bit 15                       | I                                                                                                                         | 1                                                                                                                                                                                      | 1                             |                         |                         |                         | bit 8                  |  |  |  |

|                              |                                                                                                                           |                                                                                                                                                                                        |                               |                         |                         |                         |                        |  |  |  |

| U-0                          | U-0                                                                                                                       | U-0                                                                                                                                                                                    | U-0                           | R/W-0 <sup>(1)</sup>    | R/W-0 <sup>(1)</sup>    | R/W-0 <sup>(1)</sup>    | R/W-0 <sup>(1)</sup>   |  |  |  |

| _                            | —                                                                                                                         | —                                                                                                                                                                                      | —                             | NVMOP3 <sup>(3,4)</sup> | NVMOP2 <sup>(3,4)</sup> | NVMOP1 <sup>(3,4)</sup> | NVMOP0 <sup>(3,4</sup> |  |  |  |

| bit 7                        |                                                                                                                           |                                                                                                                                                                                        |                               |                         |                         |                         | bit (                  |  |  |  |

| lagandi                      |                                                                                                                           | SO - Sottab                                                                                                                                                                            | la Only hit                   |                         |                         |                         |                        |  |  |  |

| L <b>egend:</b><br>R = Reada | ble hit                                                                                                                   | SO = Settab<br>W = Writable                                                                                                                                                            | -                             | II – I Inimplem         | nented bit, read        | ae 'O'                  |                        |  |  |  |

| -n = Value                   |                                                                                                                           | '1' = Bit is se                                                                                                                                                                        |                               | '0' = Bit is clea       |                         | x = Bit is unkr         |                        |  |  |  |

|                              |                                                                                                                           | 1 - Dit 13 30                                                                                                                                                                          |                               |                         |                         |                         | lowin                  |  |  |  |

| bit 15                       | WR: Write Co                                                                                                              | ontrol bit(1)                                                                                                                                                                          |                               |                         |                         |                         |                        |  |  |  |

|                              |                                                                                                                           |                                                                                                                                                                                        | ory program or                | erase operation         | on; the operatio        | n is self-timed         | and the bit is         |  |  |  |

|                              | cleared b                                                                                                                 | y hardware o                                                                                                                                                                           | nce the operati               | on is complete          |                         |                         |                        |  |  |  |

|                              | <ul> <li>0 = Program or erase operation is complete and inactive</li> <li>WREN: Write Enable bit<sup>(1)</sup></li> </ul> |                                                                                                                                                                                        |                               |                         |                         |                         |                        |  |  |  |

| bit 14                       |                                                                                                                           | 1 = Enables Flash program/erase operations                                                                                                                                             |                               |                         |                         |                         |                        |  |  |  |

|                              |                                                                                                                           | <ul> <li>0 = Inhibits Flash program/erase operations</li> </ul>                                                                                                                        |                               |                         |                         |                         |                        |  |  |  |

| oit 13                       |                                                                                                                           | WRERR: Write Sequence Error Flag bit <sup>(1)</sup>                                                                                                                                    |                               |                         |                         |                         |                        |  |  |  |

|                              | 1 = An impro                                                                                                              | 1 = An improper program or erase sequence attempt or termination has occurred (bit is set automatically                                                                                |                               |                         |                         |                         |                        |  |  |  |

|                              |                                                                                                                           | et attempt of th                                                                                                                                                                       | e WR bit)<br>operation com    | olotod pormally         |                         |                         |                        |  |  |  |

| bit 12                       |                                                                                                                           |                                                                                                                                                                                        | le Control bit <sup>(2)</sup> | Sieteu normaliy         |                         |                         |                        |  |  |  |

|                              |                                                                                                                           |                                                                                                                                                                                        | r goes into Star              | ndbv mode duri          | ina Idle mode           |                         |                        |  |  |  |

|                              |                                                                                                                           |                                                                                                                                                                                        | r is active durin             |                         |                         |                         |                        |  |  |  |

| bit 11-4                     | Unimplemen                                                                                                                | ted: Read as                                                                                                                                                                           | '0'                           |                         |                         |                         |                        |  |  |  |

| bit 3-0                      | NVMOP<3:0>                                                                                                                | NVM Operation                                                                                                                                                                          | ation Select bits             | <sub>3</sub> (1,3,4)    |                         |                         |                        |  |  |  |

|                              | 1111 <b>= Rese</b>                                                                                                        |                                                                                                                                                                                        |                               |                         |                         |                         |                        |  |  |  |

|                              | 1110 = Rese<br>1101 = Rese                                                                                                |                                                                                                                                                                                        |                               |                         |                         |                         |                        |  |  |  |

|                              | 1100 <b>= Rese</b>                                                                                                        |                                                                                                                                                                                        |                               |                         |                         |                         |                        |  |  |  |

|                              | 1011 <b>= Rese</b>                                                                                                        |                                                                                                                                                                                        |                               |                         |                         |                         |                        |  |  |  |

|                              | 1010 = Rese<br>0011 = Memo                                                                                                |                                                                                                                                                                                        | e operation                   |                         |                         |                         |                        |  |  |  |

|                              | 0010 = Rese                                                                                                               | rved                                                                                                                                                                                   | -                             |                         |                         |                         |                        |  |  |  |

|                              |                                                                                                                           |                                                                                                                                                                                        | ord program ope               | eration <sup>(5)</sup>  |                         |                         |                        |  |  |  |

|                              | 0000 <b>= Rese</b>                                                                                                        | rvea                                                                                                                                                                                   |                               |                         |                         |                         |                        |  |  |  |

|                              | These bits can onl                                                                                                        | -                                                                                                                                                                                      |                               |                         |                         |                         |                        |  |  |  |

|                              | If this bit is set, the                                                                                                   |                                                                                                                                                                                        |                               |                         | d upon exiting lo       | dle mode, there         | is a delay             |  |  |  |

|                              | (TVREG) before Flash memory becomes operational.<br>All other combinations of NVMOP<3:0> are unimplemented.               |                                                                                                                                                                                        |                               |                         |                         |                         |                        |  |  |  |

| <b>.</b> .                   |                                                                                                                           |                                                                                                                                                                                        |                               |                         |                         |                         |                        |  |  |  |

| 4:                           | Execution of the P                                                                                                        | cution of the PWRSAV instruction is ignored while any of the NVM operations are in progress.<br>adjacent words on a 4-word boundary are programmed during execution of this operation. |                               |                         |                         |                         |                        |  |  |  |

## REGISTER 5-1: NVMCON: NONVOLATILE MEMORY (NVM) CONTROL REGISTER

#### REGISTER 8-3: DMAXSTAH: DMA CHANNEL X START ADDRESS REGISTER A (HIGH)

| U-0            | U-0   | U-0            | U-0   | U-0          | U-0              | U-0    | U-0   |

|----------------|-------|----------------|-------|--------------|------------------|--------|-------|

| —              | _     | —              | —     | —            | —                | —      | —     |

| bit 15         |       |                |       |              |                  |        | bit 8 |

|                |       |                |       |              |                  |        |       |

| R/W-0          | R/W-0 | R/W-0          | R/W-0 | R/W-0        | R/W-0            | R/W-0  | R/W-0 |

|                |       |                | STA<  | 23:16>       |                  |        |       |

| bit 7          |       |                |       |              |                  |        | bit 0 |

|                |       |                |       |              |                  |        |       |

| Legend:        |       |                |       |              |                  |        |       |

| R = Readable b | oit   | W = Writable b | it    | U = Unimpler | mented bit, read | as '0' |       |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

|-------------------|------------------|----------------------|--------------------|

|                   |                  |                      |                    |

#### bit 15-8 Unimplemented: Read as '0'

bit 7-0 STA<23:16>: Primary Start Address bits (source or destination)

#### REGISTER 8-4: DMAXSTAL: DMA CHANNEL x START ADDRESS REGISTER A (LOW)

| R/W-0                                                                      | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0     | R/W-0 | R/W-0 |

|----------------------------------------------------------------------------|-------|-------|-------|--------|-----------|-------|-------|

|                                                                            |       |       | STA   | <15:8> |           |       |       |

| bit 15                                                                     |       |       |       |        |           |       | bit 8 |

|                                                                            |       |       |       |        |           |       |       |

| R/W-0                                                                      | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0     | R/W-0 | R/W-0 |

|                                                                            |       |       | STA   | A<7:0> |           |       |       |

| bit 7                                                                      |       |       |       |        |           |       | bit 0 |

|                                                                            |       |       |       |        |           |       |       |

| Legend:                                                                    |       |       |       |        |           |       |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'       |       |       |       |        | ad as '0' |       |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |       |       |       |        | nown      |       |       |

bit 15-0 STA<15:0>: Primary Start Address bits (source or destination)

# 9.3 Oscillator Control Registers

# REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1)</sup>

| U-0            | R-0                                                                                                | R-0                                  | R-0                                | U-0                                | R/W-y                              | R/W-y                | R/W-y                |  |  |

|----------------|----------------------------------------------------------------------------------------------------|--------------------------------------|------------------------------------|------------------------------------|------------------------------------|----------------------|----------------------|--|--|

| _              | COSC2                                                                                              | COSC1                                | COSC0                              | —                                  | NOSC2 <sup>(2)</sup>               | NOSC1 <sup>(2)</sup> | NOSCO <sup>(2)</sup> |  |  |

| bit 15         |                                                                                                    |                                      |                                    |                                    |                                    |                      | bit 8                |  |  |

| R/W-0          | R/W-0                                                                                              | R-0                                  | U-0                                | R/W-0                              | U-0                                | U-0                  | R/W-0                |  |  |

| CLKLOC         | CK IOLOCK                                                                                          | IOLOCK LOCK - CF <sup>(3)</sup>      |                                    |                                    |                                    |                      |                      |  |  |

| bit 7          |                                                                                                    |                                      |                                    |                                    |                                    |                      | bit (                |  |  |

| Legend:        |                                                                                                    | y = Value set                        | from Configur                      | ation bits on F                    | POR                                |                      |                      |  |  |

| R = Reada      | able bit                                                                                           | W = Writable                         | -                                  |                                    | mented bit, read                   | l as '0'             |                      |  |  |

| -n = Value     | n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown                          |                                      |                                    |                                    |                                    |                      |                      |  |  |

| hit 1 <i>5</i> | Unimplemen                                                                                         | ted. Dood oo                         | 0'                                 |                                    |                                    |                      |                      |  |  |

| bit 15         | -                                                                                                  | ted: Read as                         |                                    |                                    |                                    |                      |                      |  |  |

| bit 14-12      |                                                                                                    | Current Oscill                       |                                    |                                    | /)                                 |                      |                      |  |  |

|                |                                                                                                    | C Oscillator (F<br>C Oscillator (F   |                                    |                                    |                                    |                      |                      |  |  |

|                |                                                                                                    | ower RC Oscil                        |                                    |                                    |                                    |                      |                      |  |  |

|                | 100 = Reserv                                                                                       |                                      | ()                                 |                                    |                                    |                      |                      |  |  |

|                |                                                                                                    | y Oscillator (X                      |                                    | h PLL                              |                                    |                      |                      |  |  |

|                |                                                                                                    | y Oscillator (X                      |                                    |                                    |                                    |                      |                      |  |  |

|                | 001 = Fast RC Oscillator (FRC) with Divide-by-N and PLL (FRCPLL)<br>000 = Fast RC Oscillator (FRC) |                                      |                                    |                                    |                                    |                      |                      |  |  |

| bit 11         |                                                                                                    | Unimplemented: Read as '0'           |                                    |                                    |                                    |                      |                      |  |  |

| bit 10-8       | NOSC<2:0>:                                                                                         | New Oscillato                        | r Selection bits                   | <sub>S</sub> (2)                   |                                    |                      |                      |  |  |

|                | 111 = Fast R                                                                                       | C Oscillator (F                      | RC) with Divid                     | le-by-n                            |                                    |                      |                      |  |  |

|                |                                                                                                    | C Oscillator (F                      |                                    | le-by-16                           |                                    |                      |                      |  |  |

|                |                                                                                                    | ower RC Oscil                        | ator (LPRC)                        |                                    |                                    |                      |                      |  |  |

|                | 100 = Reserv                                                                                       | /ed<br>y Oscillator (X               |                                    |                                    |                                    |                      |                      |  |  |

|                |                                                                                                    | y Oscillator (X                      |                                    | IFLL                               |                                    |                      |                      |  |  |

|                |                                                                                                    | C Oscillator (F                      |                                    | le-by-N and Pl                     | LL (FRCPLL)                        |                      |                      |  |  |

|                |                                                                                                    | C Oscillator (F                      |                                    | ,                                  | ,                                  |                      |                      |  |  |

| bit 7          |                                                                                                    | Clock Lock Ena                       |                                    |                                    |                                    |                      |                      |  |  |

|                |                                                                                                    |                                      |                                    | configurations                     | are locked; if (F                  | =CKSM0 = 0), t       | then clock and       |  |  |

|                |                                                                                                    | figurations may<br>d PLL selectio    |                                    | ked, configurat                    | ions may be mo                     | odified              |                      |  |  |

| bit 6          |                                                                                                    | Lock Enable b                        |                                    | -                                  | -                                  |                      |                      |  |  |

|                | 1 = I/O lock is                                                                                    | s active                             |                                    |                                    |                                    |                      |                      |  |  |

|                | 0 = I/O lock is not active                                                                         |                                      |                                    |                                    |                                    |                      |                      |  |  |

| bit 5          | LOCK: PLL L                                                                                        | ock Status bit                       | (read-only)                        |                                    |                                    |                      |                      |  |  |

|                |                                                                                                    | s that PLL is in<br>s that PLL is ou |                                    |                                    | satisfied<br>progress or PLL       | is disabled          |                      |  |  |

| Note 1:        | Writes to this regis                                                                               |                                      |                                    |                                    |                                    |                      | ʻdsPIC33/            |  |  |

| 2:             | Direct clock switch<br>This applies to cloo<br>mode as a transitio                                 | es between ar<br>ck switches in      | y primary osci<br>either directior | llator mode wi<br>n. In these inst | th PLL and FRC<br>ances, the appli | PLL mode are         |                      |  |  |

| 0              | This bit should only                                                                               |                                      |                                    |                                    |                                    |                      |                      |  |  |

**3:** This bit should only be cleared in software. Setting the bit in software (= 1) will have the same effect as an actual oscillator failure and trigger an oscillator failure trap.

| REGISTER                          | TU-5: PIVID6                | . PERIPHER       |                           | DISABLE C         | UNIROL RE             | GISIER 6              |                       |

|-----------------------------------|-----------------------------|------------------|---------------------------|-------------------|-----------------------|-----------------------|-----------------------|

| U-0                               | U-0                         | U-0              | U-0                       | U-0               | R/W-0                 | R/W-0                 | R/W-0                 |

| —                                 | —                           | —                | —                         | —                 | PWM3MD <sup>(1)</sup> | PWM2MD <sup>(1)</sup> | PWM1MD <sup>(1)</sup> |

| bit 15                            |                             |                  |                           |                   |                       |                       | bit 8                 |

|                                   |                             |                  |                           |                   |                       |                       |                       |

| U-0                               | U-0                         | U-0              | U-0                       | U-0               | U-0                   | U-0                   | U-0                   |

|                                   |                             |                  |                           |                   |                       |                       |                       |

| bit 7                             |                             |                  |                           |                   |                       |                       | bit 0                 |

|                                   |                             |                  |                           |                   |                       |                       |                       |

| Legend:                           |                             |                  |                           |                   |                       |                       |                       |

| R = Readable bit W = Writable bit |                             |                  | bit                       | U = Unimplen      | nented bit, read      | l as '0'              |                       |

| -n = Value a                      | t POR                       | '1' = Bit is set |                           | '0' = Bit is clea | ared                  | x = Bit is unkr       | iown                  |

|                                   |                             |                  |                           |                   |                       |                       |                       |

| bit 15-11                         | Unimplement                 | ted: Read as '   | כ'                        |                   |                       |                       |                       |

| bit 10                            | PWM3MD: P\                  | NM3 Module D     | isable bit <sup>(1)</sup> |                   |                       |                       |                       |

|                                   | 1 = PWM3 mo                 | odule is disable | ed                        |                   |                       |                       |                       |

|                                   | 0 = PWM3 mo                 | odule is enable  | d                         |                   |                       |                       |                       |

| bit 9                             | PWM2MD: P\                  | NM2 Module D     | isable bit <sup>(1)</sup> |                   |                       |                       |                       |

|                                   | 1 = PWM2 module is disabled |                  |                           |                   |                       |                       |                       |

|                                   | 0 = PWM2 mo                 | odule is enable  | d                         |                   |                       |                       |                       |

| bit 8                             | PWM1MD: P\                  | NM1 Module D     | isable bit <sup>(1)</sup> |                   |                       |                       |                       |

|                                   |                             | odule is disable |                           |                   |                       |                       |                       |

|                                   | 0 = PWM1 mo                 | odule is enable  | d                         |                   |                       |                       |                       |

| bit 7-0                           | Unimplement                 | ted: Read as '   | כ'                        |                   |                       |                       |                       |

## REGISTER 10-5: PMD6: PERIPHERAL MODULE DISABLE CONTROL REGISTER 6

Note 1: This bit is available on dsPIC33EPXXXMC50X/20X and PIC24EPXXXMC20X devices only.

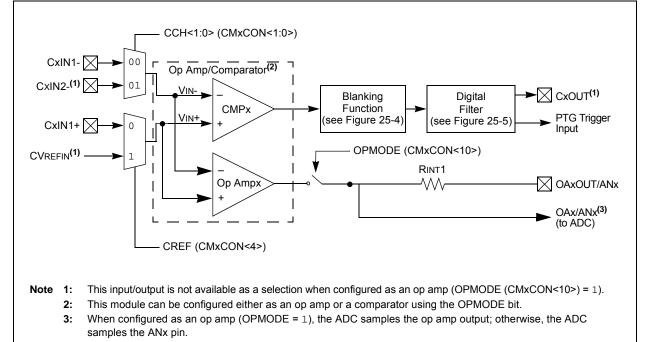

# 25.0 OP AMP/COMPARATOR MODULE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Op Amp/Comparator" (DS70357) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices contain up to four comparators, which can be configured in various ways. Comparators, CMP1, CMP2 and CMP3, also have the option to be configured as op amps, with the output being brought to an external pin for gain/filtering connections. As shown in Figure 25-1, individual comparator options are specified by the comparator module's Special Function Register (SFR) control bits.

Note: Op Amp/Comparator 3 is not available on the dsPIC33EPXXXGP502/MC502/MC202 and PIC24EP256GP/MC202 (28-pin) devices.

These options allow users to:

- · Select the edge for trigger and interrupt generation

- · Configure the comparator voltage reference

- · Configure output blanking and masking

- Configure as a comparator or op amp (CMP1, CMP2 and CMP3 only)

Note: Not all op amp/comparator input/output connections are available on all devices. See the "Pin Diagrams" section for available connections.

### FIGURE 25-1: OP AMP/COMPARATOR x MODULE BLOCK DIAGRAM (MODULES 1, 2 AND 3)

#### 27.6 JTAG Interface

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices implement a JTAG interface, which supports boundary scan device testing. Detailed information on this interface is provided in future revisions of the document.

| Note: | Refer to "Programming and Diagnostics"       |

|-------|----------------------------------------------|

|       | (DS70608) in the "dsPIC33/PIC24 Family       |

|       | Reference Manual" for further information    |

|       | on usage, configuration and operation of the |

|       | JTAG interface.                              |

## 27.7 In-Circuit Serial Programming

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices can be serially programmed while in the end application circuit. This is done with two lines for clock and data, and three other lines for power, ground and the programming sequence. Serial programming allows customers to manufacture boards with unprogrammed devices and then program the device just before shipping the product. Serial programming also allows the most recent firmware or a custom firmware to be programmed. Refer to the "dsPIC33E/PIC24E Flash Programming Specification for Devices with Volatile Configuration Bits" (DS70663) for details about In-Circuit Serial Programming (ICSP).

Any of the three pairs of programming clock/data pins can be used:

- PGEC1 and PGED1

- PGEC2 and PGED2

- PGEC3 and PGED3

#### 27.8 In-Circuit Debugger

When MPLAB<sup>®</sup> ICD 3 or REAL ICE<sup>™</sup> is selected as a debugger, the in-circuit debugging functionality is enabled. This function allows simple debugging functions when used with MPLAB IDE. Debugging functionality is controlled through the PGECx (Emulation/Debug Clock) and PGEDx (Emulation/Debug Data) pin functions.

Any of the three pairs of debugging clock/data pins can be used:

- PGEC1 and PGED1

- PGEC2 and PGED2

- PGEC3 and PGED3

To use the in-circuit debugger function of the device, the design must implement ICSP connections to  $\overline{MCLR}$ , VDD, Vss and the PGECx/PGEDx pin pair. In addition, when the feature is enabled, some of the resources are not available for general use. These resources include the first 80 bytes of data RAM and two I/O pins (PGECx and PGEDx).

### 27.9 Code Protection and CodeGuard™ Security

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X, and PIC24EPXXXGP/MC20X devices offer basic implementation of CodeGuard Security that supports only General Segment (GS) security. This feature helps protect individual Intellectual Property.

Note: Refer to "CodeGuard<sup>™</sup> Security" (DS70634) in the "dsPIC33/PIC24 Family Reference Manual" for further information on usage, configuration and operation of CodeGuard Security.

### 29.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

#### 29.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

#### 29.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

## 29.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

## 29.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

# **30.0 ELECTRICAL CHARACTERISTICS**

This section provides an overview of dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X electrical characteristics. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X family are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these or any other conditions above the parameters indicated in the operation listings of this specification is not implied.

# Absolute Maximum Ratings<sup>(1)</sup>

| Ambient temperature under bias                                                    | 40°C to +125°C       |

|-----------------------------------------------------------------------------------|----------------------|

| Storage temperature                                                               | 65°C to +150°C       |

| Voltage on VDD with respect to Vss                                                | -0.3V to +4.0V       |

| Voltage on any pin that is not 5V tolerant, with respect to Vss <sup>(3)</sup>    | 0.3V to (VDD + 0.3V) |

| Voltage on any 5V tolerant pin with respect to Vss when $VDD \ge 3.0V^{(3)}$      | 0.3V to +5.5V        |

| Voltage on any 5V tolerant pin with respect to Vss when VDD < 3.0V <sup>(3)</sup> | -0.3V to +3.6V       |

| Maximum current out of Vss pin                                                    |                      |

| Maximum current into Vod pin <sup>(2)</sup>                                       |                      |

| Maximum current sunk/sourced by any 4x I/O pin                                    | 15 mA                |

| Maximum current sunk/sourced by any 8x I/O pin                                    | 25 mA                |

| Maximum current sunk by all ports <sup>(2,4)</sup>                                | 200 mA               |

- **Note 1:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

- 2: Maximum allowable current is a function of device maximum power dissipation (see Table 30-2).

- 3: See the "Pin Diagrams" section for the 5V tolerant pins.

- 4: Exceptions are: dsPIC33EPXXXGP502, dsPIC33EPXXXMC202/502 and PIC24EPXXXGP/MC202 devices, which have a maximum sink/source capability of 130 mA.

| DC CHARACT       | ERISTICS                  |      | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |            |       |           |  |  |

|------------------|---------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------|-----------|--|--|

| Parameter<br>No. | Тур.                      | Max. | Units                                                                                                                                                                                                                                                                                   | Conditions |       |           |  |  |

| Operating Cur    | rent (IDD) <sup>(1)</sup> |      |                                                                                                                                                                                                                                                                                         |            |       |           |  |  |

| DC20d            | 9                         | 15   | mA                                                                                                                                                                                                                                                                                      | -40°C      |       |           |  |  |

| DC20a            | 9                         | 15   | mA                                                                                                                                                                                                                                                                                      | +25°C      | 3 3\/ | 10 MIPS   |  |  |

| DC20b            | 9                         | 15   | mA                                                                                                                                                                                                                                                                                      | +85°C      | 3.3V  | 10 1011-5 |  |  |

| DC20c            | 9                         | 15   | mA                                                                                                                                                                                                                                                                                      | +125°C     |       |           |  |  |

| DC22d            | 16                        | 25   | mA                                                                                                                                                                                                                                                                                      | -40°C      |       |           |  |  |

| DC22a            | 16                        | 25   | mA                                                                                                                                                                                                                                                                                      | +25°C      | 3.3∨  | 20 MIPS   |  |  |

| DC22b            | 16                        | 25   | mA                                                                                                                                                                                                                                                                                      | +85°C      |       | 20 1011-5 |  |  |

| DC22c            | 16                        | 25   | mA                                                                                                                                                                                                                                                                                      | +125°C     |       |           |  |  |

| DC24d            | 27                        | 40   | mA                                                                                                                                                                                                                                                                                      | -40°C      |       |           |  |  |

| DC24a            | 27                        | 40   | mA                                                                                                                                                                                                                                                                                      | +25°C      | 3.3V  | 40 MIPS   |  |  |

| DC24b            | 27                        | 40   | mA                                                                                                                                                                                                                                                                                      | +85°C      | 3.3V  | 40 1011-5 |  |  |

| DC24c            | 27                        | 40   | mA                                                                                                                                                                                                                                                                                      | +125°C     |       |           |  |  |

| DC25d            | 36                        | 55   | mA                                                                                                                                                                                                                                                                                      | -40°C      |       |           |  |  |

| DC25a            | 36                        | 55   | mA                                                                                                                                                                                                                                                                                      | +25°C      | 3.3V  | 60 MIPS   |  |  |

| DC25b            | 36                        | 55   | mA                                                                                                                                                                                                                                                                                      | +85°C      | 3.3V  | OU IVIIPS |  |  |

| DC25c            | 36                        | 55   | mA                                                                                                                                                                                                                                                                                      | +125°C     | 7     |           |  |  |

| DC26d            | 41                        | 60   | mA                                                                                                                                                                                                                                                                                      | -40°C      |       |           |  |  |

| DC26a            | 41                        | 60   | mA                                                                                                                                                                                                                                                                                      | +25°C      | 3.3V  | 70 MIPS   |  |  |

| DC26b            | 41                        | 60   | mA                                                                                                                                                                                                                                                                                      | +85°C      |       |           |  |  |

#### TABLE 30-6: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

**Note 1:** IDD is primarily a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDD measurements are as follows:

• Oscillator is configured in EC mode with PLL, OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)

- · CLKO is configured as an I/O input pin in the Configuration Word

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- CPU, SRAM, program memory and data memory are operational

- No peripheral modules are operating; however, every peripheral is being clocked (all PMDx bits are zeroed)

- CPU is executing while(1) {NOP(); } statement

- · JTAG is disabled

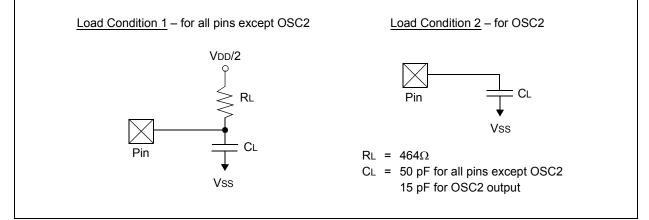

## 30.2 AC Characteristics and Timing Parameters

This section defines dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X AC characteristics and timing parameters.

#### TABLE 30-15: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

|                    | Standard Operating Conditions: 3.0V to 3.6V<br>(unless otherwise stated)                                                                                                                                |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AC CHARACTERISTICS | Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended<br>Operating voltage VDD range as described in <b>Section 30.1 "DC</b> |

|                    | Characteristics".                                                                                                                                                                                       |

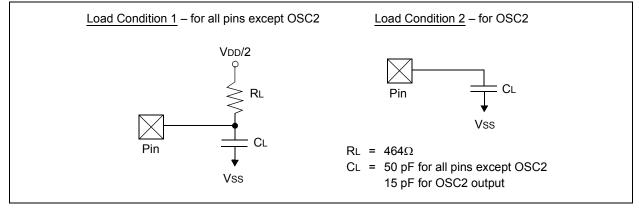

#### FIGURE 30-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

#### TABLE 30-16: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

| Param<br>No. | Symbol | Characteristic        | Min. | Тур. | Max. | Units | Conditions                                                          |

|--------------|--------|-----------------------|------|------|------|-------|---------------------------------------------------------------------|

| DO50         | Cosco  | OSC2 Pin              | _    | —    | 15   |       | In XT and HS modes, when<br>external clock is used to drive<br>OSC1 |

| DO56         | Сю     | All I/O Pins and OSC2 | —    | _    | 50   | pF    | EC mode                                                             |

| DO58         | Св     | SCLx, SDAx            | _    | _    | 400  | pF    | In I <sup>2</sup> C™ mode                                           |

| TABLE 30-23: TIME | 1 EXTERNAL CLOCK TIMING REQUI | REMENTS <sup>(1)</sup> |

|-------------------|-------------------------------|------------------------|

|-------------------|-------------------------------|------------------------|

| AC CHARACTERISTICS |           |                      | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                                        |      |               |       |                                                                             |