Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 60 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 35                                                                             |

| Program Memory Size        | 512KB (170K x 24)                                                              |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 24K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 9x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 44-QFN (8x8)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep512gp204-h-ml |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

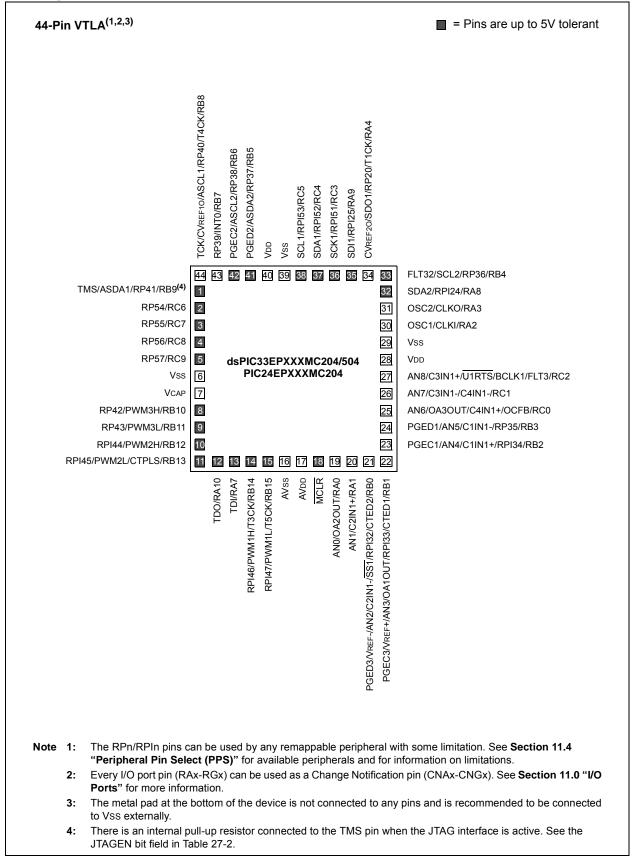

### Pin Diagrams (Continued)

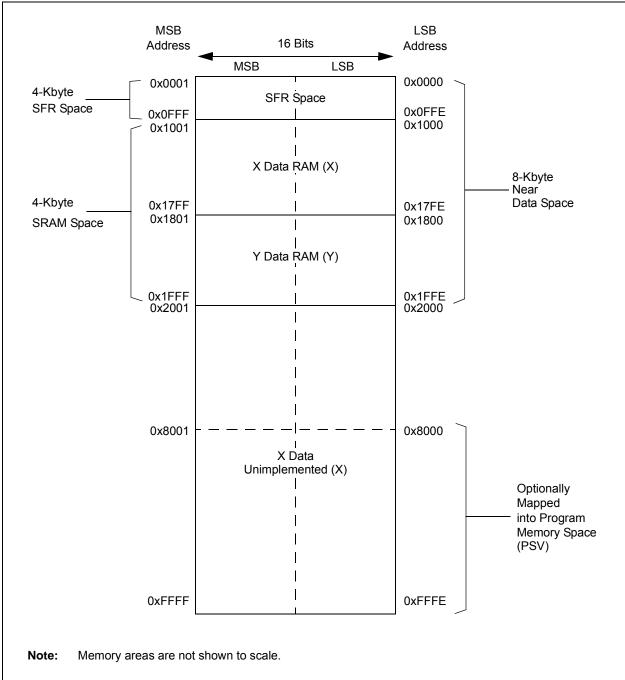

# FIGURE 4-7: DATA MEMORY MAP FOR dsPIC33EP32MC20X/50X AND dsPIC33EP32GP50X DEVICES

| File Name  | Addr          | Bit 15                        | Bit 14    | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8      | Bit 7                                                        | Bit 6    | Bit 5  | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|------------|---------------|-------------------------------|-----------|--------|--------|--------|--------|--------|------------|--------------------------------------------------------------|----------|--------|-------|--------|--------|--------|--------|---------------|

|            | 0400-<br>041E |                               |           |        |        |        |        |        | See defini | ion when W                                                   | 'IN = x  |        |       |        |        |        |        |               |

| C1BUFPNT1  | 0420          |                               | F3BF      | P<3:0> |        |        | F2BI   | ><3:0> |            |                                                              | F1BP     | <3:0>  |       |        | F0BP   | <3:0>  |        | 0000          |

| C1BUFPNT2  | 0422          | F7BP<3:0> F6BP<3:0> F5BP<3:0> |           |        |        |        |        |        |            | F4BP                                                         | <3:0>    |        | 0000  |        |        |        |        |               |

| C1BUFPNT3  | 0424          |                               | F11B      | P<3:0> |        |        | F10B   | P<3:0> |            |                                                              | F9BP     | <3:0>  |       |        | F8BP   | <3:0>  |        | 0000          |

| C1BUFPNT4  | 0426          |                               | F15B      | P<3:0> |        |        | F14B   | P<3:0> |            |                                                              | F13B     | D<3:0> |       |        | F12BF  | P<3:0> |        | 0000          |

| C1RXM0SID  | 0430          |                               |           |        | SID<   | :10:3> |        |        |            |                                                              | MIDE     | _      | EID<  | 17:16> | xxxx   |        |        |               |

| C1RXM0EID  | 0432          |                               |           |        | EID<   | :15:8> |        |        |            | EID<                                                         |          |        |       | 7:0>   |        |        |        | xxxx          |

| C1RXM1SID  | 0434          |                               |           |        | SID<   | :10:3> |        |        |            | SID<2:0>         —         MIDE         —         EID<17:16> |          |        |       |        | 17:16> | xxxx   |        |               |

| C1RXM1EID  | 0436          |                               |           |        | EID<   | :15:8> |        |        |            | EID<7:0>                                                     |          |        |       |        |        | xxxx   |        |               |

| C1RXM2SID  | 0438          |                               |           |        | SID<   | :10:3> |        |        |            |                                                              | SID<2:0> |        | —     | MIDE   | —      | EID<   | 17:16> | xxxx          |

| C1RXM2EID  | 043A          |                               |           |        | EID<   | :15:8> |        |        |            |                                                              |          |        | EID<  | 7:0>   |        |        |        | xxxx          |

| C1RXF0SID  | 0440          |                               |           |        | SID<   | :10:3> |        |        |            |                                                              | SID<2:0> |        | —     | EXIDE  | —      | EID<   | 17:16> | xxxx          |

| C1RXF0EID  | 0442          |                               |           |        | EID<   | :15:8> |        |        |            |                                                              |          |        | EID<  | 7:0>   |        | -      |        | xxxx          |

| C1RXF1SID  | 0444          |                               |           |        | SID<   | :10:3> |        |        |            |                                                              | SID<2:0> |        | _     | EXIDE  | —      | EID<   | 17:16> | xxxx          |

| C1RXF1EID  | 0446          |                               | EID<15:8> |        |        |        |        |        |            |                                                              |          | EID<   | 7:0>  |        |        |        | xxxx   |               |

| C1RXF2SID  | 0448          |                               | SID<10:3> |        |        |        |        |        |            | SID<2:0>                                                     |          | —      | EXIDE | —      | EID<   | 17:16> | xxxx   |               |

| C1RXF2EID  | 044A          |                               |           |        | EID<   | :15:8> |        |        |            |                                                              |          |        | EID<  | 7:0>   |        |        |        | xxxx          |

| C1RXF3SID  | 044C          |                               |           |        | SID<   | :10:3> |        |        |            |                                                              | SID<2:0> |        | —     | EXIDE  | —      | EID<   | 17:16> | xxxx          |

| C1RXF3EID  | 044E          |                               |           |        | EID<   | :15:8> |        |        |            | EID<7:0>                                                     |          |        |       |        |        | xxxx   |        |               |

| C1RXF4SID  | 0450          |                               |           |        | SID<   | :10:3> |        |        |            |                                                              | SID<2:0> |        | —     | EXIDE  | —      | EID<   | 17:16> | xxxx          |

| C1RXF4EID  | 0452          |                               |           |        | EID<   | :15:8> |        |        |            | EID<7:0>                                                     |          |        |       |        |        | xxxx   |        |               |

| C1RXF5SID  | 0454          |                               |           |        | SID<   | :10:3> |        |        |            | SID<2:0> — EXIDE — EID<17:16>                                |          |        |       |        |        | 17:16> | xxxx   |               |

| C1RXF5EID  | 0456          |                               |           |        | EID<   | :15:8> |        |        |            | EID<7:0>                                                     |          |        |       |        |        |        | xxxx   |               |

| C1RXF6SID  | 0458          |                               |           |        | SID<   | :10:3> |        |        |            | SID<2:0> — EXIDE — EID<17:16>                                |          |        |       |        |        | 17:16> | xxxx   |               |

| C1RXF6EID  | 045A          |                               |           |        | EID<   | :15:8> |        |        |            |                                                              |          |        | EID<  | 7:0>   |        |        |        | xxxx          |

| C1RXF7SID  | 045C          |                               |           |        | SID<   | :10:3> |        |        |            |                                                              | SID<2:0> |        | —     | EXIDE  | —      | EID<   | 17:16> | xxxx          |

| C1RXF7EID  | 045E          |                               |           |        | EID<   | :15:8> |        |        |            |                                                              |          |        | EID<  | 7:0>   |        |        |        | xxxx          |

| C1RXF8SID  | 0460          |                               |           |        | SID<   | :10:3> |        |        |            |                                                              | SID<2:0> |        | —     | EXIDE  | —      | EID<   | 17:16> | xxxx          |

| C1RXF8EID  | 0462          |                               |           |        |        | :15:8> |        |        |            | EID<7:0>                                                     |          |        |       |        |        |        |        | xxxx          |

| C1RXF9SID  | 0464          |                               |           |        |        | :10:3> |        |        |            |                                                              | SID<2:0> |        | —     | EXIDE  | —      | EID<   | 17:16> | xxxx          |

| C1RXF9EID  | 0466          |                               |           |        |        | :15:8> |        |        |            |                                                              |          |        | EID<  |        |        |        |        | xxxx          |

| C1RXF10SID | 0468          |                               |           |        |        | :10:3> |        |        |            |                                                              | SID<2:0> |        | —     | EXIDE  | —      | EID<   | 17:16> | xxxx          |

| C1RXF10EID | 046A          |                               |           |        |        | :15:8> |        |        |            |                                                              |          |        | EID<  | -      |        |        |        | xxxx          |

| C1RXF11SID | 046C          |                               |           |        | SID<   | :10:3> |        |        |            |                                                              | SID<2:0> |        | —     | EXIDE  | -      | EID<   | 17:16> | xxxx          |

### TABLE 4-23: ECAN1 REGISTER MAP WHEN WIN (C1CTRL1<0>) = 1 FOR dsPIC33EPXXXMC/GP50X DEVICES ONLY

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-27: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EPXXXGP/MC204/504 AND PIC24EPXXXGP/MC204 DEVICES ONLY DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12     | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6      | Bit 5      | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|------------|--------|--------|-------|-------|-------|------------|------------|-------|-------|--------|-------|-------|---------------|

| RPOR0        | 0680  |        |        |        |            | RP35   | R<5:0> |       |       | _     | —          |            |       | RP20F | ₹<5:0> |       |       | 0000          |

| RPOR1        | 0682  | _      | _      |        | RP37R<5:0> |        |        |       |       |       | —          | RP36R<5:0> |       |       |        |       |       | 0000          |

| RPOR2        | 0684  | _      | _      |        | RP39R<5:0> |        |        |       |       | —     | RP38R<5:0> |            |       |       |        | 0000  |       |               |

| RPOR3        | 0686  | _      | _      |        | RP41R<5:0> |        |        |       |       | —     | RP40R<5:0> |            |       |       |        | 0000  |       |               |

| RPOR4        | 0688  | _      | _      |        | RP43R<5:0> |        |        |       |       | —     | RP42R<5:0> |            |       |       |        | 0000  |       |               |

| RPOR5        | 068A  | _      | —      |        | RP55R<5:0> |        |        |       |       | _     | —          | RP54R<5:0> |       |       |        | 0000  |       |               |

| RPOR6        | 068C  | _      | —      |        | RP57R<5:0> |        |        |       |       | _     | —          |            |       | RP56F | R<5:0> |       |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-28: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EPXXXGP/MC206/506 AND PIC24EPXXXGP/MC206 DEVICES ONLY DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12     | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5      | Bit 4 | Bit 3  | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|------------|------------|--------|--------|-------|-------|-------|-------|------------|-------|--------|--------|-------|-------|---------------|

| RPOR0        | 0680  | _      | _      |            |            | RP35F  | R<5:0> |       |       | _     | _     |            | •     | RP20F  | R<5:0> |       |       | 0000          |

| RPOR1        | 0682  | _      |        | RP37R<5:0> |            |        |        |       |       | _     | _     | RP36R<5:0> |       |        |        |       | 0000  |               |

| RPOR2        | 0684  | _      | —      |            |            | RP39F  | २<5:0> |       |       | _     | _     |            |       | RP38   | R<5:0> |       |       | 0000          |

| RPOR3        | 0686  | _      | —      |            | RP41R<5:0> |        |        |       | _     | _     |       |            | RP40  | R<5:0> |        |       | 0000  |               |

| RPOR4        | 0688  | _      | _      |            |            | RP43F  | २<5:0> |       |       | —     | _     |            |       | RP42   | R<5:0> |       |       | 0000          |

| RPOR5        | 068A  | _      | _      |            |            | RP55F  | २<5:0> |       |       | —     | _     |            |       | RP54   | R<5:0> |       |       | 0000          |

| RPOR6        | 068C  | _      | _      |            | RP57R<5:0> |        |        |       |       | —     | _     | RP56R<5:0> |       |        |        | 0000  |       |               |

| RPOR7        | 068E  | _      | _      |            |            | RP97F  | २<5:0> |       |       | —     | _     | _          | _     | _      | _      | _     | _     | 0000          |

| RPOR8        | 0690  |        | _      |            |            | RP118  | R<5:0> |       |       | _     | _     | —          | _     | —      | _      | —     | _     | 0000          |

| RPOR9        | 0692  | —      | _      | _          | _          | _      | _      | _     | _     | _     | _     |            |       | RP120  | R<5:0> |       |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## 5.0 FLASH PROGRAM MEMORY

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXGP/MC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Flash Programming" (DS70609) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices contain internal Flash program memory for storing and executing application code. The memory is readable, writable and erasable during normal operation over the entire VDD range.

Flash memory can be programmed in two ways:

- In-Circuit Serial Programming™ (ICSP™) programming capability

- Run-Time Self-Programming (RTSP)

ICSP allows for a dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X device to be serially programmed while in the end application circuit. This is done with two lines for programming clock and programming data (one of the alternate programming pin pairs: PGECx/PGEDx), and three other lines for power (VDD), ground (VSS) and Master Clear (MCLR). This allows customers to manufacture boards with unprogrammed devices and then program the device just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

RTSP is accomplished using TBLRD (Table Read) and TBLWT (Table Write) instructions. With RTSP, the user application can write program memory data a single program memory word, and erase program memory in blocks or 'pages' of 1024 instructions (3072 bytes) at a time.

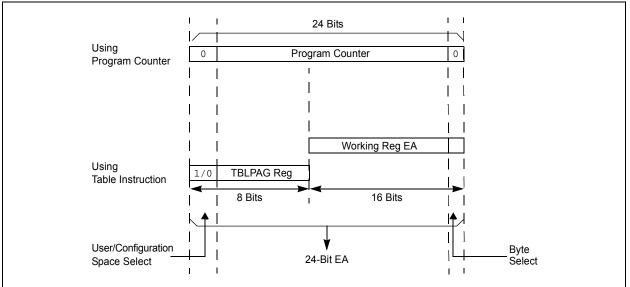

## 5.1 Table Instructions and Flash Programming

Regardless of the method used, all programming of Flash memory is done with the Table Read and Table Write instructions. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using bits<7:0> of the TBLPAG register and the Effective Address (EA) from a W register, specified in the table instruction, as shown in Figure 5-1.

The TBLRDL and the TBLWTL instructions are used to read or write to bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes.

The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

#### FIGURE 5-1: ADDRESSING FOR TABLE REGISTERS

| REGISTER     | <u>R 10-2: PMD</u> 2 | 2: PERIPHER                                         | AL MODULE       | DISABLE C         | ONTROL RE       | GISTER 2        |       |

|--------------|----------------------|-----------------------------------------------------|-----------------|-------------------|-----------------|-----------------|-------|

| U-0          | U-0                  | U-0                                                 | U-0             | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

| _            |                      | —                                                   |                 | IC4MD             | IC3MD           | IC2MD           | IC1MD |

| bit 15       |                      |                                                     |                 |                   |                 |                 | bit   |

| U-0          | U-0                  | U-0                                                 | U-0             | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|              |                      |                                                     |                 | OC4MD             | OC3MD           | OC2MD           | OC1MD |

| bit 7        |                      |                                                     |                 |                   |                 |                 | bit   |

|              |                      |                                                     |                 |                   |                 |                 |       |

| Legend:      | 1.1.1                |                                                     |                 |                   |                 |                 |       |

| R = Readab   |                      | W = Writable b                                      | Dit             | •                 | nented bit, rea |                 |       |

| -n = Value a | at POR               | '1' = Bit is set                                    |                 | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

| bit 15-12    | Unimplemen           | ted: Read as '0                                     | ,               |                   |                 |                 |       |

| bit 11       | -                    | t Capture 4 Mod                                     |                 |                   |                 |                 |       |

|              | •                    | ture 4 module is                                    |                 |                   |                 |                 |       |

|              | 0 = Input Cap        | oture 4 module is                                   | s enabled       |                   |                 |                 |       |

| bit 10       | IC3MD: Input         | t Capture 3 Mod                                     | ule Disable bit |                   |                 |                 |       |

|              |                      | oture 3 module is                                   |                 |                   |                 |                 |       |

|              |                      | oture 3 module is                                   |                 |                   |                 |                 |       |

| bit 9        |                      | t Capture 2 Mod                                     |                 |                   |                 |                 |       |

|              |                      | oture 2 module is<br>oture 2 module is              |                 |                   |                 |                 |       |

| bit 8        | IC1MD: Input         | t Capture 1 Mod                                     | ule Disable bit |                   |                 |                 |       |

|              | 1 = Input Cap        | oture 1 module is<br>oture 1 module is              | s disabled      |                   |                 |                 |       |

| bit 7-4      |                      | ted: Read as '0                                     |                 |                   |                 |                 |       |

| bit 3        | OC4MD: Out           | put Compare 4                                       | Module Disable  | e bit             |                 |                 |       |

|              |                      | ompare 4 modul                                      |                 |                   |                 |                 |       |

|              | -                    | ompare 4 modu                                       |                 |                   |                 |                 |       |

| bit 2        |                      | put Compare 3                                       |                 | e bit             |                 |                 |       |

|              | •                    | ompare 3 modul                                      |                 |                   |                 |                 |       |

| L:1 4        | -                    | ompare 3 modul                                      |                 | . h.:4            |                 |                 |       |

| bit 1        |                      | put Compare 2                                       |                 |                   |                 |                 |       |

|              | $\perp$ – Output Co  | ompare 2 modu                                       |                 |                   |                 |                 |       |

|              | 0 = Output Co        | ompare 2 modul                                      | le is enabled   |                   |                 |                 |       |

| bit 0        |                      | ompare 2 modul<br>put Compare 1                     |                 | e bit             |                 |                 |       |

| bit 0        | OC1MD: Out           | ompare 2 modul<br>put Compare 1 l<br>ompare 1 modul | Module Disable  | e bit             |                 |                 |       |

#### ~

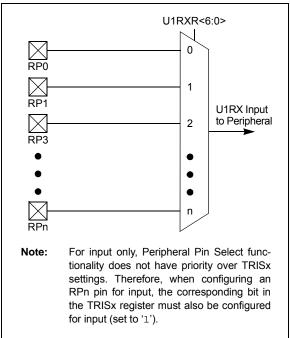

#### 11.4.4 INPUT MAPPING

The inputs of the Peripheral Pin Select options are mapped on the basis of the peripheral. That is, a control register associated with a peripheral dictates the pin it will be mapped to. The RPINRx registers are used to configure peripheral input mapping (see Register 11-1 through Register 11-17). Each register contains sets of 7-bit fields, with each set associated with one of the remappable peripherals. Programming a given peripheral's bit field with an appropriate 7-bit value maps the RPn pin with the corresponding value to that peripheral. For any given device, the valid range of values for any bit field corresponds to the maximum number of Peripheral Pin Selections supported by the device.

For example, Figure 11-2 illustrates remappable pin selection for the U1RX input.

#### FIGURE 11-2: REMAPPABLE INPUT FOR U1RX

#### 11.4.4.1 Virtual Connections

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices support virtual (internal) connections to the output of the op amp/ comparator module (see Figure 25-1 in Section 25.0 "Op Amp/Comparator Module"), and the PTG module (see Section 24.0 "Peripheral Trigger Generator (PTG) Module").

In addition, dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices support virtual connections to the filtered QEI module inputs: FINDX1, FHOME1, FINDX2 and FHOME2 (see Figure 17-1 in Section 17.0 "Quadrature Encoder Interface (QEI) Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)".

Virtual connections provide a simple way of interperipheral connection without utilizing a physical pin. For example, by setting the FLT1R<6:0> bits of the RPINR12 register to the value of `b0000001, the output of the analog comparator, C1OUT, will be connected to the PWM Fault 1 input, which allows the analog comparator to trigger PWM Faults without the use of an actual physical pin on the device.

Virtual connection to the QEI module allows peripherals to be connected to the QEI digital filter input. To utilize this filter, the QEI module must be enabled and its inputs must be connected to a physical RPn pin. Example 11-2 illustrates how the input capture module can be connected to the QEI digital filter.

# EXAMPLE 11-2: CONNECTING IC1 TO THE HOME1 QEI1 DIGITAL FILTER INPUT ON PIN 43 OF THE dsPIC33EPXXXMC206 DEVICE

| RPINR15 = 0x2500; | /* Connect the QEI1 HOME1 input to RP37 (pin 43) */                   |

|-------------------|-----------------------------------------------------------------------|

| RPINR7 = 0x009;   | /* Connect the IC1 input to the digital filter on the FHOME1 input */ |

| QEI1IOC = 0x4000; | /* Enable the QEI digital filter */                                   |

| QEI1CON = 0x8000; | /* Enable the QEI module */                                           |

### REGISTER 11-9: RPINR15: PERIPHERAL PIN SELECT INPUT REGISTER 15 (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

| U-0          | R/W-0        | R/W-0                                                  | R/W-0         | R/W-0            | R/W-0           | R/W-0           | R/W-0  |

|--------------|--------------|--------------------------------------------------------|---------------|------------------|-----------------|-----------------|--------|

| _            |              |                                                        |               | HOME1R<6:0       | >               |                 |        |

| bit 15       |              |                                                        |               |                  |                 |                 | bit 8  |

|              |              | <b>D</b> # 4 4 0                                       | 54446         | 5444.0           | 5444.0          |                 | 5444.6 |

| U-0          | R/W-0        | R/W-0                                                  | R/W-0         | R/W-0            | R/W-0           | R/W-0           | R/W-0  |

|              |              |                                                        |               | INDX1R<6:0>      | >               |                 |        |

| bit 7        |              |                                                        |               |                  |                 |                 | bit C  |

| Legend:      |              |                                                        |               |                  |                 |                 |        |

| R = Readab   | le bit       | W = Writable                                           | bit           | U = Unimplen     | nented bit, rea | ad as '0'       |        |

| -n = Value a | t POR        | '1' = Bit is set                                       |               | '0' = Bit is cle | ared            | x = Bit is unkr | nown   |

|              |              | nput tied to RPI                                       |               |                  |                 |                 |        |

|              |              | nput tied to CM<br>nput tied to Vss                    |               |                  |                 |                 |        |

| bit 7        |              | nted: Read as '                                        |               |                  |                 |                 |        |

| bit 6-0      | (see Table 1 | : Assign QEI1<br>1-2 for input pin<br>nput tied to RPI | selection nun | ,                | responding RI   | Pn Pin bits     |        |

|              |              | nput tied to CM                                        |               |                  |                 |                 |        |

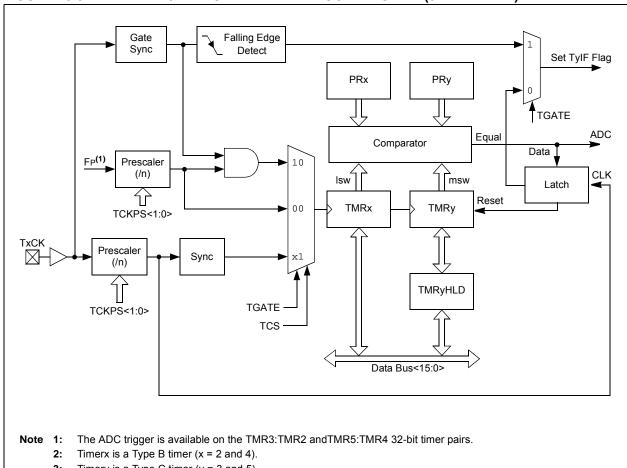

#### **FIGURE 13-3:** TYPE B/TYPE C TIMER PAIR BLOCK DIAGRAM (32-BIT TIMER)

3: Timery is a Type C timer (y = 3 and 5).

#### **Timerx/y Resources** 13.1

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/                                                                                      |

|       | wwwproducts/Devices.aspx?d<br>DocName=en555464                                                                 |

#### **KEY RESOURCES** 13.1.1

- "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- Application Notes

- · Software Libraries

- · Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

#### REGISTER 17-17: INT1TMRH: INTERVAL 1 TIMER HIGH WORD REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|-----------------|-----------------|-------|

|                 |       |                  | INTTM | R<31:24>          |                 |                 |       |

| bit 15          |       |                  |       |                   |                 |                 | bit 8 |

|                 |       |                  |       |                   |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | INTTM | R<23:16>          |                 |                 |       |

| bit 7           |       |                  |       |                   |                 |                 | bit 0 |

|                 |       |                  |       |                   |                 |                 |       |

| Legend:         |       |                  |       |                   |                 |                 |       |

| R = Readable    | bit   | W = Writable b   | oit   | U = Unimplem      | nented bit, rea | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

bit 15-0 INTTMR<31:16>: High Word Used to Form 32-Bit Interval Timer Register (INT1TMR) bits

#### REGISTER 17-18: INT1TMRL: INTERVAL 1 TIMER LOW WORD REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

|                 |       |                  | INTTM | IR<15:8>         |                 |                 |       |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

|                 |       |                  |       |                  |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | INTT  | /IR<7:0>         |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

|                 |       |                  |       |                  |                 |                 |       |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable I  | bit   | W = Writable b   | bit   | U = Unimpler     | nented bit, rea | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

bit 15-0 INTTMR<15:0>: Low Word Used to Form 32-Bit Interval Timer Register (INT1TMR) bits

| R/W-x         | R/W-x                     | R/W-x                | R/W-x         | R/W-x            | R/W-x            | R/W-x                           | R/W-x |  |  |  |  |  |

|---------------|---------------------------|----------------------|---------------|------------------|------------------|---------------------------------|-------|--|--|--|--|--|

| EID5          | EID4                      | EID3                 | EID2          | EID1             | EID0             | RTR                             | RB1   |  |  |  |  |  |

| bit 15        |                           |                      |               |                  |                  |                                 | bit 8 |  |  |  |  |  |

|               |                           |                      |               |                  |                  |                                 |       |  |  |  |  |  |

| U-x           | U-x                       | U-x                  | R/W-x         | R/W-x            | R/W-x            | R/W-x                           | R/W-x |  |  |  |  |  |

| —             | —                         | _                    | RB0           | DLC3             | DLC2             | DLC1                            | DLC0  |  |  |  |  |  |

| bit 7         |                           |                      |               |                  |                  |                                 | bit 0 |  |  |  |  |  |

| Lonondi       |                           |                      |               |                  |                  |                                 |       |  |  |  |  |  |

| Legend:       | l. h.:.                   |                      | L.11          |                  |                  | -l (O)                          |       |  |  |  |  |  |

| R = Readab    |                           | W = Writable         |               | •                | mented bit, read | ad as '0'<br>x = Bit is unknown |       |  |  |  |  |  |

| -n = Value a  | t POR                     | '1' = Bit is set     |               | '0' = Bit is cle | ared             | x = Bit is unkr                 | iown  |  |  |  |  |  |

|               |                           |                      |               |                  |                  |                                 |       |  |  |  |  |  |

| bit 15-10     | EID<5:0>: E               | xtended Identifi     | er bits       |                  |                  |                                 |       |  |  |  |  |  |

| bit 9         | RTR: Remot                | e Transmission       | Request bit   |                  |                  |                                 |       |  |  |  |  |  |

|               | When IDE =                | 1:                   |               |                  |                  |                                 |       |  |  |  |  |  |

|               | •                         | e will request re    | mote transmis | ssion            |                  |                                 |       |  |  |  |  |  |

|               | 0 = Normal n              | 0                    |               |                  |                  |                                 |       |  |  |  |  |  |

|               | When IDE =<br>The RTR bit |                      |               |                  |                  |                                 |       |  |  |  |  |  |

| <b>h</b> :+ 0 | RB1: Reserv               |                      |               |                  |                  |                                 |       |  |  |  |  |  |

| bit 8         |                           |                      | or CAN proto  |                  |                  |                                 |       |  |  |  |  |  |

|               |                           | et this bit to '0' p | -             | 0001.            |                  |                                 |       |  |  |  |  |  |

| bit 7-5       | •                         | nted: Read as '      | 0             |                  |                  |                                 |       |  |  |  |  |  |

| bit 4         | RB0: Reserv               |                      | <b></b>       |                  |                  |                                 |       |  |  |  |  |  |

|               | User must se              | et this bit to '0' p | per CAN proto | ocol.            |                  |                                 |       |  |  |  |  |  |

| hit 2 0       |                           | Jota Longth Co.      | da hita       |                  |                  |                                 |       |  |  |  |  |  |

#### BUFFER 21-3: ECAN™ MESSAGE BUFFER WORD 2

bit 3-0 DLC<3:0>: Data Length Code bits

### BUFFER 21-4: ECAN<sup>™</sup> MESSAGE BUFFER WORD 3

| R/W-x                              | R/W-x | R/W-x        | R/W-x            | R/W-x        | R/W-x           | R/W-x            | R/W-x |  |

|------------------------------------|-------|--------------|------------------|--------------|-----------------|------------------|-------|--|

|                                    |       |              | Ву               | /te 1        |                 |                  |       |  |

| bit 15                             |       |              |                  |              |                 |                  | bit 8 |  |

| R/W-x                              | R/W-x | R/W-x        | R/W-x            | R/W-x        | R/W-x           | R/W-x            | R/W-x |  |

|                                    |       |              | Ву               | rte 0        |                 |                  |       |  |

| bit 7                              |       |              |                  |              |                 |                  | bit 0 |  |

| Legend:                            |       |              |                  |              |                 |                  |       |  |

| R = Readable                       | bit   | W = Writable | bit              | U = Unimplen | nented bit, rea | d as '0'         |       |  |

| -n = Value at POR '1' = Bit is set |       |              | '0' = Bit is cle | ared         | x = Bit is unkr | = Bit is unknown |       |  |

bit 15-8 Byte 1<15:8>: ECAN Message Byte 1 bits

bit 7-0 Byte 0<7:0>: ECAN Message Byte 0 bits

|               | 23-2: Al                                                                                                                               |                                        | CONTROL REG                              |                 |                  |                 |              |  |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|------------------------------------------|-----------------|------------------|-----------------|--------------|--|--|

| R/W-0         | R/W-                                                                                                                                   | 0 R/W-0                                | U-0                                      | U-0             | R/W-0            | R/W-0           | R/W-0        |  |  |

| VCFG2         | VCFO                                                                                                                                   | G1 VCFG0                               | —                                        | _               | CSCNA            | CHPS1           | CHPS0        |  |  |

| bit 15        |                                                                                                                                        |                                        |                                          |                 |                  |                 | bit          |  |  |

| R-0           | R/W-                                                                                                                                   | 0 R/W-0                                | R/W-0                                    | R/W-0           | R/W-0            | R/W-0           | R/W-0        |  |  |

| BUFS          | SMPI                                                                                                                                   |                                        | SMPI2                                    | SMPI1           | SMPI0            | BUFM            | ALTS         |  |  |

| bit 7         | Sivil                                                                                                                                  |                                        |                                          |                 |                  | BOTW            | bit          |  |  |

| Logondi       |                                                                                                                                        |                                        |                                          |                 |                  |                 |              |  |  |

| Legend:       | hit                                                                                                                                    | M/ - Mritabla                          | hit U                                    | - Unimplo       | monted hit read  |                 |              |  |  |

| R = Readable  |                                                                                                                                        | W = Writable                           |                                          | •               | mented bit, read |                 |              |  |  |

| -n = Value at | POR                                                                                                                                    | '1' = Bit is set                       | t 'U                                     | )' = Bit is cle | eared            | x = Bit is unkr | nown         |  |  |

| bit 15-13     | VCFG<2                                                                                                                                 | 2:0>: Converter Volt                   | age Reference Co                         | onfiguration    | bits             |                 |              |  |  |

|               | Value                                                                                                                                  | VREFH                                  | VREFL                                    |                 |                  |                 |              |  |  |

|               | 000                                                                                                                                    | Avdd                                   | Avss                                     |                 |                  |                 |              |  |  |

|               | 001                                                                                                                                    | External VREF+                         | Avss                                     |                 |                  |                 |              |  |  |

|               | 010                                                                                                                                    | Avdd                                   | External VREF-                           |                 |                  |                 |              |  |  |

|               | 011                                                                                                                                    | External VREF+                         | External VREF-                           |                 |                  |                 |              |  |  |

|               | 1xx                                                                                                                                    | Avdd                                   | Avss                                     |                 |                  |                 |              |  |  |

| bit 12-11     | Unimple                                                                                                                                | emented: Read as '                     | ʻ0'                                      |                 |                  |                 |              |  |  |

| bit 10        | CSCNA: Input Scan Select bit                                                                                                           |                                        |                                          |                 |                  |                 |              |  |  |

|               | 1 = Scans inputs for CH0+ during Sample MUXA                                                                                           |                                        |                                          |                 |                  |                 |              |  |  |

|               |                                                                                                                                        | s not scan inputs                      | gp                                       |                 |                  |                 |              |  |  |

| bit 9-8       | CHPS<1:0>: Channel Select bits                                                                                                         |                                        |                                          |                 |                  |                 |              |  |  |

|               | In 12-bit mode (AD21B = 1), the CHPS<1:0> bits are Unimplemented and are Read as '0':                                                  |                                        |                                          |                 |                  |                 |              |  |  |

|               | 1x = Converts CH0, CH1, CH2 and CH3                                                                                                    |                                        |                                          |                 |                  |                 |              |  |  |

|               |                                                                                                                                        | nverts CH0 and CH                      | 1                                        |                 |                  |                 |              |  |  |

| L:1 7         |                                                                                                                                        | nverts CH0                             | (                                        |                 |                  |                 |              |  |  |

| bit 7         | <b>BUFS:</b> Buffer Fill Status bit (only valid when BUFM = 1)                                                                         |                                        |                                          |                 |                  |                 |              |  |  |

|               | 1 = ADC is currently filling the second half of the buffer; the user application should access data in the<br>first half of the buffer |                                        |                                          |                 |                  |                 |              |  |  |

|               | 0 = ADC is currently filling the first half of the buffer; the user application should access data in th                               |                                        |                                          |                 |                  |                 |              |  |  |

|               |                                                                                                                                        | ond half of the buffe                  |                                          | ,               |                  |                 |              |  |  |

| bit 6-2       | SMPI<4                                                                                                                                 | :0>: Increment Rate                    | e bits                                   |                 |                  |                 |              |  |  |

|               | When ADDMAEN = 0:                                                                                                                      |                                        |                                          |                 |                  |                 |              |  |  |

|               | x1111 = Generates interrupt after completion of every 16th sample/conversion operation                                                 |                                        |                                          |                 |                  |                 |              |  |  |

|               | x1110 = Generates interrupt after completion of every 15th sample/conversion operation                                                 |                                        |                                          |                 |                  |                 |              |  |  |

|               | •                                                                                                                                      |                                        |                                          |                 |                  |                 |              |  |  |

|               | •                                                                                                                                      |                                        |                                          |                 |                  |                 |              |  |  |

|               | x0001 =                                                                                                                                | <ul> <li>Generates interrup</li> </ul> |                                          |                 |                  |                 | n            |  |  |

|               |                                                                                                                                        |                                        | ot after completion                      | of every sa     | ample/conversio  | n operation     |              |  |  |

|               | x0000 =                                                                                                                                | -                                      | •                                        |                 |                  | -               |              |  |  |

|               | x0000 <b>=</b><br><u>When Al</u>                                                                                                       | DDMAEN = 1:                            |                                          | a manda eta a   | f                |                 |              |  |  |

|               | x0000 =<br><u>When Al</u><br>11111 =                                                                                                   | DDMAEN = 1:<br>Increments the DM       | IA address after c                       |                 |                  |                 |              |  |  |

|               | x0000 =<br><u>When Al</u><br>11111 =                                                                                                   | DDMAEN = 1:                            | IA address after c                       |                 |                  |                 |              |  |  |

|               | x0000 =<br><u>When Al</u><br>11111 =                                                                                                   | DDMAEN = 1:<br>Increments the DM       | IA address after c                       |                 |                  |                 |              |  |  |

|               | x0000 =<br><u>When Al</u><br>11111 =<br>11110 =<br>•<br>•                                                                              | DDMAEN = 1:<br>Increments the DM       | /A address after c<br>/A address after c | ompletion c     | of every 31st sa | mple/conversic  | on operation |  |  |

#### . . ACOND. ADCA CONTROL DECISTED 2

#### REGISTER 23-5: AD1CHS123: ADC1 INPUT CHANNEL 1, 2, 3 SELECT REGISTER

| 11.0   | 11.0 | 11.0 | 11.0 | 11.0 |          |          |         |

|--------|------|------|------|------|----------|----------|---------|

| U-0    | U-0  | U-0  | U-0  | U-0  | R/W-0    | R/W-0    | R/W-0   |

| —      | _    |      |      | —    | CH123NB1 | CH123NB0 | CH123SB |

| bit 15 |      |      |      |      |          |          | bit 8   |

|        |      |      |      |      |          |          |         |

| U-0    | U-0  | U-0  | U-0  | U-0  | R/W-0    | R/W-0    | R/W-0   |

| 0-0   | 0-0 | U-0 | 0-0 | U-0 | R/W-0    | R/W-0    | R/W-0   |

|-------|-----|-----|-----|-----|----------|----------|---------|

| —     | —   | —   | —   |     | CH123NA1 | CH123NA0 | CH123SA |

| bit 7 |     |     |     |     |          |          | bit 0   |

## Legend:

| Legenu.           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-11 Unimplemented: Read as '0'

bit 10-9

CH123NB<1:0>: Channel 1, 2, 3 Negative Input Select for Sample MUXB bits

In 12-bit mode (AD21B = 1), CH123NB is Unimplemented and is Read as '0':

| Value           |         | ADC Channel |       |

|-----------------|---------|-------------|-------|

| value           | CH1     | CH2         | CH3   |

| 11              | AN9     | AN10        | AN11  |

| 10 <b>(1,2)</b> | OA3/AN6 | AN7         | AN8   |

| 0x              | Vrefl   | Vrefl       | VREFL |

bit 8 **CH123SB:** Channel 1, 2, 3 Positive Input Select for Sample MUXB bit In 12-bit mode (AD21B = 1), CH123SB is Unimplemented and is Read as '0':

| Value          | ADC Channel |         |         |  |  |

|----------------|-------------|---------|---------|--|--|

| value          | CH1         | CH2     | CH3     |  |  |

| 1 <b>(2)</b>   | OA1/AN3     | OA2/AN0 | OA3/AN6 |  |  |

| 0 <b>(1,2)</b> | OA2/AN0     | AN1     | AN2     |  |  |

bit 7-3 Unimplemented: Read as '0'

bit 2-1 **CH123NA<1:0>:** Channel 1, 2, 3 Negative Input Select for Sample MUXA bits In 12-bit mode (AD21B = 1), CH123NA is Unimplemented and is Read as '<u>0</u>':

| Value           |         | ADC Channel |       |

|-----------------|---------|-------------|-------|

| Value           | CH1     | CH2         | CH3   |

| 11              | AN9     | AN10        | AN11  |

| 10 <b>(1,2)</b> | OA3/AN6 | AN7         | AN8   |

| 0x              | VREFL   | VREFL       | Vrefl |

- **Note 1:** AN0 through AN7 are repurposed when comparator and op amp functionality is enabled. See Figure 23-1 to determine how enabling a particular op amp or comparator affects selection choices for Channels 1, 2 and 3.

- 2: The OAx input is used if the corresponding op amp is selected (OPMODE (CMxCON<10>) = 1); otherwise, the ANx input is used.

#### REGISTER 25-1: CMSTAT: OP AMP/COMPARATOR STATUS REGISTER (CONTINUED)

- C2OUT: Comparator 2 Output Status bit<sup>(2)</sup> bit 1 When CPOL = 0: 1 = VIN + > VIN -0 = VIN + < VIN-When CPOL = 1: 1 = VIN + < VIN-0 = VIN + > VIN -C10UT: Comparator 1 Output Status bit<sup>(2)</sup> bit 0 When CPOL = 0: 1 = VIN + > VIN -0 = VIN + < VIN-When CPOL = 1: 1 = VIN + < VIN-0 = VIN + > VIN -

- **Note 1:** Reflects the value of the of the CEVT bit in the respective Op Amp/Comparator Control register, CMxCON<9>.

- 2: Reflects the value of the COUT bit in the respective Op Amp/Comparator Control register, CMxCON<8>.

| R/W-0         | R/W-0                                                     | R/W-0                                                                                                        | U-0                 | U-0              | R/W-0            | R/W-0               | R/W-0               |  |  |

|---------------|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|---------------------|------------------|------------------|---------------------|---------------------|--|--|

| CON           | COE <sup>(2)</sup>                                        | CPOL                                                                                                         | _                   | —                | OPMODE           | CEVT                | COUT                |  |  |

| bit 15        |                                                           |                                                                                                              |                     |                  |                  |                     | bit 8               |  |  |

|               |                                                           |                                                                                                              |                     |                  |                  |                     |                     |  |  |

| R/W-0         | R/W-0                                                     | U-0                                                                                                          | R/W-0               | U-0              | U-0              | R/W-0               | R/W-0               |  |  |

| EVPOL1        | EVPOL0                                                    | —                                                                                                            | CREF <sup>(1)</sup> | —                | —                | CCH1 <sup>(1)</sup> | CCH0 <sup>(1)</sup> |  |  |

| bit 7         |                                                           |                                                                                                              |                     |                  |                  |                     | bit (               |  |  |

| Legend:       |                                                           |                                                                                                              |                     |                  |                  |                     |                     |  |  |

| R = Readabl   | le bit                                                    | W = Writable                                                                                                 | bit                 | U = Unimple      | mented bit, read | as '0'              |                     |  |  |

| -n = Value at | t POR                                                     | '1' = Bit is set                                                                                             |                     | '0' = Bit is cle | eared            | x = Bit is unkr     | nown                |  |  |

|               |                                                           |                                                                                                              |                     |                  |                  |                     |                     |  |  |

| bit 15        |                                                           | p/Comparator                                                                                                 |                     |                  |                  |                     |                     |  |  |

|               |                                                           | comparator is e                                                                                              |                     |                  |                  |                     |                     |  |  |

|               |                                                           | comparator is d                                                                                              |                     |                  |                  |                     |                     |  |  |

| bit 14        |                                                           | <b>COE:</b> Comparator Output Enable bit <sup>(2)</sup><br>1 = Comparator output is present on the CxOUT pin |                     |                  |                  |                     |                     |  |  |

|               |                                                           | tor output is pro                                                                                            |                     | xout pin         |                  |                     |                     |  |  |

| bit 13        |                                                           | parator Output I                                                                                             | -                   | t bit            |                  |                     |                     |  |  |

|               | •                                                         | = Comparator output is inverted                                                                              |                     |                  |                  |                     |                     |  |  |

|               | 0 = Compara                                               | tor output is no                                                                                             | t inverted          |                  |                  |                     |                     |  |  |

| bit 12-11     | Unimplemen                                                | ted: Read as '                                                                                               | 0'                  |                  |                  |                     |                     |  |  |

| bit 10        | OPMODE: O                                                 | p Amp/Compai                                                                                                 | ator Operatio       | n Mode Select    | t bit            |                     |                     |  |  |

|               |                                                           | erates as an o<br>erates as a co                                                                             |                     |                  |                  |                     |                     |  |  |

| bit 9         | CEVT: Comp                                                | arator Event bi                                                                                              | t                   |                  |                  |                     |                     |  |  |

|               | interrupts                                                | s until the bit is                                                                                           | cleared             | VPOL<1:0> s      | ettings occurred | ; disables futur    | e triggers an       |  |  |

|               | •                                                         | ator event did n                                                                                             |                     |                  |                  |                     |                     |  |  |

| bit 8         |                                                           | arator Output b                                                                                              |                     |                  |                  |                     |                     |  |  |

|               | When CPOL = 0 (non-inverted polarity):<br>1 = VIN+ > VIN- |                                                                                                              |                     |                  |                  |                     |                     |  |  |

|               | 1 = VIN + > VI $0 = VIN + < VI$                           |                                                                                                              |                     |                  |                  |                     |                     |  |  |

|               |                                                           | = 1 (inverted p                                                                                              | olarity):           |                  |                  |                     |                     |  |  |

|               | 1 = VIN+ < VI                                             | N-                                                                                                           | <u> </u>            |                  |                  |                     |                     |  |  |

|               | 0 = VIN + > VI                                            |                                                                                                              |                     |                  |                  |                     |                     |  |  |

### **REGISTER 25-2:** CMxCON: COMPARATOR x CONTROL REGISTER (x = 1, 2 OR 3)

- Note 1: Inputs that are selected and not available will be tied to Vss. See the "Pin Diagrams" section for available inputs for each package.

- 2: This output is not available when OPMODE (CMxCON<10>) = 1.

| Base<br>Instr<br># | Assembly<br>Mnemonic |        | Assembly Syntax                                  | Description                               | # of<br>Words | # of<br>Cycles <sup>(2)</sup> | Status Flags<br>Affected |

|--------------------|----------------------|--------|--------------------------------------------------|-------------------------------------------|---------------|-------------------------------|--------------------------|

| 46                 | MOV                  | MOV    | f,Wn                                             | Move f to Wn                              | 1             | 1                             | None                     |

|                    |                      | MOV    | f                                                | Move f to f                               | 1             | 1                             | None                     |

|                    |                      | MOV    | f,WREG                                           | Move f to WREG                            | 1             | 1                             | None                     |

|                    |                      | MOV    | #litl6,Wn                                        | Move 16-bit literal to Wn                 | 1             | 1                             | None                     |

|                    |                      | MOV.b  | #lit8,Wn                                         | Move 8-bit literal to Wn                  | 1             | 1                             | None                     |

|                    |                      | MOV    | Wn,f                                             | Move Wn to f                              | 1             | 1                             | None                     |

|                    |                      | MOV    | Wso,Wdo                                          | Move Ws to Wd                             | 1             | 1                             | None                     |

|                    |                      | MOV    | WREG, f                                          | Move WREG to f                            | 1             | 1                             | None                     |

|                    |                      | MOV.D  | Wns,Wd                                           | Move Double from W(ns):W(ns + 1) to<br>Wd | 1             | 2                             | None                     |

|                    |                      | MOV.D  | Ws , Wnd                                         | Move Double from Ws to W(nd +<br>1):W(nd) | 1             | 2                             | None                     |

| 47                 | MOVPAG               | MOVPAG | #lit10,DSRPAG                                    | Move 10-bit literal to DSRPAG             | 1             | 1                             | None                     |

|                    |                      | MOVPAG | #lit9,DSWPAG                                     | Move 9-bit literal to DSWPAG              | 1             | 1                             | None                     |

|                    |                      | MOVPAG | #lit8,TBLPAG                                     | Move 8-bit literal to TBLPAG              | 1             | 1                             | None                     |

|                    |                      | MOVPAG | Ws, DSRPAG                                       | Move Ws<9:0> to DSRPAG                    | 1             | 1                             | None                     |

|                    |                      | MOVPAG | Ws, DSWPAG                                       | Move Ws<8:0> to DSWPAG                    | 1             | 1                             | None                     |

|                    |                      | MOVPAG | Ws, TBLPAG                                       | Move Ws<7:0> to TBLPAG                    | 1             | 1                             | None                     |

| 48                 | MOVSAC               | MOVSAC | Acc,Wx,Wxd,Wy,Wyd,AWB <sup>(1)</sup>             | Prefetch and store accumulator            | 1             | 1                             | None                     |

| 49                 | MPY                  | MPY    | Wm*Wn,Acc,Wx,Wxd,Wy,Wyd <sup>(1)</sup>           | Multiply Wm by Wn to Accumulator          | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                      | MPY    | Wm*Wm,Acc,Wx,Wxd,Wy,Wyd <sup>(1)</sup>           | Square Wm to Accumulator                  | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

| 50                 | MPY.N                | MPY.N  | Wm*Wn,Acc,Wx,Wxd,Wy,Wyd(1)                       | -(Multiply Wm by Wn) to Accumulator       | 1             | 1                             | None                     |

| 51                 | MSC                  | MSC    | Wm*Wm, Acc, Wx, Wxd, Wy, Wyd, AWB <sup>(1)</sup> | Multiply and Subtract from Accumulator    | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

#### TABLE 28-2: INSTRUCTION SET OVERVIEW (CONTINUED)

Note 1: These instructions are available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

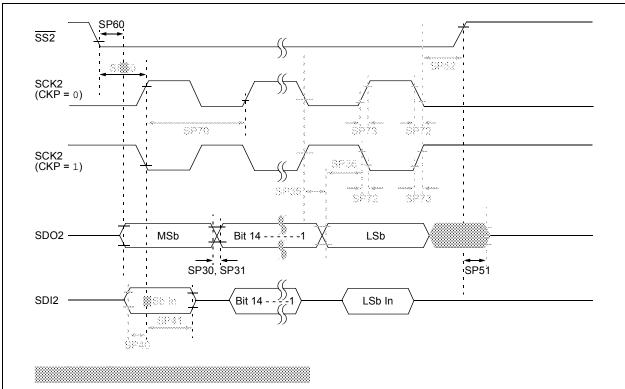

#### FIGURE 30-19: SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0) TIMING CHARACTERISTICS

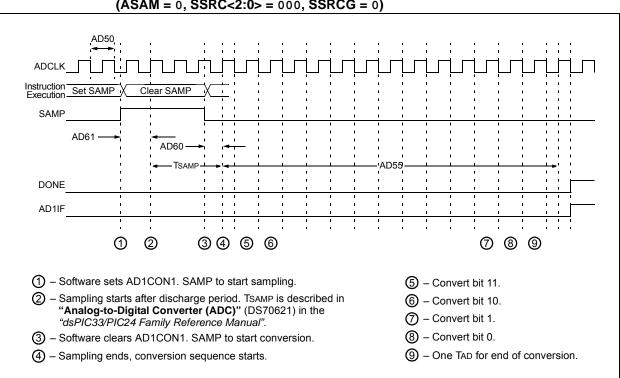

#### FIGURE 30-36: ADC CONVERSION (12-BIT MODE) TIMING CHARACTERISTICS (ASAM = 0, SSRC<2:0> = 000, SSRCG = 0)

### **Revision C (December 2011)**

This revision includes typographical and formatting changes throughout the data sheet text.

In addition, where applicable, new sections were added to each peripheral chapter that provide information and links to related resources, as well as helpful tips. For examples, see Section 20.1 "UART Helpful Tips" and Section 3.6 "CPU Resources". All occurrences of TLA were updated to VTLA throughout the document, with the exception of the pin diagrams (updated diagrams were not available at time of publication).

A new chapter, Section 31.0 "DC and AC Device Characteristics Graphs", was added.