Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Betans                     |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 60 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 35                                                                             |

| Program Memory Size        | 512KB (170K x 24)                                                              |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 24K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

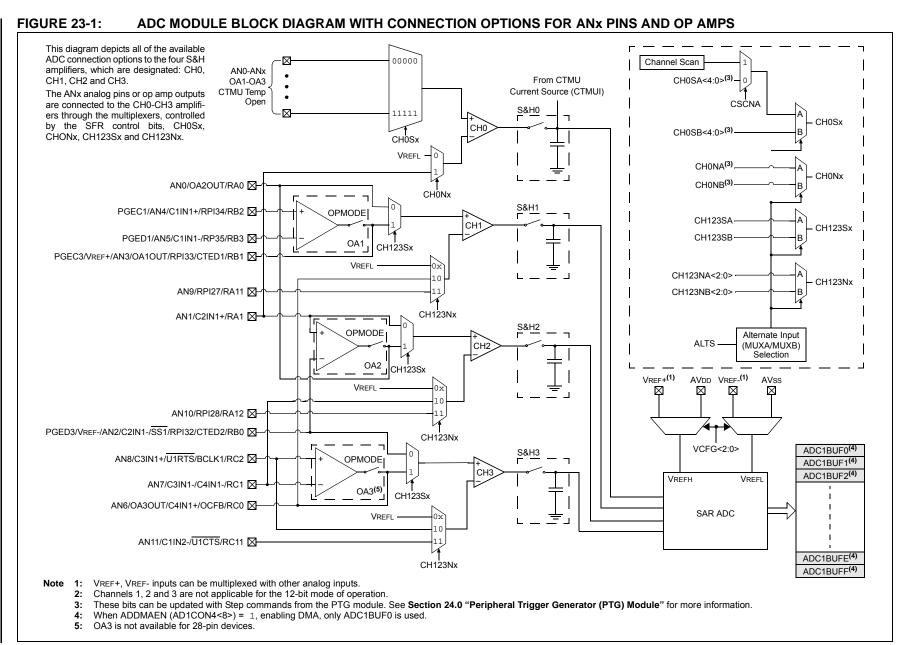

| Data Converters            | A/D 9x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-TQFP                                                                        |

| Supplier Device Package    | 44-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep512gp204-h-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **REGISTER 3-1:** SR: CPU STATUS REGISTER (CONTINUED)

| bit 7-5       | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2,3)</sup><br>111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled<br>110 = CPU Interrupt Priority Level is 6 (14)<br>101 = CPU Interrupt Priority Level is 5 (13)<br>100 = CPU Interrupt Priority Level is 4 (12)<br>011 = CPU Interrupt Priority Level is 3 (11)<br>010 = CPU Interrupt Priority Level is 2 (10)<br>001 = CPU Interrupt Priority Level is 1 (9)<br>000 = CPU Interrupt Priority Level is 0 (8) |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4         | RA: REPEAT Loop Active bit<br>1 = REPEAT loop in progress<br>0 = REPEAT loop not in progress                                                                                                                                                                                                                                                                                                                                                                                                    |

| bit 3         | N: MCU ALU Negative bit<br>1 = Result was negative<br>0 = Result was non-negative (zero or positive)                                                                                                                                                                                                                                                                                                                                                                                            |

| bit 2         | <ul> <li>OV: MCU ALU Overflow bit</li> <li>This bit is used for signed arithmetic (2's complement). It indicates an overflow of the magnitude that causes the sign bit to change state.</li> <li>1 = Overflow occurred for signed arithmetic (in this arithmetic operation)</li> <li>0 = No overflow occurred</li> </ul>                                                                                                                                                                        |

| bit 1         | <ul> <li><b>Z:</b> MCU ALU Zero bit</li> <li>1 = An operation that affects the Z bit has set it at some time in the past</li> <li>0 = The most recent operation that affects the Z bit has cleared it (i.e., a non-zero result)</li> </ul>                                                                                                                                                                                                                                                      |

| bit 0         | <b>C:</b> MCU ALU Carry/Borrow bit<br>1 = A carry-out from the Most Significant bit of the result occurred<br>0 = No carry-out from the Most Significant bit of the result occurred                                                                                                                                                                                                                                                                                                             |

| Note 1:<br>2: | This bit is available on dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices only.<br>The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority                                                                                                                                                                                                                                                                                                     |

- Level. The value in parentheses indicates the IPL, if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

3: The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

- 4: A data write to the SR register can modify the SA and SB bits by either a data write to SA and SB or by clearing the SAB bit. To avoid a possible SA or SB bit write race condition, the SA and SB bits should not be modified using bit operations.

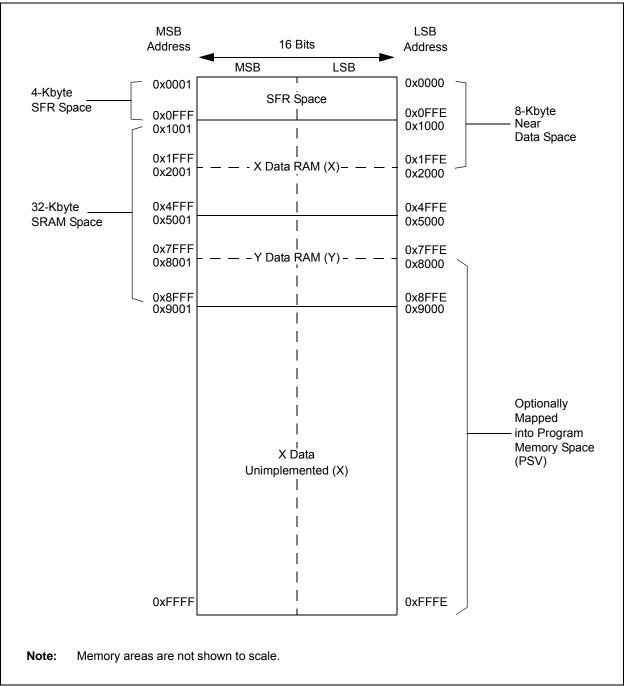

# FIGURE 4-10: DATA MEMORY MAP FOR dsPIC33EP256MC20X/50X AND dsPIC33EP256GP50X DEVICES

## TABLE 4-39: PMD REGISTER MAP FOR dsPIC33EPXXXGP50X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   |        |       |       | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | —      | C1MD   | AD1MD | 0000          |

| PMD2         | 0762  |        | _      | _      | -      | IC4MD  | IC3MD  | IC2MD | IC1MD | _      | _     | _     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  | _      | _      | _      | _      | _      | CMPMD  |       |       | CRCMD  | _     | —     | —      |        | —      | I2C2MD |       | 0000          |

| PMD4         | 0766  | _      | _      | _      | _      | _      | _      |       |       | _      | _     | —     | —      | REFOMD | CTMUMD |        |       | 0000          |

| PMD6         | 076A  | _      |        | _      | _      | _      |        |       |       | _      |       | —     | _      |        | —      |        |       | 0000          |

|              |       |        |        |        |        |        |        |       |       |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  |        |        |        |        |        |        |       |       |        |       |       | DMA1MD | PTGMD  |        |        |       | 0000          |

| FIND/        | 0700  | _      | _      | _      | _      | _      | _      | _     | _     | _      | —     | _     | DMA2MD | FIGND  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |       |       |        |       |       | DMA3MD |        |        |        |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-40: PMD REGISTER MAP FOR dsPIC33EPXXXMC50X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | QEI1MD | PWMMD  | _      | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | —      | C1MD   | AD1MD | 0000          |

| PMD2         | 0762  | _      | —      | —      | —      | IC4MD  | IC3MD  | IC2MD  | IC1MD  | _      | —     | —     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  | _      | _      | _      | _      | _      | CMPMD  | _      | _      | CRCMD  | _     | _     | _      | _      | _      | I2C2MD | _     | 0000          |

| PMD4         | 0766  | _      | _      | _      | _      | _      | _      | _      | _      | _      | _     | _     | _      | REFOMD | CTMUMD | _      | _     | 0000          |

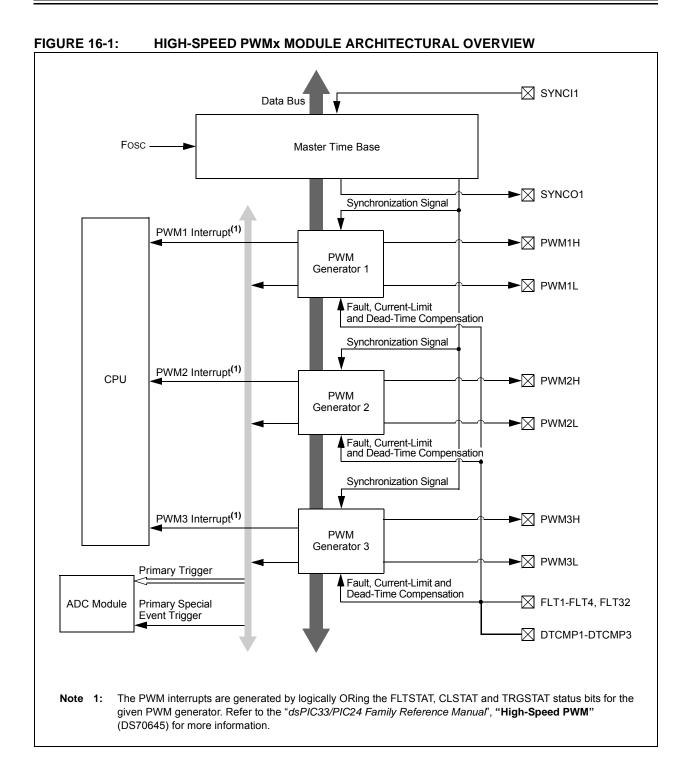

| PMD6         | 076A  | —      | —      |        | _      | —      | PWM3MD | PWM2MD | PWM1MD | —      |       |       | _      | —      |        | —      | -     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  |        |        |        |        |        |        |        |        |        |       |       | DMA1MD | PTGMD  |        |        |       | 0000          |

| FIVID7       | 0700  | _      | _      | _      | _      | _      | _      | _      | _      | —      | _     | _     | DMA2MD | FIGND  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA3MD |        |        |        |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

DS70000657H-page 95

#### TABLE 4-53: PORTA REGISTER MAP FOR PIC24EPXXXGP/MC204 AND dsPIC33EPXXXGP/MC204/504 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|---------|--------|--------|--------|-------|-------|--------|--------|--------|--------|--------|---------------|

| TRISA        | 0E00  | _      | _      | _      | _      | _      | TRISA10 | TRISA9 | TRISA8 | TRISA7 | -     | _     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 079F          |

| PORTA        | 0E02  |        | _      | _      | -      | _      | RA10    | RA9    | RA8    | RA7    | -     | _     | RA4    | RA3    | RA2    | RA1    | RA0    | 0000          |

| LATA         | 0E04  | _      | _      | _      | _      | _      | LATA10  | LATA9  | LATA8  | LATA7  | -     | _     | LATA4  | LATA3  | LATA2  | LA1TA1 | LA0TA0 | 0000          |

| ODCA         | 0E06  | _      | —      | —      | _      |        | ODCA10  | ODCA9  | ODCA8  | ODCA7  | —     | —     | ODCA4  | ODCA3  | ODCA2  | ODCA1  | ODCA0  | 0000          |

| CNENA        | 0E08  | _      | —      | —      | _      |        | CNIEA10 | CNIEA9 | CNIEA8 | CNIEA7 | —     | —     | CNIEA4 | CNIEA3 | CNIEA2 | CNIEA1 | CNIEA0 | 0000          |

| CNPUA        | 0E0A  | _      | —      | —      | _      |        | CNPUA10 | CNPUA9 | CNPUA8 | CNPUA7 | —     | —     | CNPUA4 | CNPUA3 | CNPUA2 | CNPUA1 | CNPUA0 | 0000          |

| CNPDA        | 0E0C  | _      | —      | —      | _      |        | CNPDA10 | CNPDA9 | CNPDA8 | CNPDA7 | —     | —     | CNPDA4 | CNPDA3 | CNPDA2 | CNPDA1 | CNPDA0 | 0000          |

| ANSELA       | 0E0E  | _      | —      | _      | _      | _      | —       | _      | —      | _      | _     | —     | ANSA4  | _      | _      | ANSA1  | ANSA0  | 0013          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-54: PORTB REGISTER MAP FOR PIC24EPXXXGP/MC204 AND dsPIC33EPXXXGP/MC204/504 DEVICES ONLY

| File<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISB        | 0E10  | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF          |

| PORTB        | 0E12  | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx          |

| LATB         | 0E14  | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | xxxx          |

| ODCB         | 0E16  | ODCB15  | ODCB14  | ODCB13  | ODCB12  | ODCB11  | ODCB10  | ODCB9  | ODCB8  | ODCB7  | ODCB6  | ODCB5  | ODCB4  | ODCB3  | ODCB2  | ODCB1  | ODCB0  | 0000          |

| CNENB        | 0E18  | CNIEB15 | CNIEB14 | CNIEB13 | CNIEB12 | CNIEB11 | CNIEB10 | CNIEB9 | CNIEB8 | CNIEB7 | CNIEB6 | CNIEB5 | CNIEB4 | CNIEB3 | CNIEB2 | CNIEB1 | CNIEB0 | 0000          |

| CNPUB        | 0E1A  | CNPUB15 | CNPUB14 | CNPUB13 | CNPUB12 | CNPUB11 | CNPUB10 | CNPUB9 | CNPUB8 | CNPUB7 | CNPUB6 | CNPUB5 | CNPUB4 | CNPUB3 | CNPUB2 | CNPUB1 | CNPUB0 | 0000          |

| CNPDB        | 0E1C  | CNPDB15 | CNPDB14 | CNPDB13 | CNPDB12 | CNPDB11 | CNPDB10 | CNPDB9 | CNPDB8 | CNPDB7 | CNPDB6 | CNPDB5 | CNPDB4 | CNPDB3 | CNPDB2 | CNPDB1 | CNPDB0 | 0000          |

| ANSELB       | 0E1E  | _       | _       | _       | _       | _       | -       | -      | ANSB8  | _      | _      | _      | _      | ANSB3  | ANSB2  | ANSB1  | ANSB0  | 010F          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-55: PORTC REGISTER MAP FOR PIC24EPXXXGP/MC204 AND dsPIC33EPXXXGP/MC204/504 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISC        | 0E20  | _      | _      | _      |        | —      | _      | TRISC9 | TRISC8 | TRISC7 | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 03FF          |

| PORTC        | 0E22  | _      | _      | -      | _      | _      | —      | RC9    | RC8    | RC7    | RC6    | RC5    | RC4    | RC3    | RC2    | RC1    | RC0    | xxxx          |

| LATC         | 0E24  | —      | —      | _      | _      |        | —      | LATC9  | LATC8  | LATC7  | LATC6  | LATC5  | LATC4  | LATC3  | LATC2  | LATC1  | LATC0  | xxxx          |

| ODCC         | 0E26  | —      | —      | _      | _      |        | —      | ODCC9  | ODCC8  | ODCC7  | ODCC6  | ODCC5  | ODCC4  | ODCC3  | ODCC2  | ODCC1  | ODCC0  | 0000          |

| CNENC        | 0E28  | —      | —      | _      | _      |        | —      | CNIEC9 | CNIEC8 | CNIEC7 | CNIEC6 | CNIEC5 | CNIEC4 | CNIEC3 | CNIEC2 | CNIEC1 | CNIEC0 | 0000          |

| CNPUC        | 0E2A  | —      | —      | _      | _      |        | —      | CNPUC9 | CNPUC8 | CNPUC7 | CNPUC6 | CNPUC5 | CNPUC4 | CNPUC3 | CNPUC2 | CNPUC1 | CNPUC0 | 0000          |

| CNPDC        | 0E2C  | —      | —      | _      | _      |        | —      | CNPDC9 | CNPDC8 | CNPDC7 | CNPDC6 | CNPDC5 | CNPDC4 | CNPDC3 | CNPDC2 | CNPDC1 | CNPDC0 | 0000          |

| ANSELC       | 0E2E  | —      | —      | _      | _      |        | —      | _      |        |        |        | —      |        | _      | ANSC2  | ANSC1  | ANSC0  | 0007          |

Legend: x = unknown value on Reset, --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

© 2011-2013 Microchip Technology Inc.

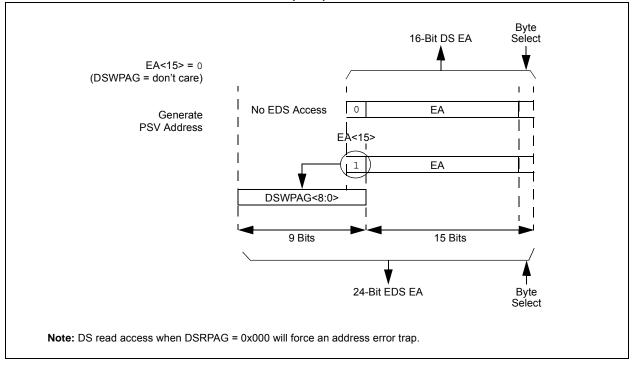

#### EXAMPLE 4-2: EXTENDED DATA SPACE (EDS) WRITE ADDRESS GENERATION

The paged memory scheme provides access to multiple 32-Kbyte windows in the EDS and PSV memory. The Data Space Page registers, DSxPAG, in combination with the upper half of the Data Space address, can provide up to 16 Mbytes of additional address space in the EDS and 8 Mbytes (DSRPAG only) of PSV address space. The paged data memory space is shown in Example 4-3.

The Program Space (PS) can be accessed with a DSRPAG of 0x200 or greater. Only reads from PS are supported using the DSRPAG. Writes to PS are not supported, so DSWPAG is dedicated to DS, including EDS only. The Data Space and EDS can be read from, and written to, using DSRPAG and DSWPAG, respectively.

# 4.5.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions. which apply to dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices, and the DSP accumulator class of instructions, which apply to the dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices, provide a greater degree of addressing flexibility than other instructions. In addition to the addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

Note: For the MOV instructions, the addressing mode specified in the instruction can differ for the source and destination EA. However, the 4-bit Wb (Register Offset) field is shared by both source and destination (but typically only used by one).

In summary, the following addressing modes are supported by move and accumulator instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-modified

- Register Indirect Pre-modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-Bit Literal

- 16-Bit Literal

Note: Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

#### 4.5.4 MAC INSTRUCTIONS (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X DEVICES ONLY)

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY. N, MOVSAC and MSC), also referred to as MAC instructions, use a simplified set of addressing modes to allow the user application to effectively manipulate the Data Pointers through register indirect tables.

The Two-Source Operand Prefetch registers must be members of the set: {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU, and W10 and W11 are always directed to the Y AGU. The Effective Addresses generated (before and after modification) must therefore, be valid addresses within X Data Space for W8 and W9, and Y Data Space for W10 and W11.

Note: Register Indirect with Register Offset Addressing mode is available only for W9 (in X space) and W11 (in Y space).

In summary, the following addressing modes are supported by the  ${\tt MAC}$  class of instructions:

- · Register Indirect

- Register Indirect Post-Modified by 2

- · Register Indirect Post-Modified by 4

- Register Indirect Post-Modified by 6

- Register Indirect with Register Offset (Indexed)

## 4.5.5 OTHER INSTRUCTIONS

Besides the addressing modes outlined previously, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ULNK, the source of an operand or result is implied by the opcode itself. Certain operations, such as a NOP, do not have any operands.

## 4.6 Modulo Addressing (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X Devices Only)

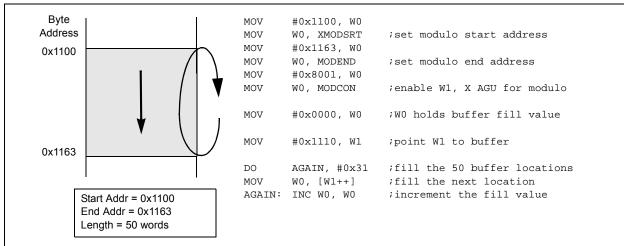

Modulo Addressing mode is a method of providing an automated means to support circular data buffers using hardware. The objective is to remove the need for software to perform data address boundary checks when executing tightly looped code, as is typical in many DSP algorithms.

Modulo Addressing can operate in either Data or Program Space (since the Data Pointer mechanism is essentially the same for both). One circular buffer can be supported in each of the X (which also provides the pointers into Program Space) and Y Data Spaces. Modulo Addressing can operate on any W Register Pointer. However, it is not advisable to use W14 or W15 for Modulo Addressing since these two registers are used as the Stack Frame Pointer and Stack Pointer, respectively.

In general, any particular circular buffer can be configured to operate in only one direction, as there are certain restrictions on the buffer start address (for incrementing buffers) or end address (for decrementing buffers), based upon the direction of the buffer.

The only exception to the usage restrictions is for buffers that have a power-of-two length. As these buffers satisfy the start and end address criteria, they can operate in a bidirectional mode (that is, address boundary checks are performed on both the lower and upper address boundaries).

## 4.6.1 START AND END ADDRESS

The Modulo Addressing scheme requires that a starting and ending address be specified, and loaded into the 16-bit Modulo Buffer Address registers: XMODSRT, XMODEND, YMODSRT and YMODEND (see Table 4-1).

| Note: | Y space Modulo Addressing EA calcula- |

|-------|---------------------------------------|

|       | tions assume word-sized data (LSb of  |

|       | every EA is always clear).            |

The length of a circular buffer is not directly specified. It is determined by the difference between the corresponding start and end addresses. The maximum possible length of the circular buffer is 32K words (64 Kbytes).

#### 4.6.2 W ADDRESS REGISTER SELECTION

The Modulo and Bit-Reversed Addressing Control register, MODCON<15:0>, contains enable flags as well as a W register field to specify the W Address registers. The XWM and YWM fields select the registers that operate with Modulo Addressing:

- If XWM = 1111, X RAGU and X WAGU Modulo Addressing is disabled

- If YWM = 1111, Y AGU Modulo Addressing is disabled

The X Address Space Pointer W register (XWM), to which Modulo Addressing is to be applied, is stored in MODCON<3:0> (see Table 4-1). Modulo Addressing is enabled for X Data Space when XWM is set to any value other than '1111' and the XMODEN bit is set (MODCON<15>).

The Y Address Space Pointer W register (YWM), to which Modulo Addressing is to be applied, is stored in MODCON<7:4>. Modulo Addressing is enabled for Y Data Space when YWM is set to any value other than '1111' and the YMODEN bit is set at MODCON<14>.

## FIGURE 4-20: MODULO ADDRESSING OPERATION EXAMPLE

| R/W-0  | U-0   | R/W-0 | R/W-0  | R/W-0               | R-0 | R-0   | R-0   |

|--------|-------|-------|--------|---------------------|-----|-------|-------|

| VAR    | —     | US1   | US0    | EDT                 | DL2 | DL1   | DL0   |

| bit 15 | -     | •     |        |                     |     |       | bit 8 |

|        |       |       |        |                     |     |       |       |

| R/W-0  | R/W-0 | R/W-1 | R/W-0  | R/C-0               | R-0 | R/W-0 | R/W-0 |

| SATA   | SATB  | SATDW | ACCSAT | IPL3 <sup>(2)</sup> | SFA | RND   | IF    |

| bit 7  |       | •     |        |                     |     |       | bit 0 |

|        |       |       |        |                     |     |       |       |

|        |       |       |        |                     |     |       |       |

# **REGISTER 7-2:** CORCON: CORE CONTROL REGISTER<sup>(1)</sup>

| Legend:           | C = Clearable bit |                      |                    |

|-------------------|-------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bi | t, read as '0'     |

| -n = Value at POR | '1'= Bit is set   | '0' = Bit is cleared | x = Bit is unknown |

bit

| VAR: Variable Exception Processing Latency Control                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------|

| <ol> <li>1 = Variable exception processing is enabled</li> </ol>                                                              |

| 0 = Fixed exception processing is enabled                                                                                     |

| IPL3: CPU Interrupt Priority Level Status bit 3 <sup>(2)</sup>                                                                |

| <ul> <li>1 = CPU Interrupt Priority Level is greater than 7</li> <li>0 = CPU Interrupt Priority Level is 7 or less</li> </ul> |

|                                                                                                                               |

**Note 1:** For complete register details, see Register 3-2.

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

## REGISTER 11-15: RPINR37: PERIPHERAL PIN SELECT INPUT REGISTER 37 (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

| U-0                | R/W-0                                      | R/W-0                                           | R/W-0                                      | R/W-0                       | R/W-0            | R/W-0           | R/W-0 |

|--------------------|--------------------------------------------|-------------------------------------------------|--------------------------------------------|-----------------------------|------------------|-----------------|-------|

|                    |                                            |                                                 |                                            | SYNCI1R<6:03                | >                |                 |       |

| bit 15             |                                            |                                                 |                                            |                             |                  |                 | bit 8 |

|                    |                                            |                                                 |                                            |                             |                  |                 |       |

| U-0                | U-0                                        | U-0                                             | U-0                                        | U-0                         | U-0              | U-0             | U-0   |

| _                  |                                            |                                                 | —                                          |                             |                  | <u> </u>        | _     |

| bit 7              |                                            |                                                 |                                            |                             |                  |                 | bit 0 |

|                    |                                            |                                                 |                                            |                             |                  |                 |       |

| Legend:            |                                            |                                                 |                                            |                             |                  |                 |       |

| R = Readab         | ole bit                                    | W = Writable                                    | bit                                        | U = Unimplem                | nented bit, read | l as '0'        |       |

| -n = Value a       | it POR                                     | '1' = Bit is set                                |                                            | '0' = Bit is clea           | ared             | x = Bit is unkn | iown  |

|                    |                                            |                                                 |                                            |                             |                  |                 |       |

|                    |                                            |                                                 |                                            |                             |                  |                 |       |

| bit 15             | Unimplemer                                 | nted: Read as '                                 | 0'                                         |                             |                  |                 |       |

| bit 15<br>bit 14-8 | SYNCI1R<6:                                 |                                                 | M Synchroniz                               | zation Input 1 to<br>nbers) | the Correspon    | ding RPn Pin b  | its   |

|                    | SYNCI1R<6:<br>(see Table 11                | <b>0&gt;:</b> Assign PW                         | M Synchroniz selection nur                 |                             | the Correspon    | ding RPn Pin b  | its   |

|                    | SYNCI1R<6:<br>(see Table 11                | • <b>0&gt;:</b> Assign PWI<br>I-2 for input pin | M Synchroniz selection nur                 |                             | the Correspon    | ding RPn Pin b  | its   |

|                    | SYNCI1R<6:<br>(see Table 11                | • <b>0&gt;:</b> Assign PWI<br>I-2 for input pin | M Synchroniz selection nur                 |                             | the Correspon    | ding RPn Pin b  | its   |

|                    | SYNCI1R<6:<br>(see Table 11<br>1111001 = I | • <b>0&gt;:</b> Assign PWI<br>I-2 for input pin | M Synchroniz<br>selection nur<br>121<br>P1 |                             | the Correspon    | ding RPn Pin b  | its   |

# 17.0 QUADRATURE ENCODER INTERFACE (QEI) MODULE (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Quadrature Encoder Interface (QEI)" (DS70601) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This chapter describes the Quadrature Encoder Interface (QEI) module and associated operational modes. The QEI module provides the interface to incremental encoders for obtaining mechanical position data.

The operational features of the QEI module include:

- 32-Bit Position Counter

- 32-Bit Index Pulse Counter

- 32-Bit Interval Timer

- 16-Bit Velocity Counter

- 32-Bit Position Initialization/Capture/Compare High register

- 32-Bit Position Compare Low register

- x4 Quadrature Count mode

- External Up/Down Count mode

- External Gated Count mode

- External Gated Timer mode

- Internal Timer mode

Figure 17-1 illustrates the QEI block diagram.

## REGISTER 17-7: VEL1CNT: VELOCITY COUNTER 1 REGISTER

| R/W-0                             | R/W-0 | R/W-0            | R/W-0                              | R/W-0                | R/W-0 | R/W-0              | R/W-0 |

|-----------------------------------|-------|------------------|------------------------------------|----------------------|-------|--------------------|-------|

|                                   |       |                  | VELC                               | NT<15:8>             |       |                    |       |

| bit 15                            |       |                  |                                    |                      |       |                    | bit 8 |

|                                   |       |                  |                                    |                      |       |                    |       |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0                              | R/W-0                | R/W-0 | R/W-0              | R/W-0 |

|                                   |       |                  | VELC                               | NT<7:0>              |       |                    |       |

| bit 7                             |       |                  |                                    |                      |       |                    | bit 0 |

|                                   |       |                  |                                    |                      |       |                    |       |

| Legend:                           |       |                  |                                    |                      |       |                    |       |

| R = Readable bit W = Writable bit |       | oit              | U = Unimplemented bit, read as '0' |                      |       |                    |       |

| -n = Value at POR '1              |       | '1' = Bit is set |                                    | '0' = Bit is cleared |       | x = Bit is unknown |       |

bit 15-0 VELCNT<15:0>: Velocity Counter bits

### REGISTER 17-8: INDX1CNTH: INDEX COUNTER 1 HIGH WORD REGISTER

| R/W-0  | R/W-0 | R/W-0 | R/W-0               | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|---------------------|----------|-------|-------|-------|

|        |       |       | INDXCN <sup>®</sup> | T<31:24> |       |       |       |

| bit 15 |       |       |                     |          |       |       | bit 8 |

|        |       |       |                     |          |       |       |       |

| R/W-0  | R/W-0 | R/W-0 | R/W-0               | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|        |       |       | INDXCN              | T<23:16> |       |       |       |

| bit 7  |       |       |                     |          |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 INDXCNT<31:16>: High Word Used to Form 32-Bit Index Counter Register (INDX1CNT) bits

#### REGISTER 17-9: INDX1CNTL: INDEX COUNTER 1 LOW WORD REGISTER

'1' = Bit is set

| R/W-0          | R/W-0 | R/W-0            | R/W-0 | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

|----------------|-------|------------------|-------|--------------|------------------|----------|-------|

|                |       |                  | INDXC | NT<15:8>     |                  |          |       |

| bit 15         |       |                  |       |              |                  |          | bit 8 |

|                |       |                  |       |              |                  |          |       |

| R/W-0          | R/W-0 | R/W-0            | R/W-0 | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

|                |       |                  | INDXC | NT<7:0>      |                  |          |       |

| bit 7          |       |                  |       |              |                  |          | bit 0 |

|                |       |                  |       |              |                  |          |       |

| Legend:        |       |                  |       |              |                  |          |       |

| R = Readable b | oit   | W = Writable bit | t     | U = Unimpler | mented bit, read | l as '0' |       |

|                |       |                  |       |              |                  |          |       |

'0' = Bit is cleared

bit 15-0 INDXCNT<15:0>: Low Word Used to Form 32-Bit Index Counter Register (INDX1CNT) bits

-n = Value at POR

x = Bit is unknown

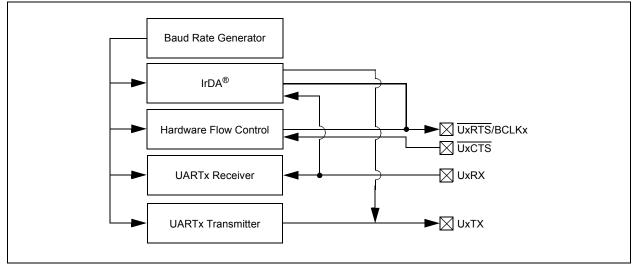

# 20.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "UART" (DS70582) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X family of devices contains two UART modules.

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X device family. The UART is a full-duplex, asynchronous system that can communicate with peripheral devices, such as personal computers, LIN/J2602, RS-232 and RS-485 interfaces. The module also supports a hardware flow control option with the UxCTS and UxRTS pins, and also includes an IrDA<sup>®</sup> encoder and decoder.

Note: <u>Hardware</u> flow control using UxRTS and UxCTS is not available on all pin count devices. See the "**Pin Diagrams**" section for availability.

The primary features of the UARTx module are:

- Full-Duplex, 8 or 9-Bit Data Transmission through the UxTX and UxRX Pins

- Even, Odd or No Parity Options (for 8-bit data)

- One or Two Stop bits

- Hardware Flow Control Option with UxCTS and UxRTS Pins

- Fully Integrated Baud Rate Generator with 16-Bit Prescaler

- Baud Rates Ranging from 4.375 Mbps to 67 bps at 16x mode at 70 MIPS

- Baud Rates Ranging from 17.5 Mbps to 267 bps at 4x mode at 70 MIPS

- 4-Deep First-In First-Out (FIFO) Transmit Data Buffer

- 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-bit mode with Address Detect (9th bit = 1)

- · Transmit and Receive Interrupts

- A Separate Interrupt for all UARTx Error Conditions

- · Loopback mode for Diagnostic Support

- · Support for Sync and Break Characters

- Support for Automatic Baud Rate Detection

- IrDA<sup>®</sup> Encoder and Decoder Logic

- 16x Baud Clock Output for IrDA Support

A simplified block diagram of the UARTx module is shown in Figure 20-1. The UARTx module consists of these key hardware elements:

- · Baud Rate Generator

- Asynchronous Transmitter

- Asynchronous Receiver

#### FIGURE 20-1: UARTx SIMPLIFIED BLOCK DIAGRAM

© 2011-2013 Microchip Technology Inc.

# 21.0 ENHANCED CAN (ECAN™) MODULE (dsPIC33EPXXXGP/ MC50X DEVICES ONLY)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXGP/MC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Enhanced Controller Area Network (ECAN™)" (DS70353) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

## 21.1 Overview

The Enhanced Controller Area Network (ECAN) module is a serial interface, useful for communicating with other CAN modules or microcontroller devices. This interface/protocol was designed to allow communications within noisy environments. The dsPIC33EPXXXGP/MC50X devices contain one ECAN module.

The ECAN module is a communication controller implementing the CAN 2.0 A/B protocol, as defined in the BOSCH CAN specification. The module supports CAN 1.2, CAN 2.0A, CAN 2.0B Passive and CAN 2.0B Active versions of the protocol. The module implementation is a full CAN system. The CAN specification is not covered within this data sheet. The reader can refer to the BOSCH CAN specification for further details.

The ECAN module features are as follows:

- Implementation of the CAN protocol, CAN 1.2, CAN 2.0A and CAN 2.0B

- · Standard and extended data frames

- 0-8 bytes data length

- Programmable bit rate up to 1 Mbit/sec

- Automatic response to remote transmission requests

- Up to eight transmit buffers with application specified prioritization and abort capability (each buffer can contain up to 8 bytes of data)

- Up to 32 receive buffers (each buffer can contain up to 8 bytes of data)

- Up to 16 full (Standard/Extended Identifier)

acceptance filters

- · Three full acceptance filter masks

- DeviceNet<sup>™</sup> addressing support

- Programmable wake-up functionality with integrated low-pass filter

- Programmable Loopback mode supports self-test operation

- Signaling via interrupt capabilities for all CAN receiver and transmitter error states

- · Programmable clock source

- Programmable link to Input Capture (IC2) module for time-stamping and network synchronization

- · Low-power Sleep and Idle mode

The CAN bus module consists of a protocol engine and message buffering/control. The CAN protocol engine handles all functions for receiving and transmitting messages on the CAN bus. Messages are transmitted by first loading the appropriate data registers. Status and errors can be checked by reading the appropriate registers. Any message detected on the CAN bus is checked for errors and then matched against filters to see if it should be received and stored in one of the receive registers.

| _                    |                                                                     |                                 |                         |                        |                      |                      |                      |

|----------------------|---------------------------------------------------------------------|---------------------------------|-------------------------|------------------------|----------------------|----------------------|----------------------|

| R/W-0                | U-0                                                                 | U-0                             | R/W-0                   | R/W-0                  | R/W-0                | R/W-0                | R/W-0                |

| ADRC                 | —                                                                   | —                               | SAMC4 <sup>(1)</sup>    | SAMC3 <sup>(1)</sup>   | SAMC2 <sup>(1)</sup> | SAMC1 <sup>(1)</sup> | SAMC0 <sup>(1)</sup> |

| bit 15               |                                                                     |                                 |                         |                        |                      |                      | bit 8                |

|                      |                                                                     |                                 |                         |                        |                      |                      |                      |

| R/W-0                | R/W-0                                                               | R/W-0                           | R/W-0                   | R/W-0                  | R/W-0                | R/W-0                | R/W-0                |

| ADCS7 <sup>(2)</sup> | ADCS6 <sup>(2)</sup>                                                | ADCS5 <sup>(2)</sup>            | ADCS4 <sup>(2)</sup>    | ADCS3 <sup>(2)</sup>   | ADCS2 <sup>(2)</sup> | ADCS1 <sup>(2)</sup> | ADCS0 <sup>(2)</sup> |

| bit 7                |                                                                     |                                 |                         |                        |                      |                      | bit 0                |

| r                    |                                                                     |                                 |                         |                        |                      |                      |                      |

| Legend:              |                                                                     |                                 |                         |                        |                      |                      |                      |

| R = Readable b       |                                                                     | W = Writable k                  | bit                     | •                      | nented bit, read     | l as '0'             |                      |

| -n = Value at P      | OR                                                                  | '1' = Bit is set                |                         | '0' = Bit is clea      | ared                 | x = Bit is unkr      | nown                 |

| bit 15               | ADRC: ADC1 Conversion Clock Source bit<br>1 = ADC internal RC clock |                                 |                         |                        |                      |                      |                      |

|                      | 0 = Clock deri                                                      | ved from syste                  | m clock                 |                        |                      |                      |                      |

| bit 14-13            | •                                                                   | ted: Read as '0                 |                         |                        |                      |                      |                      |

| bit 12-8             |                                                                     | Auto-Sample T                   | ime bits <sup>(1)</sup> |                        |                      |                      |                      |

|                      | 11111 = <b>31</b> T                                                 | AD                              |                         |                        |                      |                      |                      |

|                      | •                                                                   |                                 |                         |                        |                      |                      |                      |

|                      | •                                                                   |                                 |                         |                        |                      |                      |                      |

|                      | 00001 = 1 TA<br>00000 = 0 TA                                        |                                 |                         |                        |                      |                      |                      |

| bit 7-0              | ADCS<7:0>:                                                          | ADC1 Convers                    | ion Clock Sele          | ct bits <sup>(2)</sup> |                      |                      |                      |

|                      | 11111111 = TP • (ADCS<7:0> + 1) = TP •256 = TAD<br>•                |                                 |                         |                        |                      |                      |                      |

|                      | •                                                                   |                                 |                         |                        |                      |                      |                      |

|                      | 00000010 = -                                                        | TP • (ADCS<7:                   | 0> + 1) = TP •          | 3 = TAD                |                      |                      |                      |

|                      | 0000001 =                                                           | TP • (ADCS<7:<br>TP • (ADCS<7:  | 0> + 1) = TP •          | 2 <b>=</b> Tad         |                      |                      |                      |

|                      | •                                                                   | d if SSRC<2:0><br>if ADRC (AD10 | •                       | ,                      | nd SSRCG (AD         | 1CON1<4>) =          | 0.                   |

#### REGISTER 23-3: AD1CON3: ADC1 CONTROL REGISTER 3

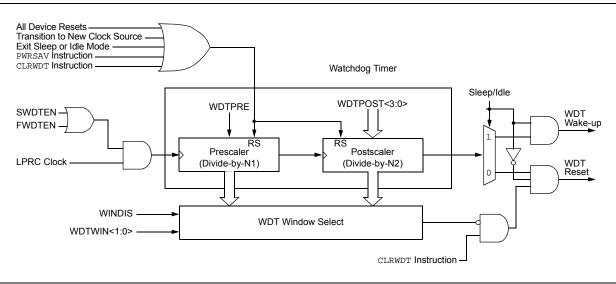

## 27.5 Watchdog Timer (WDT)

For dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices, the WDT is driven by the LPRC oscillator. When the WDT is enabled, the clock source is also enabled.

#### 27.5.1 PRESCALER/POSTSCALER

The nominal WDT clock source from LPRC is 32 kHz. This feeds a prescaler that can be configured for either 5-bit (divide-by-32) or 7-bit (divide-by-128) operation. The prescaler is set by the WDTPRE Configuration bit. With a 32 kHz input, the prescaler yields a WDT Timeout period (TWDT), as shown in Parameter SY12 in Table 30-22.

A variable postscaler divides down the WDT prescaler output and allows for a wide range of time-out periods. The postscaler is controlled by the WDTPOST<3:0> Configuration bits (FWDT<3:0>), which allow the selection of 16 settings, from 1:1 to 1:32,768. Using the prescaler and postscaler, time-out periods ranging from 1 ms to 131 seconds can be achieved.

The WDT, prescaler and postscaler are reset:

- · On any device Reset

- On the completion of a clock switch, whether invoked by software (i.e., setting the OSWEN bit after changing the NOSCx bits) or by hardware (i.e., Fail-Safe Clock Monitor)

- When a PWRSAV instruction is executed (i.e., Sleep or Idle mode is entered)

- When the device exits Sleep or Idle mode to resume normal operation

- By a CLRWDT instruction during normal execution

- Note: The CLRWDT and PWRSAV instructions clear the prescaler and postscaler counts when executed.

## FIGURE 27-2: WDT BLOCK DIAGRAM

# 27.5.2 SLEEP AND IDLE MODES

If the WDT is enabled, it continues to run during Sleep or Idle modes. When the WDT time-out occurs, the device wakes the device and code execution continues from where the PWRSAV instruction was executed. The corresponding SLEEP or IDLE bit (RCON<3,2>) needs to be cleared in software after the device wakes up.

## 27.5.3 ENABLING WDT

The WDT is enabled or disabled by the FWDTEN Configuration bit in the FWDT Configuration register. When the FWDTEN Configuration bit is set, the WDT is always enabled.

The WDT can be optionally controlled in software when the FWDTEN Configuration bit has been programmed to '0'. The WDT is enabled in software by setting the SWDTEN control bit (RCON<5>). The SWDTEN control bit is cleared on any device Reset. The software WDT option allows the user application to enable the WDT for critical code segments and disable the WDT during non-critical segments for maximum power savings.

The WDT flag bit, WDTO (RCON<4>), is not automatically cleared following a WDT time-out. To detect subsequent WDT events, the flag must be cleared in software.

#### 27.5.4 WDT WINDOW

The Watchdog Timer has an optional Windowed mode, enabled by programming the WINDIS bit in the WDT Configuration register (FWDT<6>). In the Windowed mode (WINDIS = 0), the WDT should be cleared based on the settings in the programmable Watchdog Timer Window select bits (WDTWIN<1:0>).

| DC CHARACTERISTICS |                     |      | (unless oth | •          | s: 3.0V to 3.6V<br>≤ Ta ≤ +85°C for Indi<br>≤ Ta ≤ +125°C for Ex |            |

|--------------------|---------------------|------|-------------|------------|------------------------------------------------------------------|------------|

| Parameter<br>No.   | Тур.                | Max. | Units       | Conditions |                                                                  |            |

| Idle Current (III  | dle) <sup>(1)</sup> |      |             |            |                                                                  |            |

| DC40d              | 3                   | 8    | mA          | -40°C      |                                                                  |            |

| DC40a              | 3                   | 8    | mA          | +25°C      | - 3.3V                                                           | 10 MIPS    |

| DC40b              | 3                   | 8    | mA          | +85°C      | 3.3V                                                             | 10 101195  |

| DC40c              | 3                   | 8    | mA          | +125°C     |                                                                  |            |

| DC42d              | 6                   | 12   | mA          | -40°C      | 3.3V                                                             | 20 MIPS    |

| DC42a              | 6                   | 12   | mA          | +25°C      |                                                                  |            |

| DC42b              | 6                   | 12   | mA          | +85°C      |                                                                  |            |

| DC42c              | 6                   | 12   | mA          | +125°C     |                                                                  |            |

| DC44d              | 11                  | 18   | mA          | -40°C      |                                                                  | 40 MIPS    |

| DC44a              | 11                  | 18   | mA          | +25°C      | 3.3V                                                             |            |

| DC44b              | 11                  | 18   | mA          | +85°C      | 5.5 V                                                            | 40 10117 3 |

| DC44c              | 11                  | 18   | mA          | +125°C     |                                                                  |            |

| DC45d              | 17                  | 27   | mA          | -40°C      |                                                                  |            |

| DC45a              | 17                  | 27   | mA          | +25°C      | - 3.3V                                                           | 60 MIPS    |

| DC45b              | 17                  | 27   | mA          | +85°C      | 5.30                                                             | 00 1011-5  |

| DC45c              | 17                  | 27   | mA          | +125°C     |                                                                  |            |

| DC46d              | 20                  | 35   | mA          | -40°C      |                                                                  |            |

| DC46a              | 20                  | 35   | mA          | +25°C      | 3.3V                                                             | 70 MIPS    |

| DC46b              | 20                  | 35   | mA          | +85°C      |                                                                  |            |

#### TABLE 30-7: DC CHARACTERISTICS: IDLE CURRENT (lidle)

**Note 1:** Base Idle current (IIDLE) is measured as follows:

• CPU core is off, oscillator is configured in EC mode and external clock is active; OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)

- · CLKO is configured as an I/O input pin in the Configuration Word

- All I/O pins are configured as inputs and pulled to Vss

- $\overline{\text{MCLR}}$  = VDD, WDT and FSCM are disabled

- No peripheral modules are operating; however, every peripheral is being clocked (all PMDx bits are zeroed)

- The NVMSIDL bit (NVMCON<12>) = 1 (i.e., Flash regulator is set to standby while the device is in Idle mode)

- The VREGSF bit (RCON<11>) = 0 (i.e., Flash regulator is set to standby while the device is in Sleep mode)

- JTAG is disabled

# Revision E (April 2012)

This revision includes typographical and formatting changes throughout the data sheet text.

All other major changes are referenced by their respective section in Table A-3.

| TABLE A-4: | MAJOR SECTION UPDATES |

|------------|-----------------------|

|------------|-----------------------|

| Section Name                                   | Update Description                                                                              |

|------------------------------------------------|-------------------------------------------------------------------------------------------------|

| "16-bit Microcontrollers<br>and Digital Signal | The following 512-Kbyte devices were added to the General Purpose Families table (see Table 1): |

| Controllers (up to                             | <ul> <li>PIC24EP512GP202</li> </ul>                                                             |

| 512-Kbyte Flash and                            | • PIC24EP512GP204                                                                               |

| 48-Kbyte SRAM) with High-                      | • PIC24EP512GP206                                                                               |

| Speed PWM, Op amps, and Advanced Analog"       | • dsPIC33EP512GP502                                                                             |

| Advanced Analog                                | • dsPIC33EP512GP504                                                                             |

|                                                | • dsPIC33EP512GP506                                                                             |

|                                                | The following 512-Kbyte devices were added to the Motor Control Families table (see Table 2):   |

|                                                | • PIC24EP512MC202                                                                               |

|                                                | • PIC24EP512MC204                                                                               |

|                                                | • PIC24EP512MC206                                                                               |

|                                                | • dsPIC33EP512MC202                                                                             |

|                                                | • dsPIC33EP512MC204                                                                             |

|                                                | • dsPIC33EP512MC206                                                                             |

|                                                | • dsPIC33EP512MC502                                                                             |

|                                                | • dsPIC33EP512MC504                                                                             |

|                                                | • dsPIC33EP512MC506                                                                             |

|                                                | Certain Pin Diagrams were updated to include the new 512-Kbyte devices.                         |

| Section 4.0 "Memory                            | Added a Program Memory Map for the new 512-Kbyte devices (see Figure 4-4).                      |

| Organization"                                  | Added a Data Memory Map for the new dsPIC 512-Kbyte devices (see Figure 4-11).                  |

|                                                | Added a Data Memory Map for the new PIC24 512-Kbyte devices (see Figure 4-16).                  |

| Section 7.0 "Interrupt<br>Controller"          | Updated the VECNUM bits in the INTTREG register (see Register 7-7).                             |

| Section 11.0 "I/O Ports"                       | Added tip 6 to Section 11.5 "I/O Helpful Tips".                                                 |

| Section 27.0 "Special<br>Features"             | The following modifications were made to the Configuration Byte Register Map (see Table 27-1):  |

|                                                | <ul> <li>Added the column Device Memory Size (Kbytes)</li> </ul>                                |

|                                                | Removed Notes 1 through 4                                                                       |

|                                                | Added addresses for the new 512-Kbyte devices                                                   |

| Section 30.0 "Electrical                       | Updated the Minimum value for Parameter DC10 (see Table 30-4).                                  |

| Characteristics"                               | Added Power-Down Current (Ipd) parameters for the new 512-Kbyte devices (see Table 30-8).       |

|                                                | Updated the Minimum value for Parameter CM34 (see Table 30-53).                                 |

|                                                | Updated the Minimum and Maximum values and the Conditions for paramteer SY12 (see Table 30-22). |

# THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

# **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- · Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support