Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 70 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 35                                                                             |

| Program Memory Size        | 512KB (170K x 24)                                                              |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 24K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 9x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

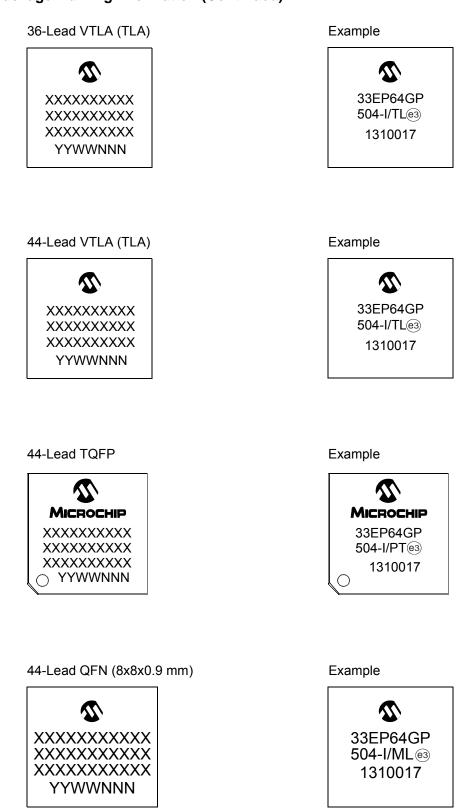

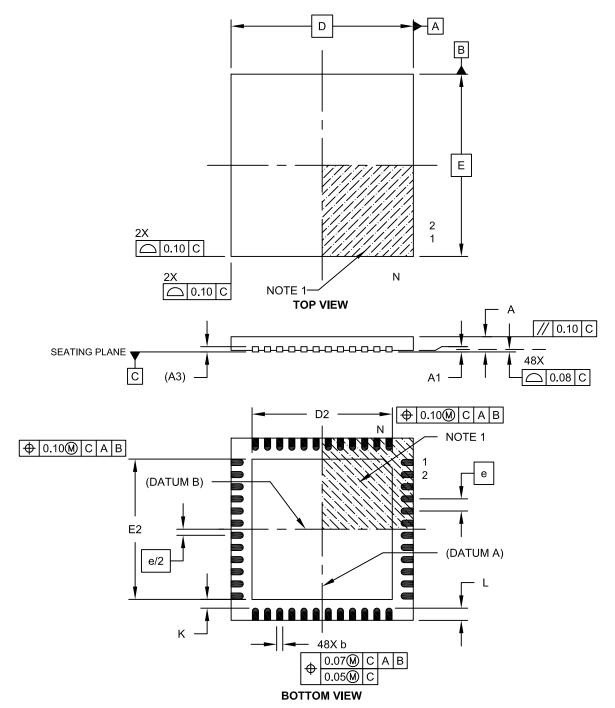

| Package / Case             | 44-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 44-QFN (8x8)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep512gp204-i-ml |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name <sup>(4)</sup>       | Pin<br>Type | Buffer<br>Type | PPS     | Description                                                                                     |

|-------------------------------|-------------|----------------|---------|-------------------------------------------------------------------------------------------------|

| C1IN1-                        | I           | Analog         | No      | Op Amp/Comparator 1 Negative Input 1.                                                           |

| C1IN2-                        | I           | Analog         | No      | Comparator 1 Negative Input 2.                                                                  |

| C1IN1+                        | I           | Analog         | No      | Op Amp/Comparator 1 Positive Input 1.                                                           |

| OA1OUT                        | 0           | Analog         | No      | Op Amp 1 output.                                                                                |

| C1OUT                         | 0           | —              | Yes     | Comparator 1 output.                                                                            |

| C2IN1-                        | I           | Analog         | No      | Op Amp/Comparator 2 Negative Input 1.                                                           |

| C2IN2-                        | I           | Analog         | No      | Comparator 2 Negative Input 2.                                                                  |

| C2IN1+                        | I           | Analog         | No      | Op Amp/Comparator 2 Positive Input 1.                                                           |

| OA2OUT                        | 0           | Analog         | No      | Op Amp 2 output.                                                                                |

| C2OUT                         | 0           |                | Yes     | Comparator 2 output.                                                                            |

| C3IN1-                        | I           | Analog         | No      | Op Amp/Comparator 3 Negative Input 1.                                                           |

| C3IN2-                        | I           | Analog         | No      | Comparator 3 Negative Input 2.                                                                  |

| C3IN1+                        | I           | Analog         | No      | Op Amp/Comparator 3 Positive Input 1.                                                           |

| OA3OUT                        | 0           | Analog         | No      | Op Amp 3 output.                                                                                |

| C3OUT                         | 0           |                | Yes     | Comparator 3 output.                                                                            |

| C4IN1-                        | I.          | Analog         | No      | Comparator 4 Negative Input 1.                                                                  |

| C4IN1+                        | I.          | Analog         | No      | Comparator 4 Positive Input 1.                                                                  |

| C4OUT                         | 0           |                | Yes     | Comparator 4 output.                                                                            |

| CVREF10                       | 0           | Analog         | No      | Op amp/comparator voltage reference output.                                                     |

| CVREF20                       | 0           | Analog         | No      | Op amp/comparator voltage reference divided by 2 output.                                        |

| PGED1                         | I/O         | ST             | No      | Data I/O pin for Programming/Debugging Communication Channel 1.                                 |

| PGEC1                         | I           | ST             | No      | Clock input pin for Programming/Debugging Communication Channel 1.                              |

| PGED2                         | I/O         | ST             | No      | Data I/O pin for Programming/Debugging Communication Channel 2.                                 |

| PGEC2                         | I           | ST             | No      | Clock input pin for Programming/Debugging Communication Channel 2.                              |

| PGED3                         | I/O         | ST             | No      | Data I/O pin for Programming/Debugging Communication Channel 3.                                 |

| PGEC3                         | I           | ST             | No      | Clock input pin for Programming/Debugging Communication Channel 3.                              |

| MCLR                          | I/P         | ST             | No      | Master Clear (Reset) input. This pin is an active-low Reset to the device.                      |

| AVDD                          | Р           | Р              | No      | Positive supply for analog modules. This pin must be connected at all times.                    |

| AVss                          | Р           | Р              | No      | Ground reference for analog modules. This pin must be connected at all times.                   |

| Vdd                           | Р           |                | No      | Positive supply for peripheral logic and I/O pins.                                              |

| VCAP                          | Р           |                | No      | CPU logic filter capacitor connection.                                                          |

| Vss                           | Р           |                | No      | Ground reference for logic and I/O pins.                                                        |

| VREF+                         | 1           | Analog         | No      | Analog voltage reference (high) input.                                                          |

| VREF-                         | Ι           | Analog         | No      | Analog voltage reference (low) input.                                                           |

| Legend: CMOS = C<br>ST = Schn | nitt Trigg  | jer input v    | with CI | or output     Analog = Analog input     P = Power       MOS levels     O = Output     I = Input |

Note 1: This pin is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This pin is available on dsPIC33EPXXXGP/MC50X devices only.

PPS = Peripheral Pin Select

3: This is the default Fault on Reset for dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices. See Section 16.0 "High-Speed PWM Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)" for more information.

TTL = TTL input buffer

4: Not all pins are available in all packages variants. See the "Pin Diagrams" section for pin availability.

**5:** There is an internal pull-up resistor connected to the TMS pin when the JTAG interface is active. See the JTAGEN bit field in Table 27-2.

# TABLE 4-19: SPI1 AND SPI2 REGISTER MAP

| SFR Name | Addr. | Bit 15 | Bit 14                                        | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8        | Bit 7       | Bit 6      | Bit 5  | Bit 4 | Bit 3      | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|----------|-------|--------|-----------------------------------------------|---------|--------|--------|--------|------------|--------------|-------------|------------|--------|-------|------------|-------|--------|--------|---------------|

| SPI1STAT | 0240  | SPIEN  | _                                             | SPISIDL | _      | _      | 5      | SPIBEC<2:0 | >            | SRMPT       | SPIROV     | SRXMPT |       | SISEL<2:0> |       | SPITBF | SPIRBF | 0000          |

| SPI1CON1 | 0242  | _      | _                                             | _       | DISSCK | DISSDO | MODE16 | SMP        | CKE          | SSEN        | CKP        | MSTEN  |       | SPRE<2:0>  |       | PPRE   | <1:0>  | 0000          |

| SPI1CON2 | 0244  | FRMEN  | SPIFSD                                        | FRMPOL  | _      | _      | -      | _          | _            | —           | _          | _      | _     | _          | _     | FRMDLY | SPIBEN | 0000          |

| SPI1BUF  | 0248  |        |                                               |         |        |        |        | SPI1 Tra   | insmit and R | eceive Buff | er Registe | r      |       |            |       |        |        | 0000          |

| SPI2STAT | 0260  | SPIEN  | _                                             | SPISIDL | _      | _      | ŝ      | SPIBEC<2:0 | >            | SRMPT       | SPIROV     | SRXMPT |       | SISEL<2:0> |       | SPITBF | SPIRBF | 0000          |

| SPI2CON1 | 0262  | _      | _                                             | _       | DISSCK | DISSDO | MODE16 | SMP        | CKE          | SSEN        | CKP        | MSTEN  |       | SPRE<2:0>  |       | PPRE   | <1:0>  | 0000          |

| SPI2CON2 | 0264  | FRMEN  | SPIFSD                                        | FRMPOL  | _      | _      |        | _          | _            | —           | _          | _      | _     | _          | _     | FRMDLY | SPIBEN | 0000          |

| SPI2BUF  | 0268  |        | SPI2 Transmit and Receive Buffer Register 000 |         |        |        |        |            |              | 0000        |            |        |       |            |       |        |        |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| IABLE 4-2  | 1: t  | ECANTI  | REGIST    |         | WHEN    |         | TOTRE      | 1<0>) =   | 0 OR . | L FOR asi | PIC33E    | PXXXIV | IC/GP5  |           | ICES O   | NLY      |        |               |

|------------|-------|---------|-----------|---------|---------|---------|------------|-----------|--------|-----------|-----------|--------|---------|-----------|----------|----------|--------|---------------|

| File Name  | Addr. | Bit 15  | Bit 14    | Bit 13  | Bit 12  | Bit 11  | Bit 10     | Bit 9     | Bit 8  | Bit 7     | Bit 6     | Bit 5  | Bit 4   | Bit 3     | Bit 2    | Bit 1    | Bit 0  | All<br>Resets |

| C1CTRL1    | 0400  | _       | —         | CSIDL   | ABAT    | CANCKS  | R          | EQOP<2:0  | >      | OPM       | /IODE<2:0 | >      | —       | CANCAP    | —        | —        | WIN    | 0480          |

| C1CTRL2    | 0402  | _       | _         | —       | _       | _       | _          | —         | _      | —         | _         | _      |         | D         | NCNT<4:0 | >        |        | 0000          |

| C1VEC      | 0404  | _       | —         | —       |         | F       | ILHIT<4:0> |           |        | —         |           |        | •       | ICODE<6:0 | >        |          |        | 0040          |

| C1FCTRL    | 0406  | C       | DMABS<2:0 | >       |         | _       | —          | —         | _      | _         | _         | _      |         |           | FSA<4:0> |          |        | 0000          |

| C1FIFO     | 0408  |         | —         |         |         | FBP<    | 5:0>       |           |        | _         | _         |        |         | FNRB      | <5:0>    |          |        | 0000          |

| C1INTF     | 040A  |         | —         | TXBO    | TXBP    | RXBP    | TXWAR      | RXWAR     | EWARN  | IVRIF     | WAKIF     | ERRIF  | —       | FIFOIF    | RBOVIF   | RBIF     | TBIF   | 0000          |

| C1INTE     | 040C  |         | —         | —       |         | _       | —          | —         | —      | IVRIE     | WAKIE     | ERRIE  | —       | FIFOIE    | RBOVIE   | RBIE     | TBIE   | 0000          |

| C1EC       | 040E  |         |           |         | TERRCN  | T<7:0>  |            |           |        |           |           |        | RERRCN  | NT<7:0>   |          |          |        | 0000          |

| C1CFG1     | 0410  | _       | _         | _       | _       | _       | _          | _         | _      | SJW<1     | :0>       |        |         | BRP       | <5:0>    |          |        | 0000          |

| C1CFG2     | 0412  | _       | WAKFIL    | _       | _       | _       | SI         | =G2PH<2:( | )>     | SEG2PHTS  | SAM       | S      | EG1PH<2 | :0>       | Р        | RSEG<2:0 | >      | 0000          |

| C1FEN1     | 0414  | FLTEN15 | FLTEN14   | FLTEN13 | FLTEN12 | FLTEN11 | FLTEN10    | FLTEN9    | FLTEN8 | FLTEN7    | FLTEN6    | FLTEN5 | FLTEN4  | FLTEN3    | FLTEN2   | FLTEN1   | FLTEN0 | FFFF          |

| C1FMSKSEL1 | 0418  | F7MSł   | <<1:0>    | F6MSł   | <<1:0>  | F5MS    | K<1:0>     | F4MS      | K<1:0> | F3MSK<    | <1:0>     | F2MS   | K<1:0>  | F1MSH     | <<1:0>   | F0MS     | <<1:0> | 0000          |

| C1FMSKSEL2 | 041A  | F15MS   | K<1:0>    | F14MS   | K<1:0>  | F13MS   | K<1:0>     | F12MS     | K<1:0> | F11MSK    | <1:0>     | F10MS  | K<1:0>  | F9MSk     | <<1:0>   | F8MSI    | <<1:0> | 0000          |

#### TABLE 4-21: ECAN1 REGISTER MAP WHEN WIN (C1CTRL1<0>) = 0 OR 1 FOR dsPIC33EPXXXMC/GP50X DEVICES ONLY

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-22: ECAN1 REGISTER MAP WHEN WIN (C1CTRL1<0>) = 0 FOR dsPIC33EPXXXMC/GP50X DEVICES ONLY

| File Name | Addr          | Bit 15  | Bit 14                     | Bit 13  | Bit 12  | Bit 11  | Bit 10                                                                    | Bit 9                                                                       | Bit 8         | Bit 7        | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|-----------|---------------|---------|----------------------------|---------|---------|---------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------|---------------|--------------|---------|---------|---------|---------|---------|---------|---------|---------------|

|           | 0400-<br>041E |         |                            |         |         |         |                                                                           | S                                                                           | ee definition | when WIN     | = x     |         |         |         |         |         |         |               |

| C1RXFUL1  | 0420          | RXFUL15 | RXFUL14                    | RXFUL13 | RXFUL12 | RXFUL11 | RXFUL10                                                                   | RXFUL9                                                                      | RXFUL8        | RXFUL7       | RXFUL6  | RXFUL5  | RXFUL4  | RXFUL3  | RXFUL2  | RXFUL1  | RXFUL0  | 0000          |

| C1RXFUL2  | 0422          | RXFUL31 | RXFUL30                    | RXFUL29 | RXFUL28 | RXFUL27 | RXFUL26                                                                   | RXFUL25                                                                     | RXFUL24       | RXFUL23      | RXFUL22 | RXFUL21 | RXFUL20 | RXFUL19 | RXFUL18 | RXFUL17 | RXFUL16 | 0000          |

| C1RXOVF1  | 0428          | RXOVF15 | RXOVF14                    | RXOVF13 | RXOVF12 | RXOVF11 | RXOVF10                                                                   | RXOVF9                                                                      | RXOVF8        | RXOVF7       | RXOVF6  | RXOVF5  | RXOVF4  | RXOVF3  | RXOVF2  | RXOVF1  | RXOVF0  | 0000          |

| C1RXOVF2  | 042A          | RXOVF31 | RXOVF30                    | RXOVF29 | RXOVF28 | RXOVF27 | RXOVF26                                                                   | OVF26 RXOVF25 RXOVF24 RXOVF23 RXOVF22 RXOVF21 RXOVF20 RXOVF19 RXOVF18 RXOVF |               |              |         |         | RXOVF17 | RXOVF16 | 0000    |         |         |               |

| C1TR01CON | 0430          | TXEN1   | TXABT1                     | TXLARB1 | TXERR1  | TXREQ1  | RTREN1                                                                    | TX1PF                                                                       | RI<1:0>       | TXEN0        | TXABAT0 | TXLARB0 | TXERR0  | TXREQ0  | RTREN0  | TX0PF   | RI<1:0> | 0000          |

| C1TR23CON | 0432          | TXEN3   | TXABT3                     | TXLARB3 | TXERR3  | TXREQ3  | RTREN3                                                                    | TX3PF                                                                       | RI<1:0>       | TXEN2        | TXABAT2 | TXLARB2 | TXERR2  | TXREQ2  | RTREN2  | TX2PF   | RI<1:0> | 0000          |

| C1TR45CON | 0434          | TXEN5   | TXABT5                     | TXLARB5 | TXERR5  | TXREQ5  | RTREN5                                                                    | RTREN5 TX5PRI<1:0> TXEN4 TXABAT4 TXLARB4 TXERR4 TXREQ4 RTREN4 TX4PRI<1:0>   |               |              |         |         |         |         | RI<1:0> | 0000    |         |               |

| C1TR67CON | 0436          | TXEN7   | TXABT7                     | TXLARB7 | TXERR7  | TXREQ7  | RTREN7 TX7PRI<1:0> TXEN6 TXABAT6 TXLARB6 TXERR6 TXREQ6 RTREN6 TX6PRI<1:0> |                                                                             |               |              |         |         |         | xxxx    |         |         |         |               |

| C1RXD     | 0440          |         |                            |         |         |         |                                                                           | E                                                                           | CAN1 Rece     | eive Data Wo | ord     |         |         |         |         |         |         | xxxx          |

| C1TXD     | 0442          |         | ECAN1 Transmit Data Word 2 |         |         |         |                                                                           |                                                                             |               |              |         | xxxx    |         |         |         |         |         |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# 5.2 RTSP Operation

RTSP allows the user application to erase a single page of memory and to program two instruction words at a time. See the General Purpose and Motor Control Family tables (Table 1 and Table 2, respectively) for the page sizes of each device.

For more information on erasing and programming Flash memory, refer to "Flash Programming" (DS70609) in the "dsPIC33/PIC24 Family Reference Manual".

## 5.3 **Programming Operations**

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. The processor stalls (waits) until the programming operation is finished.

For erase and program times, refer to Parameters D137a and D137b (Page Erase Time), and D138a and D138b (Word Write Cycle Time) in Table 30-14 in **Section 30.0 "Electrical Characteristics"**.

Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

#### 5.3.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

Programmers can program two adjacent words (24 bits x 2) of program Flash memory at a time on every other word address boundary (0x000002, 0x000006, 0x00000A, etc.). To do this, it is necessary to erase the page that contains the desired address of the location the user wants to change.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user application must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS.

Refer to **Flash Programming**" (DS70609) in the "*dsPIC33/PIC24 Family Reference Manual*" for details and codes examples on programming using RTSP.

## 5.4 Flash Memory Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter |

|-------|--------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                            |

|       | http://www.microchip.com/wwwproducts/                                                |

|       | Devices.aspx?dDocName=en555464                                                       |

#### 5.4.1 KEY RESOURCES

- "Flash Programming" (DS70609) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

# 5.5 Control Registers

Four SFRs are used to erase and write the program Flash memory: NVMCON, NVMKEY, NVMADRH and NVMADRL.

The NVMCON register (Register 5-1) enables and initiates Flash memory erase and write operations.

NVMKEY (Register 5-4) is a write-only register that is used for write protection. To start a programming or erase sequence, the user application must consecutively write 0x55 and 0xAA to the NVMKEY register.

There are two NVM Address registers: NVMADRH and NVMADRL. These two registers, when concatenated, form the 24-bit Effective Address (EA) of the selected word for programming operations or the selected page for erase operations.

The NVMADRH register is used to hold the upper 8 bits of the EA, while the NVMADRL register is used to hold the lower 16 bits of the EA.

# **10.0 POWER-SAVING FEATURES**

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Watchdog Timer and Power-Saving Modes" (DS70615) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices provide the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of peripherals being clocked constitutes lower consumed power.

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices can manage power consumption in four ways:

- Clock Frequency

- Instruction-Based Sleep and Idle modes

- Software-Controlled Doze mode

- · Selective Peripheral Control in Software

Combinations of these methods can be used to selectively tailor an application's power consumption while still maintaining critical application features, such as timing-sensitive communications.

## EXAMPLE 10-1: PWRSAV INSTRUCTION SYNTAX

| PWRSAV | #SLEEP_MODE | ; | Put | the | device | into | Sleep mode |  |

|--------|-------------|---|-----|-----|--------|------|------------|--|

| PWRSAV | #IDLE_MODE  | ; | Put | the | device | into | Idle mode  |  |

# 10.1 Clock Frequency and Clock Switching

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices allow a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or highprecision oscillators by simply changing the NOSCx bits (OSCCON<10:8>). The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in **Section 9.0 "Oscillator Configuration"**.

# 10.2 Instruction-Based Power-Saving Modes

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices have two special power-saving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution. Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. The assembler syntax of the PWRSAV instruction is shown in Example 10-1.

**Note:** SLEEP\_MODE and IDLE\_MODE are constants defined in the assembler include file for the selected device.

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to "wake-up".

| U-0                 | U-0                          | U-0              | R/W-0                                 | R/W-0                | R/W-0                | R/W-0                | R/W-0                |

|---------------------|------------------------------|------------------|---------------------------------------|----------------------|----------------------|----------------------|----------------------|

|                     | —                            | _                | DISSCK                                | DISSDO               | MODE16               | SMP                  | CKE <sup>(1)</sup>   |

| bit 15              |                              | •                |                                       | •                    | •                    | •                    | bit                  |

| R/W-0               | R/W-0                        | R/W-0            | R/W-0                                 | R/W-0                | R/W-0                | R/W-0                | R/W-0                |

| SSEN <sup>(2)</sup> | CKP                          | MSTEN            | SPRE2 <sup>(3)</sup>                  | SPRE1 <sup>(3)</sup> | SPRE0 <sup>(3)</sup> | PPRE1 <sup>(3)</sup> | PPRE0 <sup>(3)</sup> |

| bit 7               | CKF                          | WIGTEN           | SFREZ 7                               | SFREI?               | SFREU 7              | FFREN                | bit                  |

|                     |                              |                  |                                       |                      |                      |                      |                      |

| Legend:             |                              |                  |                                       |                      |                      |                      |                      |

| R = Readabl         | le bit                       | W = Writable     | bit                                   | U = Unimpler         | mented bit, read     | d as '0'             |                      |

| -n = Value at       | t POR                        | '1' = Bit is se  | t                                     | '0' = Bit is cle     | ared                 | x = Bit is unkr      | nown                 |

|                     |                              |                  |                                       |                      |                      |                      |                      |

| bit 15-13           | Unimplemen                   | ted: Read as     | 0'                                    |                      |                      |                      |                      |

| bit 12              |                              |                  | bit (SPIx Mas                         | -                    | ()                   |                      |                      |

|                     |                              | PIx clock is di  | sabled, pin fun                       | ctions as I/O        |                      |                      |                      |

| oit 11              |                              | able SDOx Pir    |                                       |                      |                      |                      |                      |

|                     |                              |                  | / the module; p                       | oin functions as     | s I/O                |                      |                      |

|                     |                              | is controlled b  |                                       |                      |                      |                      |                      |

| bit 10              | MODE16: Wo                   | ord/Byte Comn    | nunication Sele                       | ect bit              |                      |                      |                      |

|                     |                              | ication is word  | · · /                                 |                      |                      |                      |                      |

|                     |                              | ication is byte- | . ,                                   |                      |                      |                      |                      |

| bit 9               |                              | ata Input Sam    | ole Phase bit                         |                      |                      |                      |                      |

|                     | Master mode                  | -                | end of data o                         | utout time           |                      |                      |                      |

|                     |                              |                  | middle of data                        |                      |                      |                      |                      |

|                     | Slave mode:                  |                  |                                       |                      |                      |                      |                      |

|                     |                              |                  | SPIx is used i                        | n Slave mode.        |                      |                      |                      |

| bit 8               |                              | lock Edge Sele   |                                       |                      |                      |                      |                      |

|                     |                              |                  |                                       |                      |                      | lle clock state (r   |                      |

| bit 7               |                              |                  | bit (Slave mo                         |                      |                      | ve clock state (i    |                      |

|                     |                              | sused for Slav   |                                       |                      |                      |                      |                      |

|                     |                              |                  |                                       | is controlled b      | by port function     |                      |                      |

| bit 6               | CKP: Clock F                 | Polarity Select  | bit                                   |                      |                      |                      |                      |

|                     |                              |                  | nigh level; activ<br>ow level; active |                      |                      |                      |                      |

| bit 5               | MSTEN: Mas                   | ter Mode Enat    | ole bit                               |                      |                      |                      |                      |

|                     | 1 = Master m<br>0 = Slave mo |                  |                                       |                      |                      |                      |                      |

| Note 1: T           | he CKE bit is not            | used in Frame    | d SPI modes. I                        | Program this bi      | it to '0' for Fram   | ed SPI modes (       | FRMEN = 1            |

|                     | his bit must be cl           |                  |                                       |                      |                      |                      |                      |

| <b>0</b>            |                              |                  |                                       |                      |                      |                      |                      |

# REGISTER 18-2: SPIXCON1: SPIX CONTROL REGISTER 1

- **3:** Do not set both primary and secondary prescalers to the value of 1:1.

# 20.3 UARTx Control Registers

#### REGISTER 20-1: UXMODE: UARTX MODE REGISTER

| R/W-0               | U-0                                                                                                                                                                                                        | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R/W-0                          | R/W-0                          | U-0             | R/W-0            | R/W-0          |  |  |  |  |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--------------------------------|-----------------|------------------|----------------|--|--|--|--|

| UARTEN <sup>(</sup> | <sup>1)</sup>                                                                                                                                                                                              | USIDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | IREN <sup>(2)</sup>            | RTSMD                          | _               | UEN1             | UEN0           |  |  |  |  |

| bit 15              |                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                | •                              |                 |                  | bit 8          |  |  |  |  |

|                     |                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>D</b> AMA                   | <b>D</b> 444 0                 | <b>D</b> 444 0  | <b>D</b> 444.0   | <b>D</b> 444 0 |  |  |  |  |

| R/W-0, H0           |                                                                                                                                                                                                            | R/W-0, HC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | R/W-0                          | R/W-0                          | R/W-0           | R/W-0            | R/W-0          |  |  |  |  |

| WAKE                | LPBACK                                                                                                                                                                                                     | ABAUD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | URXINV                         | BRGH                           | PDSEL1          | PDSEL0           | STSEL          |  |  |  |  |

| bit 7               |                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                |                                |                 |                  | bit            |  |  |  |  |

| Legend:             |                                                                                                                                                                                                            | HC = Hardwar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | e Clearable b                  | it                             |                 |                  |                |  |  |  |  |

| R = Reada           | ble bit                                                                                                                                                                                                    | W = Writable b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | oit                            | U = Unimplem                   | ented bit, read | as '0'           |                |  |  |  |  |

| -n = Value          | at POR                                                                                                                                                                                                     | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                | '0' = Bit is clea              | ared            | x = Bit is unkn  | iown           |  |  |  |  |

| bit 15              | 1 = UARTx is                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                |                                |                 |                  |                |  |  |  |  |

| bit 14              | Unimplemen                                                                                                                                                                                                 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                |                                |                 |                  |                |  |  |  |  |

| bit 13              | USIDL: UAR                                                                                                                                                                                                 | USIDL: UARTx Stop in Idle Mode bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                |                                |                 |                  |                |  |  |  |  |

|                     |                                                                                                                                                                                                            | <ul> <li>1 = Discontinues module operation when device enters Idle mode</li> <li>0 = Continues module operation in Idle mode</li> </ul>                                                                                                                                                                                                                                                                                                                                                               |                                |                                |                 |                  |                |  |  |  |  |

| bit 12              | 1 = IrDA enc                                                                                                                                                                                               | <ul> <li>IREN: IrDA<sup>®</sup> Encoder and Decoder Enable bit<sup>(2)</sup></li> <li>1 = IrDA encoder and decoder are enabled</li> <li>0 = IrDA encoder and decoder are disabled</li> </ul>                                                                                                                                                                                                                                                                                                          |                                |                                |                 |                  |                |  |  |  |  |

| bit 11              | $1 = \overline{\text{UxRTS}} p$                                                                                                                                                                            | le Selection for<br>bin is in Simplex<br>bin is in Flow Co                                                                                                                                                                                                                                                                                                                                                                                                                                            | mode                           | t                              |                 |                  |                |  |  |  |  |

| bit 10              | Unimplemen                                                                                                                                                                                                 | ted: Read as '0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ,                              |                                |                 |                  |                |  |  |  |  |

| bit 9-8             | 11 = UxTX, U<br>10 = UxTX, U<br>01 = UxTX, U<br>00 = UxTX a                                                                                                                                                | <ul> <li>UEN&lt;1:0&gt;: UARTx Pin Enable bits</li> <li>11 = UxTX, UxRX and BCLKx pins are enabled and used; UxCTS pin is controlled by PORT latches<sup>(3)</sup></li> <li>10 = UxTX, UxRX, UxCTS and UxRTS pins are enabled and used<sup>(4)</sup></li> <li>01 = UxTX, UxRX and UxRTS pins are enabled and used; UxCTS pin is controlled by PORT latches<sup>(4)</sup></li> <li>00 = UxTX and UxRTS pins are enabled and used; UxCTS and UxRTS/BCLKx pins are controlled by PORT latches</li> </ul> |                                |                                |                 |                  |                |  |  |  |  |

| bit 7               | WAKE: Wake                                                                                                                                                                                                 | e-up on Start bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Detect During                  | Sleep Mode Ei                  | nable bit       |                  |                |  |  |  |  |

|                     | <ul> <li>1 = UARTx continues to sample the UxRX pin; interrupt is generated on the falling edge; bit is cleared<br/>in hardware on the following rising edge</li> <li>0 = No wake-up is enabled</li> </ul> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                |                                |                 |                  |                |  |  |  |  |

| bit 6               | 1 = Enables                                                                                                                                                                                                | ARTx Loopback<br>Loopback mode<br>k mode is disab                                                                                                                                                                                                                                                                                                                                                                                                                                                     | :                              | bit                            |                 |                  |                |  |  |  |  |

| 2:                  | Refer to the " <b>UAI</b><br>enabling the UAR<br>This feature is or                                                                                                                                        | Tx module for realized for realized available for the second second second second second second second second s                                                                                                                                                                                                                                                                                                                                                                                       | eceive or trans<br>the 16x BRG | mit operation.<br>mode (BRGH = | -               | ce Manual" for i | nformation or  |  |  |  |  |

|                     | This feature is or                                                                                                                                                                                         | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -                              | -                              |                 |                  |                |  |  |  |  |

| A-                  | This fastura is ar                                                                                                                                                                                         | ny available on l                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | al nin dovicos                 |                                |                 |                  |                |  |  |  |  |

4: This feature is only available on 64-pin devices.

### REGISTER 21-6: CxINTF: ECANx INTERRUPT FLAG REGISTER (CONTINUED)

- bit 1 **RBIF:** RX Buffer Interrupt Flag bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

- bit 0 **TBIF:** TX Buffer Interrupt Flag bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

# REGISTER 21-13: CxBUFPNT2: ECANx FILTER 4-7 BUFFER POINTER REGISTER 2

| R/W-0            |       |                  |       |                     |                |                 |       |

|------------------|-------|------------------|-------|---------------------|----------------|-----------------|-------|

|                  | R/W-0 | R/W-0            | R/W-0 | R/W-0               | R/W-0          | R/W-0           | R/W-0 |

|                  | F7BF  | °<3:0>           |       |                     | F6BF           | P<3:0>          |       |

| bit 15           |       |                  |       |                     |                |                 | bit 8 |

| R/W-0            | R/W-0 | R/W-0            | R/W-0 | R/W-0               | R/W-0          | R/W-0           | R/W-0 |

|                  | F5BF  | °<3:0>           |       |                     | F4BF           | P<3:0>          |       |

| bit 7            |       |                  |       |                     |                |                 | bit 0 |

| Legend:          |       |                  |       |                     |                |                 |       |

| R = Readable bi  | t     | W = Writable     | bit   | U = Unimplemer      | nted bit, read | d as '0'        |       |

| -n = Value at PO | R     | '1' = Bit is set |       | '0' = Bit is cleare | d              | x = Bit is unkr | nown  |

|          | 1110 = Filter hits received in RX Buffer 14                              |

|----------|--------------------------------------------------------------------------|

|          |                                                                          |

|          | •                                                                        |

|          | 0001 = Filter hits received in RX Buffer 1                               |

|          | 0000 = Filter hits received in RX Buffer 0                               |

| bit 11-8 | F6BP<3:0>: RX Buffer Mask for Filter 6 bits (same values as bits<15:12>) |

| bit 7-4  | F5BP<3:0>: RX Buffer Mask for Filter 5 bits (same values as bits<15:12>) |

| bit 3-0  | F4BP<3:0>: RX Buffer Mask for Filter 4 bits (same values as bits<15:12>) |

### REGISTER 21-14: CxBUFPNT3: ECANx FILTER 8-11 BUFFER POINTER REGISTER 3

| R/W-0         | R/W-0                                                                                                                                                              | R/W-0            | R/W-0            | R/W-0                                   | R/W-0           | R/W-0    | R/W-0 |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|-----------------------------------------|-----------------|----------|-------|

|               | F11BF                                                                                                                                                              | P<3:0>           |                  |                                         | F10B            | SP<3:0>  |       |

| bit 15        |                                                                                                                                                                    |                  |                  |                                         |                 |          | bit 8 |

| R/W-0         | R/W-0                                                                                                                                                              | R/W-0            | R/W-0            | R/W-0                                   | R/W-0           | R/W-0    | R/W-0 |

|               | F9BP                                                                                                                                                               | <3:0>            |                  |                                         | F8B             | P<3:0>   |       |

| bit 7         |                                                                                                                                                                    |                  |                  |                                         |                 |          | bit 0 |

| Legend:       |                                                                                                                                                                    |                  |                  |                                         |                 |          |       |

| R = Readabl   | le bit                                                                                                                                                             | W = Writable     | bit              | U = Unimplen                            | nented bit, rea | d as '0' |       |

| -n = Value at | t POR                                                                                                                                                              | '1' = Bit is set |                  | '0' = Bit is cleared x = Bit is unknown |                 |          |       |

| bit 15-12     | <pre>bit 15-12 F11BP&lt;3:0&gt;: RX Buffer Mask for Filter 11 bits 1111 = Filter hits received in RX FIFO buffer 1110 = Filter hits received in RX Buffer 14</pre> |                  |                  |                                         |                 |          |       |

| bit 11-8      | F10BP<3:0>                                                                                                                                                         | : RX Buffer Ma   | sk for Filter 1  | 0 bits (same val                        | ues as bits<1   | 5:12>)   |       |

| bit 7-4       | -4 <b>F9BP&lt;3:0&gt;:</b> RX Buffer Mask for Filter 9 bits (same values as bits<15:12>)                                                                           |                  |                  |                                         |                 |          |       |

| bit 3-0       | F8BP<3:0>:                                                                                                                                                         | RX Buffer Mas    | k for Filter 8 k | oits (same value                        | s as bits<15:1  | 2>)      |       |

|               |                                                                                                                                                                    |                  |                  |                                         |                 |          |       |

© 2011-2013 Microchip Technology Inc.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

## REGISTER 21-16: CxRXFnSID: ECANx ACCEPTANCE FILTER n STANDARD IDENTIFIER REGISTER (n = 0-15)

| RW-x       R/W-x       R/W-x       R/W-x       R/W-x       R/W-x       R/W-x       R/W-x         SID10       SID9       SID8       SID7       SID6       SID5       SID4       SID3         bit 15       bit 15       bit 8       bit 8       bit 8       bit 8       bit 8         R/W-x       R/W-x       R/W-x       U-0       R/W-x       U-0       R/W-x       R/W-x         SID2       SID1       SID0       -       EXIDE       -       EID17       EID16         bit 7       bit 0       -       EXIDE       -       EID17       EID16         bit 7       bit 0       -       -       EXIDE       -       bit 0         Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                             |                            |                                      |                     |                  |                  |                 |       |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--------------------------------------|---------------------|------------------|------------------|-----------------|-------|--|

| bit 15 bit 2 bit 3 bit 8 bit 8 bit 8 bit 7 bit 7 bit 9 bit 7 bit 0 bit 0 bit 7 bit 0 bit 0 bit 7 bit 0 bit 0 bit 0 bit 1 bit 9 bit 1 bit 9 bit 1 bit 1 bit 9 bit 1 | R/W-x                                                                                                                                                                       | R/W-x                      | R/W-x                                | R/W-x               | R/W-x            | R/W-x            | R/W-x           | R/W-x |  |

| R/W-x       R/W-x       U-0       R/W-x       U-0       R/W-x       R/W-x         SID2       SID1       SID0       -       EXIDE       -       EID17       EID16         bit 7       bit 0         Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-5       SID<10:>: Standard Identifier bits       1 = Message address bit, SIDx, must be '1' to match filter       0 = Message address bit, SIDx, must be '0' to match filter         bit 4       Unimplemented: Read as '0'       bit 3       EXIDE: Extended Identifier Enable bit         If MIDE = 1:       1 = Matches only messages with Extended Identifier addresses       0 = Matches only messages with Standard Identifier addresses         0 = Matches only messages with Standard Identifier addresses       Ignores EXIDE bit.       Ignores EXIDE bit.         bit 2       Unimplemented: Read as '0'       bit 1-0       EID       EID         bit 1-0       EID       Extended Identifier bits       1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SID10                                                                                                                                                                       | SID9                       | SID8                                 | SID7                | SID6             | SID5             | SID4            | SID3  |  |

| SID2       SID1       SID0       —       EXIDE       —       EID17       EID16         bit 7       bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | bit 15                                                                                                                                                                      |                            |                                      |                     |                  |                  |                 | bit 8 |  |

| SID2       SID1       SID0       —       EXIDE       —       EID17       EID16         bit 7       bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                             |                            |                                      |                     |                  |                  |                 |       |  |