Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2 0 0 0 0 0                |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 512KB (170K x 24)                                                               |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | · ·                                                                             |

| RAM Size                   | 24K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 9x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-TQFP                                                                         |

| Supplier Device Package    | 44-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep512gp204t-e-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 4   | TABLE 4-9:         INPUT CAPTURE 1 THROUGH INPUT CAPTURE 4 REGISTER MAP |        |                                     |        |        |           |        |       |              |              |          |       |       |       |          |          |       |               |

|-----------|-------------------------------------------------------------------------|--------|-------------------------------------|--------|--------|-----------|--------|-------|--------------|--------------|----------|-------|-------|-------|----------|----------|-------|---------------|

| File Name | Addr.                                                                   | Bit 15 | Bit 14                              | Bit 13 | Bit 12 | Bit 11    | Bit 10 | Bit 9 | Bit 8        | Bit 7        | Bit 6    | Bit 5 | Bit 4 | Bit 3 | Bit 2    | Bit 1    | Bit 0 | All<br>Resets |

| IC1CON1   | 0140                                                                    | _      | —                                   | ICSIDL | 10     | CTSEL<2:0 | >      | —     | -            | —            | ICI<     | :0>   | ICOV  | ICBNE |          | ICM<2:0> |       | 0000          |

| IC1CON2   | 0142                                                                    | _      | _                                   |        | _      |           | —      | —     | IC32         | ICTRIG       | TRIGSTAT |       |       | S     | YNCSEL<4 | :0>      |       | 000D          |

| IC1BUF    | 0144                                                                    |        | Input Capture 1 Buffer Register xx: |        |        |           |        |       |              |              |          |       |       |       | xxxx     |          |       |               |

| IC1TMR    | 0146                                                                    |        | Input Capture 1 Timer 00            |        |        |           |        |       |              |              |          | 0000  |       |       |          |          |       |               |

| IC2CON1   | 0148                                                                    |        | _                                   | ICSIDL | 10     | CTSEL<2:0 | >      | —     | _            |              | ICI<1    | :0>   | ICOV  | ICBNE |          | ICM<2:0> |       | 0000          |

| IC2CON2   | 014A                                                                    |        | IC32 ICTRIG TRIGSTAT - SYNCSEL<4:0> |        |        |           |        |       |              |              |          |       | 000D  |       |          |          |       |               |

| IC2BUF    | 014C                                                                    |        |                                     |        |        |           |        | Inp   | ut Capture 2 | 2 Buffer Reg | gister   |       |       |       |          |          |       | xxxx          |

| IC2TMR    | 014E                                                                    |        |                                     |        |        |           |        |       | Input Capt   | ture 2 Time  | r        |       |       |       |          |          |       | 0000          |

| IC3CON1   | 0150                                                                    |        | _                                   | ICSIDL | 10     | CTSEL<2:0 | >      | —     | _            |              | ICI<1    | :0>   | ICOV  | ICBNE |          | ICM<2:0> |       | 0000          |

| IC3CON2   | 0152                                                                    |        | _                                   |        |        |           | —      | —     | IC32         | ICTRIG       | TRIGSTAT |       |       | S     | YNCSEL<4 | :0>      |       | 000D          |

| IC3BUF    | 0154                                                                    |        |                                     |        |        |           |        | Inp   | ut Capture 3 | 3 Buffer Reg | gister   |       |       |       |          |          |       | xxxx          |

| IC3TMR    | 0156                                                                    |        |                                     |        |        |           |        |       | Input Capt   | ture 3 Time  | r        |       |       |       |          |          |       | 0000          |

| IC4CON1   | 0158                                                                    |        | _                                   | ICSIDL | 10     | CTSEL<2:0 | >      | —     | _            |              | ICI<1    | :0>   | ICOV  | ICBNE |          | ICM<2:0> |       | 0000          |

| IC4CON2   | 015A                                                                    | _      | _                                   |        | -      |           | -      | _     | IC32         | ICTRIG       | TRIGSTAT | -     |       | S     | YNCSEL<4 | :0>      |       | 000D          |

| IC4BUF    | 015C                                                                    |        |                                     |        |        |           |        | Inp   | ut Capture 4 | 4 Buffer Reg | gister   |       |       |       |          |          |       | xxxx          |

| IC4TMR    | 015E                                                                    |        |                                     |        |        |           |        |       | Input Capt   | ure 4 Time   | r        |       |       |       |          |          |       | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| R/S-0                | U-0                                                                              | U-0                             | U-0                   | U-0              | U-0              | U-0             | U-0     |  |  |  |  |  |

|----------------------|----------------------------------------------------------------------------------|---------------------------------|-----------------------|------------------|------------------|-----------------|---------|--|--|--|--|--|

| FORCE <sup>(1)</sup> |                                                                                  | _                               | _                     | —                |                  | _               |         |  |  |  |  |  |

| bit 15               |                                                                                  |                                 |                       |                  |                  |                 | bit 8   |  |  |  |  |  |

|                      |                                                                                  |                                 |                       |                  |                  |                 |         |  |  |  |  |  |

| R/W-0                | R/W-0                                                                            | R/W-0                           | R/W-0                 | R/W-0            | R/W-0            | R/W-0           | R/W-0   |  |  |  |  |  |

| IRQSEL7              | IRQSEL6                                                                          | IRQSEL5                         | IRQSEL4               | IRQSEL3          | IRQSEL2          | IRQSEL1         | IRQSEL0 |  |  |  |  |  |

| bit 7                |                                                                                  |                                 |                       |                  |                  |                 | bit     |  |  |  |  |  |

| Legend:              |                                                                                  | S = Settable b                  | oit                   |                  |                  |                 |         |  |  |  |  |  |

| R = Readable         | bit                                                                              | W = Writable                    | bit                   | U = Unimpler     | mented bit, read | d as '0'        |         |  |  |  |  |  |

| -n = Value at F      | POR                                                                              | '1' = Bit is set                |                       | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |  |  |  |  |  |

|                      |                                                                                  |                                 |                       |                  |                  |                 |         |  |  |  |  |  |

| bit 15               | FORCE: Force                                                                     | e DMA Transfe                   | er bit <sup>(1)</sup> |                  |                  |                 |         |  |  |  |  |  |

|                      | 1 = Forces a                                                                     | single DMA tra                  | insfer (Manua         | l mode)          |                  |                 |         |  |  |  |  |  |

|                      | 0 = Automati                                                                     | c DMA transfer                  | initiation by D       | DMA request      |                  |                 |         |  |  |  |  |  |

| bit 14-8             | Unimplemen                                                                       | ted: Read as 'd                 | )'                    |                  |                  |                 |         |  |  |  |  |  |

| bit 7-0              | IRQSEL<7:0>: DMA Peripheral IRQ Number Select bits                               |                                 |                       |                  |                  |                 |         |  |  |  |  |  |

|                      | 01000110 = ECAN1 – TX Data Request <sup>(2)</sup>                                |                                 |                       |                  |                  |                 |         |  |  |  |  |  |

|                      | 00100110 = IC4 – Input Capture 4                                                 |                                 |                       |                  |                  |                 |         |  |  |  |  |  |

|                      | 00100101 = IC3 - Input Capture 3                                                 |                                 |                       |                  |                  |                 |         |  |  |  |  |  |

|                      | 00100010 = ECAN1 – RX Data Ready <sup>(2)</sup><br>00100001 = SPI2 Transfer Done |                                 |                       |                  |                  |                 |         |  |  |  |  |  |

|                      |                                                                                  | . = UART2TX – UART2 Transmitter |                       |                  |                  |                 |         |  |  |  |  |  |

|                      |                                                                                  | UART2RX – UART2 Receiver        |                       |                  |                  |                 |         |  |  |  |  |  |

|                      |                                                                                  | TMR5 – Timer5                   |                       |                  |                  |                 |         |  |  |  |  |  |

|                      | 00011011 = TMR4 – Timer4                                                         |                                 |                       |                  |                  |                 |         |  |  |  |  |  |

|                      | 00011010 = OC4 – Output Compare 4                                                |                                 |                       |                  |                  |                 |         |  |  |  |  |  |

|                      | 00011001 = OC3 – Output Compare 3                                                |                                 |                       |                  |                  |                 |         |  |  |  |  |  |

|                      | 00001101 = ADC1 – ADC1 Convert done                                              |                                 |                       |                  |                  |                 |         |  |  |  |  |  |

|                      | 00001100 = UART1TX – UART1 Transmitter                                           |                                 |                       |                  |                  |                 |         |  |  |  |  |  |

|                      | 00001011 = UART1RX – UART1 Receiver<br>00001010 = SPI1 – Transfer Done           |                                 |                       |                  |                  |                 |         |  |  |  |  |  |

|                      |                                                                                  | TMR3 – Timer3                   |                       |                  |                  |                 |         |  |  |  |  |  |

|                      |                                                                                  | TMR2 – Timer2                   |                       |                  |                  |                 |         |  |  |  |  |  |

|                      |                                                                                  | OC2 – Output (                  |                       |                  |                  |                 |         |  |  |  |  |  |

|                      |                                                                                  | IC2 – Input Ca                  |                       |                  |                  |                 |         |  |  |  |  |  |

|                      | 0000010 =                                                                        | OC1 – Output (                  | Compare 1             |                  |                  |                 |         |  |  |  |  |  |

|                      |                                                                                  | IC1 – Input Ca                  |                       |                  |                  |                 |         |  |  |  |  |  |

|                      | 00000000 =                                                                       | INT0 – Externa                  | I Interrupt 0         |                  |                  |                 |         |  |  |  |  |  |

#### REGISTER 8-2: DMAXREQ: DMA CHANNEL x IRQ SELECT REGISTER

- **Note 1:** The FORCE bit cannot be cleared by user software. The FORCE bit is cleared by hardware when the forced DMA transfer is complete or the channel is disabled (CHEN = 0).

- 2: This selection is available in dsPIC33EPXXXGP/MC50X devices only.

| REGISTER     | <u>R 10-2: PMD</u> 2                      | 2: PERIPHER                                         | AL MODULE      | DISABLE C         | ONTROL RE       | GISTER 2        |       |  |  |  |  |  |

|--------------|-------------------------------------------|-----------------------------------------------------|----------------|-------------------|-----------------|-----------------|-------|--|--|--|--|--|

| U-0          | U-0                                       | U-0                                                 | U-0            | R/W-0             | R/W-0           | R/W-0           | R/W-0 |  |  |  |  |  |

| _            |                                           | —                                                   |                | IC4MD             | IC3MD           | IC2MD           | IC1MD |  |  |  |  |  |

| bit 15       |                                           |                                                     |                |                   |                 |                 | bit   |  |  |  |  |  |

| U-0          | U-0                                       | U-0                                                 | U-0            | R/W-0             | R/W-0           | R/W-0           | R/W-0 |  |  |  |  |  |

|              |                                           |                                                     |                | OC4MD             | OC3MD           | OC2MD           | OC1MD |  |  |  |  |  |

| bit 7        |                                           |                                                     |                |                   |                 |                 | bit   |  |  |  |  |  |

|              |                                           |                                                     |                |                   |                 |                 |       |  |  |  |  |  |

| Legend:      | 1.1.1                                     |                                                     |                |                   |                 |                 |       |  |  |  |  |  |

| R = Readab   |                                           | W = Writable b                                      | Dit            | •                 | nented bit, rea |                 |       |  |  |  |  |  |

| -n = Value a | at POR                                    | '1' = Bit is set                                    |                | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |  |  |  |  |  |

| bit 15-12    | Unimplemen                                | ted: Read as '0                                     | ,              |                   |                 |                 |       |  |  |  |  |  |

| bit 11       | -                                         | t Capture 4 Mod                                     |                |                   |                 |                 |       |  |  |  |  |  |

|              | •                                         | oture 4 module is                                   |                |                   |                 |                 |       |  |  |  |  |  |

|              | 0 = Input Cap                             | oture 4 module is                                   | s enabled      |                   |                 |                 |       |  |  |  |  |  |

| bit 10       | IC3MD: Input Capture 3 Module Disable bit |                                                     |                |                   |                 |                 |       |  |  |  |  |  |

|              | 1 = Input Capture 3 module is disabled    |                                                     |                |                   |                 |                 |       |  |  |  |  |  |

|              |                                           | oture 3 module is                                   |                |                   |                 |                 |       |  |  |  |  |  |

| bit 9        |                                           | t Capture 2 Mod                                     |                |                   |                 |                 |       |  |  |  |  |  |

|              |                                           | oture 2 module is<br>oture 2 module is              |                |                   |                 |                 |       |  |  |  |  |  |

| bit 8        | IC1MD: Input                              | IC1MD: Input Capture 1 Module Disable bit           |                |                   |                 |                 |       |  |  |  |  |  |

|              | 1 = Input Cap                             | oture 1 module is<br>oture 1 module is              | s disabled     |                   |                 |                 |       |  |  |  |  |  |

| bit 7-4      |                                           | ted: Read as '0                                     |                |                   |                 |                 |       |  |  |  |  |  |

| bit 3        | OC4MD: Out                                | put Compare 4                                       | Module Disable | e bit             |                 |                 |       |  |  |  |  |  |

|              |                                           | ompare 4 modul                                      |                |                   |                 |                 |       |  |  |  |  |  |

|              | -                                         | ompare 4 modu                                       |                |                   |                 |                 |       |  |  |  |  |  |

| bit 2        |                                           | OC3MD: Output Compare 3 Module Disable bit          |                |                   |                 |                 |       |  |  |  |  |  |

|              | •                                         | ompare 3 modul                                      |                |                   |                 |                 |       |  |  |  |  |  |

| L:1 4        | -                                         | ompare 3 modul                                      |                | . h.:4            |                 |                 |       |  |  |  |  |  |

| bit 1        |                                           | put Compare 2                                       |                |                   |                 |                 |       |  |  |  |  |  |

|              | $\perp$ – Output Co                       | ompare 2 modu                                       |                |                   |                 |                 |       |  |  |  |  |  |

|              | 0 = Output Co                             | ompare 2 modul                                      | le is enabled  |                   |                 |                 |       |  |  |  |  |  |

| bit 0        |                                           | ompare 2 modul<br>put Compare 1                     |                | e bit             |                 |                 |       |  |  |  |  |  |

| bit 0        | OC1MD: Out                                | ompare 2 modul<br>put Compare 1 l<br>ompare 1 modul | Module Disable | e bit             |                 |                 |       |  |  |  |  |  |

#### ~

## 11.1.1 OPEN-DRAIN CONFIGURATION

In addition to the PORTx, LATx and TRISx registers for data control, port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs other than VDD by using external pull-up resistors. The maximum open-drain voltage allowed on any pin is the same as the maximum VIH specification for that particular pin.

See the **"Pin Diagrams"** section for the available 5V tolerant pins and Table 30-11 for the maximum VIH specification for each pin.

# 11.2 Configuring Analog and Digital Port Pins

The ANSELx register controls the operation of the analog port pins. The port pins that are to function as analog inputs or outputs must have their corresponding ANSELx and TRISx bits set. In order to use port pins for I/O functionality with digital modules, such as Timers, UARTs, etc., the corresponding ANSELx bit must be cleared.

The ANSELx register has a default value of 0xFFFF; therefore, all pins that share analog functions are analog (not digital) by default.

Pins with analog functions affected by the ANSELx registers are listed with a buffer type of analog in the Pinout I/O Descriptions (see Table 1-1).

If the TRISx bit is cleared (output) while the ANSELx bit is set, the digital output level (VOH or VOL) is converted by an analog peripheral, such as the ADC module or comparator module.

When the PORTx register is read, all pins configured as analog input channels are read as cleared (a low level).

Pins configured as digital inputs do not convert an analog input. Analog levels on any pin defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications.

#### 11.2.1 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically this instruction would be a NOP, as shown in Example 11-1.

# **11.3** Input Change Notification (ICN)

The Input Change Notification function of the I/O ports allows devices to generate interrupt requests to the processor in response to a Change-of-State (COS) on selected input pins. This feature can detect input Change-of-States even in Sleep mode, when the clocks are disabled. Every I/O port pin can be selected (enabled) for generating an interrupt request on a Change-of-State.

Three control registers are associated with the Change Notification (CN) functionality of each I/O port. The CNENx registers contain the CN interrupt enable control bits for each of the input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

Each I/O pin also has a weak pull-up and a weak pull-down connected to it. The pull-ups and pulldowns act as a current source or sink source connected to the pin and eliminate the need for external resistors when push button, or keypad devices are connected. The pull-ups and pull-downs are enabled separately, using the CNPUx and the CNPDx registers, which contain the control bits for each of the pins. Setting any of the control bits enables the weak pull-ups and/or pull-downs for the corresponding pins.

| Note: | Pull-ups and pull-downs on Change Noti-      |

|-------|----------------------------------------------|

|       | fication pins should always be disabled      |

|       | when the port pin is configured as a digital |

|       | output.                                      |

#### EXAMPLE 11-1: PORT WRITE/READ EXAMPLE

| MOV  | 0xFF00, WO | ; Configure PORTB<15:8> |

|------|------------|-------------------------|

|      |            | ; as inputs             |

| MOV  | W0, TRISB  | ; and PORTB<7:0>        |

|      |            | ; as outputs            |

| NOP  |            | ; Delay 1 cycle         |

| BTSS | PORTB, #13 | ; Next Instruction      |

|      |            |                         |

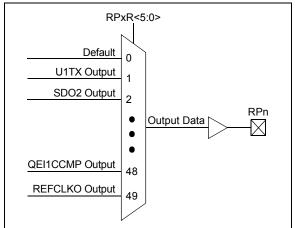

### 11.4.4.2 Output Mapping

In contrast to inputs, the outputs of the Peripheral Pin Select options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPORx registers are used to control output mapping. Like the RPINRx registers, each register contains sets of 6-bit fields, with each set associated with one RPn pin (see Register 11-18 through Register 11-27). The value of the bit field corresponds to one of the peripherals and that peripheral's output is mapped to the pin (see Table 11-3 and Figure 11-3).

A null output is associated with the output register Reset value of '0'. This is done to ensure that remappable outputs remain disconnected from all output pins by default.

#### FIGURE 11-3: MULTIPLEXING REMAPPABLE OUTPUT FOR RPn

## 11.4.4.3 Mapping Limitations

The control schema of the peripheral select pins is not limited to a small range of fixed peripheral configurations. There are no mutual or hardware-enforced lockouts between any of the peripheral mapping SFRs. Literally any combination of peripheral mappings across any or all of the RPn pins is possible. This includes both many-toone and one-to-many mappings of peripheral inputs and outputs to pins. While such mappings may be technically possible from a configuration point of view, they may not be supportable from an electrical point of view.

#### TABLE 11-3: OUTPUT SELECTION FOR REMAPPABLE PINS (RPn)

| Function                | RPxR<5:0> | Output Name                                   |

|-------------------------|-----------|-----------------------------------------------|

| Default PORT            | 000000    | RPn tied to Default Pin                       |

| U1TX                    | 000001    | RPn tied to UART1 Transmit                    |

| U2TX                    | 000011    | RPn tied to UART2 Transmit                    |

| SDO2                    | 001000    | RPn tied to SPI2 Data Output                  |

| SCK2                    | 001001    | RPn tied to SPI2 Clock Output                 |

| SS2                     | 001010    | RPn tied to SPI2 Slave Select                 |

| C1TX <sup>(2)</sup>     | 001110    | RPn tied to CAN1 Transmit                     |

| OC1                     | 010000    | RPn tied to Output Compare 1 Output           |

| OC2                     | 010001    | RPn tied to Output Compare 2 Output           |

| OC3                     | 010010    | RPn tied to Output Compare 3 Output           |

| OC4                     | 010011    | RPn tied to Output Compare 4 Output           |

| C1OUT                   | 011000    | RPn tied to Comparator Output 1               |

| C2OUT                   | 011001    | RPn tied to Comparator Output 2               |

| C3OUT                   | 011010    | RPn tied to Comparator Output 3               |

| SYNCO1 <sup>(1)</sup>   | 101101    | RPn tied to PWM Primary Time Base Sync Output |

| QEI1CCMP <sup>(1)</sup> | 101111    | RPn tied to QEI 1 Counter Comparator Output   |

| REFCLKO                 | 110001    | RPn tied to Reference Clock Output            |

| C4OUT                   | 110010    | RPn tied to Comparator Output 4               |

Note 1: This function is available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This function is available in dsPIC33EPXXXGP/MC50X devices only.

#### REGISTER 14-2: ICxCON2: INPUT CAPTURE x CONTROL REGISTER 2 (CONTINUED)

- bit 4-0 SYNCSEL<4:0>: Input Source Select for Synchronization and Trigger Operation bits<sup>(4)</sup>

- 11111 = No Sync or Trigger source for ICx

- 11110 = Reserved

- 11101 = Reserved

- 11100 = CTMU module synchronizes or triggers ICx

- 11011 = ADC1 module synchronizes or triggers  $ICx^{(5)}$

- 11010 = CMP3 module synchronizes or triggers  $ICx^{(5)}$

- $11001 = CMP2 \text{ module synchronizes or triggers ICx}^{(5)}$

- 11000 = CMP1 module synchronizes or triggers  $ICx^{(5)}$

- 10111 = Reserved

- 10110 = Reserved

- 10101 = Reserved

- 10100 = Reserved

- 10011 = IC4 module synchronizes or triggers ICx

- 10010 = IC3 module synchronizes or triggers ICx

- 10001 = IC2 module synchronizes or triggers ICx

- 10000 = IC1 module synchronizes or triggers ICx

- 01111 = Timer5 synchronizes or triggers ICx

- 01110 = Timer4 synchronizes or triggers ICx

- 01101 = Timer3 synchronizes or triggers ICx (default)

- 01100 = Timer2 synchronizes or triggers ICx

- 01011 = Timer1 synchronizes or triggers ICx

- 01010 = PTGOx module synchronizes or triggers  $ICx^{(6)}$

- 01001 = Reserved

- 01000 = Reserved

- 00111 = Reserved

- 00110 = Reserved

- 00101 = Reserved

- 00100 = OC4 module synchronizes or triggers ICx

- 00011 = OC3 module synchronizes or triggers ICx

- 00010 = OC2 module synchronizes or triggers ICx

- 00001 = OC1 module synchronizes or triggers ICx

- 00000 = No Sync or Trigger source for ICx

- **Note 1:** The IC32 bit in both the Odd and Even IC must be set to enable Cascade mode.

- 2: The input source is selected by the SYNCSEL<4:0> bits of the ICxCON2 register.

- **3:** This bit is set by the selected input source (selected by SYNCSEL<4:0> bits). It can be read, set and cleared in software.

- 4: Do not use the ICx module as its own Sync or Trigger source.

- 5: This option should only be selected as a trigger source and not as a synchronization source.

- Each Input Capture x (ICx) module has one PTG input source. See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for more information.

PTGO8 = IC1

PTGO9 = IC2 PTGO10 = IC3 PTGO11 = IC4

#### 16.1.2 WRITE-PROTECTED REGISTERS

On dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices, write protection is implemented for the IOCONx and FCLCONx registers. The write protection feature prevents any inadvertent writes to these registers. This protection feature can be controlled by the PWMLOCK Configuration bit (FOSCSEL<6>). The default state of the write protection feature is enabled (PWMLOCK = 1). The write protection feature can be disabled by configuring, PWMLOCK = 0. To gain write access to these locked registers, the user application must write two consecutive values of (0xABCD and 0x4321) to the PWMKEY register to perform the unlock operation. The write access to the IOCONx or FCLCONx registers must be the next SFR access following the unlock process. There can be no other SFR accesses during the unlock process and subsequent write access. To write to both the IOCONx and FCLCONx registers requires two unlock operations.

The correct unlocking sequence is described in Example 16-1.

#### EXAMPLE 16-1: PWMx WRITE-PROTECTED REGISTER UNLOCK SEQUENCE

|                                                                                                          | lled low externally in order to clear and disable the fault<br>egister requires unlock sequence                                                                                                                                                                                                   |

|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>mov #0xabcd,w10 mov #0x4321,w11 mov #0x0000,w0 mov w10, PWMKEY mov w11, PWMKEY mov w0,FCLCON1</pre> | <pre>; Load first unlock key to w10 register<br/>; Load second unlock key to w11 register<br/>; Load desired value of FCLCON1 register in w0<br/>; Write first unlock key to PWMKEY register<br/>; Write second unlock key to PWMKEY register<br/>; Write desired value to FCLCON1 register</pre> |

| -                                                                                                        | d polarity using the IOCON1 register<br>gister requires unlock sequence                                                                                                                                                                                                                           |

| <pre>mov #0xabcd,w10 mov #0x4321,w11 mov #0xF000,w0 mov w10, PWMKEY mov w11, PWMKEY mov w0,IOCON1</pre>  | <pre>; Load first unlock key to w10 register<br/>; Load second unlock key to w11 register<br/>; Load desired value of IOCON1 register in w0<br/>; Write first unlock key to PWMKEY register<br/>; Write second unlock key to PWMKEY register<br/>; Write desired value to IOCON1 register</pre>   |

# REGISTER 16-13: IOCONX: PWMx I/O CONTROL REGISTER<sup>(2)</sup> (CONTINUED)

- bit 1 SWAP: SWAP PWMxH and PWMxL Pins bit

1 = PWMxH output signal is connected to PWMxL pins; PWMxL output signal is connected to PWMxH pins

0 = PWMxH and PWMxL pins are mapped to their respective pins

bit 0 OSYNC: Output Override Synchronization bit

1 = Output overrides via the OVRDAT<1:0> bits are synchronized to the PWMx period boundary

- 0 = Output overrides via the OVDDAT<1:0> bits occur on the next CPU clock boundary

- Note 1: These bits should not be changed after the PWMx module is enabled (PTEN = 1).

- 2: If the PWMLOCK Configuration bit (FOSCSEL<6>) is a '1', the IOCONx register can only be written after the unlock sequence has been executed.

# REGISTER 17-13: QEI1LECH: QEI1 LESS THAN OR EQUAL COMPARE HIGH WORD REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0          | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|----------------|-----------------|-------|

|                 |       |                  | QEILE | C<31:24>          |                |                 |       |

| bit 15          |       |                  |       |                   |                |                 | bit 8 |

|                 |       |                  |       |                   |                |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0          | R/W-0           | R/W-0 |

|                 |       |                  | QEILE | C<23:16>          |                |                 |       |

| bit 7           |       |                  |       |                   |                |                 | bit 0 |

|                 |       |                  |       |                   |                |                 |       |

| Legend:         |       |                  |       |                   |                |                 |       |

| R = Readable    | bit   | W = Writable b   | bit   | U = Unimplem      | ented bit, rea | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is clea | red            | x = Bit is unkr | nown  |

bit 15-0 QEILEC<31:16>: High Word Used to Form 32-Bit Less Than or Equal Compare Register (QEI1LEC) bits

# REGISTER 17-14: QEI1LECL: QEI1 LESS THAN OR EQUAL COMPARE LOW WORD REGISTER

| R = Readable t |       | W = Writable<br>'1' = Bit is set |       | U = Unimplen<br>'0' = Bit is cle |       | ad as '0'<br>x = Bit is unkr |       |

|----------------|-------|----------------------------------|-------|----------------------------------|-------|------------------------------|-------|

| Legend:        |       |                                  |       |                                  |       |                              |       |

|                |       |                                  |       |                                  |       |                              |       |

| bit 7          |       |                                  |       |                                  |       |                              | bit   |

|                |       |                                  | QEIL  | EC<7:0>                          |       |                              |       |

| R/W-0          | R/W-0 | R/W-0                            | R/W-0 | R/W-0                            | R/W-0 | R/W-0                        | R/W-0 |

| bit 15         |       |                                  |       |                                  |       |                              | bit   |

|                |       |                                  | QEILE | EC<15:8>                         |       |                              |       |

| R/W-0          | R/W-0 | R/W-0                            | R/W-0 | R/W-0                            | R/W-0 | R/W-0                        | R/W-0 |

bit 15-0 QEILEC<15:0>: Low Word Used to Form 32-Bit Less Than or Equal Compare Register (QEI1LEC) bits

# 24.2 PTG Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

### 24.2.1 KEY RESOURCES

- "Peripheral Trigger Generator" (DS70669) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

| DC CHARACTER            | ISTICS |   | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |            |        |  |  |  |

|-------------------------|--------|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------|--|--|--|

| Parameter No. Typ. Max. |        |   | Units                                                                                                                                                                                                                                                                                 | Conditions |        |  |  |  |

| DC61d                   | 8      |   | μΑ                                                                                                                                                                                                                                                                                    | -40°C      |        |  |  |  |

| DC61a                   | 10     | — | μA                                                                                                                                                                                                                                                                                    | +25°C      | 2.21/  |  |  |  |

| DC61b                   | 12     | — | μA                                                                                                                                                                                                                                                                                    | +85°C      | - 3.3V |  |  |  |

| DC61c                   | 13     | — | μA                                                                                                                                                                                                                                                                                    | +125°C     |        |  |  |  |

# TABLE 30-9: DC CHARACTERISTICS: WATCHDOG TIMER DELTA CURRENT $(\triangle Iwdt)^{(1)}$

**Note 1:** The  $\triangle$ IwDT current is the additional current consumed when the module is enabled. This current should be added to the base IPD current. All parameters are characterized but not tested during manufacturing.

#### TABLE 30-10: DC CHARACTERISTICS: DOZE CURRENT (IDOZE)

| DC CHARACTER                        | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |       |            |    |        |      |                |

|-------------------------------------|-------------------------------------------------------|-------|------------|----|--------|------|----------------|

| Parameter No.                       | Doze<br>Ratio                                         | Units | Conditions |    |        |      |                |

| Doze Current (IDOZE) <sup>(1)</sup> |                                                       |       |            |    |        |      |                |

| DC73a <sup>(2)</sup>                | 35                                                    |       | 1:2        | mA | -40°C  | 3.3V | Fosc = 140 MHz |

| DC73g                               | 20                                                    | 30    | 1:128      | mA | -40 C  |      |                |

| DC70a <sup>(2)</sup>                | 35                                                    | _     | 1:2        | mA | +25°C  | 3.3V | Fosc = 140 MHz |

| DC70g                               | 20                                                    | 30    | 1:128      | mA | +25 C  |      |                |

| DC71a <sup>(2)</sup>                | 35                                                    | —     | 1:2        | mA | 195%   | 3.3V |                |

| DC71g                               | 20                                                    | 30    | 1:128      | mA | +85°C  |      | Fosc = 140 MHz |

| DC72a <sup>(2)</sup>                | 28                                                    | —     | 1:2        | mA | +125°C | 3.3V | Ecco - 120 MH- |

| DC72g                               | 15                                                    | 30    | 1:128      | mA | +125 C |      | Fosc = 120 MHz |

**Note 1:** IDOZE is primarily a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDOZE measurements are as follows:

- Oscillator is configured in EC mode and external clock is active, OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)</li>

- CLKO is configured as an I/O input pin in the Configuration Word

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- CPU, SRAM, program memory and data memory are operational

- No peripheral modules are operating; however, every peripheral is being clocked (all PMDx bits are zeroed)

- CPU is executing while(1) statement

- · JTAG is disabled

- 2: Parameter is characterized but not tested in manufacturing.

| DC CHARACTERISTICS |        |                                                                       | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |   |                       |    |                                                                                                                                      |  |

|--------------------|--------|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----------------------|----|--------------------------------------------------------------------------------------------------------------------------------------|--|

| Param<br>No.       | Symbol | Characteristic                                                        | Min. Typ. Max. Units Condition                                                                                                                                                                                                                                                          |   |                       |    |                                                                                                                                      |  |

| DI60a              | licl   | Input Low Injection Current                                           | 0                                                                                                                                                                                                                                                                                       |   | <sub>-5</sub> (4,7)   | mA | All pins except VDD, VSS,<br>AVDD, AVSS, MCLR, VCAP<br>and RB7                                                                       |  |

| DI60b              | Іісн   | Input High Injection Current                                          | 0                                                                                                                                                                                                                                                                                       |   | +5 <sup>(5,6,7)</sup> | mA | All pins except VDD, VSS,<br>AVDD, AVSS, MCLR, VCAP,<br>RB7 and all 5V tolerant<br>pins <sup>(6)</sup>                               |  |

| DI60c              | ∑lict  | Total Input Injection Current<br>(sum of all I/O and control<br>pins) | -20 <sup>(8)</sup>                                                                                                                                                                                                                                                                      | _ | +20 <sup>(8)</sup>    | mA | Absolute instantaneous sum<br>of all $\pm$ input injection cur-<br>rents from all I/O pins<br>(   IICL +   IICH   ) $\leq \sum$ IICT |  |

# TABLE 30-11: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS (CONTINUED)

**Note 1:** The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current can be measured at different input voltages.

2: Negative current is defined as current sourced by the pin.

3: See the "Pin Diagrams" section for the 5V tolerant I/O pins.

4: VIL source < (Vss – 0.3). Characterized but not tested.

5: Non-5V tolerant pins VIH source > (VDD + 0.3), 5V tolerant pins VIH source > 5.5V. Characterized but not tested.

6: Digital 5V tolerant pins cannot tolerate any "positive" input injection current from input sources > 5.5V.

7: Non-zero injection currents can affect the ADC results by approximately 4-6 counts.

8: Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the mathematical "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. Characterized but not tested.

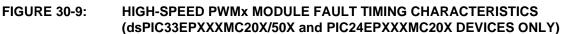

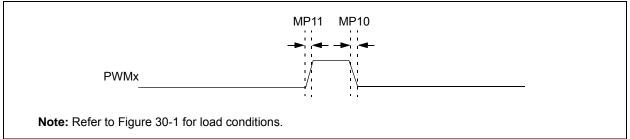

## FIGURE 30-10: HIGH-SPEED PWMx MODULE TIMING CHARACTERISTICS (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

## TABLE 30-29: HIGH-SPEED PWMx MODULE TIMING REQUIREMENTS (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

| AC CHARACTERISTICS |        |                                     | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |   |    |    |                    |

|--------------------|--------|-------------------------------------|-------------------------------------------------------|---|----|----|--------------------|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>       | Min. Typ. Max. Units Conditions                       |   |    |    | Conditions         |

| MP10               | TFPWM  | PWMx Output Fall Time               |                                                       | — | _  | ns | See Parameter DO32 |

| MP11               | TRPWM  | PWMx Output Rise Time               | _                                                     | — | _  | ns | See Parameter DO31 |

| MP20               | Tfd    | Fault Input ↓ to PWMx<br>I/O Change | _                                                     | _ | 15 | ns |                    |

| MP30               | Tfh    | Fault Input Pulse Width             | 15                                                    | _ | _  | ns |                    |

**Note 1:** These parameters are characterized but not tested in manufacturing.

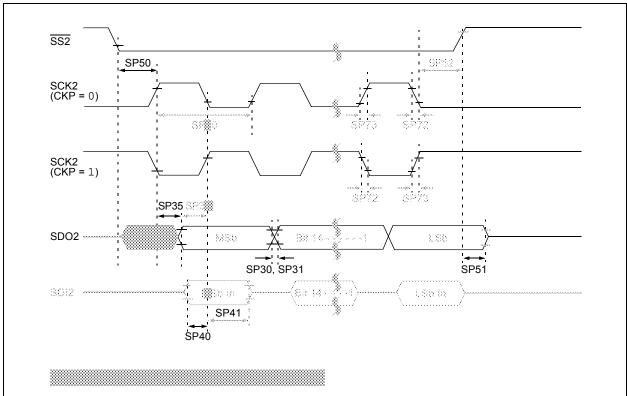

## FIGURE 30-20: SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0) TIMING CHARACTERISTICS

| AC CHARACTERISTICS |         |                               |                           | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |      |       |                                             |  |  |

|--------------------|---------|-------------------------------|---------------------------|-------------------------------------------------------|------|-------|---------------------------------------------|--|--|

| Param.<br>No.      | Symbol  | Characteristic <sup>(3)</sup> |                           | Min.                                                  | Max. | Units | Conditions                                  |  |  |

| IS10               | TLO:SCL | Clock Low Time                | 100 kHz mode              | 4.7                                                   | _    | μS    |                                             |  |  |

|                    |         |                               | 400 kHz mode              | 1.3                                                   | —    | μS    |                                             |  |  |

|                    |         |                               | 1 MHz mode <sup>(1)</sup> | 0.5                                                   | —    | μS    |                                             |  |  |

| IS11 Thi:so        | THI:SCL | Clock High Time               | 100 kHz mode              | 4.0                                                   | —    | μS    | Device must operate at a minimum of 1.5 MHz |  |  |

|                    |         |                               | 400 kHz mode              | 0.6                                                   | —    | μS    | Device must operate at a minimum of 10 MHz  |  |  |

|                    |         |                               | 1 MHz mode <sup>(1)</sup> | 0.5                                                   | —    | μS    |                                             |  |  |

| IS20               | TF:SCL  | SDAx and SCLx                 | 100 kHz mode              |                                                       | 300  | ns    | CB is specified to be from                  |  |  |

|                    |         | Fall Time                     | 400 kHz mode              | 20 + 0.1 Св                                           | 300  | ns    | 10 to 400 pF                                |  |  |

|                    |         |                               | 1 MHz mode <sup>(1)</sup> | —                                                     | 100  | ns    |                                             |  |  |

| IS21               | TR:SCL  | SDAx and SCLx                 | 100 kHz mode              |                                                       | 1000 | ns    | CB is specified to be from                  |  |  |

|                    |         | Rise Time                     | 400 kHz mode              | 20 + 0.1 Св                                           | 300  | ns    | 10 to 400 pF                                |  |  |

|                    |         |                               | 1 MHz mode <sup>(1)</sup> |                                                       | 300  | ns    |                                             |  |  |

| IS25 TSU:DAT       | TSU:DAT | Data Input<br>Setup Time      | 100 kHz mode              | 250                                                   | —    | ns    |                                             |  |  |

|                    |         |                               | 400 kHz mode              | 100                                                   | —    | ns    |                                             |  |  |

|                    |         |                               | 1 MHz mode <sup>(1)</sup> | 100                                                   | _    | ns    |                                             |  |  |

| IS26 TH            | THD:DAT | Data Input<br>Hold Time       | 100 kHz mode              | 0                                                     | —    | μS    |                                             |  |  |

|                    |         |                               | 400 kHz mode              | 0                                                     | 0.9  | μS    |                                             |  |  |

|                    |         |                               | 1 MHz mode <sup>(1)</sup> | 0                                                     | 0.3  | μS    |                                             |  |  |

| IS30               | Tsu:sta | Start Condition               | 100 kHz mode              | 4.7                                                   | —    | μS    | Only relevant for Repeated                  |  |  |

|                    |         | Setup Time                    | 400 kHz mode              | 0.6                                                   | —    | μS    | Start condition                             |  |  |

|                    |         |                               | 1 MHz mode <sup>(1)</sup> | 0.25                                                  | —    | μS    |                                             |  |  |

| IS31               | THD:STA | Start Condition               | 100 kHz mode              | 4.0                                                   | —    | μS    | After this period, the first                |  |  |

|                    |         | Hold Time                     | 400 kHz mode              | 0.6                                                   | —    | μS    | clock pulse is generated                    |  |  |

|                    |         |                               | 1 MHz mode <sup>(1)</sup> | 0.25                                                  | —    | μS    |                                             |  |  |

| IS33               | Tsu:sto | Stop Condition                | 100 kHz mode              | 4.7                                                   | —    | μS    |                                             |  |  |

|                    |         |                               | Setup Time                | 400 kHz mode                                          | 0.6  | —     | μS                                          |  |  |

|                    |         |                               | 1 MHz mode <sup>(1)</sup> | 0.6                                                   | _    | μS    |                                             |  |  |

| IS34               | THD:STO | Stop Condition<br>Hold Time   | 100 kHz mode              | 4                                                     | —    | μS    |                                             |  |  |

|                    |         |                               | 400 kHz mode              | 0.6                                                   | —    | μS    |                                             |  |  |

|                    |         |                               | 1 MHz mode <sup>(1)</sup> | 0.25                                                  |      | μS    |                                             |  |  |

| IS40               | TAA:SCL | Output Valid<br>From Clock    | 100 kHz mode              | 0                                                     | 3500 | ns    |                                             |  |  |

|                    |         |                               | 400 kHz mode              | 0                                                     | 1000 | ns    |                                             |  |  |

|                    |         |                               | 1 MHz mode <sup>(1)</sup> | 0                                                     | 350  | ns    |                                             |  |  |

| IS45               | TBF:SDA | Bus Free Time                 | 100 kHz mode              | 4.7                                                   | —    | μS    | Time the bus must be free                   |  |  |

|                    |         |                               | 400 kHz mode              | 1.3                                                   | —    | μS    | before a new transmission                   |  |  |

|                    |         |                               | 1 MHz mode <sup>(1)</sup> | 0.5                                                   |      | μs    | can start                                   |  |  |

| IS50               | Св      | Bus Capacitive Lo             | ading                     | —                                                     | 400  | pF    |                                             |  |  |

| S51                | TPGD    | Pulse Gobbler De              | lay                       | 65                                                    | 390  | ns    | (Note 2)                                    |  |  |

# TABLE 30-50: I2Cx BUS DATA TIMING REQUIREMENTS (SLAVE MODE)

Note 1: Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

**2:** Typical value for this parameter is 130 ns.

**3:** These parameters are characterized, but not tested in manufacturing.

| AC CHARACTERISTICS |        |                                                  | $ \begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)}^{(1)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array} $ |           |         |            |                                                           |  |

|--------------------|--------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------|------------|-----------------------------------------------------------|--|

| Param<br>No.       | Symbol | Min.                                             | Тур.                                                                                                                                                                                                                                                                                          | Max.      | Units   | Conditions |                                                           |  |

|                    |        | ADC A                                            | Accuracy                                                                                                                                                                                                                                                                                      | (12-Bit   | Mode)   |            |                                                           |  |

| AD20a              | Nr     | Resolution                                       | 12                                                                                                                                                                                                                                                                                            | 2 Data Bi | ts      | bits       |                                                           |  |

| AD21a              | INL    | Integral Nonlinearity                            | -2.5                                                                                                                                                                                                                                                                                          |           | 2.5     | LSb        | -40°C ≤ TA ≤ +85°C (Note 2)                               |  |

|                    |        |                                                  | -5.5                                                                                                                                                                                                                                                                                          | _         | 5.5     | LSb        | +85°C < TA ≤ +125°C (Note 2)                              |  |

| AD22a              | DNL    | Differential Nonlinearity                        | -1                                                                                                                                                                                                                                                                                            | —         | 1       | LSb        | -40°C $\leq$ TA $\leq$ +85°C (Note 2)                     |  |

|                    |        |                                                  | -1                                                                                                                                                                                                                                                                                            | —         | 1       | LSb        | +85°C < TA $\leq$ +125°C (Note 2)                         |  |

| AD23a              | Gerr   | Gain Error <sup>(3)</sup>                        | -10                                                                                                                                                                                                                                                                                           | —         | 10      | LSb        | -40°C $\leq$ TA $\leq$ +85°C (Note 2)                     |  |

|                    |        |                                                  | -10                                                                                                                                                                                                                                                                                           | _         | 10      | LSb        | +85°C < TA $\leq$ +125°C (Note 2)                         |  |

| AD24a              | EOFF   | Offset Error                                     | -5                                                                                                                                                                                                                                                                                            | _         | 5       | LSb        | $-40^{\circ}C \leq TA \leq +85^{\circ}C \text{ (Note 2)}$ |  |

|                    |        |                                                  | -5                                                                                                                                                                                                                                                                                            | _         | 5       | LSb        | +85°C < TA $\leq$ +125°C (Note 2)                         |  |

| AD25a              | —      | Monotonicity                                     | —                                                                                                                                                                                                                                                                                             | —         | —       |            | Guaranteed                                                |  |

|                    |        | Dynamic                                          | Performa                                                                                                                                                                                                                                                                                      | ance (12- | Bit Mod | e)         |                                                           |  |

| AD30a              | THD    | Total Harmonic Distortion <sup>(3)</sup>         | _                                                                                                                                                                                                                                                                                             | 75        | _       | dB         |                                                           |  |

| AD31a              | SINAD  | Signal to Noise and<br>Distortion <sup>(3)</sup> | —                                                                                                                                                                                                                                                                                             | 68        | _       | dB         |                                                           |  |

| AD32a              | SFDR   | Spurious Free Dynamic<br>Range <sup>(3)</sup>    | —                                                                                                                                                                                                                                                                                             | 80        | —       | dB         |                                                           |  |

| AD33a              | Fnyq   | Input Signal Bandwidth <sup>(3)</sup>            | —                                                                                                                                                                                                                                                                                             | 250       | —       | kHz        |                                                           |  |

| AD34a              | ENOB   | Effective Number of Bits <sup>(3)</sup>          | 11.09                                                                                                                                                                                                                                                                                         | 11.3      | _       | bits       |                                                           |  |

# TABLE 30-58: ADC MODULE SPECIFICATIONS (12-BIT MODE)

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

2: For all accuracy specifications, VINL = AVSS = VREFL = 0V and AVDD = VREFH = 3.6V.

3: Parameters are characterized but not tested in manufacturing.

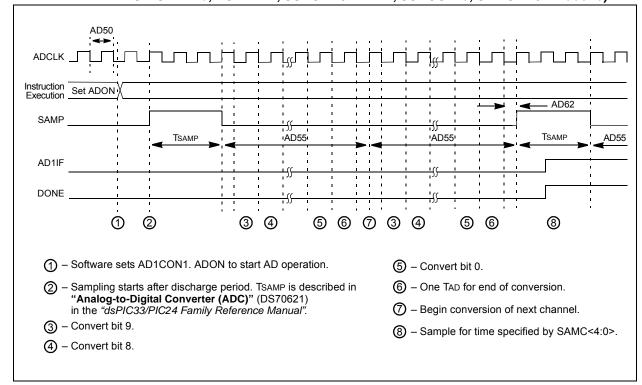

#### FIGURE 30-38: ADC CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS (CHPS<1:0> = 01, SIMSAM = 0, ASAM = 1, SSRC<2:0> = 111, SSRCG = 0, SAMC<4:0> = 00010)

DS70000657H-page 464

NOTES:

48-Lead Plastic Ultra Thin Quad Flat, No Lead Package (MV) – 6x6x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | MILLIMETERS      |          |           |      |  |  |  |

|------------------------|------------------|----------|-----------|------|--|--|--|

| Dimension              | Dimension Limits |          |           | MAX  |  |  |  |

| Number of Pins         | N                | 48       |           |      |  |  |  |

| Pitch                  | е                |          | 0.40 BSC  |      |  |  |  |

| Overall Height         | Α                | 0.45     | 0.50      | 0.55 |  |  |  |

| Standoff               | A1               | 0.00     | 0.02      | 0.05 |  |  |  |

| Contact Thickness      | A3               |          | 0.127 REF |      |  |  |  |

| Overall Width          | E                | 6.00 BSC |           |      |  |  |  |

| Exposed Pad Width      | E2               | 4.45     | 4.60      | 4.75 |  |  |  |

| Overall Length         | D                | 6.00 BSC |           |      |  |  |  |

| Exposed Pad Length     | D2               | 4.45     | 4.60      | 4.75 |  |  |  |

| Contact Width          | b                | 0.15     | 0.20      | 0.25 |  |  |  |

| Contact Length         | L                | 0.30     | 0.40      | 0.50 |  |  |  |

| Contact-to-Exposed Pad | K                | 0.20     | -         | -    |  |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-153A Sheet 2 of 2

NOTES: