Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 512KB (170K x 24)                                                               |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 24K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 9x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 44-QFN (8x8)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep512gp204t-i-ml |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name <sup>(4)</sup>                        | Pin<br>Type         | Buffer<br>Type          | PPS              | Description                                                                                                                                                                        |

|------------------------------------------------|---------------------|-------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AN0-AN15                                       | I                   | Analog                  | No               | Analog input channels.                                                                                                                                                             |

| CLKI                                           | I                   | ST/<br>CMOS             | No               | External clock source input. Always associated with OSC1 pin function                                                                                                              |

| CLKO                                           | 0                   | —                       | No               | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes. Always associated with OSC2 pin function. |

| OSC1                                           | I                   | ST/                     | No               | Oscillator crystal input. ST buffer when configured in RC mode; CMOS                                                                                                               |

| OSC2                                           | I/O                 | CMOS<br>—               | No               | otherwise.<br>Oscillator crystal output. Connects to crystal or resonator in Crystal<br>Oscillator mode. Optionally functions as CLKO in RC and EC modes.                          |

| REFCLKO                                        | 0                   |                         | Yes              | Reference clock output.                                                                                                                                                            |

| IC1-IC4                                        | Ι                   | ST                      | Yes              | Capture Inputs 1 through 4.                                                                                                                                                        |

| OCFA<br>OCFB<br>OC1-OC4                        | <br> <br> <br>0     | ST<br>ST                | Yes<br>No<br>Yes | Compare Fault A input (for Compare channels).<br>Compare Fault B input (for Compare channels).<br>Compare Outputs 1 through 4.                                                     |

| INT0                                           | I                   | ST                      | No               | External Interrupt 0.                                                                                                                                                              |

| INT1<br>INT2                                   |                     | ST<br>ST                | Yes<br>Yes       | External Interrupt 1.<br>External Interrupt 2.                                                                                                                                     |

| RA0-RA4, RA7-RA12                              | I/O                 | ST                      | No               | PORTA is a bidirectional I/O port.                                                                                                                                                 |

| RB0-RB15                                       | I/O                 | ST                      | No               | PORTB is a bidirectional I/O port.                                                                                                                                                 |

| RC0-RC13, RC15                                 | I/O                 | ST                      | No               | PORTC is a bidirectional I/O port.                                                                                                                                                 |

| RD5, RD6, RD8                                  | I/O                 | ST                      | No               | PORTD is a bidirectional I/O port.                                                                                                                                                 |

| RE12-RE15                                      | I/O                 | ST                      | No               | PORTE is a bidirectional I/O port.                                                                                                                                                 |

| RF0, RF1                                       | I/O                 | ST                      | No               | PORTF is a bidirectional I/O port.                                                                                                                                                 |

| RG6-RG9                                        | I/O                 | ST                      | No               | PORTG is a bidirectional I/O port.                                                                                                                                                 |

| T1CK                                           | Ι                   | ST                      | No               | Timer1 external clock input.                                                                                                                                                       |

| T2CK<br>T3CK                                   |                     | ST<br>ST                | Yes              | Timer2 external clock input.                                                                                                                                                       |

| T4CK                                           |                     | ST                      | No<br>No         | Timer3 external clock input.<br>Timer4 external clock input.                                                                                                                       |

| T5CK                                           | i                   | ST                      | No               | Timer5 external clock input.                                                                                                                                                       |

| CTPLS                                          | 0                   | ST                      | No               | CTMU pulse output.                                                                                                                                                                 |

| CTED1                                          | Ι                   | ST                      | No               | CTMU External Edge Input 1.                                                                                                                                                        |

| CTED2                                          | Ι                   | ST                      | No               | CTMU External Edge Input 2.                                                                                                                                                        |

| U1CTS                                          | Ι                   | ST                      | No               | UART1 Clear-To-Send.                                                                                                                                                               |

| U1RTS                                          | 0                   |                         | No               | UART1 Ready-To-Send.                                                                                                                                                               |

| U1RX                                           |                     | ST                      | Yes              | UART1 receive.<br>UART1 transmit.                                                                                                                                                  |

| U1TX<br>BCLK1                                  | 0                   | ST                      | Yes<br>No        | UART1 Iransmit.<br>UART1 IrDA <sup>®</sup> baud clock output.                                                                                                                      |

| Legend: CMOS = CM<br>ST = Schmi<br>PPS = Perip | MOS co<br>itt Trigg | ompatible<br>er input v | input<br>with CN | or output Analog = Analog input P = Power                                                                                                                                          |

# TABLE 1-1:PINOUT I/O DESCRIPTIONS

Note 1: This pin is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This pin is available on dsPIC33EPXXXGP/MC50X devices only.

3: This is the default Fault on Reset for dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices. See Section 16.0 "High-Speed PWM Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)" for more information.

4: Not all pins are available in all packages variants. See the "Pin Diagrams" section for pin availability.

**5:** There is an internal pull-up resistor connected to the TMS pin when the JTAG interface is active. See the JTAGEN bit field in Table 27-2.

# 2.5 ICSP Pins

The PGECx and PGEDx pins are used for ICSP and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes, and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin Voltage Input High (VIH) and Voltage Input Low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> PICkit<sup>™</sup> 3, MPLAB ICD 3, or MPLAB REAL ICE<sup>™</sup>.

For more information on MPLAB ICD 2, ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site.

- "Using MPLAB<sup>®</sup> ICD 3" (poster) DS51765

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" DS51764

- "MPLAB<sup>®</sup> REAL ICE<sup>™</sup> In-Circuit Emulator User's Guide" DS51616

- "Using MPLAB<sup>®</sup> REAL ICE™ In-Circuit Emulator" (poster) DS51749

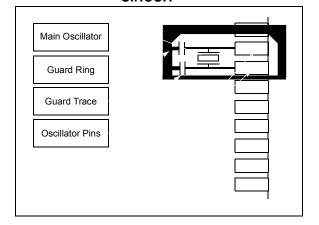

### 2.6 External Oscillator Pins

Many DSCs have options for at least two oscillators: a high-frequency Primary Oscillator and a low-frequency Secondary Oscillator. For details, see **Section 9.0 "Oscillator Configuration"** for details.

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is shown in Figure 2-3.

#### SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

### TABLE 4-52: PORTG REGISTER MAP FOR PIC24EPXXXGP/MC206 AND dsPIC33EPXXXGP/MC206/506 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|---------------|

| TRISG        | 0E60  | _      | -      | _      | _      | -      | -      | TRISG9 | TRISG8 | TRISG7 | TRISG6 | _     | _     | _     | _     | _     | -     | 03C0          |

| PORTG        | 0E62  |        |        | -      | _      | _      | _      | RG9    | RG8    | RG7    | RG6    | _     | _     | _     | _     | _     | _     | xxxx          |

| LATG         | 0E64  |        |        | -      | _      | _      | _      | LATG9  | LATG8  | LATG7  | LATG6  | _     | _     | _     | _     | _     | _     | xxxx          |

| ODCG         | 0E66  |        |        | -      | _      | _      | _      | ODCG9  | ODCG8  | ODCG7  | ODCG6  | _     | _     | _     | _     | _     | _     | 0000          |

| CNENG        | 0E68  |        |        | -      | _      | _      | _      | CNIEG9 | CNIEG8 | CNIEG7 | CNIEG6 | _     | _     | _     | _     | _     | _     | 0000          |

| CNPUG        | 0E6A  |        |        | -      | _      | _      | _      | CNPUG9 | CNPUG8 | CNPUG7 | CNPUG6 | _     | _     | _     | _     | _     | _     | 0000          |

| CNPDG        | 0E6C  | _      | -      | _      | _      |        |        | CNPDG9 | CNPDG8 | CNPDG7 | CNPDG6 | _     | _     | -     | _     | _     |       | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-56: PORTA REGISTER MAP FOR PIC24EPXXXGP/MC203 AND dsPIC33EPXXXGP/MC203/503 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|--------|-------|-------|-------|--------|--------|--------|--------|--------|---------------|

| TRISA        | 0E00  | _      | _      | _      | _      |        | _      | _     | TRISA8 | _     | —     | —     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 011F          |

| PORTA        | 0E02  | _      | _      | _      | _      | _      | _      | _     | RA8    | _     | _     | _     | RA4    | RA3    | RA2    | RA1    | RA0    | 0000          |

| LATA         | 0E04  | _      | _      | _      | _      | _      | _      | _     | LATA8  | _     | _     | _     | LATA4  | LATA3  | LATA2  | LA1TA1 | LA0TA0 | 0000          |

| ODCA         | 0E06  | _      | _      | _      | _      | _      | _      | _     | ODCA8  | _     | _     | _     | ODCA4  | ODCA3  | ODCA2  | ODCA1  | ODCA0  | 0000          |

| CNENA        | 0E08  | _      | _      | _      | _      | _      | _      | _     | CNIEA8 | _     | _     | _     | CNIEA4 | CNIEA3 | CNIEA2 | CNIEA1 | CNIEA0 | 0000          |

| CNPUA        | 0E0A  | _      | _      | _      | _      | _      | _      | _     | CNPUA8 | _     | _     | _     | CNPUA4 | CNPUA3 | CNPUA2 | CNPUA1 | CNPUA0 | 0000          |

| CNPDA        | 0E0C  | _      | _      | _      | _      | _      | _      | _     | CNPDA8 | _     | _     | _     | CNPDA4 | CNPDA3 | CNPDA2 | CNPDA1 | CNPDA0 | 0000          |

| ANSELA       | 0E0E  | _      | —      | _      | —      | _      | —      | _     | —      | _     | —     | —     | ANSA4  | —      | —      | ANSA1  | ANSA0  | 0013          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-57: PORTB REGISTER MAP FOR PIC24EPXXXGP/MC203 AND dsPIC33EPXXXGP/MC203/503 DEVICES ONLY

| File<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISB        | 0E10  | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF          |

| PORTB        | 0E12  | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx          |

| LATB         | 0E14  | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | xxxx          |

| ODCB         | 0E16  | ODCB15  | ODCB14  | ODCB13  | ODCB12  | ODCB11  | ODCB10  | ODCB9  | ODCB8  | ODCB7  | ODCB6  | ODCB5  | ODCB4  | ODCB3  | ODCB2  | ODCB1  | ODCB0  | 0000          |

| CNENB        | 0E18  | CNIEB15 | CNIEB14 | CNIEB13 | CNIEB12 | CNIEB11 | CNIEB10 | CNIEB9 | CNIEB8 | CNIEB7 | CNIEB6 | CNIEB5 | CNIEB4 | CNIEB3 | CNIEB2 | CNIEB1 | CNIEB0 | 0000          |

| CNPUB        | 0E1A  | CNPUB15 | CNPUB14 | CNPUB13 | CNPUB12 | CNPUB11 | CNPUB10 | CNPUB9 | CNPUB8 | CNPUB7 | CNPUB6 | CNPUB5 | CNPUB4 | CNPUB3 | CNPUB2 | CNPUB1 | CNPUB0 | 0000          |

| CNPDB        | 0E1C  | CNPDB15 | CNPDB14 | CNPDB13 | CNPDB12 | CNPDB11 | CNPDB10 | CNPDB9 | CNPDB8 | CNPDB7 | CNPDB6 | CNPDB5 | CNPDB4 | CNPDB3 | CNPDB2 | CNPDB1 | CNPDB0 | 0000          |

| ANSELB       | 0E1E  | _       | _       | -       | _       | -       | —       | -      | ANSB8  | _      | _      | _      | _      | ANSB3  | ANSB2  | ANSB1  | ANSB0  | 010F          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-58: PORTC REGISTER MAP FOR PIC24EPXXXGP/MC203 AND dsPIC33EPXXXGP/MC203/503 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|--------|-------|-------|-------|-------|-------|-------|--------|--------|---------------|

| TRISC        | 0E20  | _      | _      | _      | _      | _      | —      | —     | TRISC8 | _     | _     |       | _     |       | -     | TRISC1 | TRISC0 | 0103          |

| PORTC        | 0E22  |        |        | -      | -      | -      | —      | _     | RC8    | —     | -     |       | _     |       |       | RC1    | RC0    | xxxx          |

| LATC         | 0E24  |        |        | _      | _      | _      | _      | _     | LATC8  | _     | _     | _     | _     | _     | _     | LATC1  | LATC0  | xxxx          |

| ODCC         | 0E26  |        |        | _      | _      | _      | _      | _     | ODCC8  | _     | _     | _     | _     | _     | _     | ODCC1  | ODCC0  | 0000          |

| CNENC        | 0E28  | —      | _      | -      | _      |        | _      | _     | CNIEC8 | —     |       |       | _     |       |       | CNIEC1 | CNIEC0 | 0000          |

| CNPUC        | 0E2A  |        |        | _      | _      | _      | _      | _     | CNPUC8 | _     | _     | _     | _     | _     | _     | CNPUC1 | CNPUC0 | 0000          |

| CNPDC        | 0E2C  |        |        | _      | _      | _      | _      | _     | CNPDC8 | _     | _     | _     | _     | _     | _     | CNPDC1 | CNPDC0 | 0000          |

| ANSELC       | 0E2E  | -      | _      | _      | _      | _      | —      | —     | —      | —     |       | _     | _     | _     |       | ANSC1  | ANSC0  | 0003          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### REGISTER 9-2: CLKDIV: CLOCK DIVISOR REGISTER (CONTINUED)

- **Note 1:** The DOZE<2:0> bits can only be written to when the DOZEN bit is clear. If DOZEN = 1, any writes to DOZE<2:0> are ignored.

- $\label{eq:constraint} \textbf{2:} \quad \text{This bit is cleared when the ROI bit is set and an interrupt occurs.}$

- **3:** The DOZEN bit cannot be set if DOZE<2:0> = 000. If DOZE<2:0> = 000, any attempt by user software to set the DOZEN bit is ignored.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

|                 |     |                  |     |                   | UNIRUL RE       |                 |       |

|-----------------|-----|------------------|-----|-------------------|-----------------|-----------------|-------|

| U-0             | U-0 | U-0              | U-0 | U-0               | R/W-0           | U-0             | U-0   |

| —               | _   | —                | —   | —                 | CMPMD           | —               | —     |

| bit 15          |     |                  |     |                   |                 |                 | bit 8 |

|                 |     |                  |     |                   |                 |                 |       |

| R/W-0           | U-0 | U-0              | U-0 | U-0               | U-0             | R/W-0           | U-0   |

| CRCMD           | —   | —                | _   | —                 | —               | I2C2MD          | —     |

| bit 7           |     |                  |     |                   |                 |                 | bit C |

|                 |     |                  |     |                   |                 |                 |       |

| Legend:         |     |                  |     |                   |                 |                 |       |

| R = Readable    | bit | W = Writable I   | bit | U = Unimplem      | ented bit, read | l as '0'        |       |

| -n = Value at F | POR | '1' = Bit is set |     | '0' = Bit is clea | ared            | x = Bit is unkn | own   |

### REGISTER 10-3: PMD3: PERIPHERAL MODULE DISABLE CONTROL REGISTER 3

| bit 10  | CMPMD: Comparator Module Disable bit |

|---------|--------------------------------------|

|         | 1 = Comparator module is disabled    |

|         | 0 = Comparator module is enabled     |

| bit 9-8 | Unimplemented: Read as '0'           |

| bit 7   | CRCMD: CRC Module Disable bit        |

|         | 1 = CRC module is disabled           |

|         | 0 = CRC module is enabled            |

| bit 6-2 | Unimplemented: Read as '0'           |

| bit 1   | I2C2MD: I2C2 Module Disable bit      |

|         | 1 = I2C2 module is disabled          |

|         | 0 = I2C2 module is enabled           |

| bit 0   | Unimplemented: Read as '0'           |

|         |                                      |

### REGISTER 10-4: PMD4: PERIPHERAL MODULE DISABLE CONTROL REGISTER 4

|        | -   |     |     |        |        |     |       |

|--------|-----|-----|-----|--------|--------|-----|-------|

| U-0    | U-0 | U-0 | U-0 | U-0    | U-0    | U-0 | U-0   |

| —      | —   |     |     | —      | —      | —   | —     |

| bit 15 |     |     |     |        |        |     | bit 8 |

|        |     |     |     |        |        |     |       |

| U-0    | U-0 | U-0 | U-0 | R/W-0  | R/W-0  | U-0 | U-0   |

| —      | —   | —   | —   | REFOMD | CTMUMD | —   | —     |

| bit 7  |     |     |     |        |        |     | bit 0 |

|        |     |     |     |        |        |     |       |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-4 | Unimplemented: Read as '0'                                 |

|----------|------------------------------------------------------------|

| bit 3    | <b>REFOMD:</b> Reference Clock Module Disable bit          |

|          | <ol> <li>1 = Reference clock module is disabled</li> </ol> |

|          | 0 = Reference clock module is enabled                      |

| bit 2    | CTMUMD: CTMU Module Disable bit                            |

|          | 1 = CTMU module is disabled                                |

|          | 0 = CTMU module is enabled                                 |

| bit 1-0  | Unimplemented: Read as '0'                                 |

$\ensuremath{\textcircled{}^\circ}$  2011-2013 Microchip Technology Inc.

| Input Name <sup>(1)</sup>                   | Function Name | Register | Configuration Bits |

|---------------------------------------------|---------------|----------|--------------------|

| External Interrupt 1                        | INT1          | RPINR0   | INT1R<6:0>         |

| External Interrupt 2                        | INT2          | RPINR1   | INT2R<6:0>         |

| Timer2 External Clock                       | T2CK          | RPINR3   | T2CKR<6:0>         |

| Input Capture 1                             | IC1           | RPINR7   | IC1R<6:0>          |

| Input Capture 2                             | IC2           | RPINR7   | IC2R<6:0>          |

| Input Capture 3                             | IC3           | RPINR8   | IC3R<6:0>          |

| Input Capture 4                             | IC4           | RPINR8   | IC4R<6:0>          |

| Output Compare Fault A                      | OCFA          | RPINR11  | OCFAR<6:0>         |

| PWM Fault 1 <sup>(3)</sup>                  | FLT1          | RPINR12  | FLT1R<6:0>         |

| PWM Fault 2 <sup>(3)</sup>                  | FLT2          | RPINR12  | FLT2R<6:0>         |

| QEI1 Phase A <sup>(3)</sup>                 | QEA1          | RPINR14  | QEA1R<6:0>         |

| QEI1 Phase B <sup>(3)</sup>                 | QEB1          | RPINR14  | QEB1R<6:0>         |

| QEI1 Index <sup>(3)</sup>                   | INDX1         | RPINR15  | INDX1R<6:0>        |

| QEI1 Home <sup>(3)</sup>                    | HOME1         | RPINR15  | HOM1R<6:0>         |

| UART1 Receive                               | U1RX          | RPINR18  | U1RXR<6:0>         |

| UART2 Receive                               | U2RX          | RPINR19  | U2RXR<6:0>         |

| SPI2 Data Input                             | SDI2          | RPINR22  | SDI2R<6:0>         |

| SPI2 Clock Input                            | SCK2          | RPINR22  | SCK2R<6:0>         |

| SPI2 Slave Select                           | SS2           | RPINR23  | SS2R<6:0>          |

| CAN1 Receive <sup>(2)</sup>                 | C1RX          | RPINR26  | C1RXR<6:0>         |

| PWM Sync Input 1 <sup>(3)</sup>             | SYNCI1        | RPINR37  | SYNCI1R<6:0>       |

| PWM Dead-Time Compensation 1 <sup>(3)</sup> | DTCMP1        | RPINR38  | DTCMP1R<6:0>       |

| PWM Dead-Time Compensation 2 <sup>(3)</sup> | DTCMP2        | RPINR39  | DTCMP2R<6:0>       |

| PWM Dead-Time Compensation 3 <sup>(3)</sup> | DTCMP3        | RPINR39  | DTCMP3R<6:0>       |

# TABLE 11-1: SELECTABLE INPUT SOURCES (MAPS INPUT TO FUNCTION)

**Note 1:** Unless otherwise noted, all inputs use the Schmitt Trigger input buffers.

2: This input source is available on dsPIC33EPXXXGP/MC50X devices only.

3: This input source is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

# 12.2 Timer1 Control Register

| R/W-0              | U-0                                         | R/W-0                             | U-0                       | U-0              | U-0                      | U-0                | U-0                |  |  |  |

|--------------------|---------------------------------------------|-----------------------------------|---------------------------|------------------|--------------------------|--------------------|--------------------|--|--|--|

| TON <sup>(1)</sup> | —                                           | TSIDL                             | —                         | _                | —                        | _                  | _                  |  |  |  |

| bit 15             |                                             |                                   |                           |                  |                          |                    | bit 8              |  |  |  |

|                    |                                             |                                   |                           |                  |                          |                    |                    |  |  |  |

| U-0                | R/W-0                                       | R/W-0                             | R/W-0                     | U-0              | R/W-0                    | R/W-0              | U-0                |  |  |  |

|                    | TGATE                                       | TCKPS1                            | TCKPS0                    | _                | TSYNC <sup>(1)</sup>     | TCS <sup>(1)</sup> |                    |  |  |  |

| bit 7              |                                             |                                   |                           |                  |                          |                    | bit (              |  |  |  |

| Legend:            |                                             |                                   |                           |                  |                          |                    |                    |  |  |  |

| R = Readable       | e bit                                       | W = Writable                      | bit                       | U = Unimplei     | mented bit, read         | l as '0'           |                    |  |  |  |

| -n = Value at      | POR                                         | '1' = Bit is set                  |                           | '0' = Bit is cle | ared                     | x = Bit is unkno   | own                |  |  |  |

|                    |                                             | o                                 |                           |                  |                          |                    |                    |  |  |  |

| bit 15             | <b>TON:</b> Timer1<br>1 = Starts 16-        |                                   |                           |                  |                          |                    |                    |  |  |  |

|                    | 0 = Stops 16-                               |                                   |                           |                  |                          |                    |                    |  |  |  |

| bit 14             | Unimplemen                                  | ted: Read as '                    | 0'                        |                  |                          |                    |                    |  |  |  |

| bit 13             | TSIDL: Timer                                | 1 Stop in Idle N                  | /lode bit                 |                  |                          |                    |                    |  |  |  |

|                    |                                             | ues module op                     |                           |                  | ldle mode                |                    |                    |  |  |  |

|                    | 0 = Continues module operation in Idle mode |                                   |                           |                  |                          |                    |                    |  |  |  |

| bit 12-7           | -                                           | ted: Read as '                    |                           |                  |                          |                    |                    |  |  |  |

| bit 6              |                                             | r1 Gated Time                     | Accumulation              | h Enable bit     |                          |                    |                    |  |  |  |

|                    | When TCS =<br>This bit is igno              |                                   |                           |                  |                          |                    |                    |  |  |  |

|                    | When TCS =                                  |                                   |                           |                  |                          |                    |                    |  |  |  |

|                    |                                             | e accumulatio                     |                           |                  |                          |                    |                    |  |  |  |

|                    |                                             | e accumulatio                     |                           | 0.1.1.1.1.1      |                          |                    |                    |  |  |  |

| bit 5-4            |                                             | : Timer1 Input                    | Clock Prescal             | e Select bits    |                          |                    |                    |  |  |  |

|                    | 11 = 1:256<br>10 = 1:64                     |                                   |                           |                  |                          |                    |                    |  |  |  |

|                    | 01 = 1:8                                    |                                   |                           |                  |                          |                    |                    |  |  |  |

|                    | 00 = 1:1                                    |                                   |                           |                  |                          |                    |                    |  |  |  |

| bit 3              | -                                           | ted: Read as '                    |                           |                  |                          |                    |                    |  |  |  |

| bit 2              |                                             | er1 External Clo                  | ock Input Synd            | chronization S   | elect bit <sup>(1)</sup> |                    |                    |  |  |  |

|                    | When TCS =                                  |                                   |                           |                  |                          |                    |                    |  |  |  |

|                    |                                             | izes external c<br>synchronize e> |                           | nut              |                          |                    |                    |  |  |  |

|                    | When TCS =                                  | •                                 |                           | iput             |                          |                    |                    |  |  |  |

|                    | This bit is igno                            |                                   |                           |                  |                          |                    |                    |  |  |  |

| bit 1              | TCS: Timer1                                 | Clock Source S                    | Select bit <sup>(1)</sup> |                  |                          |                    |                    |  |  |  |

|                    | 1 = External c<br>0 = Internal cl           | clock is from pi<br>ock (FP)      | n, T1CK (on th            | ne rising edge)  | •                        |                    |                    |  |  |  |

| bit 0              | Unimplemen                                  | ted: Read as '                    | 0'                        |                  |                          |                    |                    |  |  |  |

|                    | nen Timer1 is er<br>empts by user s         |                                   |                           |                  |                          | SYNC = 1, TON      | <b>\ =</b> 1), any |  |  |  |

### REGISTER 12-1: T1CON: TIMER1 CONTROL REGISTER

© 2011-2013 Microchip Technology Inc.

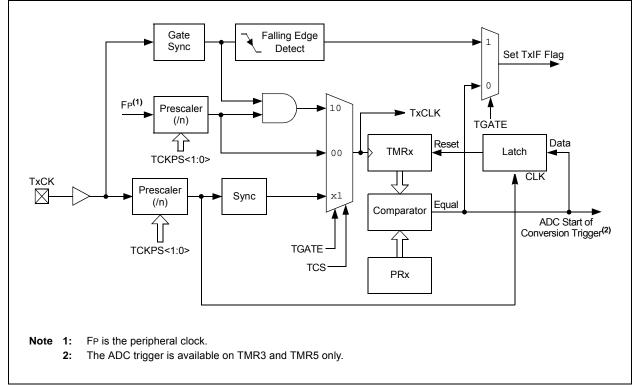

### FIGURE 13-2: TYPE C TIMER BLOCK DIAGRAM (x = 3 AND 5)

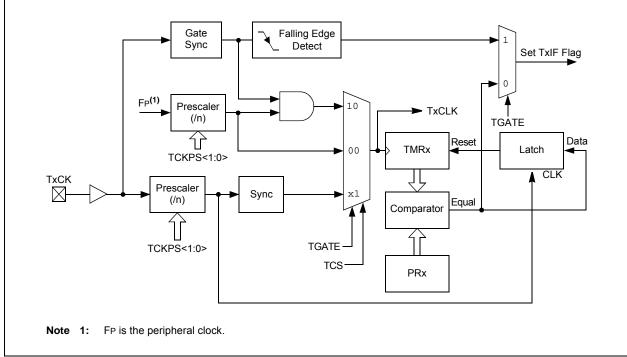

# FIGURE 13-1:TYPE B TIMER BLOCK DIAGRAM (x = 2 AND 4)

# 17.1 QEI Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this UDL increases |

|-------|---------------------------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                                               |

|       | http://www.microchip.com/wwwproducts/                                                                   |

|       | Devices.aspx?dDocName=en555464                                                                          |

### 17.1.1 KEY RESOURCES

- "Quadrature Encoder Interface" (DS70601) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

|               | 23-2: Al                                                                                                                               | DICONZ. ADCI                                         | CONTROL REG           | ISIER Z         |                   |                 |               |  |  |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-----------------------|-----------------|-------------------|-----------------|---------------|--|--|--|

| R/W-0         | R/W-                                                                                                                                   | 0 R/W-0                                              | U-0                   | U-0             | R/W-0             | R/W-0           | R/W-0         |  |  |  |

| VCFG2         | VCFO                                                                                                                                   | G1 VCFG0                                             | —                     | —               | CSCNA             | CHPS1           | CHPS0         |  |  |  |

| bit 15        |                                                                                                                                        |                                                      |                       |                 |                   |                 | bit           |  |  |  |

| R-0           | R/W-                                                                                                                                   | 0 R/W-0                                              | R/W-0                 | R/W-0           | R/W-0             | R/W-0           | R/W-0         |  |  |  |

| BUFS          | SMP                                                                                                                                    |                                                      | SMPI2                 | SMPI1           | SMPI0             | BUFM            | ALTS          |  |  |  |

| bit 7         | OWIT                                                                                                                                   |                                                      |                       |                 |                   | Borim           | bit           |  |  |  |

| Legend:       |                                                                                                                                        |                                                      |                       |                 |                   |                 |               |  |  |  |

| R = Readable  | , hit                                                                                                                                  | W = Writable                                         | bit I                 | l – Llnimolo    | monted hit rea    | d oo 'O'        |               |  |  |  |

|               |                                                                                                                                        |                                                      |                       |                 | mented bit, read  |                 |               |  |  |  |

| -n = Value at | POR                                                                                                                                    | '1' = Bit is se                                      | t 't                  | )' = Bit is cle | eared             | x = Bit is unkr | nown          |  |  |  |

| bit 15-13     | VCFG<2                                                                                                                                 | 2:0>: Converter Vol                                  | tage Reference C      | onfiguration    | bits              |                 |               |  |  |  |

|               | Value                                                                                                                                  | VREFH                                                | VREFL                 |                 |                   |                 |               |  |  |  |

|               | 000                                                                                                                                    | Avdd                                                 | Avss                  |                 |                   |                 |               |  |  |  |

|               | 001                                                                                                                                    | External VREF+                                       | Avss                  |                 |                   |                 |               |  |  |  |

|               | 010                                                                                                                                    | Avdd                                                 | External VREF-        |                 |                   |                 |               |  |  |  |

|               | 011                                                                                                                                    | External VREF+                                       | External VREF-        |                 |                   |                 |               |  |  |  |

|               | 1xx                                                                                                                                    | Avdd                                                 | Avss                  |                 |                   |                 |               |  |  |  |

| bit 12-11     | Unimple                                                                                                                                | emented: Read as                                     | ʻ0'                   |                 |                   |                 |               |  |  |  |

| bit 10        | CSCNA: Input Scan Select bit                                                                                                           |                                                      |                       |                 |                   |                 |               |  |  |  |

|               | 1 = Scans inputs for CH0+ during Sample MUXA                                                                                           |                                                      |                       |                 |                   |                 |               |  |  |  |

|               | 0 = Does                                                                                                                               | s not scan inputs                                    | <b>C</b> .            |                 |                   |                 |               |  |  |  |

| bit 9-8       | CHPS<1:0>: Channel Select bits                                                                                                         |                                                      |                       |                 |                   |                 |               |  |  |  |

|               | In 12-bit mode (AD21B = 1), the CHPS<1:0> bits are Unimplemented and are Read as '0':                                                  |                                                      |                       |                 |                   |                 |               |  |  |  |

|               |                                                                                                                                        | nverts CH0, CH1, C                                   |                       |                 |                   |                 |               |  |  |  |

|               |                                                                                                                                        | nverts CH0 and CH<br>nverts CH0                      | 11                    |                 |                   |                 |               |  |  |  |

| bit 7         |                                                                                                                                        | Buffer Fill Status bit                               | (oply valid when F    |                 |                   |                 |               |  |  |  |

|               |                                                                                                                                        |                                                      |                       |                 | ne user applicat  | ion should acco | ee data in th |  |  |  |

|               | 1 = ADC is currently filling the second half of the buffer; the user application should access data in the<br>first half of the buffer |                                                      |                       |                 |                   |                 |               |  |  |  |

|               |                                                                                                                                        | C is currently filling                               | the first half of the | e buffer; the   | e user applicatio | on should acce  | ss data in th |  |  |  |

|               | seco                                                                                                                                   | ond half of the buffe                                | er                    |                 |                   |                 |               |  |  |  |

| bit 6-2       | SMPI<4                                                                                                                                 | :0>: Increment Rate                                  | e bits                |                 |                   |                 |               |  |  |  |

|               | When ADDMAEN = 0:                                                                                                                      |                                                      |                       |                 |                   |                 |               |  |  |  |

|               | x1111 = Generates interrupt after completion of every 16th sample/conversion operation                                                 |                                                      |                       |                 |                   |                 |               |  |  |  |

|               | x1110 = Generates interrupt after completion of every 15th sample/conversion operation                                                 |                                                      |                       |                 |                   |                 |               |  |  |  |

|               |                                                                                                                                        |                                                      |                       |                 |                   |                 |               |  |  |  |

|               | •                                                                                                                                      |                                                      |                       |                 |                   |                 |               |  |  |  |

|               | x0001 = Generates interrupt after completion of every 2nd sample/conversion operation                                                  |                                                      |                       |                 |                   |                 |               |  |  |  |

|               | x0000 = Generates interrupt after completion of every sample/conversion operation                                                      |                                                      |                       |                 |                   |                 |               |  |  |  |

|               |                                                                                                                                        | $\frac{\text{DDMAEN} = 1}{\text{Increments the DN}}$ | 1A address after a    | omplotion o     | of overy 32nd s   | mplo/convorsi   | on operation  |  |  |  |

|               |                                                                                                                                        | Increments the DN                                    |                       |                 |                   |                 |               |  |  |  |

|               | •                                                                                                                                      |                                                      |                       |                 |                   |                 |               |  |  |  |

|               | •                                                                                                                                      |                                                      |                       |                 |                   |                 |               |  |  |  |

|               | •                                                                                                                                      |                                                      |                       |                 |                   | ., .            |               |  |  |  |

|               | 00001 -                                                                                                                                | Increments the DI                                    | "A address offer a    | omplation o     | t avany 2nd aar   |                 |               |  |  |  |

#### . . ACOND. ADCA CONTROL DECISTED 2

# **REGISTER 24-3: PTGBTE: PTG BROADCAST TRIGGER ENABLE REGISTER**<sup>(1,2)</sup> (CONTINUED)

| bit 4 | OC1CS: Clock Source for OC1 bit                                                                                                                                                                |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Generates clock pulse when the broadcast command is executed</li> <li>0 = Does not generate clock pulse when the broadcast command is executed</li> </ul>                         |

| bit 3 | OC4TSS: Trigger/Synchronization Source for OC4 bit                                                                                                                                             |

|       | <ul> <li>1 = Generates Trigger/Synchronization when the broadcast command is executed</li> <li>0 = Does not generate Trigger/Synchronization when the broadcast command is executed</li> </ul> |

| bit 2 | OC3TSS: Trigger/Synchronization Source for OC3 bit                                                                                                                                             |

|       | <ul> <li>1 = Generates Trigger/Synchronization when the broadcast command is executed</li> <li>0 = Does not generate Trigger/Synchronization when the broadcast command is executed</li> </ul> |

| bit 1 | OC2TSS: Trigger/Synchronization Source for OC2 bit                                                                                                                                             |

|       | <ul> <li>1 = Generates Trigger/Synchronization when the broadcast command is executed</li> <li>0 = Does not generate Trigger/Synchronization when the broadcast command is executed</li> </ul> |

| bit 0 | OC1TSS: Trigger/Synchronization Source for OC1 bit                                                                                                                                             |

|       | <ul> <li>1 = Generates Trigger/Synchronization when the broadcast command is executed</li> <li>0 = Does not generate Trigger/Synchronization when the broadcast command is executed</li> </ul> |

|       |                                                                                                                                                                                                |

- **Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

- 2: This register is only used with the PTGCTRL OPTION = 1111 Step command.

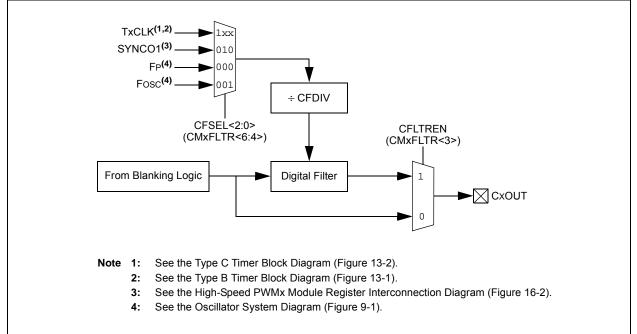

### DIGITAL FILTER INTERCONNECT BLOCK DIAGRAM

| Bit Field              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GCP                    | General Segment Code-Protect bit<br>1 = User program memory is not code-protected<br>0 = Code protection is enabled for the entire program memory space                                                                                                                                                                                                                                                                                     |

| GWRP                   | General Segment Write-Protect bit<br>1 = User program memory is not write-protected<br>0 = User program memory is write-protected                                                                                                                                                                                                                                                                                                           |

| IESO                   | <ul> <li>Two-Speed Oscillator Start-up Enable bit</li> <li>1 = Start up device with FRC, then automatically switch to the user-selected oscillator source when ready</li> <li>0 = Start up device with user-selected oscillator source</li> </ul>                                                                                                                                                                                           |

| PWMLOCK <sup>(1)</sup> | PWM Lock Enable bit<br>1 = Certain PWM registers may only be written after a key sequence<br>0 = PWM registers may be written without a key sequence                                                                                                                                                                                                                                                                                        |

| FNOSC<2:0>             | Oscillator Selection bits<br>111 = Fast RC Oscillator with Divide-by-N (FRCDIVN)<br>110 = Fast RC Oscillator with Divide-by-16 (FRCDIV16)<br>101 = Low-Power RC Oscillator (LPRC)<br>100 = Reserved; do not use<br>011 = Primary Oscillator with PLL module (XT + PLL, HS + PLL, EC + PLL)<br>010 = Primary Oscillator (XT, HS, EC)<br>001 = Fast RC Oscillator with Divide-by-N with PLL module (FRCPLL)<br>000 = Fast RC Oscillator (FRC) |

| FCKSM<1:0>             | Clock Switching Mode bits<br>1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled<br>01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled<br>00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled                                                                                                                                                                                           |

| IOL1WAY                | Peripheral Pin Select Configuration bit<br>1 = Allow only one reconfiguration<br>0 = Allow multiple reconfigurations                                                                                                                                                                                                                                                                                                                        |

| OSCIOFNC               | OSC2 Pin Function bit (except in XT and HS modes)<br>1 = OSC2 is the clock output<br>0 = OSC2 is a general purpose digital I/O pin                                                                                                                                                                                                                                                                                                          |

| POSCMD<1:0>            | Primary Oscillator Mode Select bits<br>11 = Primary Oscillator is disabled<br>10 = HS Crystal Oscillator mode<br>01 = XT Crystal Oscillator mode<br>00 = EC (External Clock) mode                                                                                                                                                                                                                                                           |

| FWDTEN                 | <ul> <li>Watchdog Timer Enable bit</li> <li>1 = Watchdog Timer is always enabled (LPRC oscillator cannot be disabled. Clearing the SWDTEN bit in the RCON register will have no effect.)</li> <li>0 = Watchdog Timer is enabled/disabled by user software (LPRC can be disabled by clearing the SWDTEN bit in the RCON register)</li> </ul>                                                                                                 |

| WINDIS                 | Watchdog Timer Window Enable bit<br>1 = Watchdog Timer in Non-Window mode<br>0 = Watchdog Timer in Window mode                                                                                                                                                                                                                                                                                                                              |

| PLLKEN                 | PLL Lock Enable bit<br>1 = PLL lock is enabled<br>0 = PLL lock is disabled<br>nly available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.                                                                                                                                                                                                                                                                                           |

# TABLE 27-2: CONFIGURATION BITS DESCRIPTION

Note 1: This bit is only available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

2: When JTAGEN = 1, an internal pull-up resistor is enabled on the TMS pin. Erased devices default to JTAGEN = 1. Applications requiring I/O pins in a high-impedance state (tri-state) in Reset should use pins other than TMS for this purpose.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

### REGISTER 27-1: DEVID: DEVICE ID REGISTER

|        | egend: R = Read-Only bit U = Unimplemented bit |   |         |                       |   |   |        |

|--------|------------------------------------------------|---|---------|-----------------------|---|---|--------|

|        |                                                |   |         |                       |   |   |        |

| bit 7  |                                                |   |         |                       |   |   | bit 0  |

|        |                                                |   | DEVID   | <7:0> <sup>(1)</sup>  |   |   |        |

| R      | R                                              | R | R       | R                     | R | R | R      |

| bit 15 |                                                |   |         |                       |   |   | bit 8  |

|        |                                                |   | DEVID<  | :15:8> <sup>(1)</sup> |   |   |        |

| R      | R                                              | R | R       | R                     | R | R | R      |

| bit 23 |                                                |   |         |                       |   |   | bit 16 |

|        |                                                |   | DEVID<2 | 23:16>(1)             |   |   |        |

| R      | R                                              | R | R       | R                     | R | R | R      |

bit 23-0 **DEVID<23:0>:** Device Identifier bits<sup>(1)</sup>

**Note 1:** Refer to the "dsPIC33E/PIC24E Flash Programming Specification for Devices with Volatile Configuration *Bits*" (DS70663) for the list of device ID values.

### **REGISTER 27-2: DEVREV: DEVICE REVISION REGISTER**

| R           | R             | R | R      | R                      | R          | R | R      |

|-------------|---------------|---|--------|------------------------|------------|---|--------|

|             |               |   | DEVREV | <23:16> <sup>(1)</sup> |            |   |        |

| bit 23      |               |   |        |                        |            |   | bit 16 |

|             |               |   |        |                        |            |   |        |

| R           | R             | R | R      | R                      | R          | R | R      |

|             |               |   | DEVREV | <15:8>(1)              |            |   |        |

| bit 15      |               |   |        |                        |            |   | bit 8  |

| R           | R             | R | R      | R                      | R          | R | R      |

|             |               |   | DEVRE\ | /<7:0> <sup>(1)</sup>  |            |   |        |

| bit 7       |               |   |        |                        |            |   | bit 0  |

|             |               |   |        |                        |            |   |        |

| Legend: R = | Read-only bit |   |        | U = Unimplem           | nented bit |   |        |

# bit 23-0 **DEVREV<23:0>:** Device Revision bits<sup>(1)</sup>

**Note 1:** Refer to the "dsPIC33E/PIC24E Flash Programming Specification for Devices with Volatile Configuration *Bits*" (DS70663) for the list of device revision values.

| DC CHARACTERISTICS |                               |               | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                       |                 |  |  |  |  |

|--------------------|-------------------------------|---------------|-------------------------------------------------------|-----------------------|-----------------|--|--|--|--|

| Parameter<br>No.   | Тур.                          | Max.          | Units                                                 | tions                 |                 |  |  |  |  |

| Power-Down Cu      | urrent (IPD) <sup>(1)</sup> - | dsPIC33EP32GI | P50X, dsPIC33EF                                       | P32MC20X/50X and PIC2 | 4EP32GP/MC20X   |  |  |  |  |

| DC60d              | 30                            | 100           | μA                                                    | -40°C                 |                 |  |  |  |  |

| DC60a              | 35                            | 100           | μA                                                    | +25°C                 | 3.3V            |  |  |  |  |

| DC60b              | 150                           | 200           | μA                                                    | +85°C                 | 3.3V            |  |  |  |  |

| DC60c              | 250                           | 500           | μA                                                    | +125°C                |                 |  |  |  |  |

| Power-Down Cu      | urrent (IPD) <sup>(1)</sup> – | dsPIC33EP64GI | P50X, dsPIC33EF                                       | P64MC20X/50X and PIC2 | 4EP64GP/MC20X   |  |  |  |  |

| DC60d              | 25                            | 100           | μA                                                    | -40°C                 |                 |  |  |  |  |

| DC60a              | 30                            | 100           | μΑ                                                    | +25°C                 | 2 2)/           |  |  |  |  |

| DC60b              | 150                           | 350           | μΑ                                                    | +85°C                 | 3.3V            |  |  |  |  |

| DC60c              | 350                           | 800           | μΑ                                                    | +125°C                |                 |  |  |  |  |

| Power-Down Cu      | urrent (IPD) <sup>(1)</sup> – | dsPIC33EP128G | P50X, dsPIC33E                                        | P128MC20X/50X and PIC | 24EP128GP/MC20X |  |  |  |  |

| DC60d              | 30                            | 100           | μΑ                                                    | -40°C                 |                 |  |  |  |  |

| DC60a              | 35                            | 100           | μΑ                                                    | +25°C                 | 3.3V            |  |  |  |  |

| DC60b              | 150                           | 350           | μΑ                                                    | +85°C                 | 5.50            |  |  |  |  |

| DC60c              | 550                           | 1000          | μΑ                                                    | +125°C                |                 |  |  |  |  |

| Power-Down Cu      | urrent (IPD) <sup>(1)</sup> – | dsPIC33EP256G | P50X, dsPIC33E                                        | P256MC20X/50X and PIC | 24EP256GP/MC20X |  |  |  |  |

| DC60d              | 35                            | 100           | μΑ                                                    | -40°C                 |                 |  |  |  |  |

| DC60a              | 40                            | 100           | μΑ                                                    | +25°C                 | 3.3V            |  |  |  |  |

| DC60b              | 250                           | 450           | μΑ                                                    | +85°C                 | 5.57            |  |  |  |  |

| DC60c              | 1000                          | 1200          | μΑ                                                    | +125°C                |                 |  |  |  |  |

| Power-Down Cu      | urrent (IPD) <sup>(1)</sup> – | dsPIC33EP512G | P50X, dsPIC33E                                        | P512MC20X/50X and PIC | 24EP512GP/MC20X |  |  |  |  |

| DC60d              | 40                            | 100           | μΑ                                                    | -40°C                 |                 |  |  |  |  |

| DC60a              | 45                            | 100           | μΑ                                                    | +25°C                 | 3.3V            |  |  |  |  |

| DC60b              | 350                           | 800           | μΑ                                                    | +85°C                 | 0.0 v           |  |  |  |  |

| DC60c              | 1100                          | 1500          | μA                                                    | +125°C                |                 |  |  |  |  |

### TABLE 30-8: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

Note 1: IPD (Sleep) current is measured as follows:

• CPU core is off, oscillator is configured in EC mode and external clock is active; OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)

- · CLKO is configured as an I/O input pin in the Configuration Word

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- All peripheral modules are disabled (PMDx bits are all set)

- The VREGS bit (RCON<8>) = 0 (i.e., core regulator is set to standby while the device is in Sleep mode)

- The VREGSF bit (RCON<11>) = 0 (i.e., Flash regulator is set to standby while the device is in Sleep mode)

- JTAG is disabled

| DC CHARACTERISTICS |        |                                         | (unless                         | d Operating<br>otherwise<br>g temperat | <b>stated)</b><br>ure -40° | C ≤ TA ≤ | <b>/ to 3.6V</b><br>+85°C for Industrial<br>+125°C for Extended                                                                                   |  |

|--------------------|--------|-----------------------------------------|---------------------------------|----------------------------------------|----------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Param<br>No.       | Symbol | Characteristic                          | Min. Typ. Max. Units Conditions |                                        |                            |          |                                                                                                                                                   |  |

|                    | liL    | Input Leakage Current <sup>(1,2)</sup>  |                                 |                                        |                            |          |                                                                                                                                                   |  |

| DI50               |        | I/O Pins 5V Tolerant <sup>(3)</sup>     | -1                              | —                                      | +1                         | μA       | $\label{eq:VSS} \begin{split} &V{\sf SS} \leq V{\sf PIN} \leq V{\sf DD}, \\ &P{\sf in \ at \ high-impedance} \end{split}$                         |  |

| DI51               |        | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1                              | _                                      | +1                         | μA       | $\label{eq:VSS} \begin{array}{l} VSS \leq VPIN \leq VDD, \\ Pin \mbox{ at high-impedance}, \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \end{array}$ |  |

| DI51a              |        | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1                              | _                                      | +1                         | μA       | Analog pins shared with external reference pins, $-40^{\circ}C \le TA \le +85^{\circ}C$                                                           |  |

| DI51b              |        | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1                              | _                                      | +1                         | μA       | $Vss \le VPIN \le VDD,$<br>Pin at high-impedance,<br>-40°C ≤ TA ≤ +125°C                                                                          |  |

| DI51c              |        | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1                              | _                                      | +1                         | μA       | Analog pins shared with external reference pins, $-40^{\circ}C \le TA \le +125^{\circ}C$                                                          |  |