Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Detuils                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 512KB (170K x 24)                                                               |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 24K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 9x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-VFTLA Exposed Pad                                                            |

| Supplier Device Package    | 44-VTLA (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep512gp204t-i-tl |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

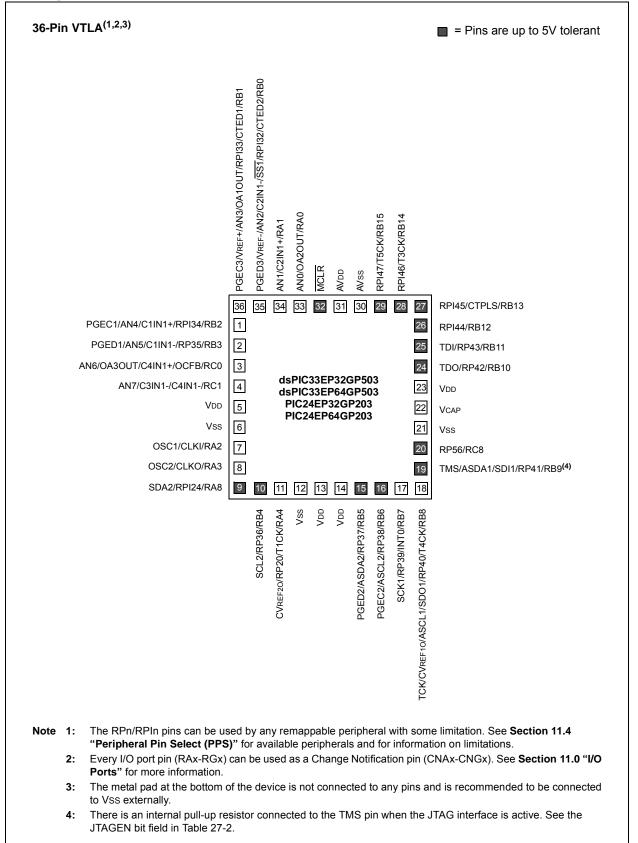

### **Pin Diagrams (Continued)**

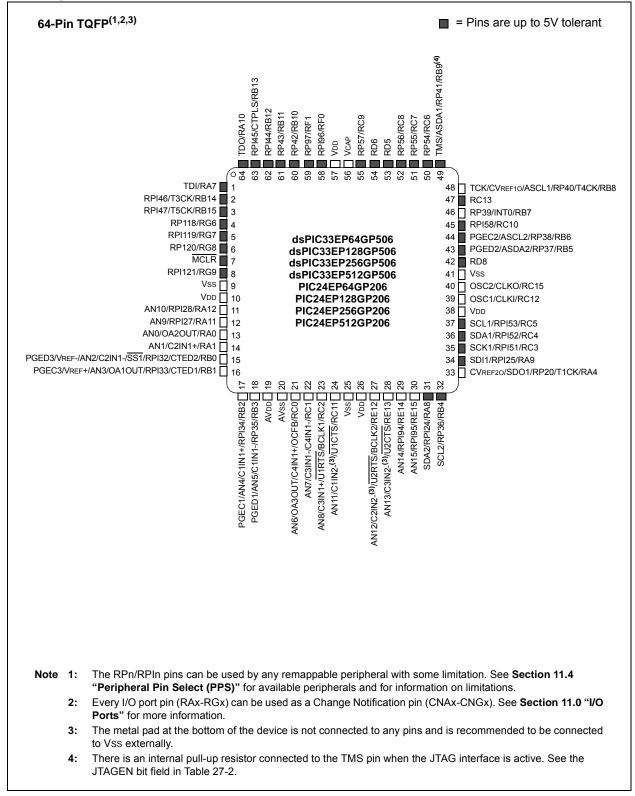

### **Pin Diagrams (Continued)**

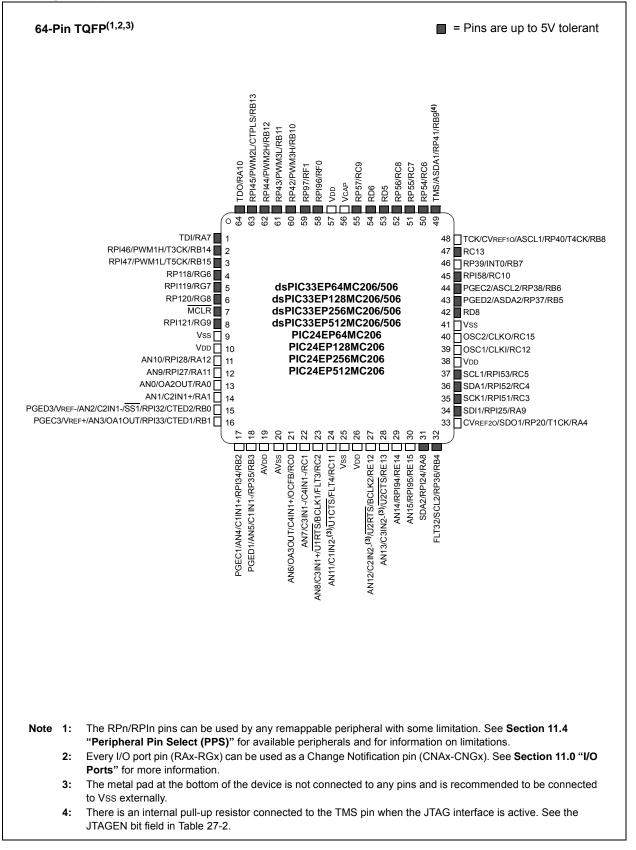

### Pin Diagrams (Continued)

### 2.5 ICSP Pins

The PGECx and PGEDx pins are used for ICSP and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes, and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin Voltage Input High (VIH) and Voltage Input Low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> PICkit<sup>™</sup> 3, MPLAB ICD 3, or MPLAB REAL ICE<sup>™</sup>.

For more information on MPLAB ICD 2, ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site.

- "Using MPLAB<sup>®</sup> ICD 3" (poster) DS51765

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" DS51764

- "MPLAB<sup>®</sup> REAL ICE<sup>™</sup> In-Circuit Emulator User's Guide" DS51616

- "Using MPLAB<sup>®</sup> REAL ICE™ In-Circuit Emulator" (poster) DS51749

### 2.6 External Oscillator Pins

Many DSCs have options for at least two oscillators: a high-frequency Primary Oscillator and a low-frequency Secondary Oscillator. For details, see **Section 9.0 "Oscillator Configuration"** for details.

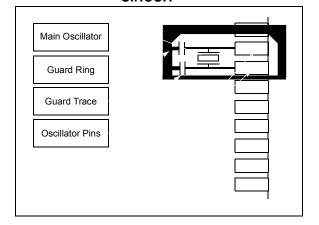

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is shown in Figure 2-3.

### SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

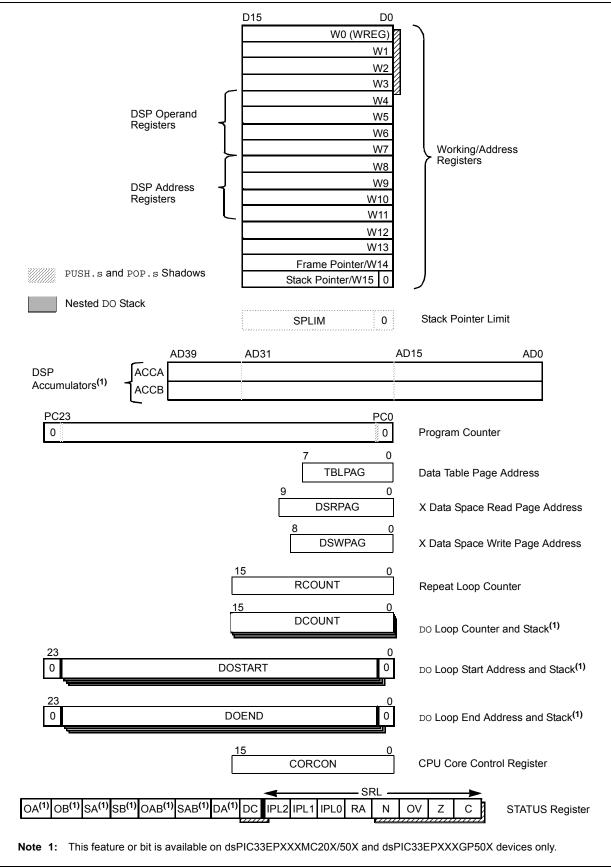

# 3.6 CPU Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter |  |  |  |  |  |  |

|-------|--------------------------------------------------------------------------------------|--|--|--|--|--|--|

|       | this URL in your browser:                                                            |  |  |  |  |  |  |

|       | http://www.microchip.com/wwwproducts/                                                |  |  |  |  |  |  |

|       | Devices.aspx?dDocName=en555464                                                       |  |  |  |  |  |  |

### 3.6.1 KEY RESOURCES

- "CPU" (DS70359) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

### 4.4.4 SOFTWARE STACK

The W15 register serves as a dedicated Software Stack Pointer (SSP) and is automatically modified by exception processing, subroutine calls and returns; however, W15 can be referenced by any instruction in the same manner as all other W registers. This simplifies reading, writing and manipulating of the Stack Pointer (for example, creating stack frames).

| Note: | To protect against misaligned stack               |

|-------|---------------------------------------------------|

|       | accesses, W15<0> is fixed to '0' by the hardware. |

W15 is initialized to 0x1000 during all Resets. This address ensures that the SSP points to valid RAM in all dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices, and permits stack availability for non-maskable trap exceptions. These can occur before the SSP is initialized by the user software. You can reprogram the SSP during initialization to any location within Data Space.

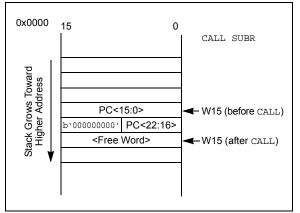

The Software Stack Pointer always points to the first available free word and fills the software stack working from lower toward higher addresses. Figure 4-19 illustrates how it pre-decrements for a stack pop (read) and post-increments for a stack push (writes).

When the PC is pushed onto the stack, PC<15:0> are pushed onto the first available stack word, then PC<22:16> are pushed into the second available stack location. For a PC push during any CALL instruction, the MSB of the PC is zero-extended before the push, as shown in Figure 4-19. During exception processing, the MSB of the PC is concatenated with the lower 8 bits of the CPU STATUS Register, SR. This allows the contents of SRL to be preserved automatically during interrupt processing.

- **Note 1:** To maintain system Stack Pointer (W15) coherency, W15 is never subject to (EDS) paging, and is therefore restricted to an address range of 0x0000 to 0xFFFF. The same applies to the W14 when used as a Stack Frame Pointer (SFA = 1).

- 2: As the stack can be placed in, and can access X and Y spaces, care must be taken regarding its use, particularly with regard to local automatic variables in a C development environment

FIGURE 4-19: CALL STACK FRAME

## 9.1 CPU Clocking System

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X family of devices provides six system clock options:

- Fast RC (FRC) Oscillator

- FRC Oscillator with Phase Locked Loop (PLL)

- · FRC Oscillator with Postscaler

- Primary (XT, HS or EC) Oscillator

- Primary Oscillator with PLL

- · Low-Power RC (LPRC) Oscillator

Instruction execution speed or device operating frequency, FCY, is given by Equation 9-1.

# EQUATION 9-1: DEVICE OPERATING FREQUENCY

FCY = Fosc/2

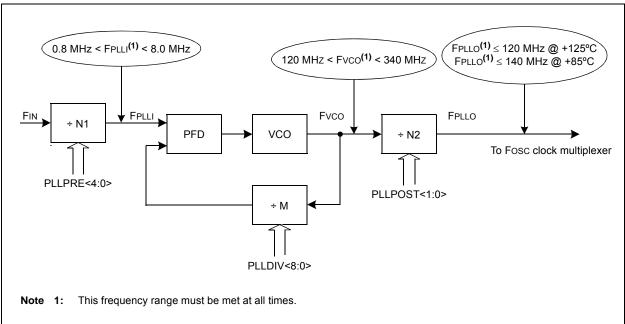

Figure 9-2 is a block diagram of the PLL module.

Equation 9-2 provides the relationship between input frequency (FIN) and output frequency (FPLLO). In clock modes S1 and S3, when the PLL output is selected, FOSC = FPLLO.

Equation 9-3 provides the relationship between input frequency (FIN) and VCO frequency (FVCO).

### EQUATION 9-2: FPLLO CALCULATION

$$FPLLO = FIN \times \left(\frac{M}{N1 \times N2}\right) = FIN \times \left(\frac{(PLLDIV + 2)}{(PLLPRE + 2) \times 2(PLLPOST + 1)}\right)$$

Where:

N1 = PLLPRE + 2 $N2 = 2 \times (PLLPOST + 1)$

M = PLLDIV + 2

### EQUATION 9-3: Fvco CALCULATION

$$Fvco = FIN \times \left(\frac{M}{N1}\right) = FIN \times \left(\frac{(PLLDIV + 2)}{(PLLPRE + 2)}\right)$$

DS70000657H-page 154

### © 2011-2013 Microchip Technology Inc.

# FIGURE 9-2: PLL BLOCK DIAGRAM

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

|                       | EGISTER 10-3: PMD3: PERIPHERAL MODULE DISABLE CONTROL REGISTER 3 |                  |                  |              |                      |          |                    |  |  |

|-----------------------|------------------------------------------------------------------|------------------|------------------|--------------|----------------------|----------|--------------------|--|--|

| U-0                   | U-0                                                              | U-0              | U-0              | U-0          | R/W-0                | U-0      | U-0                |  |  |

| —                     | _                                                                | —                | —                | —            | CMPMD                | —        | —                  |  |  |

| bit 15                |                                                                  |                  |                  |              |                      |          | bit 8              |  |  |

|                       |                                                                  |                  |                  |              |                      |          |                    |  |  |

| R/W-0                 | U-0                                                              | U-0              | U-0              | U-0          | U-0                  | R/W-0    | U-0                |  |  |

| CRCMD                 | —                                                                | —                | _                | —            | —                    | I2C2MD   | —                  |  |  |

| bit 7                 |                                                                  |                  |                  |              |                      |          | bit C              |  |  |

|                       |                                                                  |                  |                  |              |                      |          |                    |  |  |

| Legend:               |                                                                  |                  |                  |              |                      |          |                    |  |  |

| R = Readable          | bit                                                              | W = Writable I   | bit              | U = Unimplem | ented bit, read      | l as '0' |                    |  |  |

| -n = Value at POR '1' |                                                                  | '1' = Bit is set | '1' = Bit is set |              | '0' = Bit is cleared |          | x = Bit is unknown |  |  |

### REGISTER 10-3: PMD3: PERIPHERAL MODULE DISABLE CONTROL REGISTER 3

| bit 10  | CMPMD: Comparator Module Disable bit |

|---------|--------------------------------------|

|         | 1 = Comparator module is disabled    |

|         | 0 = Comparator module is enabled     |

| bit 9-8 | Unimplemented: Read as '0'           |

| bit 7   | CRCMD: CRC Module Disable bit        |

|         | 1 = CRC module is disabled           |

|         | 0 = CRC module is enabled            |

| bit 6-2 | Unimplemented: Read as '0'           |

| bit 1   | I2C2MD: I2C2 Module Disable bit      |

|         | 1 = I2C2 module is disabled          |

|         | 0 = I2C2 module is enabled           |

| bit 0   | Unimplemented: Read as '0'           |

|         |                                      |

### REGISTER 10-4: PMD4: PERIPHERAL MODULE DISABLE CONTROL REGISTER 4

| U-0    | U-0 | U-0 | U-0 | U-0    | U-0    | U-0 | U-0   |  |  |

|--------|-----|-----|-----|--------|--------|-----|-------|--|--|

| —      | —   |     |     | —      | —      | —   | —     |  |  |

| bit 15 |     |     |     |        |        |     | bit 8 |  |  |

|        |     |     |     |        |        |     |       |  |  |

| U-0    | U-0 | U-0 | U-0 | R/W-0  | R/W-0  | U-0 | U-0   |  |  |

| —      | —   | —   | —   | REFOMD | CTMUMD | —   | —     |  |  |

| bit 7  |     |     |     |        |        |     | bit 0 |  |  |

|        |     |     |     |        |        |     |       |  |  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-4 | Unimplemented: Read as '0'                                 |

|----------|------------------------------------------------------------|

| bit 3    | <b>REFOMD:</b> Reference Clock Module Disable bit          |

|          | <ol> <li>1 = Reference clock module is disabled</li> </ol> |

|          | 0 = Reference clock module is enabled                      |

| bit 2    | CTMUMD: CTMU Module Disable bit                            |

|          | 1 = CTMU module is disabled                                |

|          | 0 = CTMU module is enabled                                 |

| bit 1-0  | Unimplemented: Read as '0'                                 |

$\ensuremath{\textcircled{}^\circ}$  2011-2013 Microchip Technology Inc.

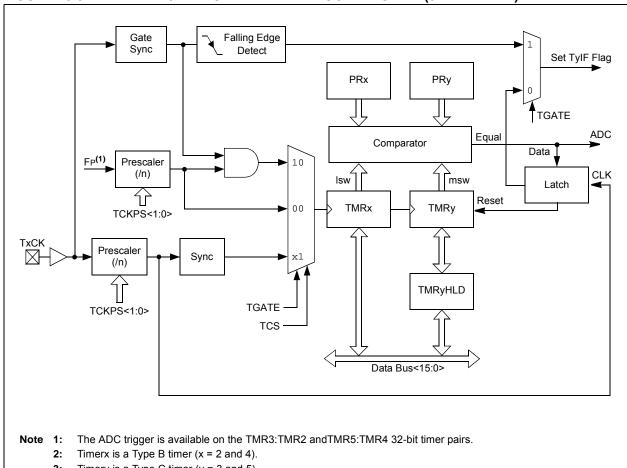

#### **FIGURE 13-3:** TYPE B/TYPE C TIMER PAIR BLOCK DIAGRAM (32-BIT TIMER)

3: Timery is a Type C timer (y = 3 and 5).

#### **Timerx/y Resources** 13.1

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/                                                                                      |

|       | wwwproducts/Devices.aspx?d<br>DocName=en555464                                                                 |

#### **KEY RESOURCES** 13.1.1

- "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- Application Notes

- · Software Libraries

- · Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

NOTES:

### REGISTER 16-7: PWMCONx: PWMx CONTROL REGISTER (CONTINUED)

| bit 7- | 6  | DTC<1:0>: Dead-Time Control bits                                                                                                    |

|--------|----|-------------------------------------------------------------------------------------------------------------------------------------|

|        |    | 11 = Dead-Time Compensation mode                                                                                                    |

|        |    | 10 = Dead-time function is disabled                                                                                                 |

|        |    | 01 = Negative dead time is actively applied for Complementary Output mode                                                           |

|        |    | 00 = Positive dead time is actively applied for all output modes                                                                    |

| bit 5  |    | <b>DTCP:</b> Dead-Time Compensation Polarity bit <sup>(3)</sup>                                                                     |

|        |    | When Set to '1':                                                                                                                    |

|        |    | If DTCMPx = 0, PWMxL is shortened and PWMxH is lengthened.                                                                          |

|        |    | If DTCMPx = 1, PWMxH is shortened and PWMxL is lengthened.                                                                          |

|        |    | <u>When Set to '0':</u><br>If DTCMPx = 0, PWMxH is shortened and PWMxL is lengthened.                                               |

|        |    | If DTCMPx = 1, PWMxL is shortened and PWMxH is lengthened.                                                                          |

| bit 4  |    | Unimplemented: Read as '0'                                                                                                          |

| bit 3  |    | MTBS: Master Time Base Select bit                                                                                                   |

|        |    | 1 = PWM generator uses the secondary master time base for synchronization and as the clock source                                   |

|        |    | for the PWM generation logic (if secondary time base is available)                                                                  |

|        |    | 0 = PWM generator uses the primary master time base for synchronization and as the clock source                                     |

|        |    | for the PWM generation logic                                                                                                        |

| bit 2  |    | CAM: Center-Aligned Mode Enable bit <sup>(2,4)</sup>                                                                                |

|        |    | 1 = Center-Aligned mode is enabled                                                                                                  |

|        |    | 0 = Edge-Aligned mode is enabled                                                                                                    |

| bit 1  |    | <b>XPRES:</b> External PWMx Reset Control bit <sup>(5)</sup>                                                                        |

|        |    | <ul> <li>1 = Current-limit source resets the time base for this PWM generator if it is in Independent Time Base<br/>mode</li> </ul> |

|        |    | 0 = External pins do not affect PWMx time base                                                                                      |

| bit 0  |    | IUE: Immediate Update Enable bit <sup>(2)</sup>                                                                                     |

|        |    | 1 = Updates to the active MDC/PDCx/DTRx/ALTDTRx/PHASEx registers are immediate                                                      |

|        |    | <ul> <li>Updates to the active MDC/PDCx/DTRx/ALTDTRx/PHASEx registers are synchronized to the<br/>PWMx period boundary</li> </ul>   |

| Note   | 1: | Software must clear the interrupt status here and in the corresponding IFSx bit in the interrupt controller.                        |

|        | 2: | These bits should not be changed after the PWMx is enabled (PTEN = 1).                                                              |

|        | 3: | DTC<1:0> = 11 for DTCP to be effective; otherwise, DTCP is ignored.                                                                 |

|        | 4: | The Independent Time Base (ITB = 1) mode must be enabled to use Center-Aligned mode. If ITB = 0, the CAM bit is ignored.            |

**5:** To operate in External Period Reset mode, the ITB bit must be '1' and the CLMOD bit in the FCLCONx register must be '0'.

| R/W-0                             | R/W-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | R/W-0              | R/W-0 |

|-----------------------------------|-------|------------------|-------|------------------------------------|-------|--------------------|-------|

| CSS15                             | CSS14 | CSS13            | CSS12 | CSS11                              | CSS10 | CSS9               | CSS8  |

| bit 15                            |       |                  |       | ·                                  | •     | ·                  | bit 8 |

|                                   |       |                  |       |                                    |       |                    |       |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | R/W-0              | R/W-0 |

| CSS7                              | CSS6  | CSS5             | CSS4  | CSS3                               | CSS2  | CSS1               | CSS0  |

| bit 7                             | -     |                  |       |                                    | •     |                    | bit ( |

|                                   |       |                  |       |                                    |       |                    |       |

| Legend:                           |       |                  |       |                                    |       |                    |       |

| R = Readable bit W = Writable bit |       |                  | bit   | U = Unimplemented bit, read as '0' |       |                    |       |

| -n = Value at POR                 |       | '1' = Bit is set |       | '0' = Bit is cleared               |       | x = Bit is unknown |       |

# REGISTER 23-8: AD1CSSL: ADC1 INPUT SCAN SELECT REGISTER LOW<sup>(1,2)</sup>

bit 15-0 CSS<15:0>: ADC1 Input Scan Selection bits

1 = Selects ANx for input scan

0 = Skips ANx for input scan

**Note 1:** On devices with less than 16 analog inputs, all AD1CSSL bits can be selected by the user. However, inputs selected for scan, without a corresponding input on the device, convert VREFL.

**2:** CSSx = ANx, where x = 0-15.

# REGISTER 24-10: PTGADJ: PTG ADJUST REGISTER<sup>(1)</sup>

| R/W-0                              | R/W-0                                                                | R/W-0 | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |

|------------------------------------|----------------------------------------------------------------------|-------|-------|-----------------------------------------|-------|-------|-------|--|

|                                    |                                                                      |       | PTGA  | DJ<15:8>                                |       |       |       |  |

| bit 15                             |                                                                      |       |       |                                         |       |       | bit 8 |  |

|                                    |                                                                      |       |       |                                         |       |       |       |  |

| R/W-0                              | R/W-0                                                                | R/W-0 | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |

|                                    |                                                                      |       | PTGA  | DJ<7:0>                                 |       |       |       |  |

| bit 7                              |                                                                      |       |       |                                         |       |       | bit 0 |  |

|                                    |                                                                      |       |       |                                         |       |       |       |  |

| Legend:                            |                                                                      |       |       |                                         |       |       |       |  |

| R = Readable                       | R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |       |       |                                         |       |       |       |  |

| -n = Value at POR '1' = Bit is set |                                                                      |       |       | '0' = Bit is cleared x = Bit is unknown |       |       |       |  |

bit 15-0 **PTGADJ<15:0>:** PTG Adjust Register bits This register holds user-supplied data to be added to the PTGTxLIM, PTGCxLIM, PTGSDLIM or PTGL0 registers with the PTGADD command.

# REGISTER 24-11: PTGL0: PTG LITERAL 0 REGISTER<sup>(1)</sup>

| R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------------|-------|-------|-------|-------|-------|-------|-------|

| PTGL0<15:8> |       |       |       |       |       |       |       |

| bit 15 bit  |       |       |       |       |       | bit 8 |       |

| R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|------------|-------|-------|-------|-------|-------|-------|-------|

| PTGL0<7:0> |       |       |       |       |       |       |       |

| bit 7 bit  |       |       |       |       |       | bit 0 |       |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | id as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

### bit 15-0 PTGL0<15:0>: PTG Literal 0 Register bits

This register holds the 16-bit value to be written to the AD1CHS0 register with the  ${\tt PTGCTRL}$  Step command.

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

### 29.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16 and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

### 29.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline

assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

### 29.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

## 29.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- · Command-line interface

- · Rich directive set

- Flexible macro language

- · MPLAB X IDE compatibility

| DC CHARACTERISTICS |        | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                    |      |                       |       |                                                                                                                                      |

|--------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------|-----------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic                                                                                                                                                                                                                                                                          | Min.               | Тур. | Max.                  | Units | Conditions                                                                                                                           |

| DI60a              | licl   | Input Low Injection Current                                                                                                                                                                                                                                                             | 0                  |      | <sub>-5</sub> (4,7)   | mA    | All pins except VDD, VSS,<br>AVDD, AVSS, MCLR, VCAP<br>and RB7                                                                       |

| DI60b              | Іісн   | Input High Injection Current                                                                                                                                                                                                                                                            | 0                  |      | +5 <sup>(5,6,7)</sup> | mA    | All pins except VDD, VSS,<br>AVDD, AVSS, MCLR, VCAP,<br>RB7 and all 5V tolerant<br>pins <sup>(6)</sup>                               |

| DI60c              | ∑lict  | Total Input Injection Current<br>(sum of all I/O and control<br>pins)                                                                                                                                                                                                                   | -20 <sup>(8)</sup> | _    | +20 <sup>(8)</sup>    | mA    | Absolute instantaneous sum<br>of all $\pm$ input injection cur-<br>rents from all I/O pins<br>(   IICL +   IICH   ) $\leq \sum$ IICT |

### TABLE 30-11: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS (CONTINUED)

**Note 1:** The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current can be measured at different input voltages.

2: Negative current is defined as current sourced by the pin.

3: See the "Pin Diagrams" section for the 5V tolerant I/O pins.

4: VIL source < (Vss – 0.3). Characterized but not tested.

5: Non-5V tolerant pins VIH source > (VDD + 0.3), 5V tolerant pins VIH source > 5.5V. Characterized but not tested.

6: Digital 5V tolerant pins cannot tolerate any "positive" input injection current from input sources > 5.5V.

7: Non-zero injection currents can affect the ADC results by approximately 4-6 counts.

8: Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the mathematical "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. Characterized but not tested.

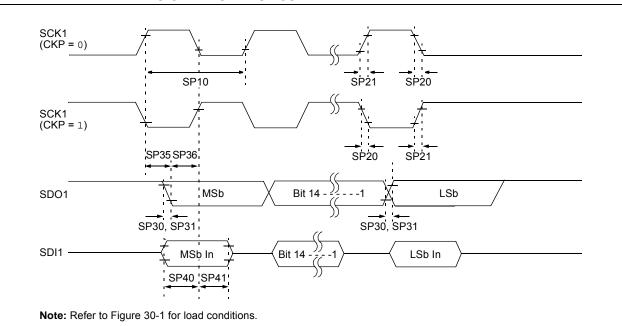

# TABLE 30-44:SPI1 MASTER MODE (FULL-DUPLEX, CKE = 0, CKP = x, SMP = 1)TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                               | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                     |      |       |                             |  |

|--------------------|-----------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|-----------------------------|--|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>                 | Min.                                                                                                                                                                                                                                                                                    | Typ. <sup>(2)</sup> | Max. | Units | Conditions                  |  |

| SP10               | FscP                  | Maximum SCK1 Frequency                        |                                                                                                                                                                                                                                                                                         | —                   | 10   | MHz   | -40°C to +125°C<br>(Note 3) |  |

| SP20               | TscF                  | SCK1 Output Fall Time                         | _                                                                                                                                                                                                                                                                                       | —                   | _    | ns    | See Parameter DO32 (Note 4) |  |

| SP21               | TscR                  | SCK1 Output Rise Time                         | _                                                                                                                                                                                                                                                                                       | —                   | _    | ns    | See Parameter DO31 (Note 4) |  |

| SP30               | TdoF                  | SDO1 Data Output Fall Time                    | _                                                                                                                                                                                                                                                                                       | —                   | _    | ns    | See Parameter DO32 (Note 4) |  |

| SP31               | TdoR                  | SDO1 Data Output Rise Time                    | _                                                                                                                                                                                                                                                                                       | —                   | _    | ns    | See Parameter DO31 (Note 4) |  |

| SP35               | TscH2doV,<br>TscL2doV | SDO1 Data Output Valid after<br>SCK1 Edge     | _                                                                                                                                                                                                                                                                                       | 6                   | 20   | ns    |                             |  |

| SP36               | TdoV2scH,<br>TdoV2scL | SDO1 Data Output Setup to<br>First SCK1 Edge  | 30                                                                                                                                                                                                                                                                                      | —                   | _    | ns    |                             |  |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDI1 Data<br>Input to SCK1 Edge | 30                                                                                                                                                                                                                                                                                      | —                   | _    | ns    |                             |  |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDI1 Data Input to SCK1 Edge     | 30                                                                                                                                                                                                                                                                                      | —                   | —    | ns    |                             |  |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The minimum clock period for SCK1 is 100 ns. The clock generated in Master mode must not violate this specification.

- 4: Assumes 50 pF load on all SPI1 pins.

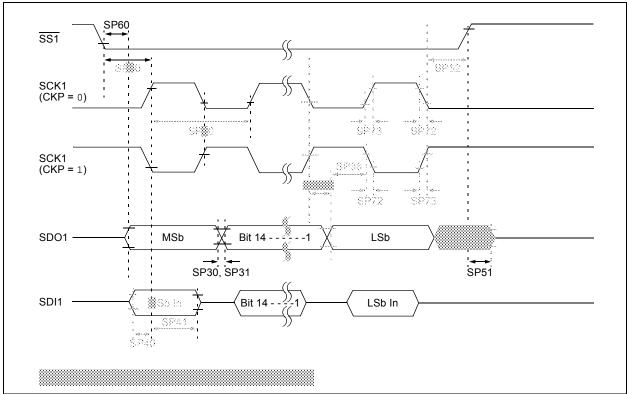

FIGURE 30-26: SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0) TIMING CHARACTERISTICS

# APPENDIX A: REVISION HISTORY

## **Revision A (April 2011)**

This is the initial released version of the document.

### Revision B (July 2011)

This revision includes minor typographical and formatting changes throughout the data sheet text.

All other major changes are referenced by their respective section in Table A-1.

### TABLE A-1: MAJOR SECTION UPDATES

| Section Name                                                                     | Update Description                                                                                                                                                                                                                                                                                                      |

|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "High-Performance, 16-bit<br>Digital Signal Controllers<br>and Microcontrollers" | Changed all pin diagrams references of VLAP to TLA.                                                                                                                                                                                                                                                                     |

| Section 4.0 "Memory<br>Organization"                                             | Updated the All Resets values for CLKDIV and PLLFBD in the System Control Register Map (see Table 4-35).                                                                                                                                                                                                                |

| Section 5.0 "Flash Program<br>Memory"                                            | Updated "one word" to "two words" in the first paragraph of <b>Section 5.2 "RTSP Operation"</b> .                                                                                                                                                                                                                       |

| Section 9.0 "Oscillator<br>Configuration"                                        | Updated the PLL Block Diagram (see Figure 9-2).<br>Updated the Oscillator Mode, Fast RC Oscillator (FRC) with divide-by-N and PLL<br>(FRCPLL), by changing (FRCDIVN + PLL) to (FRCPLL).                                                                                                                                 |

|                                                                                  | Changed (FRCDIVN + PLL) to (FRCPLL) for COSC<2:0> = 001 and NOSC<2:0> = 001 in the Oscillator Control Register (see Register 9-1).                                                                                                                                                                                      |

|                                                                                  | Changed the POR value from 0 to 1 for the DOZE<1:0> bits, from 1 to 0 for the FRCDIV<0> bit, and from 0 to 1 for the PLLPOST<0> bit; Updated the default definitions for the DOZE<2:0> and FRCDIV<2:0> bits and updated all bit definitions for the PLLPOST<1:0> bits in the Clock Divisor Register (see Register 9-2). |

|                                                                                  | Changed the POR value from 0 to 1 for the PLLDIV<5:4> bits and updated the default definitions for all PLLDIV<8:0> bits in the PLL Feedback Division Register (see Register 9-2).                                                                                                                                       |

| Section 22.0 "Charge Time<br>Measurement Unit (CTMU)"                            | Updated the bit definitions for the IRNG<1:0> bits in the CTMU Current Control Register (see Register 22-3).                                                                                                                                                                                                            |

| Section 25.0 "Op amp/<br>Comparator Module"                                      | Updated the voltage reference block diagrams (see Figure 25-1 and Figure 25-2).                                                                                                                                                                                                                                         |