Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 70 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 53                                                                             |

| Program Memory Size        | 512KB (170K x 24)                                                              |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 24K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-VFQFN Exposed Pad                                                           |

| Supplier Device Package    | 64-VQFN (9x9)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep512gp206-i-mr |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

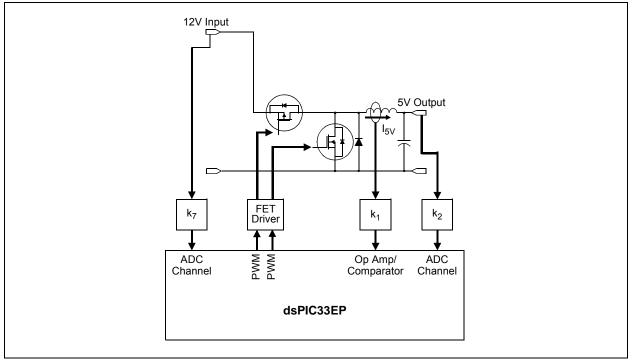

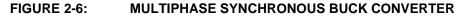

#### FIGURE 2-5: SINGLE-PHASE SYNCHRONOUS BUCK CONVERTER

Allocating different Page registers for read and write access allows the architecture to support data movement between different pages in data memory. This is accomplished by setting the DSRPAG register value to the page from which you want to read, and configuring the DSWPAG register to the page to which it needs to be written. Data can also be moved from different PSV to EDS pages, by configuring the DSRPAG and DSWPAG registers to address PSV and EDS space, respectively. The data can be moved between pages by a single instruction.

When an EDS or PSV page overflow or underflow occurs, EA<15> is cleared as a result of the register indirect EA calculation. An overflow or underflow of the EA in the EDS or PSV pages can occur at the page boundaries when:

- The initial address prior to modification addresses an EDS or PSV page

- The EA calculation uses Pre-Modified or Post-Modified Register Indirect Addressing; however, this does not include Register Offset Addressing

In general, when an overflow is detected, the DSxPAG register is incremented and the EA<15> bit is set to keep the base address within the EDS or PSV window. When an underflow is detected, the DSxPAG register is decremented and the EA<15> bit is set to keep the base address within the EDS or PSV window. This creates a linear EDS and PSV address space, but only when using Register Indirect Addressing modes.

Exceptions to the operation described above arise when entering and exiting the boundaries of Page 0, EDS and PSV spaces. Table 4-61 lists the effects of overflow and underflow scenarios at different boundaries.

In the following cases, when overflow or underflow occurs, the EA<15> bit is set and the DSxPAG is not modified; therefore, the EA will wrap to the beginning of the current page:

- · Register Indirect with Register Offset Addressing

- Modulo Addressing

- · Bit-Reversed Addressing

| 0/11        |                     |                | Before       |                        | After          |              |                        |  |  |

|-------------|---------------------|----------------|--------------|------------------------|----------------|--------------|------------------------|--|--|

| O/U,<br>R/W | Operation           | DSxPAG         | DS<br>EA<15> | Page<br>Description    | DSxPAG         | DS<br>EA<15> | Page<br>Description    |  |  |

| O,<br>Read  |                     | DSRPAG = 0x1FF | 1            | EDS: Last page         | DSRPAG = 0x1FF | 0            | See Note 1             |  |  |

| O,<br>Read  | [++Wn]              | DSRPAG = 0x2FF | 1            | PSV: Last lsw<br>page  | DSRPAG = 0x300 | 1            | PSV: First MSB<br>page |  |  |

| O,<br>Read  | <b>Or</b><br>[Wn++] | DSRPAG = 0x3FF | 1            | PSV: Last MSB<br>page  | DSRPAG = 0x3FF | 0            | See Note 1             |  |  |

| O,<br>Write |                     | DSWPAG = 0x1FF | 1            | EDS: Last page         | DSWPAG = 0x1FF | 0            | See Note 1             |  |  |

| U,<br>Read  |                     | DSRPAG = 0x001 | 1            | PSV page               | DSRPAG = 0x001 | 0            | See Note 1             |  |  |

| U,<br>Read  | [Wn]<br>Or<br>[Wn]  | DSRPAG = 0x200 | 1            | PSV: First Isw<br>page | DSRPAG = 0x200 | 0            | See Note 1             |  |  |

| U,<br>Read  | [ //11 - ]          | DSRPAG = 0x300 | 1            | PSV: First MSB<br>page | DSRPAG = 0x2FF | 1            | PSV: Last Isw<br>page  |  |  |

# TABLE 4-61: OVERFLOW AND UNDERFLOW SCENARIOS AT PAGE 0, EDS and PSV SPACE BOUNDARIES<sup>(2,3,4)</sup>

Legend: O = Overflow, U = Underflow, R = Read, W = Write

Note 1: The Register Indirect Addressing now addresses a location in the base Data Space (0x0000-0x8000).

2: An EDS access with DSxPAG = 0x000 will generate an address error trap.

- **3:** Only reads from PS are supported using DSRPAG. An attempt to write to PS using DSWPAG will generate an address error trap.

- 4: Pseudo-Linear Addressing is not supported for large offsets.

## 4.4.2 EXTENDED X DATA SPACE

The lower portion of the base address space range, between 0x0000 and 0x7FFF, is always accessible regardless of the contents of the Data Space Page registers. It is indirectly addressable through the register indirect instructions. It can be regarded as being located in the default EDS Page 0 (i.e., EDS address range of 0x000000 to 0x007FFF with the base address bit, EA<15> = 0, for this address range). However, Page 0 cannot be accessed through the upper 32 Kbytes, 0x8000 to 0xFFFF, of base Data Space, in combination with DSRPAG = 0x000 or DSWPAG = 0x000. Consequently, DSRPAG and DSWPAG are initialized to 0x001 at Reset.

- Note 1: DSxPAG should not be used to access Page 0. An EDS access with DSxPAG set to 0x000 will generate an address error trap.

- 2: Clearing the DSxPAG in software has no effect.

The remaining pages, including both EDS and PSV pages, are only accessible using the DSRPAG or DSWPAG registers in combination with the upper 32 Kbytes, 0x8000 to 0xFFFF, of the base address, where base address bit, EA<15> = 1.

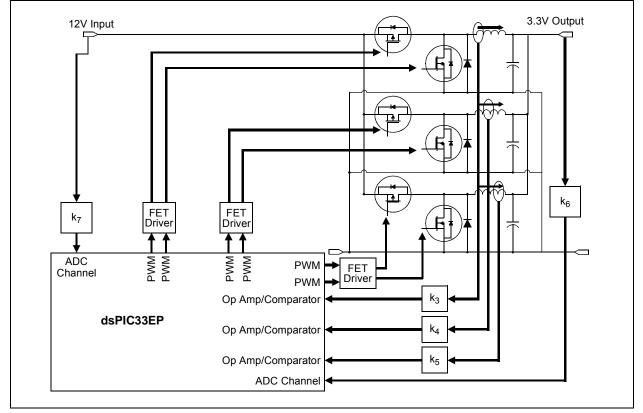

For example, when DSRPAG = 0x001 or DSWPAG = 0x001, accesses to the upper 32 Kbytes, 0x8000 to 0xFFFF, of the Data Space will map to the EDS address range of 0x008000 to 0x00FFFF. When DSRPAG = 0x002 or DSWPAG = 0x002, accesses to the upper 32 Kbytes of the Data Space will map to the EDS address range of 0x010000 to 0x017FFF and so on, as shown in the EDS memory map in Figure 4-17.

For more information on the PSV page access using Data Space Page registers, refer to the "**Program Space Visibility from Data Space**" section in "**Program Memory**" (DS70613) of the "*dsPIC33/ PIC24 Family Reference Manual*".

#### FIGURE 4-17: EDS MEMORY MAP

| R/W-0                | R/W-0                   | R/W-0                | R/W-0 | R/C-0 | R/C-0 | R-0   | R/W-0 |

|----------------------|-------------------------|----------------------|-------|-------|-------|-------|-------|

| OA                   | OB                      | SA                   | SB    | OAB   | SAB   | DA    | DC    |

| bit 15               |                         |                      |       |       |       |       | bit 8 |

|                      |                         |                      |       |       |       |       |       |

| R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup>    | R/W-0 <sup>(3)</sup> | R-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|                      | IPL<2:0> <sup>(2)</sup> |                      | RA    | Ν     | OV    | Z     | С     |

| bit 7                |                         |                      |       |       |       |       | bit 0 |

|                      |                         |                      |       |       |       |       |       |

## REGISTER 7-1: SR: CPU STATUS REGISTER<sup>(1)</sup>

| Legend:           | C = Clearable bit |                       |                    |

|-------------------|-------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1'= Bit is set   | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7-5 | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2,3)</sup>        |

|---------|----------------------------------------------------------------------------|

|         | 111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled |

|         | 110 = CPU Interrupt Priority Level is 6 (14)                               |

|         | 101 = CPU Interrupt Priority Level is 5 (13)                               |

|         | 100 = CPU Interrupt Priority Level is 4 (12)                               |

|         | 011 = CPU Interrupt Priority Level is 3 (11)                               |

|         | 010 = CPU Interrupt Priority Level is 2 (10)                               |

|         | 001 = CPU Interrupt Priority Level is 1 (9)                                |

|         | 000 = CPU Interrupt Priority Level is 0 (8)                                |

- **Note 1:** For complete register details, see Register 3-1.

- 2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL, if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- **3:** The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

| R/W-1        | R/W-0         | R/W-0                                                                                      | U-0           | U-0              | U-0              | U-0             | U-0    |  |

|--------------|---------------|--------------------------------------------------------------------------------------------|---------------|------------------|------------------|-----------------|--------|--|

| GIE          | DISI          | SWTRAP                                                                                     |               |                  |                  | _               |        |  |

| bit 15       |               |                                                                                            |               |                  |                  |                 | bit 8  |  |

|              |               |                                                                                            |               |                  |                  |                 |        |  |

| U-0          | U-0           | U-0                                                                                        | U-0           | U-0              | R/W-0            | R/W-0           | R/W-0  |  |

|              | —             |                                                                                            |               |                  | INT2EP           | INT1EP          | INT0EP |  |

| bit 7        |               |                                                                                            |               |                  |                  |                 | bit C  |  |

| Legend:      |               |                                                                                            |               |                  |                  |                 |        |  |

| R = Readab   | le bit        | W = Writable                                                                               | bit           | U = Unimpler     | mented bit, read | l as '0'        |        |  |

| -n = Value a |               | '1' = Bit is set                                                                           |               | '0' = Bit is cle |                  | x = Bit is unki | nown   |  |

|              |               |                                                                                            |               |                  |                  |                 |        |  |

| bit 15       | GIE: Global   | Interrupt Enable                                                                           | e bit         |                  |                  |                 |        |  |

|              | 1 = Interrupt | s and associate                                                                            | d IE bits are | enabled          |                  |                 |        |  |

|              |               | s are disabled, I                                                                          | •             | still enabled    |                  |                 |        |  |

| bit 14       | DISI: DISI    | nstruction Statu                                                                           | s bit         |                  |                  |                 |        |  |

|              |               | struction is active<br>struction is not a                                                  | -             |                  |                  |                 |        |  |

| bit 13       | SWTRAP: S     | Software Trap St                                                                           | atus bit      |                  |                  |                 |        |  |

|              |               | e trap is enabled<br>e trap is disabled                                                    |               |                  |                  |                 |        |  |

| bit 12-3     | Unimpleme     | nted: Read as '                                                                            | 0'            |                  |                  |                 |        |  |

| bit 2        | INT2EP: Ext   | ternal Interrupt 2                                                                         | 2 Edge Detec  | t Polarity Selec | t bit            |                 |        |  |

|              |               | <ul> <li>1 = Interrupt on negative edge</li> <li>0 = Interrupt on positive edge</li> </ul> |               |                  |                  |                 |        |  |

| bit 1        | INT1EP: Ext   | ternal Interrupt 1                                                                         | Edge Detec    | t Polarity Selec | t bit            |                 |        |  |

|              |               | on negative edg                                                                            |               |                  |                  |                 |        |  |

| bit 0        | INTOEP: Ext   | ternal Interrupt C                                                                         | Edge Detec    | t Polarity Selec | t bit            |                 |        |  |

|              |               | on negative edg                                                                            |               |                  |                  |                 |        |  |

#### REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0                               | U-0   | U-0              | U-0   | U-0                                     | U-0              | U-0      | U-0   |

|-----------------------------------|-------|------------------|-------|-----------------------------------------|------------------|----------|-------|

| —                                 | —     | —                | —     | —                                       | —                | _        | —     |

| bit 15                            |       |                  |       |                                         | •                |          | bit 8 |

|                                   |       |                  |       |                                         |                  |          |       |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0            | R/W-0    | R/W-0 |

|                                   |       |                  | STB<  | 23:16>                                  |                  |          |       |

| bit 7                             |       |                  |       |                                         |                  |          | bit 0 |

|                                   |       |                  |       |                                         |                  |          |       |

| Legend:                           |       |                  |       |                                         |                  |          |       |

| R = Readable bit W = Writable bit |       |                  | bit   | U = Unimpler                            | mented bit, read | l as '0' |       |

| -n = Value at P                   | POR   | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |                  |          | nown  |

|                                   |       |                  |       |                                         |                  |          |       |

## REGISTER 8-5: DMAXSTBH: DMA CHANNEL X START ADDRESS REGISTER B (HIGH)

bit 15-8 Unimplemented: Read as '0'

bit 7-0 STB<23:16>: Secondary Start Address bits (source or destination)

## REGISTER 8-6: DMAXSTBL: DMA CHANNEL X START ADDRESS REGISTER B (LOW)

| R/W-0           | R/W-0                                                                | R/W-0          | R/W-0           | R/W-0        | R/W-0           | R/W-0     | R/W-0 |

|-----------------|----------------------------------------------------------------------|----------------|-----------------|--------------|-----------------|-----------|-------|

|                 |                                                                      |                | STB             | <15:8>       |                 |           |       |

| bit 15          |                                                                      |                |                 |              |                 |           | bit 8 |

|                 |                                                                      |                |                 |              |                 |           |       |

| R/W-0           | R/W-0                                                                | R/W-0          | R/W-0           | R/W-0        | R/W-0           | R/W-0     | R/W-0 |

|                 |                                                                      |                | STE             | 3<7:0>       |                 |           |       |

| bit 7           |                                                                      |                |                 |              |                 |           | bit 0 |

| Legend:         |                                                                      |                |                 |              |                 |           |       |

| R = Readable    | bit                                                                  | W = Writable b | bit             | U = Unimplen | nented bit, rea | ad as '0' |       |

| -n = Value at P | n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is ur |                | x = Bit is unkı | nown         |                 |           |       |

bit 15-0 **STB<15:0>:** Secondary Start Address bits (source or destination)

## 12.2 Timer1 Control Register

| R/W-0              | U-0                                  | R/W-0                             | U-0                       | U-0              | U-0                      | U-0                | U-0                |

|--------------------|--------------------------------------|-----------------------------------|---------------------------|------------------|--------------------------|--------------------|--------------------|

| TON <sup>(1)</sup> | —                                    | TSIDL                             | —                         | _                | —                        | _                  | _                  |

| bit 15             |                                      |                                   |                           |                  |                          |                    | bit 8              |

|                    |                                      |                                   |                           |                  |                          |                    |                    |

| U-0                | R/W-0                                | R/W-0                             | R/W-0                     | U-0              | R/W-0                    | R/W-0              | U-0                |

|                    | TGATE                                | TCKPS1                            | TCKPS0                    | _                | TSYNC <sup>(1)</sup>     | TCS <sup>(1)</sup> |                    |

| bit 7              |                                      |                                   |                           |                  |                          |                    | bit (              |

| Legend:            |                                      |                                   |                           |                  |                          |                    |                    |

| R = Readable       | e bit                                | W = Writable                      | bit                       | U = Unimplei     | mented bit, read         | l as '0'           |                    |

| -n = Value at      | POR                                  | '1' = Bit is set                  |                           | '0' = Bit is cle | ared                     | x = Bit is unkno   | own                |

|                    |                                      | o                                 |                           |                  |                          |                    |                    |

| bit 15             | <b>TON:</b> Timer1<br>1 = Starts 16- |                                   |                           |                  |                          |                    |                    |

|                    | 0 = Stops 16-                        |                                   |                           |                  |                          |                    |                    |

| bit 14             | Unimplemen                           | ted: Read as '                    | 0'                        |                  |                          |                    |                    |

| bit 13             | TSIDL: Timer                         | 1 Stop in Idle N                  | /lode bit                 |                  |                          |                    |                    |

|                    |                                      | ues module op                     |                           |                  | ldle mode                |                    |                    |

|                    |                                      | s module opera                    |                           | ode              |                          |                    |                    |

| bit 12-7           | -                                    | ted: Read as '                    |                           |                  |                          |                    |                    |

| bit 6              |                                      | r1 Gated Time                     | Accumulation              | h Enable bit     |                          |                    |                    |

|                    | When TCS =<br>This bit is igno       |                                   |                           |                  |                          |                    |                    |

|                    | When TCS =                           |                                   |                           |                  |                          |                    |                    |

|                    |                                      | e accumulatio                     |                           |                  |                          |                    |                    |

|                    |                                      | e accumulatio                     |                           | 0.1.1.1.1.1      |                          |                    |                    |

| bit 5-4            |                                      | : Timer1 Input                    | Clock Prescal             | e Select bits    |                          |                    |                    |

|                    | 11 = 1:256<br>10 = 1:64              |                                   |                           |                  |                          |                    |                    |

|                    | 01 = 1:8                             |                                   |                           |                  |                          |                    |                    |

|                    | 00 = 1:1                             |                                   |                           |                  |                          |                    |                    |

| bit 3              | -                                    | ted: Read as '                    |                           |                  |                          |                    |                    |

| bit 2              |                                      | er1 External Clo                  | ock Input Synd            | chronization S   | elect bit <sup>(1)</sup> |                    |                    |

|                    | When TCS =                           |                                   |                           |                  |                          |                    |                    |

|                    |                                      | izes external c<br>synchronize e> |                           | nut              |                          |                    |                    |

|                    | When TCS =                           | •                                 |                           | iput             |                          |                    |                    |

|                    | This bit is igno                     |                                   |                           |                  |                          |                    |                    |

| bit 1              | TCS: Timer1                          | Clock Source S                    | Select bit <sup>(1)</sup> |                  |                          |                    |                    |

|                    | 1 = External c<br>0 = Internal cl    | clock is from pi<br>ock (FP)      | n, T1CK (on th            | ne rising edge)  | •                        |                    |                    |

| bit 0              | Unimplemen                           | ted: Read as '                    | 0'                        |                  |                          |                    |                    |

|                    | nen Timer1 is er<br>empts by user s  |                                   |                           |                  |                          | SYNC = 1, TON      | <b>\ =</b> 1), any |

## REGISTER 12-1: T1CON: TIMER1 CONTROL REGISTER

© 2011-2013 Microchip Technology Inc.

## 14.1 Input Capture Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 14.1.1 KEY RESOURCES

- "Input Capture" (DS70352) in the "dsPIC33/ PIC24 Family Reference Manual"

- · Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

#### REGISTER 14-2: ICxCON2: INPUT CAPTURE x CONTROL REGISTER 2 (CONTINUED)

- bit 4-0 SYNCSEL<4:0>: Input Source Select for Synchronization and Trigger Operation bits<sup>(4)</sup>

- 11111 = No Sync or Trigger source for ICx

- 11110 = Reserved

- 11101 = Reserved

- 11100 = CTMU module synchronizes or triggers ICx

- 11011 = ADC1 module synchronizes or triggers  $ICx^{(5)}$

- 11010 = CMP3 module synchronizes or triggers  $ICx^{(5)}$

- $11001 = CMP2 \text{ module synchronizes or triggers ICx}^{(5)}$

- 11000 = CMP1 module synchronizes or triggers  $ICx^{(5)}$

- 10111 = Reserved

- 10110 = Reserved

- 10101 = Reserved

- 10100 = Reserved

- 10011 = IC4 module synchronizes or triggers ICx

- 10010 = IC3 module synchronizes or triggers ICx

- 10001 = IC2 module synchronizes or triggers ICx

- 10000 = IC1 module synchronizes or triggers ICx

- 01111 = Timer5 synchronizes or triggers ICx

- 01110 = Timer4 synchronizes or triggers ICx

- 01101 = Timer3 synchronizes or triggers ICx (default)

- 01100 = Timer2 synchronizes or triggers ICx

- 01011 = Timer1 synchronizes or triggers ICx

- 01010 = PTGOx module synchronizes or triggers  $ICx^{(6)}$

- 01001 = Reserved

- 01000 = Reserved

- 00111 = Reserved

- 00110 = Reserved

- 00101 = Reserved

- 00100 = OC4 module synchronizes or triggers ICx

- 00011 = OC3 module synchronizes or triggers ICx

- 00010 = OC2 module synchronizes or triggers ICx

- 00001 = OC1 module synchronizes or triggers ICx

- 00000 = No Sync or Trigger source for ICx

- **Note 1:** The IC32 bit in both the Odd and Even IC must be set to enable Cascade mode.

- 2: The input source is selected by the SYNCSEL<4:0> bits of the ICxCON2 register.

- **3:** This bit is set by the selected input source (selected by SYNCSEL<4:0> bits). It can be read, set and cleared in software.

- 4: Do not use the ICx module as its own Sync or Trigger source.

- 5: This option should only be selected as a trigger source and not as a synchronization source.

- Each Input Capture x (ICx) module has one PTG input source. See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for more information.

PTGO8 = IC1

PTGO9 = IC2 PTGO10 = IC3 PTGO11 = IC4 NOTES:

## REGISTER 24-1: PTGCST: PTG CONTROL/STATUS REGISTER (CONTINUED)

- PTGITM<1:0>: PTG Input Trigger Command Operating Mode bits<sup>(1)</sup>

- 11 = Single level detect with Step delay not executed on exit of command (regardless of the PTGCTRL command)

- 10 = Single level detect with Step delay executed on exit of command

- 01 = Continuous edge detect with Step delay not executed on exit of command (regardless of the PTGCTRL command)

- 00 = Continuous edge detect with Step delay executed on exit of command

- Note 1: These bits apply to the PTGWHI and PTGWLO commands only.

bit 1-0

- **2:** This bit is only used with the PTGCTRL step command software trigger option.

- **3:** Use of the PTG Single-Step mode is reserved for debugging tools only.

## REGISTER 24-8: PTGC1LIM: PTG COUNTER 1 LIMIT REGISTER<sup>(1)</sup>

| R/W-0  | R/W-0 | R/W-0 | R/W-0  | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|--------|----------|-------|-------|-------|

|        |       |       | PTGC1L | IM<15:8> |       |       |       |

| bit 15 |       |       |        |          |       |       | bit 8 |

|        |       |       |        |          |       |       |       |

| R/W-0  | R/W-0 | R/W-0 | R/W-0  | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|        |       |       | PTGC1L | IM<7:0>  |       |       |       |

| bit 7  |       |       |        |          |       |       | bit C |

| Legena.           |                  |                       |                                    |  |  |

|-------------------|------------------|-----------------------|------------------------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | U = Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown                 |  |  |

bit 15-0 **PTGC1LIM<15:0>:** PTG Counter 1 Limit Register bits May be used to specify the loop count for the PTGJMPC1 Step command or as a limit register for the General Purpose Counter 1.

## REGISTER 24-9: PTGHOLD: PTG HOLD REGISTER<sup>(1)</sup>

| R/W-0  | R/W-0 | R/W-0 | R/W-0  | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|--------|----------|-------|-------|-------|

|        |       |       | PTGHOL | _D<15:8> |       |       |       |

| bit 15 |       |       |        |          |       |       | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|---------|-------|-------|-------|

|       |       |       | PTGHO | LD<7:0> |       |       |       |

| bit 7 |       |       |       |         |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 **PTGHOLD<15:0>:** PTG General Purpose Hold Register bits Holds user-supplied data to be copied to the PTGTxLIM, PTGCxLIM, PTGSDLIM or PTGL0 registers with the PTGCOPY command.

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

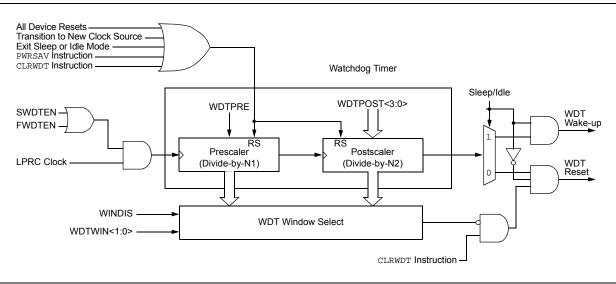

## 27.5 Watchdog Timer (WDT)

For dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices, the WDT is driven by the LPRC oscillator. When the WDT is enabled, the clock source is also enabled.

#### 27.5.1 PRESCALER/POSTSCALER

The nominal WDT clock source from LPRC is 32 kHz. This feeds a prescaler that can be configured for either 5-bit (divide-by-32) or 7-bit (divide-by-128) operation. The prescaler is set by the WDTPRE Configuration bit. With a 32 kHz input, the prescaler yields a WDT Timeout period (TWDT), as shown in Parameter SY12 in Table 30-22.

A variable postscaler divides down the WDT prescaler output and allows for a wide range of time-out periods. The postscaler is controlled by the WDTPOST<3:0> Configuration bits (FWDT<3:0>), which allow the selection of 16 settings, from 1:1 to 1:32,768. Using the prescaler and postscaler, time-out periods ranging from 1 ms to 131 seconds can be achieved.

The WDT, prescaler and postscaler are reset:

- · On any device Reset

- On the completion of a clock switch, whether invoked by software (i.e., setting the OSWEN bit after changing the NOSCx bits) or by hardware (i.e., Fail-Safe Clock Monitor)

- When a PWRSAV instruction is executed (i.e., Sleep or Idle mode is entered)

- When the device exits Sleep or Idle mode to resume normal operation

- By a CLRWDT instruction during normal execution

- Note: The CLRWDT and PWRSAV instructions clear the prescaler and postscaler counts when executed.

## FIGURE 27-2: WDT BLOCK DIAGRAM

## 27.5.2 SLEEP AND IDLE MODES

If the WDT is enabled, it continues to run during Sleep or Idle modes. When the WDT time-out occurs, the device wakes the device and code execution continues from where the PWRSAV instruction was executed. The corresponding SLEEP or IDLE bit (RCON<3,2>) needs to be cleared in software after the device wakes up.

## 27.5.3 ENABLING WDT

The WDT is enabled or disabled by the FWDTEN Configuration bit in the FWDT Configuration register. When the FWDTEN Configuration bit is set, the WDT is always enabled.

The WDT can be optionally controlled in software when the FWDTEN Configuration bit has been programmed to '0'. The WDT is enabled in software by setting the SWDTEN control bit (RCON<5>). The SWDTEN control bit is cleared on any device Reset. The software WDT option allows the user application to enable the WDT for critical code segments and disable the WDT during non-critical segments for maximum power savings.

The WDT flag bit, WDTO (RCON<4>), is not automatically cleared following a WDT time-out. To detect subsequent WDT events, the flag must be cleared in software.

## 27.5.4 WDT WINDOW

The Watchdog Timer has an optional Windowed mode, enabled by programming the WINDIS bit in the WDT Configuration register (FWDT<6>). In the Windowed mode (WINDIS = 0), the WDT should be cleared based on the settings in the programmable Watchdog Timer Window select bits (WDTWIN<1:0>).

| DC CHARACTERISTICS |        |                                         | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |   |    |    |                                                                                                                                                   |  |  |

|--------------------|--------|-----------------------------------------|-------------------------------------------------------|---|----|----|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Param<br>No.       | Symbol | Characteristic                          | Min. Typ. Max. Units Conditions                       |   |    |    |                                                                                                                                                   |  |  |

|                    | liL    | Input Leakage Current <sup>(1,2)</sup>  |                                                       |   |    |    |                                                                                                                                                   |  |  |

| DI50               |        | I/O Pins 5V Tolerant <sup>(3)</sup>     | -1                                                    | — | +1 | μA | $\label{eq:VSS} \begin{split} &V{\sf SS} \leq V{\sf PIN} \leq V{\sf DD}, \\ &P{\sf in \ at \ high-impedance} \end{split}$                         |  |  |

| DI51               |        | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1                                                    | _ | +1 | μA | $\label{eq:VSS} \begin{array}{l} VSS \leq VPIN \leq VDD, \\ Pin \mbox{ at high-impedance}, \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \end{array}$ |  |  |

| DI51a              |        | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1                                                    | _ | +1 | μA | Analog pins shared with external reference pins, $-40^{\circ}C \le TA \le +85^{\circ}C$                                                           |  |  |

| DI51b              |        | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1                                                    | _ | +1 | μA | $Vss \le VPIN \le VDD,$<br>Pin at high-impedance,<br>-40°C ≤ TA ≤ +125°C                                                                          |  |  |

| DI51c              |        | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1                                                    | _ | +1 | μA | Analog pins shared with external reference pins, $-40^{\circ}C \le TA \le +125^{\circ}C$                                                          |  |  |

| DI55               |        | MCLR                                    | -5                                                    | — | +5 | μA | $Vss \leq V \text{PIN} \leq V \text{DD}$                                                                                                          |  |  |

| DI56               |        | OSC1                                    | -5                                                    | — | +5 | μΑ | $\label{eq:VSS} \begin{split} &V{\sf SS} \leq V{\sf PIN} \leq V{\sf DD}, \\ &X{\sf T} \text{ and }H{\sf S} \text{ modes} \end{split}$             |  |  |

## TABLE 30-11: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS (CONTINUED)

**Note 1:** The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current can be measured at different input voltages.

- 2: Negative current is defined as current sourced by the pin.

- 3: See the "Pin Diagrams" section for the 5V tolerant I/O pins.

- 4: VIL source < (Vss 0.3). Characterized but not tested.

- **5:** Non-5V tolerant pins VIH source > (VDD + 0.3), 5V tolerant pins VIH source > 5.5V. Characterized but not tested.

- 6: Digital 5V tolerant pins cannot tolerate any "positive" input injection current from input sources > 5.5V.

- 7: Non-zero injection currents can affect the ADC results by approximately 4-6 counts.

8: Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the mathematical "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. Characterized but not tested.

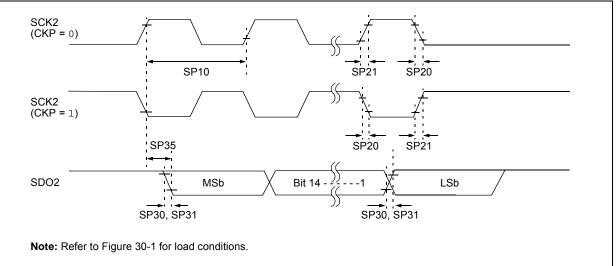

| AC CHARACTERISTICS   |                                          |                                             | Standard Operating Conditions: 3.0V to 3.6V<br>(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |     |     |     |  |  |

|----------------------|------------------------------------------|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|--|--|

| Maximum<br>Data Rate | Master<br>Transmit Only<br>(Half-Duplex) | Master<br>Transmit/Receive<br>(Full-Duplex) | Slave<br>Transmit/Receive<br>(Full-Duplex)                                                                                                                                                                  | CKE | СКР | SMP |  |  |

| 15 MHz               | Table 30-33                              | _                                           | _                                                                                                                                                                                                           | 0,1 | 0,1 | 0,1 |  |  |

| 9 MHz                | _                                        | Table 30-34                                 | —                                                                                                                                                                                                           | 1   | 0,1 | 1   |  |  |

| 9 MHz                | —                                        | Table 30-35                                 | —                                                                                                                                                                                                           | 0   | 0,1 | 1   |  |  |

| 15 MHz               | —                                        | —                                           | Table 30-36                                                                                                                                                                                                 | 1   | 0   | 0   |  |  |

| 11 MHz               | —                                        | —                                           | Table 30-37                                                                                                                                                                                                 | 1   | 1   | 0   |  |  |

| 15 MHz               | _                                        | —                                           | Table 30-38                                                                                                                                                                                                 | 0   | 1   | 0   |  |  |

| 11 MHz               | _                                        | —                                           | Table 30-39                                                                                                                                                                                                 | 0   | 0   | 0   |  |  |

## TABLE 30-33: SPI2 MAXIMUM DATA/CLOCK RATE SUMMARY

## FIGURE 30-14: SPI2 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 0) TIMING CHARACTERISTICS

| AC CHA       | RACTER     | ISTICS                        |                           | Standard Operating Conditions: 3.0V to 3.6V<br>(unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |             |         |                        |  |

|--------------|------------|-------------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------|------------------------|--|

| Param<br>No. | Symbol     | Characteristic <sup>(4)</sup> |                           | Min. <sup>(1)</sup>                                                                                                                                                                                             | -40<br>Max. | Units   | Conditions             |  |

| IM10         | TLO:SCL    | Clock Low Time                | 100 kHz mode              | Tcy/2 (BRG + 2)                                                                                                                                                                                                 | _           | μS      |                        |  |

|              |            |                               | 400 kHz mode              | TCY/2 (BRG + 2)                                                                                                                                                                                                 |             | ,<br>μS |                        |  |

|              |            |                               | 1 MHz mode <sup>(2)</sup> | TCY/2 (BRG + 2)                                                                                                                                                                                                 |             | μs      |                        |  |

| IM11         | THI:SCL    | Clock High Time               | 100 kHz mode              | Tcy/2 (BRG + 2)                                                                                                                                                                                                 |             | μS      |                        |  |

|              |            |                               | 400 kHz mode              | Tcy/2 (BRG + 2)                                                                                                                                                                                                 |             | μs      |                        |  |

|              |            |                               | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 2)                                                                                                                                                                                                 | _           | μS      |                        |  |

| IM20         | TF:SCL     | SDAx and SCLx                 | 100 kHz mode              | _                                                                                                                                                                                                               | 300         | ns      | CB is specified to be  |  |

|              |            | Fall Time                     | 400 kHz mode              | 20 + 0.1 Св                                                                                                                                                                                                     | 300         | ns      | from 10 to 400 pF      |  |

|              |            |                               | 1 MHz mode <sup>(2)</sup> | _                                                                                                                                                                                                               | 100         | ns      |                        |  |

| IM21         | TR:SCL     | SDAx and SCLx                 | 100 kHz mode              | _                                                                                                                                                                                                               | 1000        | ns      | CB is specified to be  |  |

|              |            | Rise Time                     | 400 kHz mode              | 20 + 0.1 Св                                                                                                                                                                                                     | 300         | ns      | from 10 to 400 pF      |  |

|              |            |                               | 1 MHz mode <sup>(2)</sup> |                                                                                                                                                                                                                 | 300         | ns      |                        |  |

| IM25         | TSU:DAT    | Data Input                    | 100 kHz mode              | 250                                                                                                                                                                                                             |             | ns      |                        |  |

|              |            | Setup Time                    | 400 kHz mode              | 100                                                                                                                                                                                                             |             | ns      |                        |  |

|              |            |                               | 1 MHz mode <sup>(2)</sup> | 40                                                                                                                                                                                                              |             | ns      |                        |  |

| IM26 THD:DAT | Data Input | 100 kHz mode                  | 0                         |                                                                                                                                                                                                                 | μS          |         |                        |  |

|              |            | Hold Time                     | 400 kHz mode              | 0                                                                                                                                                                                                               | 0.9         | μs      |                        |  |

|              |            |                               | 1 MHz mode <sup>(2)</sup> | 0.2                                                                                                                                                                                                             |             | μS      |                        |  |

| IM30         | TSU:STA    | Start Condition               | 100 kHz mode              | TCY/2 (BRG + 2)                                                                                                                                                                                                 | —           | μS      | Only relevant for      |  |

|              |            | Setup Time                    | 400 kHz mode              | TCY/2 (BRG + 2)                                                                                                                                                                                                 | —           | μS      | Repeated Start         |  |

|              |            |                               | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 2)                                                                                                                                                                                                 |             | μS      | condition              |  |

| IM31         | THD:STA    | Start Condition               | 100 kHz mode              | TCY/2 (BRG + 2)                                                                                                                                                                                                 | —           | μS      | After this period, the |  |

|              |            | Hold Time                     | 400 kHz mode              | TCY/2 (BRG +2)                                                                                                                                                                                                  | —           | μS      | first clock pulse is   |  |

|              |            |                               | 1 MHz mode <sup>(2)</sup> | TCY/2 (BRG + 2)                                                                                                                                                                                                 |             | μS      | generated              |  |

| IM33         | Tsu:sto    | Stop Condition                | 100 kHz mode              | TCY/2 (BRG + 2)                                                                                                                                                                                                 | _           | μS      |                        |  |

|              |            | Setup Time                    | 400 kHz mode              | TCY/2 (BRG + 2)                                                                                                                                                                                                 |             | μS      |                        |  |

|              |            |                               | 1 MHz mode <sup>(2)</sup> | TCY/2 (BRG + 2)                                                                                                                                                                                                 |             | μS      |                        |  |

| IM34         | THD:STO    | Stop Condition                | 100 kHz mode              | TCY/2 (BRG + 2)                                                                                                                                                                                                 |             | μS      |                        |  |

|              |            | Hold Time                     | 400 kHz mode              | TCY/2 (BRG + 2)                                                                                                                                                                                                 |             | μS      |                        |  |

|              |            |                               | 1 MHz mode <sup>(2)</sup> | TCY/2 (BRG + 2)                                                                                                                                                                                                 |             | μS      |                        |  |

| IM40         | TAA:SCL    | Output Valid                  | 100 kHz mode              | —                                                                                                                                                                                                               | 3500        | ns      |                        |  |

|              |            | From Clock                    | 400 kHz mode              |                                                                                                                                                                                                                 | 1000        | ns      |                        |  |

|              |            |                               | 1 MHz mode <sup>(2)</sup> |                                                                                                                                                                                                                 | 400         | ns      |                        |  |

| IM45         | TBF:SDA    | Bus Free Time                 | 100 kHz mode              | 4.7                                                                                                                                                                                                             |             | μS      | Time the bus must be   |  |

|              |            |                               | 400 kHz mode              | 1.3                                                                                                                                                                                                             |             | μS      | free before a new      |  |

|              |            |                               | 1 MHz mode <sup>(2)</sup> | 0.5                                                                                                                                                                                                             | —           | μS      | transmission can star  |  |

| IM50         | Св         | Bus Capacitive L              | oading                    | —                                                                                                                                                                                                               | 400         | pF      |                        |  |

| IM51         | Tpgd       | Pulse Gobbler De              | elay                      | 65                                                                                                                                                                                                              | 390         | ns      | (Note 3)               |  |

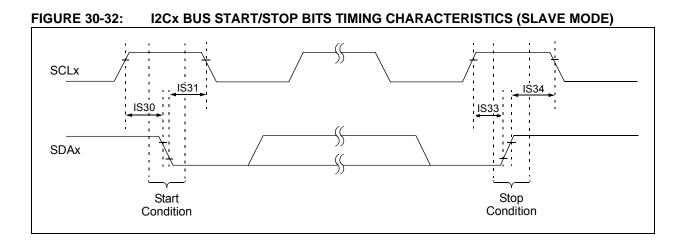

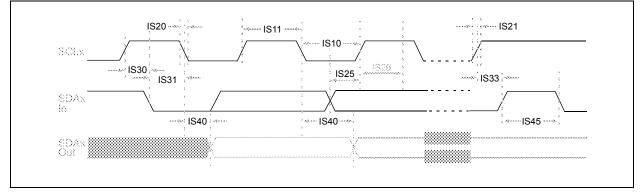

## TABLE 30-49: I2Cx BUS DATA TIMING REQUIREMENTS (MASTER MODE)

Note 1: BRG is the value of the l<sup>2</sup>C<sup>™</sup> Baud Rate Generator. Refer to "Inter-Integrated Circuit (l<sup>2</sup>C<sup>™</sup>)" (DS70330) in the "dsPIC33/PIC24 Family Reference Manual". Please see the Microchip web site for the latest family reference manual sections.

- 2: Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

- **3:** Typical value for this parameter is 130 ns.

- 4: These parameters are characterized, but not tested in manufacturing.

## 31.1 High-Temperature DC Characteristics

## TABLE 31-1: OPERATING MIPS VS. VOLTAGE

|                |                                                   |                 | Max MIPS                                                              |

|----------------|---------------------------------------------------|-----------------|-----------------------------------------------------------------------|

| Characteristic | VDD Range Temperature Range<br>(in Volts) (in °C) |                 | dsPIC33EPXXXGP50X,<br>dsPIC33EPXXXMC20X/50X and<br>PIC24EPXXXGP/MC20X |

| HDC5           | 3.0 to 3.6V <sup>(1)</sup>                        | -40°C to +150°C | 40                                                                    |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN. Analog modules, such as the ADC, may have degraded performance. Device functionality is tested but not characterized.

## TABLE 31-2: THERMAL OPERATING CONDITIONS

| Rating                                                                                                                                                                                 | Symbol | Min | Тур         | Max  | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|-------------|------|------|

| High-Temperature Devices                                                                                                                                                               |        |     |             |      |      |

| Operating Junction Temperature Range                                                                                                                                                   | TJ     | -40 | _           | +155 | °C   |

| Operating Ambient Temperature Range                                                                                                                                                    | TA     | -40 | _           | +150 | °C   |

| Power Dissipation:<br>Internal Chip Power Dissipation:<br>$PINT = VDD x (IDD - \Sigma IOH)$<br>I/O Pin Power Dissipation:<br>$I/O = \Sigma (\{VDD - VOH\} x IOH) + \Sigma (VOL x IOL)$ | PD     | I   | Pint + Pi/c | )    | W    |

| Maximum Allowed Power Dissipation                                                                                                                                                      | PDMAX  | (   | TJ — TA)/θJ | IA   | W    |

## TABLE 31-3: DC TEMPERATURE AND VOLTAGE SPECIFICATIONS

| DC CHARACTERISTICS |           |                | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ |     |     |       |                 |  |  |

|--------------------|-----------|----------------|-----------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------|-----------------|--|--|

| Parameter<br>No.   | Symbol    | Characteristic | Min                                                                                                                               | Тур | Max | Units | Conditions      |  |  |

| Operating V        | /oltage   |                |                                                                                                                                   |     |     |       |                 |  |  |

| HDC10              | Supply Vo | Supply Voltage |                                                                                                                                   |     |     |       |                 |  |  |

|                    | Vdd       | _              | 3.0                                                                                                                               | 3.3 | 3.6 | V     | -40°C to +150°C |  |  |

# 44-Terminal Very Thin Leadless Array Package (TL) – 6x6x0.9 mm Body With Exposed Pad [VTLA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

DETAIL A

|                         | MILLIMETERS |          |          |       |  |

|-------------------------|-------------|----------|----------|-------|--|

| Dimension               | Limits      | MIN      | NOM      | MAX   |  |

| Number of Pins          | Ν           |          | 44       |       |  |

| Number of Pins per Side | ND          |          | 12       |       |  |

| Number of Pins per Side | NE          | 10       |          |       |  |

| Pitch                   | е           | 0.50 BSC |          |       |  |

| Overall Height          | Α           | 0.80     | 0.90     | 1.00  |  |

| Standoff                | A1          | 0.025    | -        | 0.075 |  |

| Overall Width           | Е           |          | 6.00 BSC |       |  |

| Exposed Pad Width       | E2          | 4.40     | 4.55     | 4.70  |  |

| Overall Length          | D           |          | 6.00 BSC |       |  |

| Exposed Pad Length      | D2          | 4.40     | 4.55     | 4.70  |  |

| Contact Width           | b           | 0.20     | 0.25     | 0.30  |  |

| Contact Length          | L           | 0.20     | 0.25     | 0.30  |  |

| Contact-to-Exposed Pad  | К           | 0.20     | -        | -     |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-157C Sheet 2 of 2

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| ECAN Module                |          |

|----------------------------|----------|

| Control Registers          |          |

| Modes of Operation         |          |

| Overview                   |          |

| Resources                  |          |

| Electrical Characteristics | 401      |

| AC                         | 413, 471 |

| Enhanced CAN (ECAN) Module |          |

| Equations                  |          |

| Device Operating Frequency | 154      |

| FPLLO Calculation          |          |

| Fvco Calculation           | 154      |

| Errata                     | 23       |

## F

| Filter Capacitor (CEFC) Specifications | 403 |

|----------------------------------------|-----|

| Flash Program Memory                   | 119 |

| Control Registers                      | 120 |

| Programming Operations                 | 120 |

| Resources                              | 120 |

| RTSP Operation                         | 120 |

| Table Instructions                     | 119 |

| Flexible Configuration                 |     |

## G

|                                              | 2  |

|----------------------------------------------|----|

| Application Examples                         | 2  |

| Basic Connection Requirements2               | 29 |

| CPU Logic Filter Capacitor Connection (VCAP) | 60 |

| Decoupling Capacitors 2                      | 29 |

| External Oscillator Pins3                    | 51 |

| ICSP Pins                                    | 51 |

| Master Clear (MCLR) Pin 3                    | 60 |

| Oscillator Value Conditions on Start-up      | 52 |

| Unused I/Os 3                                | 2  |

## Н

| High-Speed PWM                              | 225 |

|---------------------------------------------|-----|

| Control Registers                           |     |

| Faults                                      | 225 |

| Resources                                   | 229 |

| High-Temperature Electrical Characteristics |     |

| Absolute Maximum Ratings                    |     |

## I

| -                                    |          |

|--------------------------------------|----------|

| I/O Ports                            |          |

| Helpful Tips                         |          |

| Parallel I/O (PIO)                   |          |

| Resources                            |          |

| Write/Read Timing                    |          |

| In-Circuit Debugger                  |          |

| In-Circuit Emulation                 |          |

| In-Circuit Serial Programming (ICSP) | 379, 386 |

| Input Capture                        |          |

| Control Registers                    |          |

| Resources                            |          |

| Input Change Notification (ICN)      |          |

| Instruction Addressing Modes         | 112      |

| File Register Instructions           |          |

| Fundamental Modes Supported          |          |

| MAC Instructions                     |          |

| MCU Instructions                     |          |

| Move and Accumulator Instructions    | 113      |

| Other Instructions                   | 113      |

|                                      |          |

| Instruction Set                             |       |

|---------------------------------------------|-------|

| Overview                                    | . 390 |

| Summary                                     | . 387 |

| Symbols Used in Opcode Descriptions         | . 388 |

| Inter-Integrated Circuit (I <sup>2</sup> C) | . 273 |

| Control Registers                           | . 276 |

| Resources                                   | . 275 |

| Internal RC Oscillator                      |       |

| Use with WDT                                | . 385 |

| Internet Address                            | . 524 |

| Interrupt Controller                        |       |

| Control and Status Registers                | . 131 |

| INTCON1                                     | . 131 |

| INTCON2                                     | . 131 |

| INTCON3                                     | . 131 |

| INTCON4                                     | . 131 |

| INTTREG                                     | . 131 |

| Interrupt Vector Details                    | . 129 |

| Interrupt Vector Table (IVT)                | . 127 |

| Reset Sequence                              | . 127 |

| Resources                                   | . 131 |

|                                             |       |

## J

| JTAG Boundary Scan Interface | 379 |

|------------------------------|-----|

| JTAG Interface               | 386 |

## Μ

| 9 |

|---|

| 5 |

| 2 |

| 4 |

| 4 |

| 5 |

| 4 |

| 4 |

| 4 |

| 8 |

| 9 |

| 9 |

| 9 |

|   |

| 7 |

| 9 |

| 8 |

| 8 |

|   |

# 0

| Op Amp                     |     |

|----------------------------|-----|

| Application Considerations | 358 |

| Configuration A            | 358 |

| Configuration B            | 359 |

| Op Amp/Comparator          | 355 |

| Control Registers          | 360 |

| Resources                  | 359 |

| Open-Drain Configuration   | 174 |

| Oscillator                 |     |

| Control Registers          | 156 |

| Resources                  | 155 |

| Output Compare             | 219 |

| Control Registers          | 221 |

| Resources                  | 220 |

|                            |     |