Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 70 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 53                                                                             |

| Program Memory Size        | 512KB (170K x 24)                                                              |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | ·                                                                              |

| RAM Size                   | 24K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-TQFP                                                                        |

| Supplier Device Package    | 64-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep512gp206-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

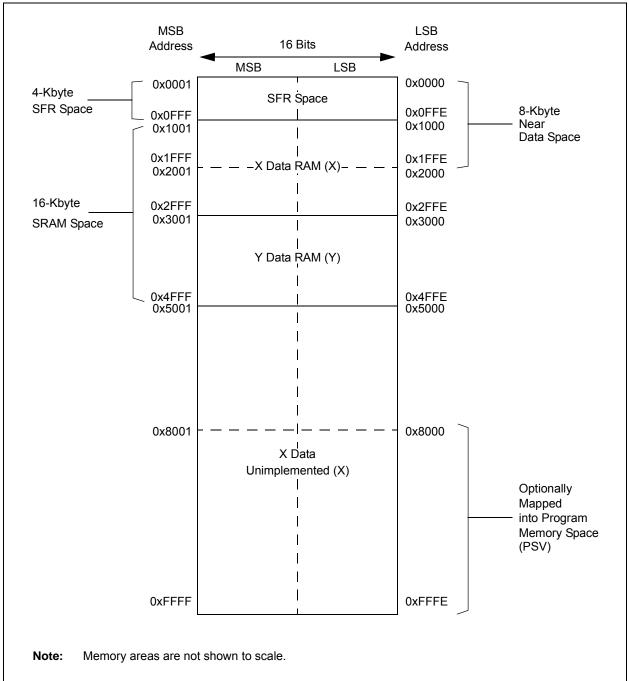

# FIGURE 4-9: DATA MEMORY MAP FOR dsPIC33EP128MC20X/50X AND dsPIC33EP128GP50X DEVICES

| IABLE 4-2  | 23: E | CAN1 I               | REGIST | ER MA  | P WHE  | N WIN  | (CICIE | <l1<0></l1<0> | •) = 1 FC | OR dsPIC | 33EPX    | XXMC/G | P50X D | EVICES | ONLY ( |       | NUED) |               |

|------------|-------|----------------------|--------|--------|--------|--------|--------|---------------|-----------|----------|----------|--------|--------|--------|--------|-------|-------|---------------|

| File Name  | Addr  | Bit 15               | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9         | Bit 8     | Bit 7    | Bit 6    | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

| C1RXF11EID | 046E  |                      |        |        | EID<   | :15:8> |        |               |           |          |          |        | EID<   | 7:0>   |        |       |       | xxxx          |

| C1RXF12SID | 0470  |                      |        |        | SID<   | :10:3> |        |               |           |          | SID<2:0> |        | _      | EXIDE  | _      | EID<1 | 7:16> | xxxx          |

| C1RXF12EID | 0472  |                      |        |        | EID<   | :15:8> |        |               |           | EID<7:0> |          |        |        |        |        | xxxx  |       |               |

| C1RXF13SID | 0474  |                      |        |        | SID<   | :10:3> |        |               |           |          | SID<2:0> |        | _      | EXIDE  | —      | EID<1 | 7:16> | xxxx          |

| C1RXF13EID | 0476  |                      |        |        | EID<   | :15:8> |        |               |           |          |          |        | EID<   | 7:0>   |        |       |       | xxxx          |

| C1RXF14SID | 0478  |                      |        |        | SID<   | :10:3> |        |               |           |          | SID<2:0> |        | _      | EXIDE  | —      | EID<1 | 7:16> | xxxx          |

| C1RXF14EID | 047A  |                      |        |        | EID<   | :15:8> |        |               |           |          |          |        | EID<   | 7:0>   |        |       |       | xxxx          |

| C1RXF15SID | 047C  | C SID<10:3> SID<2:0> |        |        |        |        |        | _             | EXIDE     | _        | EID<1    | 7:16>  | xxxx   |        |        |       |       |               |

| C1RXF15EID | 047E  |                      |        |        | EID<   | :15:8> |        |               |           |          |          |        | EID<   | 7:0>   |        |       |       | xxxx          |

#### ECANI DECISTED MAD WHEN WIN (CICTDI 1 -0.) 1 EOD doDIC22EDXXXMC/CDE0X DEVICES ONLY (CONTINUED) TARIE 1 22.

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# 7.3 Interrupt Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

#### 7.3.1 KEY RESOURCES

- "Interrupts" (DS70600) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- Development Tools

### 7.4 Interrupt Control and Status Registers

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices implement the following registers for the interrupt controller:

- INTCON1

- INTCON2

- INTCON3

- INTCON4

- INTTREG

#### 7.4.1 INTCON1 THROUGH INTCON4

Global interrupt control functions are controlled from INTCON1, INTCON2, INTCON3 and INTCON4.

INTCON1 contains the Interrupt Nesting Disable bit (NSTDIS), as well as the control and status flags for the processor trap sources.

The INTCON2 register controls external interrupt request signal behavior and also contains the Global Interrupt Enable bit (GIE).

INTCON3 contains the status flags for the DMA and DO stack overflow status trap sources.

The INTCON4 register contains the software generated hard trap status bit (SGHT).

# 7.4.2 IFSx

The IFSx registers maintain all of the interrupt request flags. Each source of interrupt has a status bit, which is set by the respective peripherals or external signal and is cleared via software.

#### 7.4.3 IECx

The IECx registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

#### 7.4.4 IPCx

The IPCx registers are used to set the Interrupt Priority Level (IPL) for each source of interrupt. Each user interrupt source can be assigned to one of eight priority levels.

#### 7.4.5 INTTREG

The INTTREG register contains the associated interrupt vector number and the new CPU Interrupt Priority Level, which are latched into the Vector Number bits (VECNUM<7:0>) and Interrupt Priority Level bits (ILR<3:0>) fields in the INTTREG register. The new Interrupt Priority Level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the same sequence as they are listed in Table 7-1. For example, the INT0 (External Interrupt 0) is shown as having Vector Number 8 and a natural order priority of 0. Thus, the INT0IF bit is found in IFS0<0>, the INT0IE bit in IEC0<0> and the INT0IP bits in the first position of IPC0 (IPC0<2:0>).

#### 7.4.6 STATUS/CONTROL REGISTERS

Although these registers are not specifically part of the interrupt control hardware, two of the CPU Control registers contain bits that control interrupt functionality. For more information on these registers refer to "**CPU**" (DS70359) in the "dsPIC33/PIC24 Family Reference Manual".

- The CPU STATUS Register, SR, contains the IPL<2:0> bits (SR<7:5>). These bits indicate the current CPU Interrupt Priority Level. The user software can change the current CPU Interrupt Priority Level by writing to the IPLx bits.

- The CORCON register contains the IPL3 bit which, together with IPL<2:0>, also indicates the current CPU priority level. IPL3 is a read-only bit so that trap events cannot be masked by the user software.

All Interrupt registers are described in Register 7-3 through Register 7-7 in the following pages.

# 8.0 DIRECT MEMORY ACCESS (DMA)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Direct Memory Access (DMA)" (DS70348) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

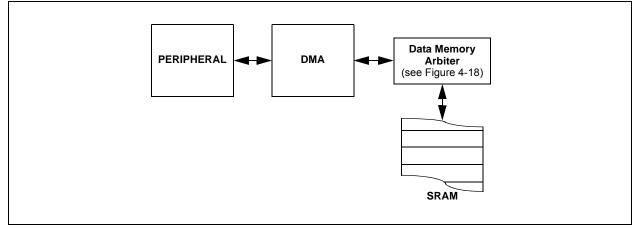

The DMA Controller transfers data between Peripheral Data registers and Data Space SRAM

In addition, DMA can access the entire data memory space. The Data Memory Bus Arbiter is utilized when either the CPU or DMA attempts to access SRAM, resulting in potential DMA or CPU stalls.

The DMA Controller supports 4 independent channels. Each channel can be configured for transfers to or from selected peripherals. Some of the peripherals supported by the DMA Controller include:

- ECAN<sup>™</sup>

- Analog-to-Digital Converter (ADC)

- Serial Peripheral Interface (SPI)

- UART

- Input Capture

- Output Compare

Refer to Table 8-1 for a complete list of supported peripherals.

# FIGURE 8-1: DMA CONTROLLER MODULE

#### REGISTER 9-2: CLKDIV: CLOCK DIVISOR REGISTER (CONTINUED)

- **Note 1:** The DOZE<2:0> bits can only be written to when the DOZEN bit is clear. If DOZEN = 1, any writes to DOZE<2:0> are ignored.

- $\label{eq:constraint} \textbf{2:} \quad \text{This bit is cleared when the ROI bit is set and an interrupt occurs.}$

- **3:** The DOZEN bit cannot be set if DOZE<2:0> = 000. If DOZE<2:0> = 000, any attempt by user software to set the DOZEN bit is ignored.

#### REGISTER 11-15: RPINR37: PERIPHERAL PIN SELECT INPUT REGISTER 37 (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

| U-0                | R/W-0                                      | R/W-0                                           | R/W-0                                      | R/W-0                              | R/W-0         | R/W-0              | R/W-0 |  |  |

|--------------------|--------------------------------------------|-------------------------------------------------|--------------------------------------------|------------------------------------|---------------|--------------------|-------|--|--|

|                    |                                            |                                                 |                                            | SYNCI1R<6:03                       | >             |                    |       |  |  |

| bit 15             |                                            |                                                 |                                            |                                    |               |                    | bit 8 |  |  |

|                    |                                            |                                                 |                                            |                                    |               |                    |       |  |  |

| U-0                | U-0                                        | U-0                                             | U-0                                        | U-0                                | U-0           | U-0                | U-0   |  |  |

| _                  |                                            |                                                 | —                                          |                                    |               | <u> </u>           | _     |  |  |

| bit 7              |                                            |                                                 |                                            |                                    |               |                    | bit 0 |  |  |

|                    |                                            |                                                 |                                            |                                    |               |                    |       |  |  |

| Legend:            |                                            |                                                 |                                            |                                    |               |                    |       |  |  |

| R = Readab         | ole bit                                    | W = Writable                                    | bit                                        | U = Unimplemented bit, read as '0' |               |                    |       |  |  |

| -n = Value a       | it POR                                     | '1' = Bit is set                                |                                            | '0' = Bit is clea                  | ared          | x = Bit is unknown |       |  |  |

|                    |                                            |                                                 |                                            |                                    |               |                    |       |  |  |

|                    |                                            |                                                 |                                            |                                    |               |                    |       |  |  |

| bit 15             | Unimplemer                                 | nted: Read as '                                 | 0'                                         |                                    |               |                    |       |  |  |

| bit 15<br>bit 14-8 | SYNCI1R<6:                                 |                                                 | M Synchroniz                               | zation Input 1 to<br>nbers)        | the Correspon | ding RPn Pin b     | its   |  |  |

|                    | SYNCI1R<6:<br>(see Table 11                | <b>0&gt;:</b> Assign PW                         | M Synchroniz selection nur                 |                                    | the Correspon | ding RPn Pin b     | its   |  |  |

|                    | SYNCI1R<6:<br>(see Table 11                | • <b>0&gt;:</b> Assign PWI<br>I-2 for input pin | M Synchroniz selection nur                 |                                    | the Correspon | ding RPn Pin b     | its   |  |  |

|                    | SYNCI1R<6:<br>(see Table 11                | • <b>0&gt;:</b> Assign PWI<br>I-2 for input pin | M Synchroniz selection nur                 |                                    | the Correspon | ding RPn Pin b     | its   |  |  |

|                    | SYNCI1R<6:<br>(see Table 11<br>1111001 = I | • <b>0&gt;:</b> Assign PWI<br>I-2 for input pin | M Synchroniz<br>selection nur<br>121<br>P1 |                                    | the Correspon | ding RPn Pin b     | its   |  |  |

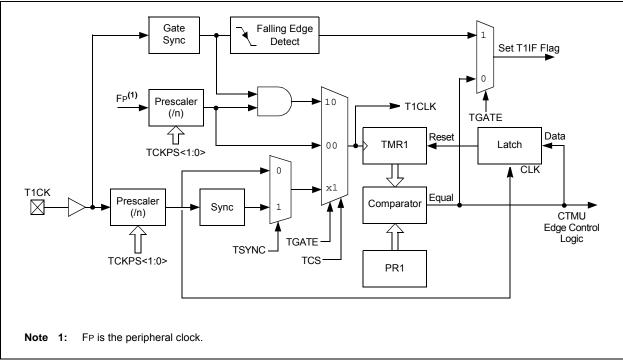

# 12.0 TIMER1

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Timer1 module is a 16-bit timer that can operate as a free-running interval timer/counter.

The Timer1 module has the following unique features over other timers:

- Can be operated in Asynchronous Counter mode from an external clock source

- The external clock input (T1CK) can optionally be synchronized to the internal device clock and the clock synchronization is performed after the prescaler

- A block diagram of Timer1 is shown in Figure 12-1.

The Timer1 module can operate in one of the following modes:

- Timer mode

- · Gated Timer mode

- Synchronous Counter mode

- · Asynchronous Counter mode

In Timer and Gated Timer modes, the input clock is derived from the internal instruction cycle clock (FCY). In Synchronous and Asynchronous Counter modes, the input clock is derived from the external clock input at the T1CK pin.

The Timer modes are determined by the following bits:

- Timer Clock Source Control bit (TCS): T1CON<1>

- Timer Synchronization Control bit (TSYNC): T1CON<2>

- Timer Gate Control bit (TGATE): T1CON<6>

Timer control bit setting for different operating modes are given in the Table 12-1.

| Mode                    | TCS | TGATE | TSYNC |  |  |

|-------------------------|-----|-------|-------|--|--|

| Timer                   | 0   | 0     | х     |  |  |

| Gated Timer             | 0   | 1     | x     |  |  |

| Synchronous<br>Counter  | 1   | х     | 1     |  |  |

| Asynchronous<br>Counter | 1   | x     | 0     |  |  |

#### TABLE 12-1: TIMER MODE SETTINGS

#### FIGURE 12-1: 16-BIT TIMER1 MODULE BLOCK DIAGRAM

#### 14.1 Input Capture Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 14.1.1 KEY RESOURCES

- "Input Capture" (DS70352) in the "dsPIC33/ PIC24 Family Reference Manual"

- · Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|------------------|-----------------|-------|

|                 |       |                  | TRGC  | MP<15:8>          |                  |                 |       |

| bit 15          |       |                  |       |                   |                  |                 | bit 8 |

|                 |       |                  |       |                   |                  |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|                 |       |                  | TRGC  | MP<7:0>           |                  |                 |       |

| bit 7           |       |                  |       |                   |                  |                 | bit 0 |

| Legend:         |       |                  |       |                   |                  |                 |       |

| R = Readable    | bit   | W = Writable t   | oit   | U = Unimplem      | nented bit, read | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

# REGISTER 16-14: TRIGX: PWMx PRIMARY TRIGGER COMPARE VALUE REGISTER

bit 15-0 TRGCMP<15:0>: Trigger Control Value bits

When the primary PWMx functions in local time base, this register contains the compare values that can trigger the ADC module.

# 21.2 Modes of Operation

The ECAN module can operate in one of several operation modes selected by the user. These modes include:

- · Initialization mode

- Disable mode

- Normal Operation mode

- · Listen Only mode

- Listen All Messages mode

- Loopback mode

Modes are requested by setting the REQOP<2:0> bits (CxCTRL1<10:8>). Entry into a mode is Acknowledged by monitoring the OPMODE<2:0> bits (CxCTRL1<7:5>). The module does not change the mode and the OPMODEx bits until a change in mode is acceptable, generally during bus Idle time, which is defined as at least 11 consecutive recessive bits.

#### 21.3 ECAN Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 21.3.1 KEY RESOURCES

- "Enhanced Controller Area Network (ECAN™)" (DS70353) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- · Development Tools

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| RXOVF15 | RXOVF14 | RXOVF13 | RXOVF12 | RXOVF11 | RXOVF10 | RXOVF9 | RXOVF8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

|         |         |         |         |         |         |        |        |

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

#### REGISTER 21-24: CxRXOVF1: ECANx RECEIVE BUFFER OVERFLOW REGISTER 1

| RXOVF7  | RXOVF6 | RXOVF5         | RXOVF4            | RXOVF3         | RXOVF2             | RXOVF1 | RXOVF0 |

|---------|--------|----------------|-------------------|----------------|--------------------|--------|--------|

| bit 7   |        |                |                   |                |                    |        | bit 0  |

|         |        |                |                   |                |                    |        |        |

| Legend: |        | C = Writable b | oit, but only '0' | can be writter | n to clear the bit |        |        |

| Legend:           | C = Writable bit, but only '0' can be written to clear the bit |                      |                    |  |  |  |

|-------------------|----------------------------------------------------------------|----------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit U = Unimplemented bit, read as '0'            |                      |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set                                               | '0' = Bit is cleared | x = Bit is unknown |  |  |  |

bit 15-0 RXOVF<15:0>: Receive Buffer n Overflow bits

1 = Module attempted to write to a full buffer (set by module)

0 = No overflow condition (cleared by user software)

#### REGISTER 21-25: CxRXOVF2: ECANx RECEIVE BUFFER OVERFLOW REGISTER 2

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXOVF31 | RXOVF30 | RXOVF29 | RXOVF28 | RXOVF27 | RXOVF26 | RXOVF25 | RXOVF24 |

| bit 15  |         |         |         |         |         |         | bit 8   |

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXOVF23 | RXOVF22 | RXOVF21 | RXOVF20 | RXOVF19 | RXOVF18 | RXOVF17 | RXOVF16 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           | C = Writable bit, but or | C = Writable bit, but only '0' can be written to clear the bit |                    |  |  |  |  |

|-------------------|--------------------------|----------------------------------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit         | W = Writable bit U = Unimplemented bit, read as '0'            |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set         | '0' = Bit is cleared                                           | x = Bit is unknown |  |  |  |  |

bit 15-0 RXOVF<31:16>: Receive Buffer n Overflow bits

1 = Module attempted to write to a full buffer (set by module)

0 = No overflow condition (cleared by user software)

# 22.0 CHARGE TIME MEASUREMENT UNIT (CTMU)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Charge Time Measurement Unit (CTMU)" (DS70661) in the "dsPIC33/PIC24 Family Reference Manual", which is available on the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Charge Time Measurement Unit is a flexible analog module that provides accurate differential time measurement between pulse sources, as well as asynchronous pulse generation. Its key features include:

- Four Edge Input Trigger Sources

- Polarity Control for Each Edge Source

- Control of Edge Sequence

- Control of Response to Edges

- · Precise Time Measurement Resolution of 1 ns

- Accurate Current Source Suitable for Capacitive Measurement

- On-Chip Temperature Measurement using a Built-in Diode

Together with other on-chip analog modules, the CTMU can be used to precisely measure time, measure capacitance, measure relative changes in capacitance or generate output pulses that are independent of the system clock.

The CTMU module is ideal for interfacing with capacitive-based sensors. The CTMU is controlled through three registers: CTMUCON1, CTMUCON2 and CTMUICON. CTMUCON1 and CTMUCON2 enable the module and control edge source selection, edge source polarity selection and edge sequencing. The CTMUICON register controls the selection and trim of the current source.

#### REGISTER 23-2: AD1CON2: ADC1 CONTROL REGISTER 2 (CONTINUED)

| bit 1 | BUFM: Buffer Fill Mode Select bit                                                                                                                                                                                               |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Starts the buffer filling the first half of the buffer on the first interrupt and the second half of the buffer on next interrupt</li> <li>0 = Always starts filling the buffer from the start address.</li> </ul> |

| bit 0 | ALTS: Alternate Input Sample Mode Select bit                                                                                                                                                                                    |

1 = Uses channel input selects for Sample MUXA on first sample and Sample MUXB on next sample 0 = Always uses channel input selects for Sample MUXA

| R/W-0           | R/W-0                                                                                                                      | R/W-0                                                                             | R/W-0                                                                                                                                             | R/W-0                                                                                                        | R/W-0            | R/W-0           | R/W-0   |

|-----------------|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|------------------|-----------------|---------|

| PTGCLK2         | PTGCLK1                                                                                                                    | PTGCLK0                                                                           | PTGDIV4                                                                                                                                           | PTGDIV3                                                                                                      | PTGDIV2          | PTGDIV1         | PTGDIV0 |

| bit 15          | 1                                                                                                                          | 1                                                                                 | 1                                                                                                                                                 |                                                                                                              |                  |                 | bit     |

| R/W-0           | R/W-0                                                                                                                      | R/W-0                                                                             | R/W-0                                                                                                                                             | U-0                                                                                                          | R/W-0            | R/W-0           | R/W-0   |

| PTGPWD3         | PTGPWD2                                                                                                                    | PTGPWD1                                                                           | PTGPWD0                                                                                                                                           | _                                                                                                            | PTGWDT2          | PTGWDT1         | PTGWDTC |

| bit 7           |                                                                                                                            |                                                                                   |                                                                                                                                                   |                                                                                                              |                  |                 | bit     |

| Legend:         |                                                                                                                            |                                                                                   |                                                                                                                                                   |                                                                                                              |                  |                 |         |

| R = Readable    | bit                                                                                                                        | W = Writable                                                                      | bit                                                                                                                                               | U = Unimpler                                                                                                 | mented bit, read | l as '0'        |         |

| -n = Value at F | POR                                                                                                                        | '1' = Bit is set                                                                  |                                                                                                                                                   | '0' = Bit is cle                                                                                             | ared             | x = Bit is unkr | nown    |

| bit 15-13       | 111 = Reserv<br>110 = Reserv<br>101 = PTG m<br>100 = PTG m<br>011 = PTG m<br>010 = PTG m<br>001 = PTG m                    |                                                                                   | urce will be T3<br>urce will be T2<br>urce will be T1<br>urce will be TA<br>urce will be Fc                                                       | BCLK<br>PCLK<br>ICLK<br>D<br>DSC                                                                             |                  |                 |         |

| bit 12-8        | PTGDIV<4:0> 11111 = Divic 11110 = Divic                                                                                    | de-by-31<br>de-by-2                                                               | Clock Presca                                                                                                                                      | ler (divider) bi                                                                                             | ts               |                 |         |

| bit 7-4         | PTGPWD<3:0<br>1111 = All trig<br>1110 = All trig<br>0001 = All trig                                                        | <b>D&gt;:</b> PTG Trigge<br>gger outputs ar<br>gger outputs ar<br>gger outputs ar | e 16 PTG cloc<br>e 15 PTG cloc<br>e 2 PTG clock                                                                                                   | k cycles wide<br>k cycles wide<br>cycles wide                                                                |                  |                 |         |

| bit 3           | -                                                                                                                          | ted: Read as '                                                                    |                                                                                                                                                   |                                                                                                              |                  |                 |         |

| bit 2-0         | PTGWDT<2:0<br>111 = Watcho<br>110 = Watcho<br>101 = Watcho<br>011 = Watcho<br>011 = Watcho<br>010 = Watcho<br>010 = Watcho |                                                                                   | Watchdog Tir<br>ime-out after 5<br>ime-out after 2<br>ime-out after 1<br>ime-out after 3<br>ime-out after 3<br>ime-out after 3<br>ime-out after 8 | 12 PTG clock<br>56 PTG clock<br>28 PTG clock<br>4 PTG clocks<br>2 PTG clocks<br>6 PTG clocks<br>6 PTG clocks | S<br>S           | 5               |         |

# REGISTER 24-2: PTGCON: PTG CONTROL REGISTER

|          |        |                                                             | (unless            | s otherw | ating Covinse stat | <b>ed)</b><br>-40°C | s: 3.0V to 3.6V<br>$\leq$ TA $\leq$ +85°C for Industrial<br>$\leq$ TA $\leq$ +125°C for Extended                                                                       |

|----------|--------|-------------------------------------------------------------|--------------------|----------|--------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param.   | Symbol | Characteristic                                              | Min.               | Тур.     | Max.               | Units               | Conditions                                                                                                                                                             |

| DO10 Vol |        | Output Low Voltage<br>4x Sink Driver Pins <sup>(2)</sup>    |                    |          | 0.4                | V                   | VDD = 3.3V,<br>$IOL \le 6 \text{ mA}, -40^{\circ}\text{C} \le Ta \le +85^{\circ}\text{C}$<br>$IOL \le 5 \text{ mA}, +85^{\circ}\text{C} < Ta \le +125^{\circ}\text{C}$ |

|          |        | Output Low Voltage<br>8x Sink Driver Pins <sup>(3)</sup>    | _                  |          | 0.4                | V                   |                                                                                                                                                                        |

| DO20 V   | Vон    | Output High Voltage<br>4x Source Driver Pins <sup>(2)</sup> | 2.4                |          | _                  | V                   | $IOH \ge -10 \text{ mA}, \text{ VDD} = 3.3 \text{ V}$                                                                                                                  |

|          |        | Output High Voltage<br>8x Source Driver Pins <sup>(3)</sup> | 2.4                | _        | —                  | V                   | $IOH \ge -15 \text{ mA}, \text{ VDD} = 3.3 \text{ V}$                                                                                                                  |

| DO20A    | Von1   | Output High Voltage                                         | 1.5(1)             | _        |                    | V                   | $IOH \ge -14 \text{ mA}, \text{ VDD} = 3.3 \text{V}$                                                                                                                   |

|          |        | 4x Source Driver Pins <sup>(2)</sup>                        | 2.0 <sup>(1)</sup> | _        | —                  |                     | $IOH \ge -12 \text{ mA}, \text{ VDD} = 3.3 \text{V}$                                                                                                                   |

|          |        |                                                             | 3.0(1)             |          | —                  |                     | $IOH \ge -7 \text{ mA}, \text{ VDD} = 3.3 \text{V}$                                                                                                                    |

|          |        | Output High Voltage                                         | 1.5 <sup>(1)</sup> | —        | —                  | V                   | $IOH \geq -22  mA,  VDD = 3.3  V$                                                                                                                                      |

|          |        | 8x Source Driver Pins <sup>(3)</sup>                        | 2.0 <sup>(1)</sup> | —        | —                  |                     | IOH $\geq$ -18 mA, VDD = 3.3V                                                                                                                                          |

|          |        |                                                             | 3.0(1)             | —        | —                  | 1                   | IOH $\geq$ -10 mA, VDD = 3.3V                                                                                                                                          |

### TABLE 30-12: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

Note 1: Parameters are characterized but not tested.

2: Includes all I/O pins that are not 8x Sink Driver pins (see below).

Includes the following pins:

For devices with less than 64 pins: RA3, RA4, RA9, RB<7:15> and RC3

For 64-pin devices: RA4, RA9, RB<7:15>, RC3 and RC15

#### TABLE 30-13: ELECTRICAL CHARACTERISTICS: BOR

| DC CHARACTERISTICS |        | $ \begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)}^{(1)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array} $ |                     |      |      |       |                        |

|--------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|------|-------|------------------------|

| Param<br>No.       | Symbol | Characteristic                                                                                                                                                                                                                                                                            | Min. <sup>(2)</sup> | Тур. | Max. | Units | Conditions             |

| BO10               | VBOR   | BOR Event on VDD Transition<br>High-to-Low                                                                                                                                                                                                                                                | 2.65                | _    | 2.95 | V     | VDD<br>(Notes 2 and 3) |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance.

**2:** Parameters are for design guidance only and are not tested in manufacturing.

3: The VBOR specification is relative to VDD.

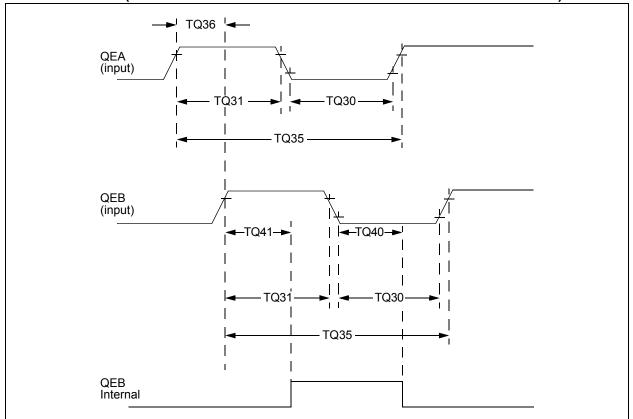

#### FIGURE 30-12: QEA/QEB INPUT CHARACTERISTICS (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

#### TABLE 30-31: QUADRATURE DECODER TIMING REQUIREMENTS (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

| AC CHARACTERISTICS |        |                                                    | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Indus $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extermination |      |       |                                                         |  |

|--------------------|--------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|---------------------------------------------------------|--|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>                      | Тур. <sup>(2)</sup>                                                                                                                                                                                  | Max. | Units | Conditions                                              |  |

| TQ30               | TQUL   | Quadrature Input Low Time                          | 6 Tcy                                                                                                                                                                                                |      | ns    |                                                         |  |

| TQ31               | TQUH   | Quadrature Input High Time                         | 6 Tcy                                                                                                                                                                                                | —    | ns    |                                                         |  |

| TQ35               | TQUIN  | Quadrature Input Period                            | 12 TCY                                                                                                                                                                                               | _    | ns    |                                                         |  |

| TQ36               | TQUP   | Quadrature Phase Period                            | 3 TCY                                                                                                                                                                                                | —    | ns    |                                                         |  |

| TQ40               | TQUFL  | Filter Time to Recognize Low, with Digital Filter  | 3 * N * Tcy                                                                                                                                                                                          | —    | ns    | N = 1, 2, 4, 16, 32, 64, 128<br>and 256 <b>(Note 3)</b> |  |

| TQ41               | TQUFH  | Filter Time to Recognize High, with Digital Filter | 3 * N * Tcy                                                                                                                                                                                          | —    | ns    | N = 1, 2, 4, 16, 32, 64, 128<br>and 256 <b>(Note 3)</b> |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

**2:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

3: N = Index Channel Digital Filter Clock Divide Select bits. Refer to "Quadrature Encoder Interface (QEI)" (DS70601) in the "*dsPIC33/PIC24 Family Reference Manual*". Please see the Microchip web site for the latest family reference manual sections.

| DC CH                         | ARACTERIS       | STICS                                                | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)(1)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                     |      |        |                                                   |  |  |  |  |

|-------------------------------|-----------------|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|--------|---------------------------------------------------|--|--|--|--|

| Param<br>No.                  | Symbol          | Characteristic                                       | Min.                                                                                                                                                                                                    | Тур. <sup>(2)</sup> | Max. | Units  | Conditions                                        |  |  |  |  |

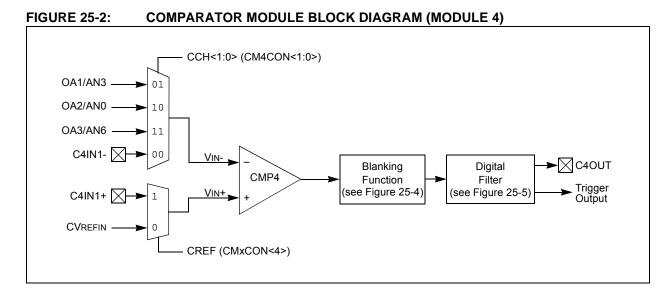

| Comparator AC Characteristics |                 |                                                      |                                                                                                                                                                                                         |                     |      |        |                                                   |  |  |  |  |

| CM10                          | TRESP           | Response Time <sup>(3)</sup>                         | —                                                                                                                                                                                                       | 19                  | —    | ns     | V+ input step of 100 mV<br>V- input held at VDD/2 |  |  |  |  |

| CM11                          | Тмс2о∨          | Comparator Mode<br>Change to Output Valid            | —                                                                                                                                                                                                       | -                   | 10   | μs     |                                                   |  |  |  |  |

| Compa                         | rator DC Ch     | naracteristics                                       |                                                                                                                                                                                                         |                     |      |        |                                                   |  |  |  |  |

| CM30                          | VOFFSET         | Comparator Offset<br>Voltage                         | —                                                                                                                                                                                                       | ±10                 | 40   | mV     |                                                   |  |  |  |  |

| CM31                          | VHYST           | Input Hysteresis<br>Voltage <sup>(3)</sup>           | _                                                                                                                                                                                                       | 30                  | —    | mV     |                                                   |  |  |  |  |

| CM32                          | Trise/<br>Tfall | Comparator Output Rise/<br>Fall Time <sup>(3)</sup>  | —                                                                                                                                                                                                       | 20                  | —    | ns     | 1 pF load capacitance<br>on input                 |  |  |  |  |

| CM33                          | Vgain           | Open-Loop Voltage<br>Gain <sup>(3)</sup>             | —                                                                                                                                                                                                       | 90                  | —    | db     |                                                   |  |  |  |  |

| CM34                          | VICM            | Input Common-Mode<br>Voltage                         | AVss                                                                                                                                                                                                    | -                   | AVDD | V      |                                                   |  |  |  |  |

| Op Am                         | p AC Chara      | cteristics                                           |                                                                                                                                                                                                         |                     |      |        |                                                   |  |  |  |  |

| CM20                          | SR              | Slew Rate <sup>(3)</sup>                             |                                                                                                                                                                                                         | 9                   | _    | V/µs   | 10 pF load                                        |  |  |  |  |

| CM21a                         | Рм              | Phase Margin<br>(Configuration A) <sup>(3,4)</sup>   | _                                                                                                                                                                                                       | 55                  | —    | Degree | G = 100V/V; 10 pF load                            |  |  |  |  |

| CM21b                         | Рм              | Phase Margin<br>(Configuration B) <sup>(3,5)</sup>   | _                                                                                                                                                                                                       | 40                  | _    | Degree | G = 100V/V; 10 pF load                            |  |  |  |  |

| CM22                          | Gм              | Gain Margin <sup>(3)</sup>                           | —                                                                                                                                                                                                       | 20                  | _    | db     | G = 100V/V; 10 pF load                            |  |  |  |  |

| CM23a                         | Gвw             | Gain Bandwidth<br>(Configuration A) <sup>(3,4)</sup> | _                                                                                                                                                                                                       | 10                  | —    | MHz    | 10 pF load                                        |  |  |  |  |

| CM23b                         | GBW             | Gain Bandwidth<br>(Configuration B) <sup>(3,5)</sup> | —                                                                                                                                                                                                       | 6                   | —    | MHz    | 10 pF load                                        |  |  |  |  |

# TABLE 30-53: OP AMP/COMPARATOR SPECIFICATIONS

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

- 2: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

- 3: Parameter is characterized but not tested in manufacturing.

- 4: See Figure 25-6 for configuration information.

- 5: See Figure 25-7 for configuration information.

- 6: Resistances can vary by ±10% between op amps.

| AC CHARACTERISTICS |        |                                                                                                     | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) <sup>(1)</sup>                                                                                         |         |       |       |                                         |  |

|--------------------|--------|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------|-------|-----------------------------------------|--|

|                    |        |                                                                                                     | $\begin{array}{ll} Operating \ temperature \\ -40^\circ C \leq TA \leq +85^\circ C \ for \ Industrial \\ -40^\circ C \leq TA \leq +125^\circ C \ for \ Extended \end{array}$ |         |       |       |                                         |  |

| Param<br>No.       | Symbol | Characteristic                                                                                      | Min.                                                                                                                                                                         | Тур.    | Max.  | Units | Conditions                              |  |

|                    |        | Cloci                                                                                               | k Parame                                                                                                                                                                     | eters   |       |       |                                         |  |

| AD50               | TAD    | ADC Clock Period                                                                                    | 76                                                                                                                                                                           | _       | _     | ns    |                                         |  |

| AD51               | tRC    | ADC Internal RC Oscillator Period <sup>(2)</sup>                                                    |                                                                                                                                                                              | 250     | _     | ns    |                                         |  |

|                    | •      | Conv                                                                                                | version F                                                                                                                                                                    | Rate    |       | •     |                                         |  |

| AD55               | tCONV  | Conversion Time                                                                                     |                                                                                                                                                                              | 12 Tad  | _     |       |                                         |  |

| AD56               | FCNV   | Throughput Rate                                                                                     | _                                                                                                                                                                            | —       | 1.1   | Msps  | Using simultaneous sampling             |  |

| AD57a              | TSAMP  | Sample Time when Sampling any ANx Input                                                             | 2 Tad                                                                                                                                                                        | —       | _     | —     |                                         |  |

| AD57b              | TSAMP  | Sample Time when Sampling the Op Amp Outputs (Configuration A and Configuration B) <sup>(4,5)</sup> | 4 Tad                                                                                                                                                                        | _       | —     | —     |                                         |  |

|                    |        | Timin                                                                                               | g Param                                                                                                                                                                      | eters   |       |       |                                         |  |

| AD60               | tPCS   | Conversion Start from Sample<br>Trigger <sup>(2,3)</sup>                                            | 2 Tad                                                                                                                                                                        | —       | 3 Tad | _     | Auto-convert trigger is<br>not selected |  |

| AD61               | tPSS   | Sample Start from Setting<br>Sample (SAMP) bit <sup>(2,3))</sup>                                    | 2 Tad                                                                                                                                                                        | —       | 3 Tad | —     |                                         |  |

| AD62               | tcss   | Conversion Completion to<br>Sample Start (ASAM = 1) <sup>(2,3)</sup>                                | _                                                                                                                                                                            | 0.5 Tad |       | —     |                                         |  |

| AD63               | tdpu   | Time to Stabilize Analog Stage<br>from ADC Off to ADC On <sup>(2,3)</sup>                           |                                                                                                                                                                              | —       | 20    | μs    | (Note 6)                                |  |

#### TABLE 30-61: ADC CONVERSION (10-BIT MODE) TIMING REQUIREMENTS

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

- 2: Parameters are characterized but not tested in manufacturing.

- **3:** Because the sample caps will eventually lose charge, clock rates below 10 kHz may affect linearity performance, especially at elevated temperatures.

- 4: See Figure 25-6 for configuration information.

- 5: See Figure 25-7 for configuration information.

- 6: The parameter, tDPU, is the time required for the ADC module to stabilize at the appropriate level when the module is turned on (ADON (AD1CON1<15>) = 1). During this time, the ADC result is indeterminate.

#### TABLE 30-62: DMA MODULE TIMING REQUIREMENTS

| AC CH        |                                |                             | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |       |            |  |  |

|--------------|--------------------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------------|--|--|

| Param<br>No. | Characteristic                 | Min.                        | Тур. <sup>(1)</sup>                                                                                                                                                                                                                                                                     | Max. | Units | Conditions |  |  |

| DM1          | DMA Byte/Word Transfer Latency | 1 TCY <sup>(2)</sup> — — ns |                                                                                                                                                                                                                                                                                         |      |       |            |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Because DMA transfers use the CPU data bus, this time is dependent on other functions on the bus.

<sup>© 2011-2013</sup> Microchip Technology Inc.

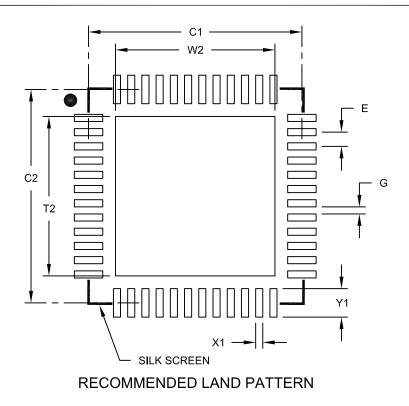

48-Lead Ultra Thin Plastic Quad Flat, No Lead Package (MV) - 6x6 mm Body [UQFN] With 0.40 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                             | MILLIMETERS      |  |          |      |

|-----------------------------|------------------|--|----------|------|

| Dimensior                   | Dimension Limits |  |          | MAX  |

| Contact Pitch               | E                |  | 0.40 BSC |      |

| Optional Center Pad Width   | W2               |  |          | 4.45 |

| Optional Center Pad Length  | T2               |  |          | 4.45 |

| Contact Pad Spacing         | C1               |  | 6.00     |      |

| Contact Pad Spacing         | C2               |  | 6.00     |      |

| Contact Pad Width (X28)     | X1               |  |          | 0.20 |

| Contact Pad Length (X28) Y1 |                  |  |          | 0.80 |

| Distance Between Pads       | 0.20             |  |          |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2153A