Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 512KB (170K x 24)                                                               |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | · ·                                                                             |

| RAM Size                   | 24K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

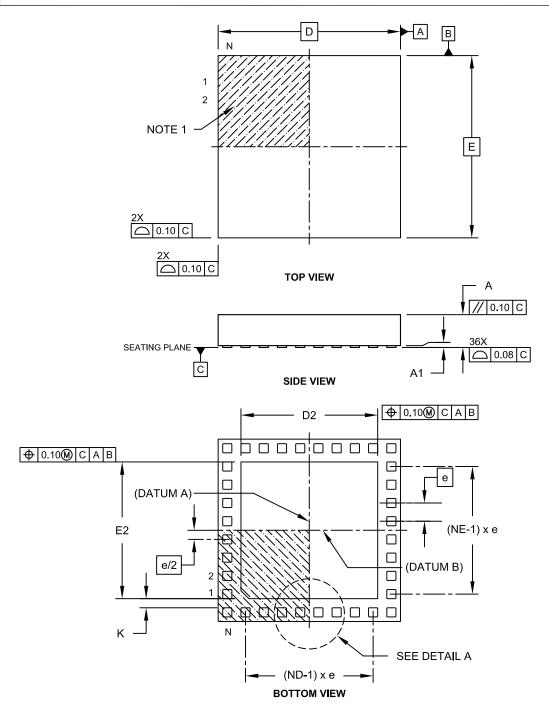

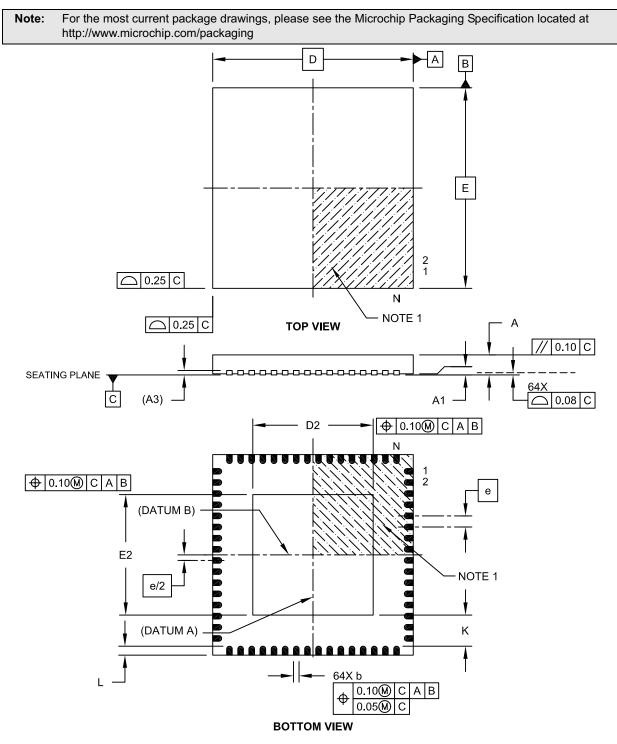

| Package / Case             | 64-TQFP                                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep512gp206t-e-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8  | Bit 7 | Bit 6  | Bit 5       | Bit 4  | Bit 3  | Bit 2    | Bit 1        | Bit 0   | All<br>Resets |

|--------------|-------|--------|--------|------------|--------|--------|--------|------------|--------|-------|--------|-------------|--------|--------|----------|--------------|---------|---------------|

| IFS0         | 0800  | _      | DMA1IF | AD1IF      | U1TXIF | U1RXIF | SPI1IF | SPI1EIF    | T3IF   | T2IF  | OC2IF  | IC2IF       | DMA0IF | T1IF   | OC1IF    | IC1IF        | INTOIF  | 0000          |

| IFS1         | 0802  | U2TXIF | U2RXIF | INT2IF     | T5IF   | T4IF   | OC4IF  | OC3IF      | DMA2IF | _     | _      | _           | INT1IF | CNIF   | CMIF     | MI2C1IF      | SI2C1IF | 0000          |

| IFS2         | 0804  | _      |        | _          | _      | _      |        | _          | _      |       | IC4IF  | IC3IF       | DMA3IF | _      | —        | SPI2IF       | SPI2EIF | 0000          |

| IFS3         | 0806  | _      | _      | _          | _      | _      | QEI1IF | PSEMIF     | _      | _     | _      | _           | _      | _      | MI2C2IF  | SI2C2IF      | —       | 0000          |

| IFS4         | 0808  | -      | _      | CTMUIF     | _      | _      |        | —          | _      | _     |        | _           | _      | CRCIF  | U2EIF    | U1EIF        |         | 0000          |

| IFS5         | 080A  | PWM2IF | PWM1IF | _          | _      | _      |        | —          | _      | _     |        | _           | _      | _      | _        | _            |         | 0000          |

| IFS6         | 080C  | _      | _      | _          | _      | _      |        | —          | _      | _     |        | _           | _      | _      | _        | _            | PWM3IF  | 0000          |

| IFS8         | 0810  | JTAGIF | ICDIF  | _          | _      | _      |        | —          | _      | _     |        | _           | _      | _      | _        | _            | _       | 0000          |

| IFS9         | 0812  | _      | _      | _          | -      | _      |        | _          | —      | _     | PTG3IF | PTG2IF      | PTG1IF | PTG0IF | PTGWDTIF | PTGSTEPIF    |         | 0000          |

| IEC0         | 0820  | _      | DMA1IE | AD1IE      | U1TXIE | U1RXIE | SPI1IE | SPI1EIE    | T3IE   | T2IE  | OC2IE  | IC2IE       | DMA0IE | T1IE   | OC1IE    | IC1IE        | INTOIE  | 0000          |

| IEC1         | 0822  | U2TXIE | U2RXIE | INT2IE     | T5IE   | T4IE   | OC4IE  | OC3IE      | DMA2IE | —     | _      | —           | INT1IE | CNIE   | CMIE     | MI2C1IE      | SI2C1IE | 0000          |

| IEC2         | 0824  | _      | _      | —          | -      | _      |        | —          | —      | _     | IC4IE  | IC3IE       | DMA3IE |        | _        | SPI2IE       | SPI2EIE | 0000          |

| IEC3         | 0826  | _      | _      | _          | -      | _      | QEI1IE | PSEMIE     | —      | _     | _      | —           | —      | -      | MI2C2IE  | SI2C2IE      | —       | 0000          |

| IEC4         | 0828  | _      | _      | CTMUIE     | -      | _      |        | —          | —      | _     | _      | —           | _      | CRCIE  | U2EIE    | U1EIE        |         | 0000          |

| IEC5         | 082A  | PWM2IE | PWM1IE | —          | -      | _      | _      | _          | —      | _     | _      | —           | _      |        | _        | —            |         | 0000          |

| IEC6         | 082C  | _      | _      | _          | -      | _      | _      | _          | —      | _     | _      | —           | _      | -      | _        | —            | PWM3IE  | 0000          |

| IEC8         | 0830  | JTAGIE | ICDIE  | _          | -      | _      | _      | _          | —      | _     | _      | —           | _      | -      | _        | —            | —       | 0000          |

| IEC9         | 0832  | _      | _      | _          | -      | _      | _      | _          | —      | _     | PTG3IE | PTG2IE      | PTG1IE | PTG0IE | PTGWDTIE | PTGSTEPIE    |         | 0000          |

| IPC0         | 0840  | _      |        | T1IP<2:0>  |        | _      |        | OC1IP<2:0  | )>     | _     |        | IC1IP<2:0>  |        |        |          | INT0IP<2:0>  |         | 4444          |

| IPC1         | 0842  | _      |        | T2IP<2:0>  |        | _      |        | OC2IP<2:0  | )>     | _     |        | IC2IP<2:0>  |        | -      | [        | DMA0IP<2:0>  |         | 4444          |

| IPC2         | 0844  | _      | -      | U1RXIP<2:0 | >      | _      | :      | SPI1IP<2:0 | )>     | _     |        | SPI1EIP<2:0 | >      | -      |          | T3IP<2:0>    |         | 4444          |

| IPC3         | 0846  | _      | _      | —          | —      | _      | C      | MA1IP<2:   | 0>     | _     |        | AD1IP<2:0>  |        | -      |          | U1TXIP<2:0>  |         | 0444          |

| IPC4         | 0848  | _      |        | CNIP<2:0>  |        | _      |        | CMIP<2:0   | >      | _     |        | MI2C1IP<2:0 | >      | -      | 5        | SI2C1IP<2:0> |         | 4444          |

| IPC5         | 084A  | _      | _      | —          | —      | _      |        | —          | —      | _     | _      | —           | —      |        |          | INT1IP<2:0>  |         | 0004          |

| IPC6         | 084C  | _      |        | T4IP<2:0>  |        | _      |        | OC4IP<2:0  | )>     |       |        | OC3IP<2:0>  |        |        | [        | DMA2IP<2:0>  |         | 4444          |

| IPC7         | 084E  | _      |        | U2TXIP<2:0 | >      | _      | ι      | J2RXIP<2:  | 0>     |       |        | INT2IP<2:0> | •      |        |          | T5IP<2:0>    |         | 4444          |

| IPC8         | 0850  | _      | _      | —          | —      | _      |        | —          | —      | _     |        | SPI2IP<2:0> | •      |        | 5        | SPI2EIP<2:0> |         | 0044          |

| IPC9         | 0852  | _      | _      | _          | -      | _      |        | IC4IP<2:0  | >      | _     |        | IC3IP<2:0>  |        |        | [        | DMA3IP<2:0>  |         | 0444          |

| IPC12        | 0858  | _      | _      | _          |        | _      | N      | 112C2IP<2: | 0>     | _     |        | SI2C2IP<2:0 | >      |        | _        | —            |         | 0440          |

| IPC14        | 085C  | _      | _      | _          | _      | _      | (      | QEI1IP<2:0 | )>     | _     |        | PSEMIP<2:0  | >      | _      | _        | _            | _       | 0440          |

| IPC16        | 0860  | _      |        | CRCIP<2:0  | >      | _      |        | U2EIP<2:0  | >      | _     |        | U1EIP<2:0>  |        | _      | _        | _            | _       | 4440          |

| IPC19        | 0866  | _      | _      | —          | —      | _      | —      | —          | _      | _     |        | CTMUIP<2:0  | >      | _      | _        | _            | _       | 0040          |

| IPC23        | 086E  | _      | F      | PWM2IP<2:0 | )>     | _      | P      | WM1IP<2:   | 0>     | _     | _      | _           | —      | _      | _        | _            | _       | 4400          |

| IPC24        | 0870  | _      | _      |            |        | _      |        | _          |        |       | _      | _           | _      | _      | F        | PWM3IP<2:0>  |         | 4004          |

#### TABLE 4-4: INTERRUPT CONTROLLER REGISTER MAP FOR PIC24EPXXXMC20X DEVICES ONLY

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| REGISTER 7-5: | INTCON3: INTERRUPT CONTROL REGISTER 3 |

|---------------|---------------------------------------|

| U-0          | U-0                                          | U-0             | U-0              | U-0              | U-0              | U-0                | U-0   |  |  |  |

|--------------|----------------------------------------------|-----------------|------------------|------------------|------------------|--------------------|-------|--|--|--|

|              | —                                            | _               | —                | —                | —                | —                  | _     |  |  |  |

| bit 15       |                                              |                 |                  |                  |                  | •                  | bit 8 |  |  |  |

|              |                                              |                 |                  |                  |                  |                    |       |  |  |  |

| U-0          | U-0                                          | R/W-0           | R/W-0            | U-0              | U-0              | U-0                | U-0   |  |  |  |

| —            | —                                            | DAE             | DOOVR            | —                | —                | —                  | —     |  |  |  |

| bit 7        |                                              |                 |                  |                  |                  |                    | bit 0 |  |  |  |

|              |                                              |                 |                  |                  |                  |                    |       |  |  |  |

| Legend:      |                                              |                 |                  |                  |                  |                    |       |  |  |  |

| R = Readab   | le bit                                       | W = Writable    | bit              | U = Unimplei     | mented bit, read | as '0'             |       |  |  |  |

| -n = Value a | It POR                                       | '1' = Bit is se | t                | '0' = Bit is cle | eared            | x = Bit is unknown |       |  |  |  |

|              |                                              |                 |                  |                  |                  |                    |       |  |  |  |

| bit 15-6     | Unimplemen                                   | ted: Read as    | '0'              |                  |                  |                    |       |  |  |  |

| bit 5        | DAE: DMA A                                   | ddress Error S  | Soft Trap Status | s bit            |                  |                    |       |  |  |  |

|              | 1 = DMA add                                  | ress error soft | trap has occur   | red              |                  |                    |       |  |  |  |

|              | 0 = DMA add                                  | ress error soft | trap has not o   | ccurred          |                  |                    |       |  |  |  |

| bit 4        | DOOVR: DO                                    | Stack Overflov  | v Soft Trap Sta  | tus bit          |                  |                    |       |  |  |  |

|              | 1 = DO stack overflow soft trap has occurred |                 |                  |                  |                  |                    |       |  |  |  |

| I = D0 | Stack Overnow  | 3011 11 ap 11 a3 | occurred     |

|--------|----------------|------------------|--------------|

| 0 = DO | stack overflow | soft trap has    | not occurred |

| bit 3-0 | Unimplemented: Read as '0' |

|---------|----------------------------|

|---------|----------------------------|

#### REGISTER 7-6: INTCON4: INTERRUPT CONTROL REGISTER 4

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|---------|-----|-----|-----|-----|-----|-----|-------|

| —       | —   | —   | —   | —   | —   | —   | —     |

| bit 15  |     |     |     |     | •   |     | bit 8 |

|         |     |     |     |     |     |     |       |

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 |

| _       | _   | —   |     | —   | —   | —   | SGHT  |

| bit 7   |     |     |     |     | •   |     | bit 0 |

|         |     |     |     |     |     |     |       |

| Legend: |     |     |     |     |     |     |       |

| 3                 |                                 |                      |                                    |  |  |  |  |

|-------------------|---------------------------------|----------------------|------------------------------------|--|--|--|--|

| R = Readable bit  | = Readable bit W = Writable bit |                      | U = Unimplemented bit, read as '0' |  |  |  |  |

| -n = Value at POR | '1' = Bit is set                | '0' = Bit is cleared | x = Bit is unknown                 |  |  |  |  |

|                   |                                 |                      |                                    |  |  |  |  |

bit 0

SGHT: Software Generated Hard Trap Status bit

1 = Software generated hard trap has occurred

0 = Software generated hard trap has not occurred

### 9.1 CPU Clocking System

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X family of devices provides six system clock options:

- Fast RC (FRC) Oscillator

- FRC Oscillator with Phase Locked Loop (PLL)

- · FRC Oscillator with Postscaler

- Primary (XT, HS or EC) Oscillator

- Primary Oscillator with PLL

- · Low-Power RC (LPRC) Oscillator

Instruction execution speed or device operating frequency, FCY, is given by Equation 9-1.

# EQUATION 9-1: DEVICE OPERATING FREQUENCY

FCY = Fosc/2

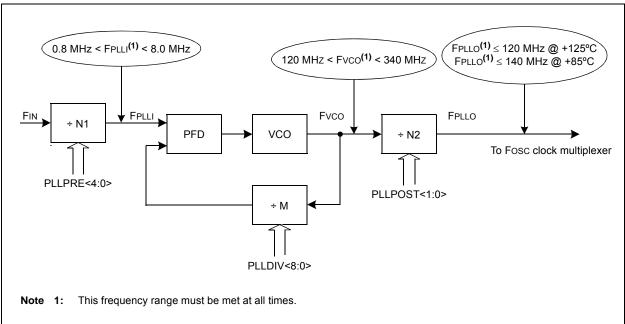

Figure 9-2 is a block diagram of the PLL module.

Equation 9-2 provides the relationship between input frequency (FIN) and output frequency (FPLLO). In clock modes S1 and S3, when the PLL output is selected, FOSC = FPLLO.

Equation 9-3 provides the relationship between input frequency (FIN) and VCO frequency (FVCO).

#### EQUATION 9-2: FPLLO CALCULATION

$$FPLLO = FIN \times \left(\frac{M}{N1 \times N2}\right) = FIN \times \left(\frac{(PLLDIV + 2)}{(PLLPRE + 2) \times 2(PLLPOST + 1)}\right)$$

Where:

N1 = PLLPRE + 2 $N2 = 2 \times (PLLPOST + 1)$

M = PLLDIV + 2

#### EQUATION 9-3: Fvco CALCULATION

$$Fvco = FIN \times \left(\frac{M}{N1}\right) = FIN \times \left(\frac{(PLLDIV + 2)}{(PLLPRE + 2)}\right)$$

DS70000657H-page 154

#### © 2011-2013 Microchip Technology Inc.

### FIGURE 9-2: PLL BLOCK DIAGRAM

| R/W-0         | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | R/W-0                                                             | R/W-0           | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |  |  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-----------------|-----------------------|-----------------------|-----------------------|-----------------------|--|--|

| ROON          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ROSSLP                                                            | ROSEL           | RODIV3 <sup>(1)</sup> | RODIV2 <sup>(1)</sup> | RODIV1 <sup>(1)</sup> | RODIV0 <sup>(1)</sup> |  |  |

| bit 15        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                   |                 |                       |                       | •                     | bit                   |  |  |

| U-0           | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | U-0                                                               | U-0             | U-0                   | U-0                   | U-0                   | U-0                   |  |  |

|               | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | _                                                                 |                 | _                     |                       | _                     |                       |  |  |

| bit 7         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                   |                 |                       |                       |                       | bit                   |  |  |

| Legend:       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                   |                 |                       |                       |                       |                       |  |  |

| R = Readable  | e bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | W = Writable                                                      | bit             | U = Unimpler          | nented bit, read      | l as '0'              |                       |  |  |

| -n = Value at |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | '1' = Bit is set                                                  |                 | '0' = Bit is cle      |                       | x = Bit is unkr       | iown                  |  |  |

| bit 14        | 0 = Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | e oscillator outp<br>e oscillator outp<br>i <b>ted:</b> Read as ' | out is disabled |                       | .K pin <sup>(2)</sup> |                       |                       |  |  |

| bit 13        | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ference Oscilla                                                   |                 | en hit                |                       |                       |                       |  |  |

|               | 1 = Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | e oscillator out<br>e oscillator out                              | out continues   | to run in Sleep       |                       |                       |                       |  |  |

| bit 12        | 1 = Oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -                                                                 | as the refere   | nce clock             |                       |                       |                       |  |  |

| bit 11-8      | 1 = Oscillator crystal is used as the reference clock<br>0 = System clock is used as the reference clock<br><b>RODIV&lt;3:0&gt;:</b> Reference Oscillator Divider bits <sup>(1)</sup><br>1111 = Reference clock divided by 32,768<br>1100 = Reference clock divided by 16,384<br>1101 = Reference clock divided by 4,096<br>1011 = Reference clock divided by 2,048<br>1010 = Reference clock divided by 2,048<br>1010 = Reference clock divided by 512<br>1000 = Reference clock divided by 256<br>0111 = Reference clock divided by 128<br>0110 = Reference clock divided by 32<br>0101 = Reference clock divided by 32<br>0102 = Reference clock divided by 4<br>0011 = Reference clock divided by 4<br>0010 = Reference clock divided by 4<br>0010 = Reference clock divided by 4<br>0011 = Reference clock divided by 4<br>0011 = Reference clock divided by 4<br>0011 = Reference clock divided by 4 |                                                                   |                 |                       |                       |                       |                       |  |  |

|               | 0000 = Refer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ence clock                                                        | -               |                       |                       |                       |                       |  |  |

#### REGISTER 9-5: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

- **Note 1:** The reference oscillator output must be disabled (ROON = 0) before writing to these bits.

- 2: This pin is remappable. See Section 11.4 "Peripheral Pin Select (PPS)" for more information.

- g) The TRISx registers control only the digital I/O output buffer. Any other dedicated or remappable active "output" will automatically override the TRIS setting. The TRISx register does not control the digital logic "input" buffer. Remappable digital "inputs" do not automatically override TRIS settings, which means that the TRISx bit must be set to input for pins with only remappable input function(s) assigned

- h) All analog pins are enabled by default after any Reset and the corresponding digital input buffer on the pin has been disabled. Only the Analog Pin Select registers control the digital input buffer, *not* the TRISx register. The user must disable the analog function on a pin using the Analog Pin Select registers in order to use any "digital input(s)" on a corresponding pin, no exceptions.

#### 11.6 I/O Ports Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

#### 11.6.1 KEY RESOURCES

- "I/O Ports" (DS70598) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

| R/W-0              | U-0                  | R/W-0                 | U-0                   | U-0 | U-0 | U-0                  | U-0   |

|--------------------|----------------------|-----------------------|-----------------------|-----|-----|----------------------|-------|

| TON <sup>(1)</sup> | —                    | TSIDL <sup>(2)</sup>  | —                     | —   | —   | —                    | —     |

| bit 15             |                      |                       |                       |     |     |                      | bit 8 |

|                    |                      |                       |                       |     |     |                      |       |

| U-0                | R/W-0                | R/W-0                 | R/W-0                 | U-0 | U-0 | R/W-0                | U-0   |

| —                  | TGATE <sup>(1)</sup> | TCKPS1 <sup>(1)</sup> | TCKPS0 <sup>(1)</sup> |     | —   | TCS <sup>(1,3)</sup> | —     |

| bit 7              |                      |                       |                       |     |     |                      | bit 0 |

|                    |                      |                       |                       |     |     |                      |       |

#### REGISTER 13-2: TyCON: (TIMER3 AND TIMER5) CONTROL REGISTER

| Legend:      |                        |                                                                               |                                          |                                   |

|--------------|------------------------|-------------------------------------------------------------------------------|------------------------------------------|-----------------------------------|

| R = Readal   | ole bit                | W = Writable bit                                                              | U = Unimplemented bit                    | , read as '0'                     |

| -n = Value a | at POR                 | '1' = Bit is set                                                              | '0' = Bit is cleared                     | x = Bit is unknown                |

| bit 15       | TON: Tin               | nery On bit <sup>(1)</sup>                                                    |                                          |                                   |

|              |                        | s 16-bit Timery<br>s 16-bit Timery                                            |                                          |                                   |

| bit 14       | •                      | mented: Read as '0'                                                           |                                          |                                   |

| bit 13       | -                      | imery Stop in Idle Mode bit                                                   | 2)                                       |                                   |

|              |                        | ontinues module operation winues module operation in Id                       | when device enters Idle mode<br>lle mode |                                   |

| bit 12-7     | Unimple                | mented: Read as '0'                                                           |                                          |                                   |

| bit 6        | TGATE:                 | Timery Gated Time Accumu                                                      | lation Enable bit <sup>(1)</sup>         |                                   |

|              | When TC<br>This bit is | <u>CS = 1:</u><br>s ignored.                                                  |                                          |                                   |

|              |                        | <u>CS = 0:</u><br>d time accumulation is enab<br>d time accumulation is disab |                                          |                                   |

| bit 5-4      | TCKPS<                 | 1:0>: Timery Input Clock Pre                                                  | escale Select bits <sup>(1)</sup>        |                                   |

|              | 11 <b>= 1:2</b> 5      |                                                                               |                                          |                                   |

|              | 10 = 1:64<br>01 = 1:8  | 1                                                                             |                                          |                                   |

|              | 01 = 1.8               |                                                                               |                                          |                                   |

| bit 3-2      | Unimple                | mented: Read as '0'                                                           |                                          |                                   |

| bit 1        | -                      | nery Clock Source Select bit                                                  | (1,3)                                    |                                   |

|              |                        | nal clock is from pin, TyCK (<br>nal clock (FP)                               | (on the rising edge)                     |                                   |

| bit 0        | Unimple                | mented: Read as '0'                                                           |                                          |                                   |

|              |                        | peration is enabled (T2CON<br>set through TxCON.                              | <3> = 1), these bits have no e           | ffect on Timery operation; all ti |

|              |                        |                                                                               |                                          |                                   |

2: When 32-bit timer operation is enabled (T32 = 1) in the Timerx Control register (TxCON<3>), the TSIDL bit must be cleared to operate the 32-bit timer in Idle mode.

3: The TyCK pin is not available on all timers. See the "Pin Diagrams" section for the available pins.

#### **REGISTER 15-1: OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1 (CONTINUED)**

- bit 3 TRIGMODE: Trigger Status Mode Select bit

- 1 = TRIGSTAT (OCxCON2<6>) is cleared when OCxRS = OCxTMR or in software

- 0 = TRIGSTAT is cleared only by software

- bit 2-0 OCM<2:0>: Output Compare x Mode Select bits

- 111 = Center-Aligned PWM mode: Output set high when OCxTMR = OCxR and set low when OCxTMR = OCxRS<sup>(1)</sup>

- 110 = Edge-Aligned PWM mode: Output set high when OCxTMR = 0 and set low when OCxTMR = OCxR<sup>(1)</sup>

- 101 = Double Compare Continuous Pulse mode: Initializes OCx pin low, toggles OCx state continuously on alternate matches of OCxR and OCxRS

- 100 = Double Compare Single-Shot mode: Initializes OCx pin low, toggles OCx state on matches of OCxR and OCxRS for one cycle

- 011 = Single Compare mode: Compare event with OCxR, continuously toggles OCx pin

- 010 = Single Compare Single-Shot mode: Initializes OCx pin high, compare event with OCxR, forces OCx pin low

- 001 = Single Compare Single-Shot mode: Initializes OCx pin low, compare event with OCxR, forces OCx pin high

- 000 = Output compare channel is disabled

- Note 1: OCxR and OCxRS are double-buffered in PWM mode only.

- 2: Each Output Compare x module (OCx) has one PTG clock source. See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for more information.

- PTGO4 = OC1 PTGO5 = OC2

- PTGO6 = OC3 PTGO7 = OC4

#### REGISTER 16-1: PTCON: PWMx TIME BASE CONTROL REGISTER (CONTINUED)

| bit 6-4 | SYNCSRC<2:0>: Synchronous Source Selection bits <sup>(1)</sup><br>111 = Reserved<br>100 = Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3-0 | 100 = Reserved<br>011 = PTGO17 <sup>(2)</sup><br>010 = PTGO16 <sup>(2)</sup><br>001 = Reserved<br>000 = SYNCI1 input from PPS<br>SEVTPS<3:0>: PWMx Special Event Trigger Output Postscaler Select bits <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|         | <ul> <li>1111 = 1:16 Postscaler generates Special Event Trigger on every sixteenth compare match event</li> <li>.</li> <l< td=""></l<></ul> |

|         | 0000 = 1:1 Postscaler generates Special Event Trigger on every second compare match event                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

- **Note 1:** These bits should be changed only when PTEN = 0. In addition, when using the SYNCI1 feature, the user application must program the period register with a value that is slightly larger than the expected period of the external synchronization input signal.

- 2: See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for information on this selection.

| R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1  | R/W-1  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| FLTEN15 | FLTEN14 | FLTEN13 | FLTEN12 | FLTEN11 | FLTEN10 | FLTEN9 | FLTEN8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

|         |         |         |         |         |         |        |        |

| R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1  | R/W-1  |

| FLTEN7  | FLTEN6  | FLTEN5  | FLTEN4  | FLTEN3  | FLTEN2  | FLTEN1 | FLTEN0 |

| bit 7   |         |         |         |         |         |        | bit 0  |

|         |         |         |         |         |         |        |        |

| Legend: |         |         |         |         |         |        |        |

#### REGISTER 21-11: CxFEN1: ECANx ACCEPTANCE FILTER ENABLE REGISTER 1

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-0

FLTEN<15:0>: Enable Filter n to Accept Messages bits

1 = Enables Filter n

0 = Disables Filter n

### REGISTER 21-12: CxBUFPNT1: ECANx FILTER 0-3 BUFFER POINTER REGISTER 1

| R/W-0         | R/W-0             | R/W-0                                                          | R/W-0            | R/W-0                                   | R/W-0           | R/W-0    | R/W-0 |

|---------------|-------------------|----------------------------------------------------------------|------------------|-----------------------------------------|-----------------|----------|-------|

|               | F3BF              | ><3:0>                                                         |                  |                                         | F2BF            | P<3:0>   |       |

| bit 15        |                   |                                                                |                  |                                         |                 |          | bit 8 |

| R/W-0         | R/W-0             | R/W-0                                                          | R/W-0            | R/W-0                                   | R/W-0           | R/W-0    | R/W-0 |

|               | F1BF              | ><3:0>                                                         |                  |                                         | F0BF            | P<3:0>   |       |

| bit 7         |                   |                                                                |                  |                                         |                 |          | bit C |

| Legend:       |                   |                                                                |                  |                                         |                 |          |       |

| R = Readabl   | e bit             | W = Writable                                                   | bit              | U = Unimplen                            | nented bit, rea | d as '0' |       |

| -n = Value at | POR               | '1' = Bit is set                                               |                  | '0' = Bit is cleared x = Bit is unknown |                 |          |       |

| bit 15-12     | F3BP<3:0>         | : RX Buffer Mas                                                | k for Filter 3 b | oits                                    |                 |          |       |

|               | 1110 = Filte<br>• | r hits received in<br>r hits received in<br>r hits received in | n RX Buffer 14   |                                         |                 |          |       |

|               | 0001              | er hits received in<br>er hits received in                     |                  |                                         |                 |          |       |

| bit 11-8      | F2BP<3:0>         | RX Buffer Mas                                                  | k for Filter 2 b | oits (same value                        | s as bits<15:1  | 2>)      |       |

| bit 7-4       | F1BP<3:0>         | RX Buffer Mas                                                  | k for Filter 1 b | oits (same value                        | s as bits<15:12 | 2>)      |       |

|               |                   |                                                                |                  |                                         |                 |          |       |

### dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-0         | R/W-0                        | R/W-0                                                                                                                      | R/W-0                                          | R/W-0                              | R/W-0          | R/W-0           | R/W-0  |  |

|---------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|------------------------------------|----------------|-----------------|--------|--|

|               | F15B                         | P<3:0>                                                                                                                     |                                                |                                    | F14BI          | P<3:0>          |        |  |

| bit 15        |                              |                                                                                                                            |                                                |                                    |                |                 | bit 8  |  |

| R/W-0         | R/W-0                        | R/W-0                                                                                                                      | R/W-0                                          | R/W-0                              | R/W-0          | R/W-0           | R/W-0  |  |

| F13BP<3:0>    |                              |                                                                                                                            |                                                |                                    |                | P<3:0>          | 1010 0 |  |

| bit 7         |                              |                                                                                                                            |                                                |                                    |                |                 | bit 0  |  |

| Legend:       |                              |                                                                                                                            |                                                |                                    |                |                 |        |  |

| R = Readabl   | e bit                        | W = Writable                                                                                                               | bit                                            | U = Unimplemented bit, read as '0' |                |                 |        |  |

| -n = Value at | t POR                        | '1' = Bit is set                                                                                                           | :                                              | '0' = Bit is clea                  | ared           | x = Bit is unkr | nown   |  |

| bit 15-12     | 1111 = Filte<br>1110 = Filte | RX Buffer Ma<br>r hits received in<br>r hits received in<br>r hits received in<br>r hits received in<br>r hits received in | n RX FIFO bu<br>n RX Buffer 1<br>n RX Buffer 1 | ıffer<br>4                         |                |                 |        |  |

| bit 11-8      | F14BP<3:0;                   | RX Buffer Ma                                                                                                               | sk for Filter 1                                | 4 bits (same val                   | ues as bits<15 | :12>)           |        |  |

| bit 7-4       | F13BP<3:0;                   | RX Buffer Ma                                                                                                               | sk for Filter 1                                | 3 bits (same val                   | ues as bits<15 | :12>)           |        |  |

| bit 3-0       | F12BP<3:0:                   | RX Buffer Ma                                                                                                               | sk for Filter 1                                | 2 bits (same val                   | ues as bits<15 | :12>)           |        |  |

#### REGISTER 21-15: CxBUFPNT4: ECANx FILTER 12-15 BUFFER POINTER REGISTER 4

### 23.4 ADC Control Registers

#### REGISTER 23-1: AD1CON1: ADC1 CONTROL REGISTER 1

| R/W-0         | U-0                        | R/W-0                               | R/W-0               | U-0               | R/W-0            | R/W-0                               | R/W-0               |

|---------------|----------------------------|-------------------------------------|---------------------|-------------------|------------------|-------------------------------------|---------------------|

| ADON          | —                          | ADSIDL                              | ADDMABM             |                   | AD12B            | FORM1                               | FORM0               |

| bit 15        | •                          |                                     |                     |                   |                  |                                     | bit 8               |

| R/W-0         | R/W-0                      | R/W-0                               | R/W-0               | R/W-0             | R/W-0            | R/W-0, HC, HS                       | R/C-0. HC. HS       |

| SSRC2         | SSRC1                      | SSRC0                               | SSRCG               | SIMSAM            | ASAM             | SAMP                                | DONE <sup>(3)</sup> |

| bit 7         |                            |                                     |                     |                   |                  |                                     | bit (               |

| Legend:       |                            | HC - Hardwar                        | e Clearable bit     | HS - Hardwa       | re Settable bit  | C = Clearable bi                    | +                   |

| R = Readable  | a hit                      | W = Writable b                      |                     |                   | nented bit, read |                                     | L                   |

| -n = Value at |                            | '1' = Bit is set                    | nt -                | '0' = Bit is clea |                  | x = Bit is unknov                   | vp.                 |

|               | FUR                        | I - DILIS SEL                       |                     |                   | aieu             |                                     |                     |

| bit 15        | ADON: ADO                  | C1 Operating M                      | ode bit             |                   |                  |                                     |                     |

|               | 1 = ADC mo<br>0 = ADC is 0 | odule is operatir<br>off            | ng                  |                   |                  |                                     |                     |

| bit 14        | Unimpleme                  | nted: Read as                       | <b>'</b> 0 <b>'</b> |                   |                  |                                     |                     |

| bit 13        | ADSIDL: A                  | DC1 Stop in Idle                    | e Mode bit          |                   |                  |                                     |                     |

|               | 1 = Disconti               | nues module oj                      | peration when o     | device enters     | ldle mode        |                                     |                     |

|               | 0 = Continu                | es module oper                      | ation in Idle mo    | ode               |                  |                                     |                     |

| bit 12        |                            | : DMA Buffer B                      |                     |                   |                  |                                     |                     |

|               |                            |                                     |                     |                   |                  | rovides an addre                    | ess to the DM       |

|               |                            |                                     |                     |                   |                  | nd-alone buffer<br>des a Scatter/Ga | ther address t      |

|               |                            |                                     |                     |                   |                  | size of the DMA b                   |                     |

| bit 11        |                            | nted: Read as                       |                     |                   |                  |                                     |                     |

| bit 10        | AD12B: AD                  | C1 10-Bit or 12                     | -Bit Operation I    | Mode bit          |                  |                                     |                     |

|               |                            | -channel ADC                        | -                   |                   |                  |                                     |                     |

|               | 0 = 10-bit, 4              | -channel ADC                        | operation           |                   |                  |                                     |                     |

| bit 9-8       | FORM<1:0>                  | Data Output I                       | Format bits         |                   |                  |                                     |                     |

|               | For 10-Bit C               |                                     |                     |                   |                  |                                     |                     |

|               |                            | l fractional (Dou<br>nal (Dou⊤ = dd |                     |                   | 0, where s = .I  | NOT.d<9>)                           |                     |

|               |                            | l integer (DOUT                     |                     |                   | where $s = .NC$  | (<9>)                               |                     |

|               |                            | r (Dout = 0000                      |                     |                   |                  |                                     |                     |

|               | For 12-Bit C               | peration:                           |                     |                   |                  |                                     |                     |

|               | •                          | fractional (Dou                     |                     |                   | 0, where s = .I  | NOT.d<11>)                          |                     |

|               |                            |                                     |                     |                   |                  |                                     |                     |

|               |                            | nal (Dout = dd<br>I integer (Dout   |                     |                   |                  | (<11>)                              |                     |

- 2: This setting is available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

- 3: Do not clear the DONE bit in software if Auto-Sample is enabled (ASAM = 1).

#### REGISTER 25-1: CMSTAT: OP AMP/COMPARATOR STATUS REGISTER (CONTINUED)

- C2OUT: Comparator 2 Output Status bit<sup>(2)</sup> bit 1 When CPOL = 0: 1 = VIN + > VIN -0 = VIN + < VIN-When CPOL = 1: 1 = VIN + < VIN-0 = VIN + > VIN -C10UT: Comparator 1 Output Status bit<sup>(2)</sup> bit 0 When CPOL = 0: 1 = VIN + > VIN-0 = VIN + < VIN-When CPOL = 1: 1 = VIN + < VIN-0 = VIN + > VIN -

- **Note 1:** Reflects the value of the of the CEVT bit in the respective Op Amp/Comparator Control register, CMxCON<9>.

- 2: Reflects the value of the COUT bit in the respective Op Amp/Comparator Control register, CMxCON<8>.

#### 27.6 JTAG Interface

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices implement a JTAG interface, which supports boundary scan device testing. Detailed information on this interface is provided in future revisions of the document.

| Note: | Refer to "Programming and Diagnostics"       |

|-------|----------------------------------------------|

|       | (DS70608) in the "dsPIC33/PIC24 Family       |

|       | Reference Manual" for further information    |

|       | on usage, configuration and operation of the |

|       | JTAG interface.                              |

#### 27.7 In-Circuit Serial Programming

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices can be serially programmed while in the end application circuit. This is done with two lines for clock and data, and three other lines for power, ground and the programming sequence. Serial programming allows customers to manufacture boards with unprogrammed devices and then program the device just before shipping the product. Serial programming also allows the most recent firmware or a custom firmware to be programmed. Refer to the "dsPIC33E/PIC24E Flash Programming Specification for Devices with Volatile Configuration Bits" (DS70663) for details about In-Circuit Serial Programming (ICSP).

Any of the three pairs of programming clock/data pins can be used:

- PGEC1 and PGED1

- PGEC2 and PGED2

- PGEC3 and PGED3

#### 27.8 In-Circuit Debugger

When MPLAB<sup>®</sup> ICD 3 or REAL ICE<sup>™</sup> is selected as a debugger, the in-circuit debugging functionality is enabled. This function allows simple debugging functions when used with MPLAB IDE. Debugging functionality is controlled through the PGECx (Emulation/Debug Clock) and PGEDx (Emulation/Debug Data) pin functions.

Any of the three pairs of debugging clock/data pins can be used:

- PGEC1 and PGED1

- PGEC2 and PGED2

- PGEC3 and PGED3

To use the in-circuit debugger function of the device, the design must implement ICSP connections to  $\overline{MCLR}$ , VDD, Vss and the PGECx/PGEDx pin pair. In addition, when the feature is enabled, some of the resources are not available for general use. These resources include the first 80 bytes of data RAM and two I/O pins (PGECx and PGEDx).

#### 27.9 Code Protection and CodeGuard™ Security

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X, and PIC24EPXXXGP/MC20X devices offer basic implementation of CodeGuard Security that supports only General Segment (GS) security. This feature helps protect individual Intellectual Property.

Note: Refer to "CodeGuard<sup>™</sup> Security" (DS70634) in the "dsPIC33/PIC24 Family Reference Manual" for further information on usage, configuration and operation of CodeGuard Security.

# TABLE 30-46:SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0)TIMING REQUIREMENTS

| АС СНА | ARACTERIST            | <b>FICS</b>                                     | Standard Op<br>(unless othe<br>Operating ter | rwise st            | <b>ated)</b><br>e -40°C | ≤ Ta ≤ +8 | <b>o 3.6V</b><br>85°C for Industrial<br>125°C for Extended |

|--------|-----------------------|-------------------------------------------------|----------------------------------------------|---------------------|-------------------------|-----------|------------------------------------------------------------|

| Param. | Symbol                | Characteristic <sup>(1)</sup>                   | Min.                                         | Тур. <sup>(2)</sup> | Max.                    | Units     | Conditions                                                 |

| SP70   | FscP                  | Maximum SCK1 Input<br>Frequency                 | _                                            |                     | Lesser of<br>FP or 11   | MHz       | (Note 3)                                                   |

| SP72   | TscF                  | SCK1 Input Fall Time                            | _                                            |                     |                         | ns        | See Parameter DO32<br>(Note 4)                             |

| SP73   | TscR                  | SCK1 Input Rise Time                            | —                                            |                     |                         | ns        | See Parameter DO31 (Note 4)                                |

| SP30   | TdoF                  | SDO1 Data Output Fall Time                      | —                                            | _                   |                         | ns        | See Parameter DO32<br>(Note 4)                             |

| SP31   | TdoR                  | SDO1 Data Output Rise Time                      |                                              |                     |                         | ns        | See Parameter DO31<br>(Note 4)                             |

| SP35   | TscH2doV,<br>TscL2doV | SDO1 Data Output Valid after<br>SCK1 Edge       | —                                            | 6                   | 20                      | ns        |                                                            |

| SP36   | TdoV2scH,<br>TdoV2scL | SDO1 Data Output Setup to<br>First SCK1 Edge    | 30                                           | _                   | _                       | ns        |                                                            |

| SP40   | TdiV2scH,<br>TdiV2scL | Setup Time of SDI1 Data Input to SCK1 Edge      | 30                                           |                     | —                       | ns        |                                                            |

| SP41   | TscH2diL,<br>TscL2diL | Hold Time of SDI1 Data Input to SCK1 Edge       | 30                                           | _                   | _                       | ns        |                                                            |

| SP50   | TssL2scH,<br>TssL2scL | $\overline{SS1}$ ↓ to SCK1 ↑ or SCK1 ↓<br>Input | 120                                          | _                   | _                       | ns        |                                                            |

| SP51   | TssH2doZ              | SS1 ↑ to SDO1 Output<br>High-Impedance          | 10                                           | _                   | 50                      | ns        | (Note 4)                                                   |

| SP52   | TscH2ssH,<br>TscL2ssH | SS1 ↑ after SCK1 Edge                           | 1.5 Tcy + 40                                 | _                   | _                       | ns        | (Note 4)                                                   |

| SP60   | TssL2doV              | SDO1 Data Output Valid after<br>SS1 Edge        | —                                            | _                   | 50                      | ns        |                                                            |

Note 1: These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCK1 is 91 ns. Therefore, the SCK1 clock generated by the master must not violate this specification.

4: Assumes 50 pF load on all SPI1 pins.

| AC CHA       | ARACTER | RISTICS                                                                                             | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) <sup>(1)</sup> |           |       |       |                                                        |  |