Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 512KB (170K x 24)                                                               |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | ·                                                                               |

| RAM Size                   | 24K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-VFQFN Exposed Pad                                                            |

| Supplier Device Package    | 64-VQFN (9x9)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep512gp206t-i-mr |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

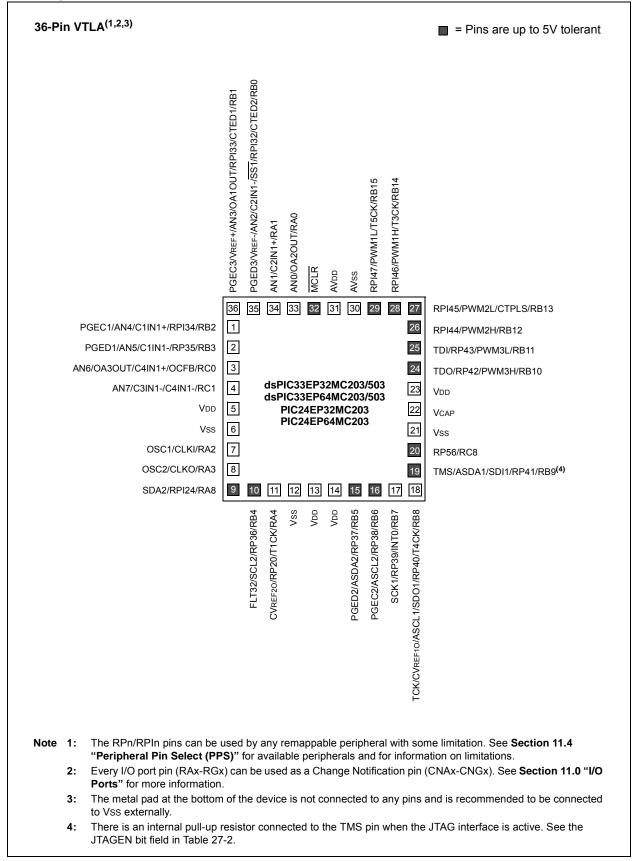

# Pin Diagrams (Continued)

| Pin Name <sup>(4)</sup>       | Pin<br>Type | Buffer<br>Type | PPS     | Description                                                                   |  |  |

|-------------------------------|-------------|----------------|---------|-------------------------------------------------------------------------------|--|--|

| C1IN1-                        | I           | Analog         | No      | Op Amp/Comparator 1 Negative Input 1.                                         |  |  |

| C1IN2-                        | I           | Analog         | No      | Comparator 1 Negative Input 2.                                                |  |  |

| C1IN1+                        | I           | Analog         | No      | Op Amp/Comparator 1 Positive Input 1.                                         |  |  |

| OA1OUT                        | 0           | Analog         | No      | Op Amp 1 output.                                                              |  |  |

| C1OUT                         | 0           | —              | Yes     | Comparator 1 output.                                                          |  |  |

| C2IN1-                        | I           | Analog         | No      | Op Amp/Comparator 2 Negative Input 1.                                         |  |  |

| C2IN2-                        | I           | Analog         | No      | Comparator 2 Negative Input 2.                                                |  |  |

| C2IN1+                        | I           | Analog         | No      | Op Amp/Comparator 2 Positive Input 1.                                         |  |  |

| OA2OUT                        | 0           | Analog         | No      | Op Amp 2 output.                                                              |  |  |

| C2OUT                         | 0           |                | Yes     | Comparator 2 output.                                                          |  |  |

| C3IN1-                        | I           | Analog         | No      | Op Amp/Comparator 3 Negative Input 1.                                         |  |  |

| C3IN2-                        | I           | Analog         | No      | Comparator 3 Negative Input 2.                                                |  |  |

| C3IN1+                        | I           | Analog         | No      | Op Amp/Comparator 3 Positive Input 1.                                         |  |  |

| OA3OUT                        | 0           | Analog         | No      | Op Amp 3 output.                                                              |  |  |

| C3OUT                         | 0           |                | Yes     | Comparator 3 output.                                                          |  |  |

| C4IN1-                        | I.          | Analog         | No      | Comparator 4 Negative Input 1.                                                |  |  |

| C4IN1+                        | I.          | Analog         | No      | Comparator 4 Positive Input 1.                                                |  |  |

| C4OUT                         | 0           |                | Yes     | Comparator 4 output.                                                          |  |  |

| CVREF10                       | 0           | Analog         | No      | Op amp/comparator voltage reference output.                                   |  |  |

| CVREF20                       | 0           | Analog         | No      | Op amp/comparator voltage reference divided by 2 output.                      |  |  |

| PGED1                         | I/O         | ST             | No      | Data I/O pin for Programming/Debugging Communication Channel 1.               |  |  |

| PGEC1                         | I           | ST             | No      | Clock input pin for Programming/Debugging Communication Channel 1.            |  |  |

| PGED2                         | I/O         | ST             | No      | Data I/O pin for Programming/Debugging Communication Channel 2.               |  |  |

| PGEC2                         | I           | ST             | No      | Clock input pin for Programming/Debugging Communication Channel 2.            |  |  |

| PGED3                         | I/O         | ST             | No      | Data I/O pin for Programming/Debugging Communication Channel 3.               |  |  |

| PGEC3                         | I           | ST             | No      | Clock input pin for Programming/Debugging Communication Channel 3.            |  |  |

| MCLR                          | I/P         | ST             | No      | Master Clear (Reset) input. This pin is an active-low Reset to the device.    |  |  |

| AVDD                          | Р           | Р              | No      | Positive supply for analog modules. This pin must be connected at all times.  |  |  |

| AVss                          | Р           | Р              | No      | Ground reference for analog modules. This pin must be connected at all times. |  |  |

| Vdd                           | Р           |                | No      | Positive supply for peripheral logic and I/O pins.                            |  |  |

| VCAP                          | Р           |                | No      | CPU logic filter capacitor connection.                                        |  |  |

| Vss                           | Р           |                | No      | Ground reference for logic and I/O pins.                                      |  |  |

| VREF+                         | 1           | Analog         | No      | Analog voltage reference (high) input.                                        |  |  |

| VREF-                         | Ι           | Analog         | No      | Analog voltage reference (low) input.                                         |  |  |

| Legend: CMOS = C<br>ST = Schn | nitt Trigg  | jer input v    | with CI | or output Analog = Analog input P = Power   MOS levels O = Output I = Input   |  |  |

Note 1: This pin is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This pin is available on dsPIC33EPXXXGP/MC50X devices only.

PPS = Peripheral Pin Select

3: This is the default Fault on Reset for dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices. See Section 16.0 "High-Speed PWM Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)" for more information.

TTL = TTL input buffer

4: Not all pins are available in all packages variants. See the "Pin Diagrams" section for pin availability.

**5:** There is an internal pull-up resistor connected to the TMS pin when the JTAG interface is active. See the JTAGEN bit field in Table 27-2.

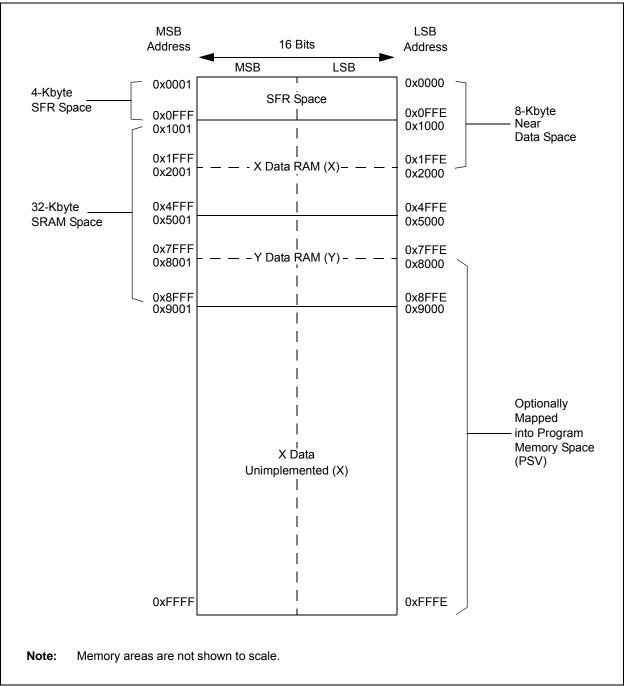

# FIGURE 4-10: DATA MEMORY MAP FOR dsPIC33EP256MC20X/50X AND dsPIC33EP256GP50X DEVICES

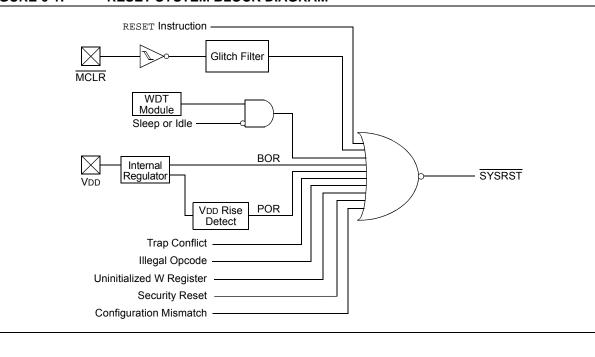

# 6.0 RESETS

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Reset" (DS70602) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- · POR: Power-on Reset

- · BOR: Brown-out Reset

- MCLR: Master Clear Pin Reset

- SWR: RESET Instruction

- WDTO: Watchdog Timer Time-out Reset

- CM: Configuration Mismatch Reset

- TRAPR: Trap Conflict Reset

- IOPUWR: Illegal Condition Device Reset

- Illegal Opcode Reset

- Uninitialized W Register Reset

- Security Reset

FIGURE 6-1: RESET SYSTEM BLOCK DIAGRAM

A simplified block diagram of the Reset module is shown in Figure 6-1.

Any active source of Reset will make the SYSRST signal active. On system Reset, some of the registers associated with the CPU and peripherals are forced to a known Reset state and some are unaffected.

Note: Refer to the specific peripheral section or Section 4.0 "Memory Organization" of this manual for register Reset states.

All types of device Reset set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 6-1).

A POR clears all the bits, except for the POR and BOR bits (RCON<1:0>), that are set. The user application can set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software does not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer and device power-saving states. The function of these bits is discussed in other sections of this manual.

**Note:** The status bits in the RCON register should be cleared after they are read so that the next RCON register value after a device Reset is meaningful.

For all Resets, the default clock source is determined by the FNOSC<2:0> bits in the FOSCSEL Configuration register. The value of the FNOSC<2:0> bits is loaded into NOSC<2:0> (OSCCON<10:8>) on Reset, which in turn, initializes the system clock.

# 7.3 Interrupt Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

#### 7.3.1 KEY RESOURCES

- "Interrupts" (DS70600) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

# 7.4 Interrupt Control and Status Registers

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices implement the following registers for the interrupt controller:

- INTCON1

- INTCON2

- INTCON3

- INTCON4

- INTTREG

# 7.4.1 INTCON1 THROUGH INTCON4

Global interrupt control functions are controlled from INTCON1, INTCON2, INTCON3 and INTCON4.

INTCON1 contains the Interrupt Nesting Disable bit (NSTDIS), as well as the control and status flags for the processor trap sources.

The INTCON2 register controls external interrupt request signal behavior and also contains the Global Interrupt Enable bit (GIE).

INTCON3 contains the status flags for the DMA and DO stack overflow status trap sources.

The INTCON4 register contains the software generated hard trap status bit (SGHT).

# 7.4.2 IFSx

The IFSx registers maintain all of the interrupt request flags. Each source of interrupt has a status bit, which is set by the respective peripherals or external signal and is cleared via software.

## 7.4.3 IECx

The IECx registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

## 7.4.4 IPCx

The IPCx registers are used to set the Interrupt Priority Level (IPL) for each source of interrupt. Each user interrupt source can be assigned to one of eight priority levels.

## 7.4.5 INTTREG

The INTTREG register contains the associated interrupt vector number and the new CPU Interrupt Priority Level, which are latched into the Vector Number bits (VECNUM<7:0>) and Interrupt Priority Level bits (ILR<3:0>) fields in the INTTREG register. The new Interrupt Priority Level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the same sequence as they are listed in Table 7-1. For example, the INT0 (External Interrupt 0) is shown as having Vector Number 8 and a natural order priority of 0. Thus, the INT0IF bit is found in IFS0<0>, the INT0IE bit in IEC0<0> and the INT0IP bits in the first position of IPC0 (IPC0<2:0>).

# 7.4.6 STATUS/CONTROL REGISTERS

Although these registers are not specifically part of the interrupt control hardware, two of the CPU Control registers contain bits that control interrupt functionality. For more information on these registers refer to "**CPU**" (DS70359) in the "*dsPIC33/PIC24 Family Reference Manual*".

- The CPU STATUS Register, SR, contains the IPL<2:0> bits (SR<7:5>). These bits indicate the current CPU Interrupt Priority Level. The user software can change the current CPU Interrupt Priority Level by writing to the IPLx bits.

- The CORCON register contains the IPL3 bit which, together with IPL<2:0>, also indicates the current CPU priority level. IPL3 is a read-only bit so that trap events cannot be masked by the user software.

All Interrupt registers are described in Register 7-3 through Register 7-7 in the following pages.

| R/W-0                | R/W-0                   | R/W-0                | R/W-0 | R/C-0 | R/C-0 | R-0   | R/W-0 |

|----------------------|-------------------------|----------------------|-------|-------|-------|-------|-------|

| OA                   | OB                      | SA                   | SB    | OAB   | SAB   | DA    | DC    |

| bit 15               |                         |                      |       |       |       |       | bit 8 |

|                      |                         |                      |       |       |       |       |       |

| R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup>    | R/W-0 <sup>(3)</sup> | R-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|                      | IPL<2:0> <sup>(2)</sup> |                      | RA    | Ν     | OV    | Z     | С     |

| bit 7                |                         |                      |       |       |       |       | bit 0 |

|                      |                         |                      |       |       |       |       |       |

# REGISTER 7-1: SR: CPU STATUS REGISTER<sup>(1)</sup>

| Legend:           | C = Clearable bit |                       |                    |

|-------------------|-------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1'= Bit is set   | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7-5 | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2,3)</sup>        |

|---------|----------------------------------------------------------------------------|

|         | 111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled |

|         | 110 = CPU Interrupt Priority Level is 6 (14)                               |

|         | 101 = CPU Interrupt Priority Level is 5 (13)                               |

|         | 100 = CPU Interrupt Priority Level is 4 (12)                               |

|         | 011 = CPU Interrupt Priority Level is 3 (11)                               |

|         | 010 = CPU Interrupt Priority Level is 2 (10)                               |

|         | 001 = CPU Interrupt Priority Level is 1 (9)                                |

|         | 000 = CPU Interrupt Priority Level is 0 (8)                                |

- **Note 1:** For complete register details, see Register 3-1.

- 2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL, if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- **3:** The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

# REGISTER 9-2: CLKDIV: CLOCK DIVISOR REGISTER (CONTINUED)

- **Note 1:** The DOZE<2:0> bits can only be written to when the DOZEN bit is clear. If DOZEN = 1, any writes to DOZE<2:0> are ignored.

- $\label{eq:constraint} \textbf{2:} \quad \text{This bit is cleared when the ROI bit is set and an interrupt occurs.}$

- **3:** The DOZEN bit cannot be set if DOZE<2:0> = 000. If DOZE<2:0> = 000, any attempt by user software to set the DOZEN bit is ignored.

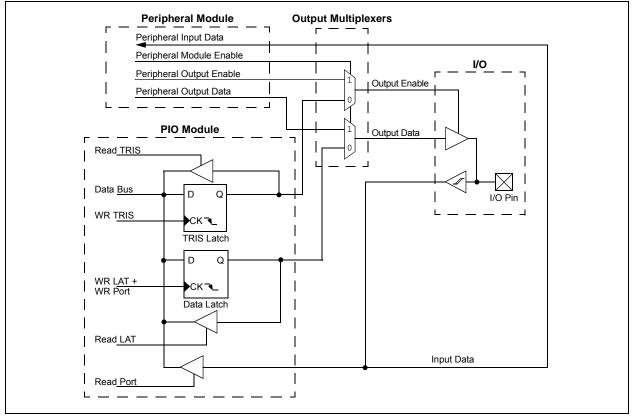

# 11.0 I/O PORTS

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "I/O Ports" (DS70598) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

Many of the device pins are shared among the peripherals and the parallel I/O ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

# 11.1 Parallel I/O (PIO) Ports

Generally, a parallel I/O port that shares a pin with a peripheral is subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pin. The logic also prevents "loop through," in which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 11-1 illustrates how ports are shared with other peripherals and the associated I/O pin to which they are connected.

When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin can be read, but the output driver for the parallel port bit is disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin can be driven by a port.

All port pins have eight registers directly associated with their operation as digital I/O. The Data Direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the Latch register (LATx) read the latch. Writes to the Latch write the latch. Reads from the port (PORTx) read the port pins, while writes to the port pins write the latch.

Any bit and its associated data and control registers that are not valid for a particular device is disabled. This means the corresponding LATx and TRISx registers and the port pin are read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0    | U-0 | R/W-0      | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|--------|-----|------------|------------|-------|-------|-------|-------|--|

| —      | —   |            | RP43R<5:0> |       |       |       |       |  |

| bit 15 |     |            |            |       |       |       | bit 8 |  |

|        |     |            |            |       |       |       |       |  |

| U-0    | U-0 | R/W-0      | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

| —      | —   | RP42R<5:0> |            |       |       |       |       |  |

## REGISTER 11-22: RPOR4: PERIPHERAL PIN SELECT OUTPUT REGISTER 4

|   | bit | 7 |

|---|-----|---|

| 1 |     |   |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP43R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP43 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP42R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP42 Output Pin bits (see Table 11-3 for peripheral function numbers) |

#### REGISTER 11-23: RPOR5: PERIPHERAL PIN SELECT OUTPUT REGISTER 5

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| —      | —   |       |       | RP55  | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|-------|-----|-------|------------|-------|-------|-------|-------|--|--|--|

| —     | —   |       | RP54R<5:0> |       |       |       |       |  |  |  |

| bit 7 |     |       |            |       |       |       |       |  |  |  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP55R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP55 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP54R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP54 Output Pin bits (see Table 11-3 for peripheral function numbers) |

bit 0

# 12.0 TIMER1

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Timer1 module is a 16-bit timer that can operate as a free-running interval timer/counter.

The Timer1 module has the following unique features over other timers:

- Can be operated in Asynchronous Counter mode from an external clock source

- The external clock input (T1CK) can optionally be synchronized to the internal device clock and the clock synchronization is performed after the prescaler

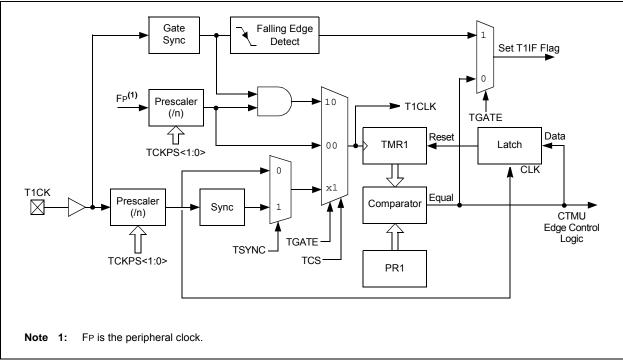

- A block diagram of Timer1 is shown in Figure 12-1.

The Timer1 module can operate in one of the following modes:

- Timer mode

- · Gated Timer mode

- Synchronous Counter mode

- · Asynchronous Counter mode

In Timer and Gated Timer modes, the input clock is derived from the internal instruction cycle clock (FCY). In Synchronous and Asynchronous Counter modes, the input clock is derived from the external clock input at the T1CK pin.

The Timer modes are determined by the following bits:

- Timer Clock Source Control bit (TCS): T1CON<1>

- Timer Synchronization Control bit (TSYNC): T1CON<2>

- Timer Gate Control bit (TGATE): T1CON<6>

Timer control bit setting for different operating modes are given in the Table 12-1.

| Mode                    | TCS | TGATE | TSYNC |  |  |  |  |

|-------------------------|-----|-------|-------|--|--|--|--|

| Timer                   | 0   | 0     | х     |  |  |  |  |

| Gated Timer             | 0   | 1     | x     |  |  |  |  |

| Synchronous<br>Counter  | 1   | х     | 1     |  |  |  |  |

| Asynchronous<br>Counter | 1   | x     | 0     |  |  |  |  |

#### TABLE 12-1: TIMER MODE SETTINGS

# FIGURE 12-1: 16-BIT TIMER1 MODULE BLOCK DIAGRAM

# 12.2 Timer1 Control Register

| R/W-0              | U-0                                                 | R/W-0                                         | U-0                       | U-0              | U-0                      | U-0                | U-0                |  |  |  |  |  |

|--------------------|-----------------------------------------------------|-----------------------------------------------|---------------------------|------------------|--------------------------|--------------------|--------------------|--|--|--|--|--|

| TON <sup>(1)</sup> | —                                                   | TSIDL                                         | —                         | _                | —                        | _                  | _                  |  |  |  |  |  |

| bit 15             |                                                     |                                               |                           |                  |                          |                    | bit 8              |  |  |  |  |  |

|                    |                                                     |                                               |                           |                  |                          |                    |                    |  |  |  |  |  |

| U-0                | R/W-0                                               | R/W-0                                         | R/W-0                     | U-0              | R/W-0                    | R/W-0              | U-0                |  |  |  |  |  |

|                    | TGATE                                               | TCKPS1                                        | TCKPS0                    | _                | TSYNC <sup>(1)</sup>     | TCS <sup>(1)</sup> |                    |  |  |  |  |  |

| bit 7              |                                                     |                                               |                           |                  |                          |                    | bit (              |  |  |  |  |  |

| Legend:            |                                                     |                                               |                           |                  |                          |                    |                    |  |  |  |  |  |

| R = Readable       | e bit                                               | W = Writable                                  | bit                       | U = Unimplei     | mented bit, read         | l as '0'           |                    |  |  |  |  |  |

| -n = Value at      | POR                                                 | '1' = Bit is set                              |                           | '0' = Bit is cle | ared                     | x = Bit is unkno   | own                |  |  |  |  |  |

|                    |                                                     | o                                             |                           |                  |                          |                    |                    |  |  |  |  |  |

| bit 15             | <b>TON:</b> Timer1<br>1 = Starts 16-                |                                               |                           |                  |                          |                    |                    |  |  |  |  |  |

|                    | 0 = Stops 16-                                       |                                               |                           |                  |                          |                    |                    |  |  |  |  |  |

| bit 14             | Unimplemen                                          | ted: Read as '                                | 0'                        |                  |                          |                    |                    |  |  |  |  |  |

| bit 13             | TSIDL: Timer                                        | 1 Stop in Idle N                              | /lode bit                 |                  |                          |                    |                    |  |  |  |  |  |

|                    |                                                     | ues module op                                 |                           |                  | ldle mode                |                    |                    |  |  |  |  |  |

|                    |                                                     | s module opera                                |                           | ode              |                          |                    |                    |  |  |  |  |  |

| bit 12-7           | -                                                   | ted: Read as '                                |                           |                  |                          |                    |                    |  |  |  |  |  |

| bit 6              |                                                     | r1 Gated Time                                 | Accumulation              | h Enable bit     |                          |                    |                    |  |  |  |  |  |

|                    | <u>When TCS = 1:</u><br>This bit is ignored.        |                                               |                           |                  |                          |                    |                    |  |  |  |  |  |

|                    | When TCS = $0$ :                                    |                                               |                           |                  |                          |                    |                    |  |  |  |  |  |

|                    |                                                     | e accumulatio                                 |                           |                  |                          |                    |                    |  |  |  |  |  |

|                    |                                                     | e accumulatio                                 |                           | 0.1.1.1.1.1      |                          |                    |                    |  |  |  |  |  |

| bit 5-4            | TCKPS<1:0>: Timer1 Input Clock Prescale Select bits |                                               |                           |                  |                          |                    |                    |  |  |  |  |  |

|                    | 11 = 1:256<br>10 = 1:64                             |                                               |                           |                  |                          |                    |                    |  |  |  |  |  |

|                    | 01 = 1.8                                            |                                               |                           |                  |                          |                    |                    |  |  |  |  |  |

|                    | 00 = 1:1                                            |                                               |                           |                  |                          |                    |                    |  |  |  |  |  |

| bit 3              | -                                                   | ted: Read as '                                |                           |                  |                          |                    |                    |  |  |  |  |  |

| bit 2              |                                                     | er1 External Clo                              | ock Input Synd            | chronization S   | elect bit <sup>(1)</sup> |                    |                    |  |  |  |  |  |

|                    |                                                     | When TCS = 1:                                 |                           |                  |                          |                    |                    |  |  |  |  |  |

|                    |                                                     | izes external c<br>synchronize ex             |                           | nut              |                          |                    |                    |  |  |  |  |  |

|                    | When TCS =                                          | 0 = Does not synchronize external clock input |                           |                  |                          |                    |                    |  |  |  |  |  |

|                    | This bit is igno                                    |                                               |                           |                  |                          |                    |                    |  |  |  |  |  |

| bit 1              | TCS: Timer1                                         | Clock Source S                                | Select bit <sup>(1)</sup> |                  |                          |                    |                    |  |  |  |  |  |

|                    | 1 = External c<br>0 = Internal cl                   | clock is from pi<br>ock (FP)                  | n, T1CK (on th            | ne rising edge)  | •                        |                    |                    |  |  |  |  |  |

| bit 0              | Unimplemen                                          | ted: Read as '                                | 0'                        |                  |                          |                    |                    |  |  |  |  |  |

|                    | nen Timer1 is er<br>empts by user s                 |                                               |                           |                  |                          | SYNC = 1, TON      | <b>\ =</b> 1), any |  |  |  |  |  |

# REGISTER 12-1: T1CON: TIMER1 CONTROL REGISTER

© 2011-2013 Microchip Technology Inc.

# 21.2 Modes of Operation

The ECAN module can operate in one of several operation modes selected by the user. These modes include:

- · Initialization mode

- Disable mode

- Normal Operation mode

- · Listen Only mode

- Listen All Messages mode

- Loopback mode

Modes are requested by setting the REQOP<2:0> bits (CxCTRL1<10:8>). Entry into a mode is Acknowledged by monitoring the OPMODE<2:0> bits (CxCTRL1<7:5>). The module does not change the mode and the OPMODEx bits until a change in mode is acceptable, generally during bus Idle time, which is defined as at least 11 consecutive recessive bits.

## 21.3 ECAN Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 21.3.1 KEY RESOURCES

- "Enhanced Controller Area Network (ECAN™)" (DS70353) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- · Development Tools

## REGISTER 23-6: AD1CHS0: ADC1 INPUT CHANNEL 0 SELECT REGISTER (CONTINUED)

| bit 4-0 | CH0SA<4:0>: Channel 0 Positive Input Select for Sample MUXA bits <sup>(1)</sup>                     |

|---------|-----------------------------------------------------------------------------------------------------|

|         | 11111 = Open; use this selection with CTMU capacitive and time measurement                          |

|         | 11110 = Channel 0 positive input is connected to the CTMU temperature measurement diode (CTMU TEMP) |

|         | 11101 = Reserved                                                                                    |

|         | 11100 = Reserved                                                                                    |

|         | 11011 = Reserved<br>11010 = Channel 0 positive input is the output of OA3/AN6 <sup>(2,3)</sup>      |

|         | 11010 =  Channel 0 positive input is the output of OA3/AN0 <sup>(2)</sup>                           |

|         | 11000 = Channel 0 positive input is the output of OA1/AN3 <sup>(2)</sup>                            |

|         | 10110 = Reserved                                                                                    |

|         | •                                                                                                   |

|         | •                                                                                                   |

|         | •                                                                                                   |

|         | 10000 = Reserved                                                                                    |

|         | 01111 = Channel 0 positive input is AN15 <sup>(1,3)</sup>                                           |

|         | 01110 = Channel 0 positive input is AN14 <sup>(1,3)</sup>                                           |

|         | 01101 = Channel 0 positive input is AN13 <sup>(1,3)</sup>                                           |

|         | •                                                                                                   |

|         | •                                                                                                   |

|         | •                                                                                                   |

|         | 00010 = Channel 0 positive input is $AN2^{(1,3)}$                                                   |

|         | 00001 = Channel 0 positive input is $AN1^{(1,3)}$                                                   |

|         | 00000 = Channel 0 positive input is AN0 <sup>(1,3)</sup>                                            |

|         |                                                                                                     |

- **Note 1:** AN0 through AN7 are repurposed when comparator and op amp functionality is enabled. See Figure 23-1 to determine how enabling a particular op amp or comparator affects selection choices for Channels 1, 2 and 3.

- 2: The OAx input is used if the corresponding op amp is selected (OPMODE (CMxCON<10>) = 1); otherwise, the ANx input is used.

- 3: See the "Pin Diagrams" section for the available analog channels for each device.

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                                   | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |

|------------------------------------|-------|-------|-----------------------------------------|------------------------------------|-------|-------|-------|--|

| CSS15                              | CSS14 | CSS13 | CSS12                                   | CSS11                              | CSS10 | CSS9  | CSS8  |  |

| bit 15                             |       |       |                                         | ·                                  | •     | ·     | bit 8 |  |

|                                    |       |       |                                         |                                    |       |       |       |  |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                                   | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |

| CSS7                               | CSS6  | CSS5  | CSS4                                    | CSS3                               | CSS2  | CSS1  | CSS0  |  |

| bit 7                              | -     |       |                                         |                                    | •     |       | bit ( |  |

|                                    |       |       |                                         |                                    |       |       |       |  |

| Legend:                            |       |       |                                         |                                    |       |       |       |  |

| R = Readable bit W = Writable bit  |       |       | bit                                     | U = Unimplemented bit, read as '0' |       |       |       |  |

| -n = Value at POR '1' = Bit is set |       |       | '0' = Bit is cleared x = Bit is unknown |                                    |       |       |       |  |

# REGISTER 23-8: AD1CSSL: ADC1 INPUT SCAN SELECT REGISTER LOW<sup>(1,2)</sup>

bit 15-0 CSS<15:0>: ADC1 Input Scan Selection bits

1 = Selects ANx for input scan

0 = Skips ANx for input scan

**Note 1:** On devices with less than 16 analog inputs, all AD1CSSL bits can be selected by the user. However, inputs selected for scan, without a corresponding input on the device, convert VREFL.

**2:** CSSx = ANx, where x = 0-15.

| PTG Output<br>Number | PTG Output Description                                  |

|----------------------|---------------------------------------------------------|

| PTGO0                | Trigger/Synchronization Source for OC1                  |

| PTGO1                | Trigger/Synchronization Source for OC2                  |

| PTGO2                | Trigger/Synchronization Source for OC3                  |

| PTGO3                | Trigger/Synchronization Source for OC4                  |

| PTGO4                | Clock Source for OC1                                    |

| PTGO5                | Clock Source for OC2                                    |

| PTGO6                | Clock Source for OC3                                    |

| PTGO7                | Clock Source for OC4                                    |

| PTGO8                | Trigger/Synchronization Source for IC1                  |

| PTGO9                | Trigger/Synchronization Source for IC2                  |

| PTGO10               | Trigger/Synchronization Source for IC3                  |

| PTGO11               | Trigger/Synchronization Source for IC4                  |

| PTGO12               | Sample Trigger for ADC                                  |

| PTGO13               | Sample Trigger for ADC                                  |

| PTGO14               | Sample Trigger for ADC                                  |

| PTGO15               | Sample Trigger for ADC                                  |

| PTGO16               | PWM Time Base Synchronous Source for PWM <sup>(1)</sup> |

| PTGO17               | PWM Time Base Synchronous Source for PWM <sup>(1)</sup> |

| PTGO18               | Mask Input Select for Op Amp/Comparator                 |

| PTGO19               | Mask Input Select for Op Amp/Comparator                 |

| PTGO20               | Reserved                                                |

| PTGO21               | Reserved                                                |

| PTGO22               | Reserved                                                |

| PTGO23               | Reserved                                                |

| PTGO24               | Reserved                                                |

| PTGO25               | Reserved                                                |

| PTGO26               | Reserved                                                |

| PTGO27               | Reserved                                                |

| PTGO28               | Reserved                                                |

| PTGO29               | Reserved                                                |

| PTGO30               | PTG Output to PPS Input Selection                       |

| PTGO31               | PTG Output to PPS Input Selection                       |

# TABLE 24-2: PTG OUTPUT DESCRIPTIONS

Note 1: This feature is only available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

#### TABLE 30-18: PLL CLOCK TIMING SPECIFICATIONS

| AC CHARACTERISTICS |        |                                                                  |      | $\label{eq:standard operating Conditions: 3.0V to 3.6V} \end{tabular} \begin{tabular}{lllllllllllllllllllllllllllllllllll$ |      |       |                    |  |

|--------------------|--------|------------------------------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------|------|-------|--------------------|--|

| Param<br>No.       | Symbol | Characteristic                                                   | Min. | Typ. <sup>(1)</sup>                                                                                                        | Max. | Units | Conditions         |  |

| OS50               | Fplli  | PLL Voltage Controlled Oscillator<br>(VCO) Input Frequency Range | 0.8  | _                                                                                                                          | 8.0  | MHz   | ECPLL, XTPLL modes |  |

| OS51               | Fvco   | On-Chip VCO System Frequency                                     | 120  | —                                                                                                                          | 340  | MHz   |                    |  |

| OS52               | TLOCK  | PLL Start-up Time (Lock Time)                                    | 0.9  | 1.5                                                                                                                        | 3.1  | ms    |                    |  |

| OS53               | DCLK   | CLKO Stability (Jitter) <sup>(2)</sup>                           | -3   | 0.5                                                                                                                        | 3    | %     |                    |  |

**Note 1:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: This jitter specification is based on clock cycle-by-clock cycle measurements. To get the effective jitter for individual time bases, or communication clocks used by the application, use the following formula:

$$Effective Jitter = \frac{DCLK}{\sqrt{\frac{FOSC}{Time Base or Communication Clock}}}$$

For example, if Fosc = 120 MHz and the SPIx bit rate = 10 MHz, the effective jitter is as follows:

Effective Jitter =

$$\frac{DCLK}{\sqrt{\frac{120}{10}}} = \frac{DCLK}{\sqrt{12}} = \frac{DCLK}{3.464}$$

#### TABLE 30-19: INTERNAL FRC ACCURACY

| AC CHA                                                          | RACTERISTICS | $\begin{array}{ll} \mbox{Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |      |       |                                         |                |  |  |

|-----------------------------------------------------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|-----------------------------------------|----------------|--|--|

| Param<br>No. Characteristic                                     |              | Min.                                                                                                                                                                                                                                                                         | Тур. | Max. | Units | Conditio                                | ons            |  |  |

| Internal FRC Accuracy @ FRC Frequency = 7.37 MHz <sup>(1)</sup> |              |                                                                                                                                                                                                                                                                              |      |      |       |                                         |                |  |  |

| F20a                                                            | FRC          | -1.5                                                                                                                                                                                                                                                                         | 0.5  | +1.5 | %     | $-40^{\circ}C \le TA \le -10^{\circ}C$  | VDD = 3.0-3.6V |  |  |

|                                                                 |              |                                                                                                                                                                                                                                                                              | 0.5  | +1   | %     | $-10^{\circ}C \le TA \le +85^{\circ}C$  | VDD = 3.0-3.6V |  |  |

| F20b                                                            | FRC          | -2                                                                                                                                                                                                                                                                           | 1    | +2   | %     | $+85^{\circ}C \le TA \le +125^{\circ}C$ | VDD = 3.0-3.6V |  |  |

Note 1: Frequency is calibrated at +25°C and 3.3V. TUNx bits can be used to compensate for temperature drift.

#### TABLE 30-20: INTERNAL LPRC ACCURACY

| AC CH                       | ARACTERISTICS               | $\begin{array}{ll} \mbox{Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |      |      |       |                                           |                |  |  |

|-----------------------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|-------------------------------------------|----------------|--|--|

| Param<br>No. Characteristic |                             | Min.                                                                                                                                                                                                                                                                     | Тур. | Max. | Units | Conditions                                |                |  |  |

| LPRC (                      | @ 32.768 kHz <sup>(1)</sup> |                                                                                                                                                                                                                                                                          |      |      |       |                                           |                |  |  |

| F21a                        | LPRC                        | -30                                                                                                                                                                                                                                                                      | —    | +30  | %     | $-40^{\circ}C \le TA \le -10^{\circ}C$    | VDD = 3.0-3.6V |  |  |

|                             |                             | -20                                                                                                                                                                                                                                                                      | _    | +20  | %     | $-10^{\circ}C \leq TA \leq +85^{\circ}C$  | VDD = 3.0-3.6V |  |  |

| F21b                        | LPRC                        | -30                                                                                                                                                                                                                                                                      | _    | +30  | %     | $+85^{\circ}C \leq TA \leq +125^{\circ}C$ | VDD = 3.0-3.6V |  |  |

**Note 1:** The change of LPRC frequency as VDD changes.

NOTES:

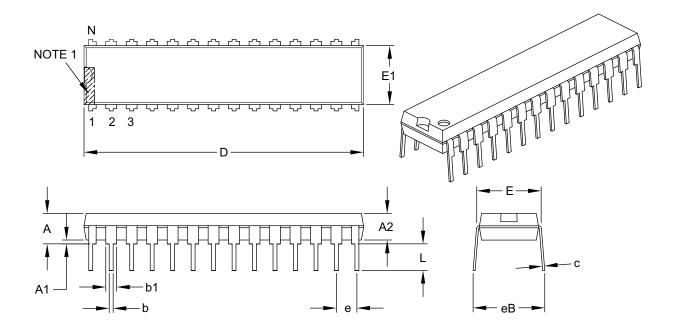

#### 33.2 Package Details

## 28-Lead Skinny Plastic Dual In-Line (SP) – 300 mil Body [SPDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                      |    | INCHES   |       |       |

|----------------------------|----|----------|-------|-------|

| Dimension Limits           |    | MIN      | NOM   | MAX   |

| Number of Pins             | Ν  | 28       |       |       |

| Pitch                      | е  | .100 BSC |       |       |

| Top to Seating Plane       | Α  | -        | -     | .200  |

| Molded Package Thickness   | A2 | .120     | .135  | .150  |

| Base to Seating Plane      | A1 | .015     | -     | -     |

| Shoulder to Shoulder Width | E  | .290     | .310  | .335  |

| Molded Package Width       | E1 | .240     | .285  | .295  |

| Overall Length             | D  | 1.345    | 1.365 | 1.400 |

| Tip to Seating Plane       | L  | .110     | .130  | .150  |

| Lead Thickness             | С  | .008     | .010  | .015  |

| Upper Lead Width           | b1 | .040     | .050  | .070  |

| Lower Lead Width           | b  | .014     | .018  | .022  |

| Overall Row Spacing §      | eB | _        | -     | .430  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-070B

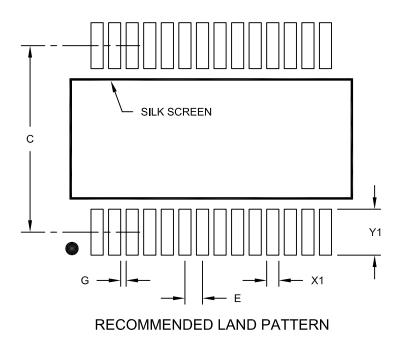

28-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units | MILLIMETERS |          |      |  |

|--------------------------|-------|-------------|----------|------|--|

| Dimension Limits         |       | MIN         | NOM      | MAX  |  |

| Contact Pitch            | E     |             | 0.65 BSC |      |  |

| Contact Pad Spacing      | С     |             | 7.20     |      |  |

| Contact Pad Width (X28)  | X1    |             |          | 0.45 |  |

| Contact Pad Length (X28) | Y1    |             |          | 1.75 |  |

| Distance Between Pads    | G     | 0.20        |          |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2073A